# Characteristics of Self-Induced Lightly-Doped-Drain Polycrystalline Silicon Thin Film Transistors with Liquid-Phase Deposition SiO<sub>2</sub> as Gate-Insulator and Passivation-Layer

Ching-Fa Yeh, Tzung-Zu Yang, and Tai-Ju Chen

Abstract— As the passivation layer on the top of undoped offset region for offset-gate structured poly-Si TFTs is exposed to hydrogen plasma, a lightly-doped-like drain region could be equivalently self-induced. The hydrogenated polycrystalline silicon thin-film transistor of this structure, named self-induced lightly-doped-drain (SI-LDD) poly-Si TFTs, was first developed with liquid-phase deposition oxide as both the gate insulator and the passivation layer. This paper describes the optimum hydrogenation condition, and the electrical characteristics for the novel SI-LDD poly-Si TFTs. The effects of DC electrical stress on SI-LDD poly-Si TFTs are also described. Finally a model is proposed to explain the degradation phenomena observed in our SI-LDD devices.

#### I. INTRODUCTION

OLYCRYSTALLINE silicon thin-film transistors (Poly-Si TFTs) have been actively investigated for a long time because of their potential use in applications such as three-dimensional integrated circuits and active-matrix liquid-crystal displays (AMLCDs). Because of their high field-effect mobility and reliability, poly-Si TFTs can be used in both the peripheral circuits and switching devices of AMLCDs. However, poly-Si TFTs have an anomalous OFF-state leakage current which increases with gate voltage ( $V_{\rm GS}$ ) and drain voltage ( $V_{\rm DS}$ ), and are unacceptable for switching device application. Holding signal levels needed for acceptable image quality requires lowering the OFF-state current below 0.1 pA per micrometer of channel width [1].

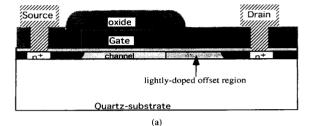

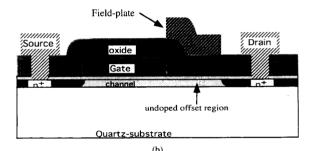

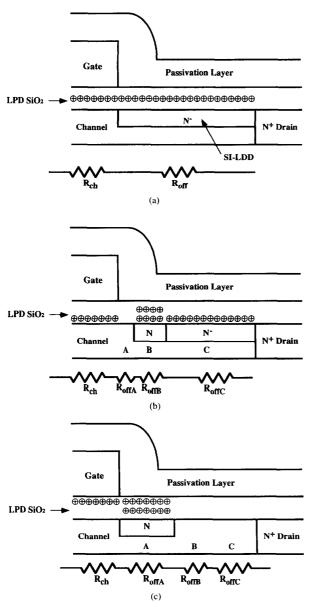

The anomalous leakage current  $(I_{\rm OFF})$  is generally attributed to field enhanced carrier emission via trap states near the drain junction. To decrease the electric field in the drain depletion region, an offset-gate structured TFT (Fig. 1(a)) in which a lightly-doped  $n^-$  region is introduced between the undoped channel and the  $n^+$  region has been proposed [2]–[4]. In that case, the additionally required implantation for lightly-doped  $n^-$  region complicates processing and increases costs. Besides, another TFT structure called the field-induced-drain (FID) TFT has also been proposed to reduce the anomalous leakage current and achieve high ON/OFF current ratio [5]–[8]. However, this FID structure (Fig. 1(b)) requires

Manuscript received May 11, 1994; revised October 4, 1994. The review of this paper was arranged by Associate Editor K. Shenai.

The authors are with the Department of Electronics Engineering & Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C. IEEE Log Number 9407766.

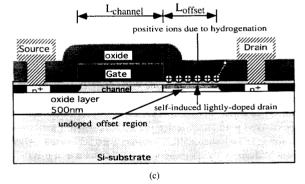

Fig. 1. (a) Offset-gate TFT structure; (b) field-induced-drain (FID) TFT structure; (c) self-induced lightly-doped-drain (SI-LDD) TFT structure.

use of an additional field-plate electrode. Furthermore, the performance of the FID device is very sensitive to the field-plate bias and interlayer material compositional characteristic.

Recently, Kanicki [9] proposed a novel TFT with an undoped offset structure for achieving high ON/OFF current ratio

0018-9383/95\$04.00 © 1995 IEEE

| Тн | E DEVICE CHARACTERISTIC | C PARAMETERS FOR THE S  | ample Groups A, I                | 3, and C. Gro       | UPS A AND B: $L$ | $_{ m off}=0\mu m,$ Gro                  | UP C: $L_{ m off}=0$                  | μη |

|----|-------------------------|-------------------------|----------------------------------|---------------------|------------------|------------------------------------------|---------------------------------------|----|

|    | parameters sample group | Hydrogenation time (hr) | Active poly-Si<br>thickness (nm) | V <sub>th</sub> (V) | S<br>(V/dec)     | μ <sub>FE</sub> (cm <sup>2</sup> /V·sec) | N <sub>t</sub><br>(cm <sup>-2</sup> ) |    |

|    | Α                       | 0                       | 100                              | 12.9                | 2.11             | 17.9                                     | 7.25×10 <sup>12</sup>                 |    |

|    | В                       | 3                       | 100                              | 6.91                | 1.28             | 25.5                                     | 4.20×10 <sup>12</sup>                 | l  |

3.37

0.425

30

TABLE I

(The maximum process temperature is 625°C)

independent of gate bias. With a dual passivation layer on top of the undoped offset region being exposed to hydrogen plasma, a lightly-doped-like region can be equivalently selfinduced. The dual passivation layer was prepared by a series of processes including silicon dioxide (SiO<sub>2</sub>) deposition by plasma enhanced chemical vapor deposition (PECVD), hydrogen plasma annealing and N-rich silicon nitride deposition by PECVD. These processes were very complicated, and the equipment was very expensive. In this study, we first developed an undoped poly-Si TFT structure with liquid-phase deposited (LPD) [10] oxide as a gate insulator and passivation layer. The apparatus used for LPD-oxide was very inexpensive, and the process easily performed at room-temperature. Because the hydrogenation treatment is an indispensable step in poly-Si TFTs processing, we called such devices "Self-Induced Lightly-Doped-Drain" (SI-LDD) poly-Si TFTs (Fig. 1(c)) [11], [12]. First, we will describe the investigation of the hydrogenation condition for the passivation layer, and then describe the electrical behavior of our SI-LDD poly-Si TFTs. The effects of DC electrical stress on the new devices will also be described. Finally, a model of SI-LDD and the migration of positive charges will be proposed to explain the results of this research.

C

## II. DEVICE FABRICATION

The fundamental fabrication processes of SI-LDD TFTs are compatible with those of conventional TFTs. First, both the 30 nm and the 100 nm-thick active poly-Si layer prepared by solid-phase crystallization (SPC) method were patterned into islands, respectively. As both gate insulator and passivation layer, a 100 nm-thick silicon oxide was grown at 30°C by LPD method. The 400 nm-thick poly-Si layer was deposited and patterned as a gate electrode. After the undoped offset regions were covered with photo-resist, the self-aligned ion implantation for gate and source/drain regions was performed. After dopant activation, hydrogenation was performed in a parallelplate plasma reactor at 300°C. The optimum hydrogenation time was determined. Finally, a 500 nm-thick interlayer oxide was formed by PECVD method. After metallization, sintering was performed at 400°C for 15 minutes. The maximum process temperature was 625°C. A schematic cross-sectional view of a finished SI-LDD poly-Si TFT is shown in Fig. 1(c). In this experiment, the channel length (L) is 20  $\mu$ m, the channel width (W) is 100  $\mu$ m, and the offset length ( $L_{\text{off}}$ ) varies from 0 to 10  $\mu$ m. Three groups of SI-LDD samples labeled A, B and C were prepared and are summarized in Table I.

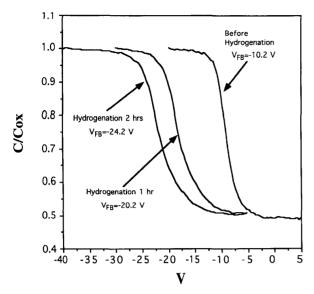

To reduce the series resistance in the undoped offset region, the hydrogenation treatment must be optimized; that is, enough positive charges must be incorporated into the passivation layer to ensure that an adequate number of electrons will be induced in the surface layer of the offset region. Hydrogenation was performed in a atmosphere containing H2 and N2 gas mixture. As a parameter, the hydrogenation time was 1 hour, 2 hours, or 3 hours. To trace the effect of hydrogenation on incorporation of positive charges, the metal/oxide/singlecrystal Si (MOS) capacitors with hydrogenated LPD-SiO<sub>2</sub> as insulator were also prepared.

22.4

$3.00 \times 10^{12}$

# III. RESULTS AND DISCUSSION

### A. Hydrogenation Effect

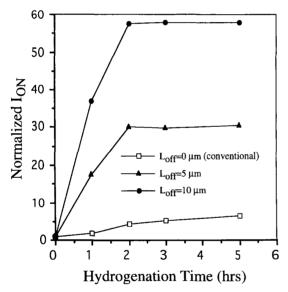

First, the positive-charge incorporation in the passivation layer was investigated by means of flat-band voltage  $(V_{\rm FB})$ shifts of MOS capacitors exposed to hydrogen plasma. As shown in Fig. 2, the value of  $V_{\rm FB}$  corresponding to C-V curves changed from -10.6 V to -20.2 V and to -24.2 V after 1 hr and 2 hrs of hydrogenation, respectively. These results show that positive charges indeed were incorporated in the passivation layer during hydrogenation. There is also evidence of positive charges incorporated in the passivation layer of SI-LDD poly-Si TFT: it became more conductive owing to electron accumulation on the surface layer of the undoped offset region. In other words, a lightly-doped-like region has been equivalently self-induced with the hydrogen plasma treatment. The quantity of positive charges is propositional to hydrogenation time. However, the  $V_{\mathrm{FB}}$  changes indicated a saturation after 2 hrs. of hydrogenation. As shown in Fig. 3, there is also evidence of saturation on normalized ON current  $(I_{ON})$  in SI-LDD poly-Si TFTs which can be attributed to positive-charge saturation in the passivation layer. Therefore, in this study, we considered 3 hours the optimum hydrogenation time.

# B. Characteristics of Low-Temperature-Processed (LTP)SI-LDD Poly-Si TFTs

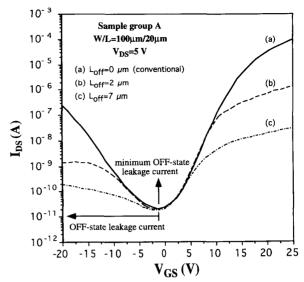

Next, we will discuss the characteristics of the LTP SI-LDD poly-Si TFTs with LPD-SiO<sub>2</sub> as gate insulator. Figure 4 shows the transfer characteristics ( $I_{DS}$ - $V_{GS}$ ) at  $V_{DS}$  =5 V for the group A samples (no hydrogenation) with  $L_{\rm off}$  as a parameter. From the  $I_{\rm DS}$ - $V_{\rm GS}$  of the conventional TFT ( $L_{\rm off}=0~\mu{\rm m}$ ), the typical characteristic parameters including threshold voltage  $(V_{\rm th})$  of 12.9 V, subthreshold swing (S) of 2.11 V/dec,

Fig. 2. High frequency (1 MHz) C-V characteristics and flat-band voltage ( $V_{\rm FB}$ ) of MOS capacitors before and after hydrogenation. The value of  $V_{\rm FB}$  corresponding to C-V curves changed from  $-10.6\,\rm V$  to  $-20.2\,\rm V$  and to  $-24.2\,\rm V$ after 1 hr and 2 hrs of hydrogenation, respectively.

Fig. 3. Normalized ON current  $(I_{\rm ON})$  as a function of hydrogenation time for SI-LDD poly-Si TFTs with  $L_{\rm off}=0~\mu{\rm m}$ , 5  $\mu{\rm m}$  and 10  $\mu{\rm m}$ . Normalized  $I_{\rm ON}$  saturated after 2 hrs of hydrogenation for TFTs with  $L_{\rm off}=5~\mu{\rm m}$ , and 10  $\mu{\rm m}$ .

mobility ( $\mu_{\rm FE}$ ) of 17.9 cm<sup>2</sup>/V·sec and trap-state density ( $N_t$ ) of 7.25  $\times$  10<sup>12</sup> cm<sup>-2</sup> were obtained and summarized in Table I.  $V_{\rm th}$  is defined as the gate voltage which yields a normalized drain current of 0.1  $\mu$ A·W/L measured at  $V_{\rm DS}$  =5 V [13].  $N_t$  existed in the poly-Si channel is calculated by extracting a straight line on the plot of In ( $I_{\rm DS}/V_{\rm GS}$ ) versus 1/ $V_{\rm GS}^2$  at low  $V_{\rm DS}$  and high  $V_{\rm GS}$  [14]. Since the group A were as-fabricated samples, no self-induced lightly-doped drain existed; ON-state performance was very poor and severely limited by the series

Fig. 4. A typical  $I_{\rm DS}$ - $V_{\rm GS}$  characteristics at  $V_{\rm DS}$  =5 V for sample group A poly-Si TFTs with  $L_{\rm off}$  as a parameter.

resistance in undoped offset region. On the other hand, for TFT with  $L_{\rm off}=2~\mu{\rm m}$  or 7  $\mu{\rm m}$ , the OFF-state current increased with  $|V_{\rm GS}|$  in the range of  $-10~{\rm V}< V_{\rm GS}<0~{\rm V}$ . The behavior was similar to that in conventional poly-Si TFT. The OFF-state current in this gate bias range was dominated by the resistive leakage current [10], [15]. The increase of negative  $V_{\rm GS}$  reduces the resistance of the channel region, as a result, the resistive leakage current increases.

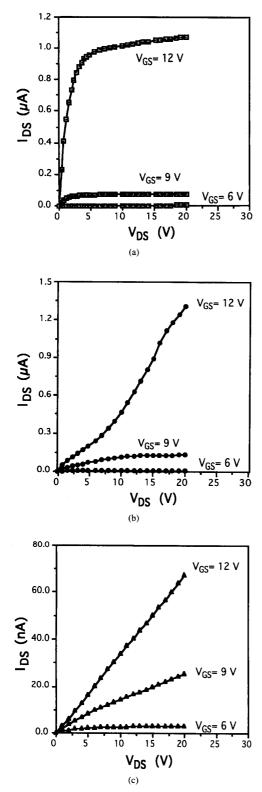

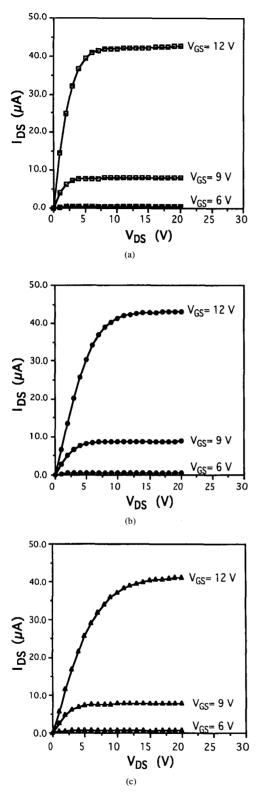

Figures 5(a), (b) and (c) show typical output characteristics  $(I_{\rm DS}\text{-}V_{\rm DS})$  for sample group A with  $L_{\rm off}=0~\mu{\rm m}$ , 2  $\mu{\rm m}$  and 7  $\mu{\rm m}$ , respectively. Except for conventional TFT ( $L_{\rm off}=0~\mu{\rm m}$ ), both offset-gate structured TFTs showed triode-like characteristics in the low  $V_{\rm DS}$  region. In other words, the TFTs without hydrogenation suffered from the so-called current-pinching phenomena in the low  $V_{\rm DS}$  region. It is attributable to high series resistance in the undoped offset region.

However, a comparison of Fig. 6 (sample group B) with Fig. 4 shows 3 hours of hydrogenation time greatly improves transfer characteristics. When compared to the transfer characteristics of traditional TFT, significantly improved parameters including  $V_{\rm th}$  of 6.91 V, S of 1.28 V/dec,  $\mu_{\rm FE}$  of 25.5 cm<sup>2</sup>/V·sec and  $N_t$  of  $4.2 \times 10^{12}$  cm<sup>-2</sup> were obtained; these are summarized in Table I. And, after 3 hrs. of hydrogenation the driving currents were increased over two orders of magnitude no matter whether the TFT was tested with  $L_{\rm off}$  of 2  $\mu{\rm m}$ or 7  $\mu m$ . Because a lightly-doped-drain had been induced and thus the conductivity was increased, these samples were therefore called SI-LDD TFTs. Moreover, in these SI-LDD TFTs, excellent turn-on characteristics without kink effect, as shown in Fig. 7(a), (b) and (c), were also achieved. The saturation current  $(I_{\mathrm{DS,sat}})$  only decreased a little even when the TFT was tested with  $L_{\rm off}$  of 7  $\mu{\rm m}$ . And the saturation voltage  $(V_{\rm DS,sat})$  also increased with  $L_{\rm off}$ . On the other hand, from a comparison of Fig. 4 and Fig. 6 we see that in our LTP SI-LDD poly-Si TFTs, the  $L_{\rm off}$  of 2  $\mu m$  was not long

Fig. 5. A typical output characteristics  $(I_{\rm DS}\text{-}V_{\rm DS})$  with  $V_{\rm GS}$  as a parameter for sample group A. (a)  $L_{\rm off}$  =0  $\mu$ m (conventional), (b)  $L_{\rm off}$  =2  $\mu$ m, and (c)  $L_{\rm off}$  =7  $\mu$ m.

Fig. 6. A typical transfer characteristics ( $I_{\rm DS}$ - $V_{\rm GS}$ ) at  $V_{\rm DS}$  =5 V for sample group B with  $L_{\rm off}$  as a parameter.

enough to make OFF-state current independent of  $|V_{\rm GS}|$  for both sample groups A and B.

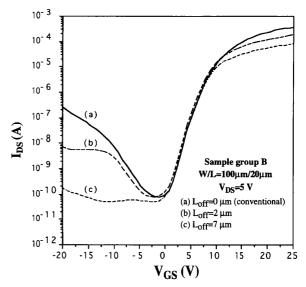

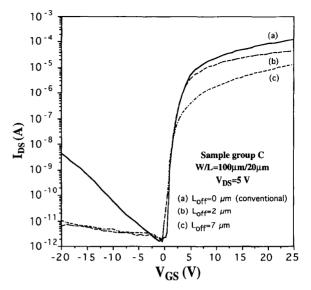

From Fig. 6, we see that the minimum OFF-state current of about 10<sup>-10</sup> A is still too large to satisfy the specification of less than 0.1 pA per micrometer of channel width for switchingdevice application in AMLCD. To further improve ON/OFF electric characteristics, the effectness of thinning the active poly-Si films was also investigated for the SI-LDD TFTs. Fig. 8 shows a typical transfer characteristics of  $V_{\rm DS}$  =5 V for the sample group C, in which the active poly-Si was 30 nm-thick. Compared with sample groups A and B, we found that the sample group C indeed had much-improved OFF-state characteristics. Especially, the minimum OFF-state drain current drops to about 2 pA. It shows that our SI-LDD TFTs with thinned poly-Si film achieves the specification of AMLCD. On the other hand, ON-state current of this sample group with  $L_{\rm off}$  =7  $\mu m$  was decreased about one order of magnitude compared with conventional TFT. Compromising OFF-state current with ON-state current, the offset length in  $2\sim5~\mu m$  is therefore an optimum choice for SI-LDD poly-Si TFTs in sample group C. The characteristics parameters of LTP SI-LDD poly-Si TFT with 30 nm-thick active-layer and  $L_{\rm off}$  =2  $\mu m$  are summarized in Table I. The characteristics with  $V_{\rm th}$  of 3.37 V, S of 425 mV/dec,  $\mu_{\rm FE}$  of 22.4 cm<sup>2</sup>/V·sec,  $N_t$  of  $3.0\times 10^{12}~\rm cm^{-2}$  and  $I_{\rm ON}/I_{\rm OFF}$  ratio of  $2.08\times 10^7$  at  $V_{\rm DS}$  =5 V were obtained. All of the parameters exhibited eminently satisfactory performance. The excellent ON/OFF current ratio (>10<sup>7</sup>), nearly independent of  $V_{\rm DS}$  and  $V_{\rm GS}$ , was achieved.

# C. Reliability of SI-LDD Poly-Si TFT

The stability of the new SI-LDD poly-Si TFTs is of significant importance from the standpoints of fabrication technology and device structure. The long-term stability of the devices

Fig. 7. A typical output characteristics ( $I_{\rm DS}$ - $V_{\rm DS}$ ) with  $V_{\rm GS}$ as a parameter for sample group B. (a)  $L_{\rm off}$  =0  $\mu$ m (conventional), (b)  $L_{\rm off}$  =2  $\mu$ m, and (c)  $L_{\rm off}$  =7  $\mu$ m.

Fig. 8. A typical transfer characteristics ( $I_{\rm DS}$ - $V_{\rm GS}$ ) at  $V_{\rm DS}$  =5 V for sample group C with  $L_{\rm off}$  as a parameter.

after they were fabricated and stored for a long time was studied. We found no changes in the device performance even after two months of storage at room temperature. However, after DC electrical stress, the characteristics of the devices changed significantly.

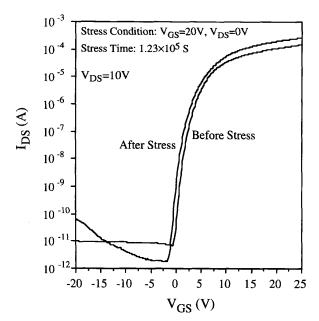

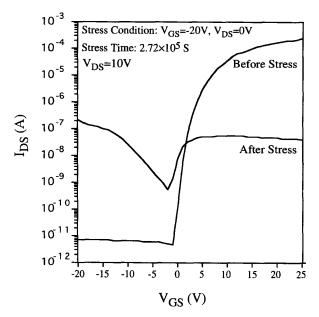

Fig. 9 shows a typical change of  $I_{DS}$ - $V_{GS}$  characteristics for the SI-LDD poly-Si TFT (sample group C) with  $L_{\rm off} = 2$  $\mu m$  under positive stress with  $V_{\rm GS}$  =20 V and  $V_{\rm DS}$  = 0 V for  $1.23 \times 10^5$  s. It is seen that the characteristics curve after positive stress parallelly shifted to the left of the original curve. It is also found that the value of threshold voltage decreased from 3.59 V to 2.28 V, while the subthreshold swing was nearly unchanged. The degradation implied that there existes an instability factor that causes curve parallel shifting. The instability factor obviously can not be attributed to the generation of trapping states. In addition, the minimun of OFFstate current decreased from  $7.0 \times 10^{-12}$  A to  $1.8 \times 10^{-12}$ A, which was the level of the gate leakage current. The OFFstate current also increased with  $|V_{\rm GS}|$  and behaved like that in conventional TFTs without offset regions. The degradation phenomenon implied that the series resistance of the current path had increased. The result is consistent with the output characteristics after stress, which exhibited slight currentpinching phenomena in the linear region at low drain voltage. Figure 10 shows a typical change of  $I_{DS}$ - $V_{GS}$  characteristics for the same devices (sample group C) after negative stress with  $V_{\rm GS} = -20$  V and  $V_{\rm DS} = 0$  V for  $2.72 \times 10^5$  s. We can see that device characteristics changed very much after negative stress in comparison with their before-stress values, and they changed differently than after positive stress. The  $I_{ON}$  after negative stress was significantly suppressed, it was suspected that the series resistance had increased. On the contrary, the OFF-state current (hole current) increased greatly in comparison with that before stress. The increase of minimum OFF-state leakage current was again attributed to the

Fig. 9. A typical change of  $I_{\rm DS}$ - $V_{\rm GS}$  characteristics for the SI-LDD poly-Si TFTs with  $L_{\rm off}=2~\mu{\rm m}$  (sample group C) under the stress with  $V_{\rm GS}=20~{\rm V}$  and  $V_{\rm DS}=0~{\rm V}$  for  $1.23\times10^5~{\rm s}$ .

Fig. 10. The changes of  $I_{\rm DS}\text{-}V_{\rm GS}$  characteristics for the SI-LDD poly-Si TFTs with  $L_{\rm off}=22\,\mu{\rm m}$  (sample group C) under the stress with  $V_{\rm GS}=-20$  V and  $V_{\rm DS}=0$  V for  $2.72\times10^5$  s.

series resistance of the current path, which must have locally decreased very much. The above results lead to suspicion that the positive charges in the gate oxide and the passivation layer above the offset region moved differently under both cases of high field stress. The details will be explained later.

To further clear the essential factor of device degradation, the bias-temperature (BT) test on the conventional poly-Si

1

TFTs without offset region was also studied. The conventional device was also prepared with plasma-treated LPD-oxide as gate insulator. First, after the stress with  $V_{\rm GS}$  =20 V at 150°C for 30 min, the transfer curve parallelly shifted to the left about 5 V. The subthrethold swing was nearly unchanged, Next, after the subsequent stress with  $V_{\rm GS} = -20~{\rm V}$  at 150°C for 30 min, the curve returned about 2.5 V, and the subthrethold swing increased. The value of threshold voltage also changed in response to the shift. The most possible mechanism that could change the performance of our SI-LDD TFTs under stress was the migration of positive charges in the oxide layer [16], [17]. We speculated that most of the positive charges were hydrogen atoms. During the hydrogenation treatment, there were positive charges incorporated in the passivation layer. Because the oxides regarded as paths for high diffusion of hydrogen [18], the hydrogen atoms could laterally diffuse into gate oxide. Therefore, many hydrogen atoms acumulated at the poly-Si/SiO<sub>2</sub> interface [19]. During stressing at  $V_{\rm GS} =$ 20 V, the parallel shift toward the left for the transfer curve implied that the positive charges in the gate dielectric moved more near the poly-Si/SiO<sub>2</sub> interface. During subsequently stressing at  $V_{\mathrm{GS}} = -20$  V, the fact that the transfer curve returned toward the right suggested that the positive charges moved far away from the poly-Si/SiO<sub>2</sub> interface. In addition, some of the positive charges passivating the traps broke away from the defect sites caused by the high negative gate bias leading to the increase of the effective trap states density  $(N_t)$  [17], [20]. The tests implied that a possible migration phenomenon of positive charges in the plasma-treated LPDoxide had occurred corresponding to the BT stress. In addition, because no changes in subthreshold swing were found in the BT tests, we could conclude that neither hot-carrier effect nor charge trapping in the gate dielectric [21-25] dominated the device degradation.

# D. A Proposed Model

According to the above discussion, the most probable factor responsible for degradation in the performance of our SI-LDD TFT under stress was the migration of positive charges in the oxide layer. There have been many reports describing the unreliable positive charges existing in insulators [16], [17]. We proposed a model and illustrated the mechanism of SI-LDD and degradation in terms of positive charges migration. Figure 11(a) shows an original distribution of positive charges incorporated in both the gate oxide and the passivation layer above the offset region after hydrogen plasma treatment. Owing to the existance of positive charges in the passivation layer, beneath it a lightly doped  $N^-$  layer in the offset region was easily generated. Thus the TFT device with an equivalently lightly-doped offset region could effectively reduce the anomalous leakage current and achieve a high ON/OFF current ratio.

When a positive stress-bias was applied to the gate electrode, the high electric field under the gate electrode with the fringing fields at the edge of the gate electrode could make the positive charges migrate. The positive charges in the gate oxide under the gate electrode, as shown in Fig. 11(b), were

Fig. 11. A proposed model about the distributions of positive charges in the passivation layer above the offset region (a) before stress, (b) after  $V_{\rm GS}=20$  V stress, (c) after  $V_{\rm GS}=-20$  V stress.

forced closer to the  ${\rm Si/SiO_2}$  interface, therefore the transfer curve at ON state (as shown in Fig. 9) parallelly shifted a little. In addition, the fringing fields will be significant for only a small portion of  $L_{\rm off}$ , a small portion of the positive charges in the passivation layer were also piled up a short distance away from the gate as shown in Fig. 11(b). It can thus be concluded that the positive charges above offset region A were depleted, while those were accumulated above offset region B. Above offset region C, the positive charges were only slightly affected. Therefore, the equivalent resistance ( $R_{\rm off\ A}$ ) at region A increased due to low electron induction; while the equivalent resistance ( $R_{\rm off\ B}$ ) at region B decreased due to higher electron

1

induction. The increase in total offset resistance resultantly caused a reduction in the minimun OFF-state current (hole current) and a current-pinching phenomenon in the output characteristics. In addition, the lateral electric field along offset region B also changed with the redistribution of the positive charges. These changes thus caused an increase with  $|V_{\rm GS}|$  in OFF-state current [15]. Therefore the change of transfer curve at OFF state became much different from the simply parallel shift on the conventional device.

On the other hand, when a negative stress-bias was applied to the gate electrode, a high electric field made the distribution of positive charges under the gate electrode and above the offset region change as shown in Fig. 11(c). Owing to the negative electrical field, positive charges easily accumulated above the offset region A, while those were depleted above the offset region B and C. Thus,  $R_{\rm off A}$  easily decreased due to more electrons induced, while  $R_{\rm off B}$  and  $R_{\rm off C}$  increased greatly due to fewer electrons induced. Therefore, after negative stress the minimun of OFF-state current (hole current) increased with the reduction of total offset resistance. Because the redistribution of positive charges could affect the distribution of the lateral electric field along the offset region, the electric field near offset region A was enhanced. In addition, since these TFTs have been hydrogenated and hydrogen is only weakly bounded to the defect sites, we can see an increase in trap formation as the hydrogen breaks away from weakly passivated defect sites and migrates to the gate electrode. Thus the increase of OFF-state current with  $|V_{\rm GS}|$ was mainly due to the increase of effective trap state density and the lateral electric field along the offset region [15]. At the same time, the ON-state current was limited by the high series resistance in the offset region and effective trap state density.

The drain voltage could also play an important role in the degradation of SI-LDD poly-Si TFT. When the drain bias was applied during stress, the carrier-induced metastable midgap states were created within the poly-Si active layer due to the presence of high carrier densities in the channel [21], [23]. However, the enhancement of the high carrier densities on degradation would become dominant only in the case of long stress time.

### IV. CONCLUSION

For reducing OFF-state current and achieving high ON/OFF current ratio, a novel and simple SI-LDD poly-Si TFT with LPD-oxide as both gate insulator and passivation layer has been newly developed using LTP technologies. The 3-hour hydrogenation treatment effectively incorporated positive charges in the passivation layer, and achieved significant improvements in device performance, for example, excellent turn-on characteristics without kink effect. The driving currents were increased over two orders of magnitude, while the OFF-state current become independent of  $|V_{\rm GS}|$  (if  $L_{\rm off}>2~\mu{\rm m}$ ). Besides, the SI-LDD poly-Si TFTs with 30 nm-thick active-layer and 2  $\mu{\rm m}$  of  $L_{\rm off}$ , having an  $I_{\rm ON}/I_{\rm OFF}$  ratio of  $2.08\times10^7$  at  $V_{\rm DS}=5$  V, a  $\mu_{\rm FE}$  of  $22.4~{\rm cm}^2/{\rm V}\cdot{\rm sec}$ , a S of 425 mV/dec, a  $V_{\rm th}$  of 3.37 V, and a  $N_t$  of  $3.0\times10^{12}~{\rm cm}^{-2}$  exhibited sufficient performance for pixel transistors of AMLCDs. This new SI-

LDD poly-Si TFT was rather stable during storage. However, degradation in electrical characteristics owing to migration of positive charges was found.

#### ACKNOWLEDGMENT

This study was supported by the National Science Council, Republic of China, under contract number NSC 83-0404-E-009-093, and partly by Microelectric Technology Development Project, ERSO/ITRI.

#### REFERENCES

- H. Ohshima and S. Morozumi, "High performance poly-Si TFT for LCDs," Extended Abstr. 1991 Conf. Solid State Devices and Materials, p. 577.

- [2] S. Seki, O. Kogure, and B. Tsujiyama, "Leakage current characteristics of offset-gate-structure polycrystalline-silicon MOSFET's," *IEEE Electron Device Lett.*, vol. 8, no. 9, p. 434, 1987.

[3] K. Tanaka, H. Arai, and S. Kohda, "characteristics of offset-structure

- [3] K. Tanaka, H. Arai, and S. Kohda, "characteristics of offset-structure polycrystalline-silicon thin-film transistors," *IEEE Electron Device Lett.*, vol. 9, no. 1, p. 23, 1988.

- vol. 9, no. 1, p. 23, 1988.

[4] K. Nakazawa, K. Tanaka, S. Suyama, K. Kato, and S. Kohda, "lightly doped drain TET structure for poly.Si I CDs." SID Diagram, 3.11, 1990.

- doped drain TFT structure for poly-Si LCDs," SID Digest, p. 311, 1990.

[5] T. Y. Huang, I.-W. Wu, A. G. Lewis, A. Chiang, and R. H. Bruce, "A simpler 100-V polysilicon TFT with improved turn-on characteristics," IEEE Electron Device Lett., vol. 11, no. 6, p. 244, 1990.

- IEEE Electron Device Lett., vol. 11, no. 6, p. 244, 1990.

[6] T. Y. Huang, I.-W. Wu, A. G. Lewis, A. Chiang, and R. H. Bruce, "Device sensitivity of field-plated polysilicon high-voltage TFT's and their application to low-voltage operation," IEEE Electron Device Lett., vol. 11, no. 11, p. 541, 1990.

- vol. 11, no. 11, p. 541, 1990.

[7] K. Takana, S. Suyama, K. Kato, and S. Kohda, "A novel unified-structure field-induced-drain (UFID) poly-Si TFTs in CMOS circuits for LCD applications," SID Digest, p. 539, 1991.

- [8] K. Takana, K. Nakazawa, S. Suyama, and K. Kato, "characteristics of field-induced-drain (FID) poly-Si TFT's with high ON/OFF current ratio," IEEE Trans. Flectron Devices, vol. 39, no. 4, p. 916, 1992.

- ratio," *IEEE Trans. Electron Devices*, vol. 39, no. 4, p. 916, 1992.

[9] J. Kanicki and M. K. Hatalis, "A simple polysilicon thin film transistor structure for achieving high on/off current ratio independent of gate bias," *Extended Abstr. 1992 Conf. Solid State Devices and Materials*, p. 52.

- [10] C. F. Yeh, S. S. Lin, T. Z. Yang, C. L. Chen, and Y. C. Yang, "Performance and off-state current mechanism of low-temperature processed polysilicon thin-film transistors with LPD-SiO<sub>2</sub> gate insulator," *IEEE Trans. Electron Devices*, vol. 41, no. 2, p. 173, 1994.

- [11] C. F. Yeh, T. J. Chen, T. Z. Yang, and H. K. Chen, "Low-temperature processed poly-Si TFT with self-induced lightly-doped-drain (SI-LDD) structure," *Electronic Devices and Materials Symposium*, (Taiwan), p. 5, Oct. 15-17, 1993.

- [12] C. F. Yeh, T. J. Chen, and T. Z. Yang, "DC reliability of low-temperature self-induced lightly-doped drain poly-Si TFTs," Active Matrix Liquid Crystal Display Symposium (AMLCDS), (Bethlehem, Pennsylvania), p. 64, Oct. 21-22, 1993.

- [13] A. G. Lewis, I.-W. Wu, T. Y. Huang, M. Koyanagi, A. Chiang, and R. H. Bruce, "Polysilicon thin film transistors for analogue circuit applications," *IEDM Tech. Dig.*, p. 260, 1988.

[14] J. Levinsor, F. R. Shepherd, P. J Scanlon, W. D. Westwood, G. Este,

- [14] J. Levinsor, F. R. Shepherd, P. J Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," J. Appl. Phy., vol. 53, no. 2, p. 1193, 1982.

- thin film transistors," *J. Appl. Phy.*, vol. 53, no. 2, p. 1193, 1982. [15] C. F. Yeh, T. Z. Yang, C. L. Chen, T. J. Chen, and Y. C. Yang, "Experimental comparison of off-state current between high-temperature-and low-temperature-processed undoped channel polysilicon thin-film transistors" *Inn. I. Appl. Phys.*, vol. 32, no. 10, p. 4472, 1993.

- transistors," *Jpn. J. Appl. Phys.*, vol. 32, no. 10, p. 4472, 1993.

[16] R. M. Patrikar, R. Lal, and J. Vasi, "Net positive-charge buildup in various MOS insulators due to high-field stressing," *IEEE Electron Device Lett.*, vol. 14, no. 11, p. 530, 1993.

- [17] W. B. Jackson, N. M. Johnson, C. C. Tsai, I.-W. Wu, A. Chiang, and D. Smith, "Hydrogen diffusion in polycrystalline silicon thin films," *Appl. Phys. Lett.*, vol. 61, no. 14, p. 1670, 1992.

- Phys. Lett., vol. 61, no. 14, p. 1670, 1992.

[18] M. Nakabayashi, M. Ikegami, and T. Daikoku, "Influence of hydrogen on electrical characteristics of poly-Si resistor," Jpn. J. Appl. Phys., vol. 32, no. 9A, p. 3734, 1993.

- [19] C. A. Dimitriadis, P. A. Coxon, A. J. Lowe, J. Stoemenos, and N. A. Economou, "Control of the performance of polysilicon thin-film

- transistor by high-gate-voltage stress," *IEEE Electron Device Lett.*, vol. 12, no. 12, p. 676, 1991.

- [20] S. Banerjee, H. Shichijo, R. Sundaresan, and S. Malhi, "Hot-electron degradation of n-channel polysilicon MOSFET's," *IEEE Trans. Electron Devices*, vol. 35, no. 2, p. 152, 1988.

[21] 1.-W.Wu, W. B. Jackson, T. Y. Huang, A. G. Lewis, and A. Chiang,

- [21] I.-W.Wu, W. B. Jackson, T. Y. Huang, A. G. Lewis, and A. Chiang, "Mechanism of device degradation in n- and p-channel polysilicon TFT's by electrical stressing," *IEEE Electron Device Lett.*, vol. 11, no. 4, p. 167, 1990.

- p. 167, 1990.

C. A. Dimitriadis and P. A. Coxon, "Effects of temperature and electrical stress on the performance of thin-film transistors fabricated from undoped low-pressure chemical vapor deposited polycrystalline silicon." April Phys. Lett., vol. 54, no. 7, p. 620, 1989.

- silicon," *Appl. Phys. Lett.*, vol. 54, no. 7, p. 620, 1989.

[23] M. Hack, A. G. Lewis, and I.-W. Wu, "Physical models for degradation effects in polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 40, no. 5, p. 890, 1993.

- Devices, vol. 40, no. 5, p. 890, 1993.

[24] I.-C. Chen, S. Holland, and C. Hu, "Electrical breakdown in thin gate and tunneling oxides," *IEEE Trans. Electron Devices*, vol. 32, no. 2, p. 413, 1985

- [25] N. Kato, T. Yamada, S. Yamada, T. Nakamura, and T. Hamano, "Degradation mechanism of polysilicon TFT's under d.c. stress," *IEDM Tech. Dig.*, p. 677, 1992.

Ching-Fa Yeh was born in Hsinchu, Taiwan, on September 20, 1948. He received the B.S. degree from National Oceanic University, Keelung, Taiwan, ROC, in 1971, the M.S. and Ph.D. degrees from the University of Tokyo, Tokyo, Japan, in 1979 and 1982, respectively, all in electrical engineering.

From 1982 to 1988, he was with the Fuji Xerox's Electronic Technology Laboratories, Ebina, where his work has been concerned with the research and development of semiconductor process technologies and devices, particularly on Dry Process technology

and Contact Amorphous-Si Image Sensor, and High-Voltage MOSFET.

Currently, he is an Associated Professor at the Department of electronics Engineering & Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan. His current research interests include thin-film transistor, power devices, silicon-wafer directly bonding technologies, and low-temperature processed materials and devices.

Dr. Yeh is a member of Japanese Journal Applied Physics Society, and he also as an oversea member of program committee of the international Conference on Solid State Devices and Materials.

Tzung-Zu Yang was born in Pingtung, Taiwan, on July 11, 1969. He received the B.S. and M.S. degrees in electronics engineering from National Chiao-Tung University in 1991 and 1993, respectively.

Currently, he is working with the Electronic Research and Service Organization, Industrial Technology Research Institute, Hsinchu, Taiwan, ROC, where he is engaged in the research of field emission display.

Tai-Ju Chen was born in Tainan, Taiwan, on September 13, 1970. He received the B.S. degree in electrical engineering from National Cheng Kung University, Tainan, Taiwan, ROC, in 1992. He is currently working towards the Ph.D. degree in electronics engineering at National Chiao-Tung University.

His current research interest is in the fabrication of polysilicon thin-film transistors.