## Improved current distribution in resistive memory on flexible substrate using nitrogenrich TaN electrode

Zhi-Wei Zheng, Chun-Hu Cheng, Kun-I Chou, Ming Liu, and Albert Chin

Citation: Applied Physics Letters 101, 243507 (2012); doi: 10.1063/1.4772003

View online: http://dx.doi.org/10.1063/1.4772003

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/101/24?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Band alignment between Ta2O5 and metals for resistive random access memory electrodes engineering Appl. Phys. Lett. **102**, 062106 (2013); 10.1063/1.4792274

Flexible resistive random access memory using solution-processed TiOx with Al top electrode on Ag layer-inserted indium-zinc-tin-oxide-coated polyethersulfone substrate

Appl. Phys. Lett. 99, 142110 (2011); 10.1063/1.3621826

Microscopic origin of bipolar resistive switching of nanoscale titanium oxide thin films

Appl. Phys. Lett. 95, 162108 (2009); 10.1063/1.3251784

Role of TaON interface for Cu x O resistive switching memory based on a combined model

Appl. Phys. Lett. 94, 053510 (2009); 10.1063/1.3078824

Resistive switching of aluminum oxide for flexible memory

Appl. Phys. Lett. 92, 223508 (2008); 10.1063/1.2939555

## Improved current distribution in resistive memory on flexible substrate using nitrogen-rich TaN electrode

Zhi-Wei Zheng, 1 Chun-Hu Cheng, 2 Kun-I Chou, 3 Ming Liu, 1 and Albert Chin 3,a)

(Received 17 October 2012; accepted 28 November 2012; published online 12 December 2012)

Narrow current distribution, good endurance, and low  $28 \,\mu\text{W}$  switching power are successfully achieved in Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN resistive random access memory devices. The good distribution and endurance are attributed to the nitrogen-rich TaN to increase the oxidation resistance and decrease the TaON and oxygen vacancies formation from x-ray photoelectron spectroscopy measurements, where such oxygen vacancies are related to current conduction at high resistance state. In addition, the devices on the flexible polyimide substrate exhibit excellent mechanical endurance upon repeated bending tests, showing their high potential for low-cost flexible memory application. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4772003]

The down-scaling flash memory 1-3 into sub-20 nm becomes more difficult due to the fundamental physics of smaller stored charges in highly scaled cell size. The noncharge based resistive random access memory (RRAM) stores resistance change in memory cell that is attractive to scale down into sub-10 nm regime. Besides, the simpler structure, lower cost, faster switching speed, and embedded memory function are other merits for RRAM.3-18 Unfortunately, the much poor distribution and high switching power are the major challenges for RRAM. Furthermore, noble metal electrodes are widely used for RRAM, but the difficult etching process and higher cost are the other concerns. To address these issues, we previously reported the ultra-low power RRAM by using hopping conduction via defects in covalent-bond oxide or metal-oxynitride. 13-16 However, the wide current distribution is still the most difficult challenge for RRAM.

In this paper, we discovered the strong dependence of current distribution on electrode material of RRAM. Using etching friendly and low cost TaN electrode and deposited under nitrogen-rich (N-rich) condition, excellent current distribution, endurance, and low switching power are successfully achieved in the Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/N-rich-TaN RRAM devices simultaneously. The forming-free and selfcompliance resistive switching are other merits for this RRAM to simplify the test and operation. These superior performances are ascribed to the improved oxidation resistance in N-rich-TaN to decrease the oxygen vacancies formation in dielectric. Such oxygen vacancies are related to the hopping conduction current, 19 by multi-phonon-assisted electron tunneling via oxygen vacancy created traps in dielectric. 18 Moreover, the RRAM device on flexible plastic substrate showed strong mechanical endurance upon repeated bending tests, showing its potential for lowtemperature flexible memory application.

A low-cost flexible polyimide substrate was used in this study. Prior to the device fabrication process, the polyimide

substrates were annealed at 100 °C. The RRAM devices have similar metal-insulator-metal (MIM) structure with analog/ DRAM capacitors. The fabrication began with a 100 nm thick SiO<sub>2</sub> deposition on substrate. Then, a 100 nm thick TaN was deposited by physical vapor deposition (PVD) as the bottom electrode, followed by the nitrogen plasma treatment.<sup>20</sup> Such treatment has been used for MIM capacitor to increase its capacitance density and decrease the oxidation of bottom TaN electrode. Sequentially, 15 nm TiO<sub>v</sub> and 8 nm GeO<sub>x</sub> were deposited. Finally, a 50 nm thick Ni was deposited and patterned to form the top electrode, which provides high workfunction (5.1 eV) and works as a low-cost solution for high-κ DRAM capacitors.<sup>21</sup> The control sample without nitrogen plasma treatment was also fabricated for performance comparison. The fabricated devices were characterized by current-voltage (I-V), set/reset cycled endurance, and x-ray photoelectron spectroscopy (XPS) measurements.

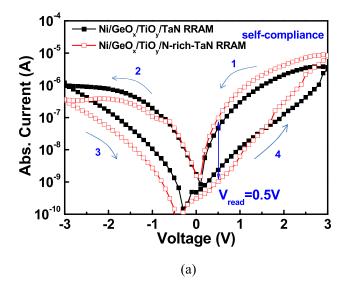

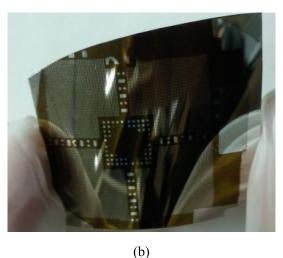

Figure 1(a) shows the swept I-V curves of Ni/GeO<sub>x</sub>/ TiO<sub>v</sub>/TaN RRAM devices with or without the nitrogen plasma treatment, and the photo of fabricated devices on flexible substrate is shown in Fig. 1(b). The  $3 V \rightarrow 0 V$  $\rightarrow$  -3 V $\rightarrow$ 0 V $\rightarrow$ 3 V swept directions were indicated by the arrows. The resistance changes from high resistance state (HRS) to low resistance state (LRS) during set (direction 4) at positive voltages and returns to HRS during reset (direction 2) at negative voltages. Forming-free resistive switching and self-compliance set/reset operations were obtained, which are attributed to the unique hopping conduction mechanism in  ${\rm GeO_x}$ -based RRAM $^{13-16}$  rather than the conductive filament. The asymmetric switching I-V curves are ascribed to the different work functions of bottom TaN (4.6 eV) and top Ni (5.1 eV) electrodes. A resistance ratio of 96 at 0.5 V read, a low set power of  $27 \mu W$  (9  $\mu A$  at 3 V), and a lower reset power of  $0.9 \,\mu\text{W}$  ( $0.3 \,\mu\text{A}$  at  $-3 \,\text{V}$ ) were measured in the Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/N-rich-TaN devices. Such low switching currents are ascribed to the hopping conduction in dielectric defects 13-16,18 with large hopping resistance. 19

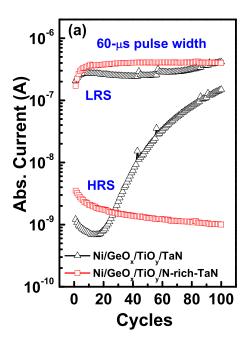

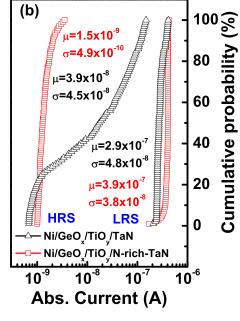

Good endurance and distribution are the necessary characteristics for non-volatile memory. Figures 2(a) and 2(b) show the measured endurance and current distributions of

<sup>&</sup>lt;sup>1</sup>Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China <sup>2</sup>Department of Mechatronic Technology, National Taiwan Normal University, Taipei 106, Taiwan

<sup>&</sup>lt;sup>3</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

a) Author to whom correspondence should be addressed. Electronic mail: albert\_achin@hotmail.com.

FIG. 1. (a) Swept *I-V* curves of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices on polyimide substrate, with or without the nitrogen plasma treatment. The swept directions are indicated by the arrows. (b) The photograph of the fabricated devices.

Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices, with or without the nitrogen plasma treatment. Here, the endurance was tested under 60 μs set/reset operation for 100 cycles. The fast degradation of HRS current under stress leads to poor endurance in control RRAM devices without nitrogen plasma treatment. The control devices also suffer from the very wide HRS current distribution. In sharp contrast, much improved endurance and distributions are achieved in Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/N-rich-TaN RRAM devices, indicating the importance of nitrogen plasma treatment. The fast change of LRS and HRS currents for the first 11th set/reset cycles may be related to the lacking of forming process.

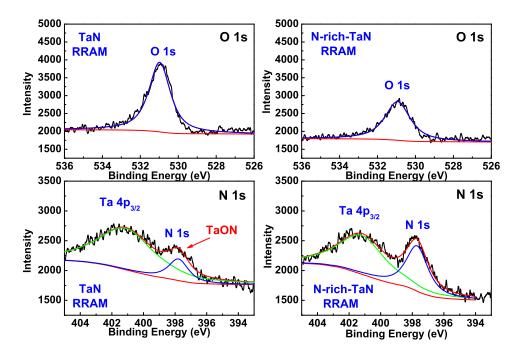

We further performed the XPS analysis to investigate such large improvements of endurance and distribution. Figure 3 shows the measured XPS spectra of O 1s and N 1s near the TiO<sub>v</sub>/TaN interface, where the RRAM devices after electrical stress were examined (60 µs set/reset for 100 cycles). Here, the ion-beam sputtering was used to analyze the XPS signals near the bottom TaN. Better nondestructive analysis can be obtained by hard x-ray photoelectron spectroscopy (HAXPES)<sup>22-24</sup> that has thicker probing depth. After continuous electrical stress, higher O 1s peak intensity and lower N 1s peak intensity were observed in control devices than those devices with nitrogen plasma treatment. Thus, the poor endurance of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices under electrical stress is related to the oxygen reaction with TaN. Such reaction also forms more oxygen vacancies in TiO<sub>v</sub> for hopping conduction that in turn increases the HRS current in Fig. 2(a) with increasing stress cycles. In contrast, N-rich-TaN increases oxidation resistance to lower the randomly reacted TaON and oxygen vacancies formation, which improves the HRS current distribution. Although such interface reaction is improvable using noble metal, such as Pt, no selective reactive-ion etching is available to pattern this noble metal in addition to its expansive cost.

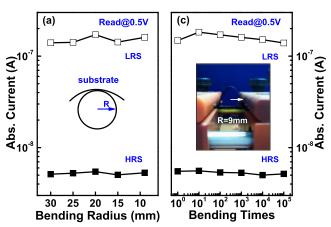

To further explore the feasibility of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/N-rich-TaN RRAM for flexible electronics application, the

FIG. 2. (a) Endurance and (b) current distributions of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices, with or without the nitrogen plasma treatment. The standard deviation  $(\sigma)$  and mean  $(\mu)$  values are also shown for comparison.

FIG. 3. The XPS spectra of O 1s (upper curves) and N 1s (lower curves) core level for TaN electrode near TiO<sub>y</sub>/TaN interface of Ni/GeO<sub>x</sub>/TiO<sub>y</sub>/TaN RRAM devices, with or without the nitrogen plasma treatment, after continuous set/reset stress.

FIG. 4. (a) The LRS and HRS currents as a function of bending radius. (b) The mechanical endurance characteristics with continuous bending of polyimide substrate.

fabricated devices were under a flexibility test. In the flexibility test, the RRAM device was bent to a surface curvature radius of  $30\sim9$  mm, and then released for electrical measurements. As shown in Fig. 4(a), severe mechanical bending from 30 to 9 mm radius did not degrade the device characteristics of LRS and HRS currents. This may be due to the small  $60 \, \mu \text{m}$  radius of RRAM device. The mechanical endurance was also investigated by repeated bending. As shown in Fig. 4(b), the flexible RRAM devices show excellent mechanical endurance of continuous bending to  $10^5$  cycles, with a bending radius as small as 9 mm.

In conclusion, using nitrogen plasma treatment, the Ni/  $GeO_x/TiO_y/N$ -rich-TaN RRAM shows a low total  $28 \,\mu W$  switching power, good uniformity, and high endurance. These good performances are ascribed to the N-rich-TaN electrode to reduce TaON and oxygen vacancy formation that in turn preserve a stable low HRS current. Besides, excellent mechanical flexibility was achieved, showing good potential of low-cost and high-performance flexible electronics application.

<sup>1</sup>C. Y. Tsai, T. H. Lee, A. Chin, H. Wang, C. H. Cheng, and F. S. Yeh, Tech. Dig.—Int. Electron Devices Meet. **2010**, 110.

<sup>2</sup>A. Chin, C. C. Laio, C. Chen, K. C. Chiang, D. S. Yu, W. J. Yoo, G. S. Samudra, T. Wang, I. J. Hsieh, S. P. McAlister, and C. C. Chi, Tech. Dig.—Int. Electron Devices Meet. **2005**, 158.

<sup>3</sup>See www.itrs.net for International Technology Roadmap for Semiconductors (ITRS), 2011 (Online).

<sup>4</sup>U. Russo, D. Ielmini, C. Cagli, A. L. Lacaita, S. Spiga, C. Wiemer, M. Perego, and M. Fanciulli, Tech. Dig.—Int. Electron Devices Meet. 2007, 775.

<sup>5</sup>C. Yoshida, K. Tsunoda, H. Noshiro, and Y. Sugiyama, Appl. Phys. Lett. **91**, 223510 (2007).

<sup>6</sup>N. Xu, L. Liu, X. Sun, X. Liu, D. Han, Y. Wang, R. Han, J. Kang, and B. Yu, Appl. Phys. Lett. **92**, 232112 (2008).

<sup>7</sup>N. Xu, B. Gao, L. F. Liu, B. Sun, X. Y. Liu, R. Q. Han, J. F. Kang, and B. Yu, Tech. Dig.—Symp. on VLSI Tech. **2008**, 100.

S. Yoon, I. G. Baek, J. Zhao, H. Sim, M. Y. Park, H. Lee, G. H. Oh, J. C. Shin, I. S. Yeo, and U. I. Chung, Tech. Dig.—Symp. on VLSI Tech. 2009, 26.

X. Sun, B. Sun, L. Liu, N. Xu, X. Liu, R. Han, J. Kang, G. Xiong, and T. P. Ma, IEEE Electron Device Lett. 30, 334 (2009).

<sup>10</sup>Q. Liu, S. Long, W. Wang, Q. Zuo, S. Zhang, J. Chen, and M. Liu, IEEE Electron Device Lett. 30, 1335 (2009).

<sup>11</sup>B. Gao, B. Sun, H. Zhang, L. Liu, X. Liu, R. Han, J. Kang, and B. Yu, IEEE Electron Device Lett. 30, 1326 (2009).

<sup>12</sup>M. Jo, D. J. Seong, S. Kim, J. Lee, W. Lee, J. B. Park, S. Park, S. Jung, J. Shin, D. Lee, and H. Hwang, Tech. Dig.—Symp. on VLSI Tech. 2010, 53

<sup>13</sup>C. H. Cheng, A. Chin, and F. S. Yeh, Tech. Dig.—Int. Electron Devices Meet. 2010, 448.

<sup>14</sup>C. H. Cheng, A. Chin, and F. S. Yeh, Adv. Mater. 23, 902 (2011).

<sup>15</sup>C. H. Cheng, A. Chin, and F. S. Yeh, Appl. Phys. Lett. **98**, 052905 (2011).

<sup>16</sup>C. H. Cheng, P. C. Chen, Y. H. Wu, F. S. Yeh, and A. Chin, IEEE Electron Device Lett. 32, 1749 (2011).

<sup>17</sup>W. Kim, S. I. Park, Z. Zhang, Y. L. Young, D. Sekar, H.-S. Philip Wong, and S. Simon Wong, Tech. Dig.—Symp. on VLSI Tech. 2011, 22.

<sup>18</sup>A. V. Shaposhnikov, T. V. Perevalov, V. A. Gritsenko, C. H. Cheng, and A. Chin, Appl. Phys. Lett. **100**, 243506 (2012).

<sup>19</sup>A. Chin, K. Lee, B. C. Lin, and S. Horng, Appl. Phys. Lett. **69**, 653 (1996).

<sup>20</sup>K. C. Chiang, C. C. Huang, A. Chin, W. J. Chen, H. L. Kao, M. Hong, and J. Kwo, Tech. Dig.—Symp. on VLSI Tech. 2006, 102.

<sup>21</sup>K. C. Chiang, C. H. Cheng, H. C. Pan, C. N. Hsiao, C. P. Chou, A. Chin, and H. L. Hwang, IEEE Electron Device Lett. 28, 235 (2007).

<sup>22</sup>M. Sowinska, T. Bertaud, D. Walczyk, S. Thiess, M. A. Schubert, M. Lukosius, W. Drube, Ch. Walczyk, and T. Schroeder, Appl. Phys. Lett. 100, 233509 (2012).

<sup>23</sup>T. Bertaud, M. Sowinska, D. Walczyk, S. Thiess, A. Gloskovskii, Ch. Walczyk, and T. Schroeder, Appl. Phys. Lett. **101**, 143501 (2012).

<sup>24</sup>H. Akinaga and H. Shima, Proc. IEEE **98**, 2237 (2010).