## Analysis of anomalous traps measured by charge pumping technique in HfO2/metal gate n-channel metal-oxide-semiconductor field-effect transistors

Szu-Han Ho, Ting-Chang Chang, Ying-shin Lu, Wen-Hung Lo, Ching-En Chen, Jyun-Yu Tsai, Hua-Mao Chen, Chi-Wei Wu, Hung-Ping Luo, Guan-Ru Liu, Tseung-Yuen Tseng, Osbert Cheng, Cheng-Tung Huang, and Simon M. Sze

Citation: Applied Physics Letters 101, 233509 (2012); doi: 10.1063/1.4769444

View online: http://dx.doi.org/10.1063/1.4769444

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/101/23?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Investigation of abnormal negative threshold voltage shift under positive bias stress in input/output n-channel metal-oxide-semiconductor field-effect transistors with TiN/HfO2 structure using fast I-V measurement Appl. Phys. Lett. **104**, 113503 (2014); 10.1063/1.4868532

Investigation of extra traps measured by charge pumping technique in high voltage zone in p-channel metal-oxide-semiconductor field-effect transistors with HfO2/metal gate stacks

Appl. Phys. Lett. 102, 012106 (2013); 10.1063/1.4773914

Investigation of an anomalous hump in gate current after negative-bias temperature-instability in HfO2/metal gate p-channel metal-oxide-semiconductor field-effect transistors

Appl. Phys. Lett. 102, 012103 (2013); 10.1063/1.4773479

Analysis of an anomalous hump in gate current after dynamic negative bias stress in HfxZr1-xO2/metal gate p-channel metal-oxide-semiconductor field-effect transistors

Appl. Phys. Lett. 101, 052105 (2012); 10.1063/1.4739525

Anomalous negative bias temperature instability behavior in p -channel metal-oxide-semiconductor field-effect transistors with Hf Si O N Si O 2 gate stack

Appl. Phys. Lett. 90, 233505 (2007); 10.1063/1.2745649

## Analysis of anomalous traps measured by charge pumping technique in HfO<sub>2</sub>/metal gate n-channel metal-oxide-semiconductor field-effect transistors

Szu-Han Ho,<sup>1</sup> Ting-Chang Chang,<sup>1,2,a)</sup> Ying-shin Lu,<sup>2</sup> Wen-Hung Lo,<sup>2</sup> Ching-En Chen,<sup>1</sup> Jyun-Yu Tsai,<sup>2</sup> Hua-Mao Chen,<sup>3</sup> Chi-Wei Wu,<sup>1</sup> Hung-Ping Luo,<sup>1</sup> Guan-Ru Liu,<sup>2</sup> Tseung-Yuen Tseng,<sup>1</sup> Osbert Cheng,<sup>4</sup> Cheng-Tung Huang,<sup>4</sup> and Simon M. Sze<sup>1,2,5</sup>

<sup>1</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

(Received 20 September 2012; accepted 16 November 2012; published online 7 December 2012)

This letter investigates anomalous traps measured by charge pumping technique in high voltage in HfO<sub>2</sub>/metal gate n-channel metal-oxide-semiconductor field-effect transistors. N-V<sub>high level</sub> characteristic curves with different duty ratios indicate that the electron discharge time dominates the value of N for extra traps. By fitting ln (N ( $t_{base\ level} = 2.5 \mu s$ )-N ( $t_{base\ level}$ ))- $\Delta t_{base\ level}$  at different temperatures and computing the equation  $t = \tau_0 \exp{(\alpha_{e,SiO2} d_{SiO2} + \alpha_{e,HfO2} d_{HfO2,trap})}$ , results show that these extra traps measured by the charge pumping technique at high voltage can be attributed to high-k bulk shallow traps. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4769444]

With the scaling down of metal-oxide semiconductor field-effect transistors (MOSFETs), conventional SiO<sub>2</sub>-based dielectric is only a few atomic layers thick, causing gate current to rise, power dissipation to increase, and performance to degrade. In addition, conventional SiO<sub>2</sub>-based dielectrics have approached their physical limits. Consequently, replacing SiO<sub>2</sub>-based dielectrics with high-k based dielectrics is a valid solution to these problems. Furthermore, high-k/metal gates can be integrated with techniques such as silicon on insulator (SOI), 1-3 strained-silicon, 4,5 and multi-gate to improve device characteristics. As recommended in the International Technology Roadmap for Semiconductors, Hf-based dielectrics have been heavily studied to replace SiO<sub>2</sub>-based dielectrics in recent years.<sup>6-9</sup> However, with changes in Hf-based dielectrics, many measurement techniques must be corrected, especially charge pumping techniques. For instance, with a decrease in frequency, charge pumping current (I<sub>cp</sub>) decreases in conventional SiO<sub>2</sub>-based dielectrics since carriers have enough time to discharge from interface shallow traps. Conversely, with a decrease in frequency, I<sub>cp</sub> increases in Hf-based dielectrics since carriers have enough time to tunnel into high-k bulk traps. 10 Charge pumping techniques play an important role to inspect defect. Thus, this study mainly focuses on anomalous traps measured by the charge pumping technique at high voltage, with the devices used in this study HfO<sub>2</sub> dielectrics n-MOSFETs. The causes of the anomalous traps are explained in this

The HfO<sub>2</sub>/metal gate n-MOSFETs used in this study were fabricated by the gate first process. First, a high quality 1 nm-thick thermal oxide was grown as an interfacial layer. Second, 3 nm of HfO<sub>2</sub> dielectrics were sequentially deposited by atomic layer deposition. Third, 10 nm of  $\text{Ti}_x \text{N}_{1-x}$  was deposited by radio frequency physical vapor deposition, because metal gates can eliminate gate depletion and resist remote phonon scattering. 11,12 Next, poly-Si was deposited as a low resistance gate electrode. Finally, the dopant activation was performed at 1025 °C. The n-MOSFETs are measured by the charge pumping technique with different duty ratios at different temperatures. A pulse train with lowvoltage of  $-0.6 \,\mathrm{V}$ , high-voltage from  $0 \,\mathrm{V}$  to  $1.8 \,\mathrm{V}$ , and frequency of 200 kHz was applied on the gate terminal. Ig-Vg transfer curves were measured with the source, drain, and body terminals all grounded, with Vg given from 0 V to 1.8 V. Then through body floating (BF), source/drain floating (SDF), and source/drain/body all grounded (SDB) process, the current path and carrier polarity can be confirmed. Next, the I<sub>g</sub>-V<sub>g</sub> curve is fitted by Frenkel-Poole current and tunneling current. All experimental curves were measured using an Agilent B1500 semiconductor parameter analyzer.

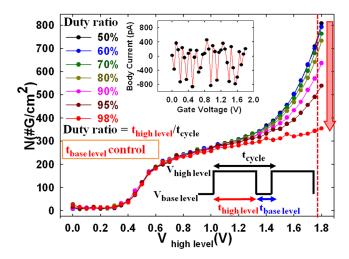

Figure 1 shows the N-V  $_{\rm high\ level}$  characteristic curves at different duty ratios. N is the number of traps, and duty  $ratio = (t_{high\ level}/t_{cycle}). \ Clearly, \ N-V_{high\ level} \ characteristic$ curves are the same in the  $V_{high level} < 1.1 \text{ V}$  with an increase in duty ratio. This information implies that interface traps detected by the charge pumping technique are not dependent on t<sub>base level</sub>. This is because the time for electrons in the interface traps to recombine with holes is very short. Hence, the numbers of interface traps measured by I<sub>cp</sub> are not sensitive to duty ratio. On the contrary, N decreases with a rise in duty ratio in  $V_{high\ level} > 1.1 \text{ V}$ . Furthermore, only interface traps can be measured with a duty ratio value of 98%. In other words, extra traps nearly disappear. The detrap time (t<sub>base level</sub>) of electron dominates the value of N such that N becomes smaller with a decrease in detrap time. This demonstrates that electrons need time to discharge. Thus, it is necessary to know the relationship between N and the detrap time ( $t_{base level}$ ) in  $V_{high level} > 1.1 \text{ V}$ . The inset of the Fig. 1

<sup>&</sup>lt;sup>2</sup>Department of Physics, National Sun Yat-Sen University, Kaohsiung 804, Taiwan

$<sup>^3</sup>$ Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsinchu, Taiwan

$<sup>^4</sup>$ Device Department, United Microelectronics Corporation, Tainan Science Park, Taiwan

Department of Electronics Engineering, Stanford University, Stanford, California 94305, USA

a)Electronic mail: tcchang@mail.phys.nsysu.edu.tw.

FIG. 1. N-V<sub>high level</sub> characteristic curves at different duty ratios by charge pumping measurement. Inset shows  $I_{sub}$ -V<sub>g</sub> curve with source, drain, and body all grounded.

shows  $I_{\text{sub}}$ - $V_g$  curves with source, drain, and body all grounded. It can be first observed that body current is small. In addition, N ( $I_{cp}$ ) is dependent on the detrap time. Hence, these results mean that N measured by the charge pumping technique is not caused by gate leakage current, but rather high-k bulk traps that have been detected, as shown in the energy band diagram of Fig. 2.

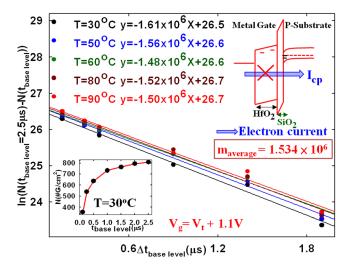

The inset of Figure 2 shows N-t<sub>baselevel</sub> curve at 30 °C, for  $V_g = V_t$  (0.67 V) + 1.1 V, as shown by the dotted red line in Fig. 1. Since N can also represent the numbers of electrons discharged from high-k bulk traps, N ( $t_{base\ level} = 2.5\mu s$ )-N ( $t_{base\ level}$ ) is the number of electrons still charged in the high-k bulk traps at  $t_{base\ level}$ , an important parameter. Figure 2 shows ln (N ( $t_{base\ level} = 2.5\mu s$ ) – N ( $t_{base\ level}$ )) –  $\Delta t_{base\ level}$  curves fitted from the inset of Figure 2.  $\Delta t_{base\ level}$  is  $t_{base\ level}$  curves from traps. Clearly, fitting these curves can be accomplished with straight lines even for different temperatures. In addition, slopes are also similar at these temperatures. The

FIG. 2. In (N ( $t_{base\ level} = 2.5\,\mu s$ ) – N ( $t_{base\ level}$ )) -  $\Delta t_{baselevel}$  curves at different temperatures at  $V_g = V_t + 1.1\,V$ . Inset shows N- $t_{baselevel}$  curve in 30 °C at  $V_g = V_t\,(0.67\,V) + 1.1\,V$ . The energy band diagram shows  $I_{cp}$  is caused by bulk trap, not gate leakage current.

discharge equation can be described by  $dQ(t)/dt = -\Delta Q(t)/dt$  $\tau_{\rm p} = -e_{\rm p}\Delta Q(t)$ ,  $\Delta Q(t) = \Delta Q(0)\exp(-e_{\rm p}t)$ , where  $e_{\rm p}$  is the escape probability and  $\tau_p$  is the average escape time. Thus, slope is indicated by  $e_p$  or  $1/\tau_p$  with  $e_p$  not dependent on temperature. Hence, ep may be the tunneling probability. The average value of the slope at different temperatures  $(m_{\text{average}})$  is  $1.534 \times 10^6$ , and  $\tau_{\rm p,average}$  is  $6.52 \times 10^{-7}$  (s). Now the value of tunneling distance can be determined by using  $\tau_{\rm p,average}$  and can verify that the traps are actually in the high-k bulk. The relationship between tunneling time and distance can be approximated by  $t = \tau_0 \exp{(\alpha_e x)}$ ,  $\alpha_e = 2(2m_e q \phi_0 / \hbar^2)^{0.5}$ , 14,15 where  $\tau_0$  is an electron tunneling characteristic time, m<sub>e</sub> is electron effective mass for SiO<sub>2</sub>, and  $q\phi_0$  is an effective tunneling barrier height. However, because electrons are tunneling through two layers, SiO<sub>2</sub> and HfO<sub>2</sub>, this equation can be described by  $t = \tau_0 \exp (\alpha_{e,SiO2} d_{SiO2} + \alpha_{e,HfO2} d_{HfO2,trap})$ ,  $\alpha_{e,SiO2} = 2(2 \,\mathrm{m_{e,SiO2}} \,\mathrm{q} \,\phi_{0,SiO2} / \hbar^2)^{0.5}$ , and  $\alpha_{e,HfO2} = 2(2 \,\mathrm{m_{e,SiO2}} \,\mathrm{d} \,\mathrm{d$  $_{\rm HfO2}q\phi_{0,\rm HfO2}/\hbar^2)^{0.5}$ , where  $\rm d_{SiO2}$  is the thickness of SiO<sub>2</sub>, d<sub>HfO2,trap</sub> is the distance from traps to interlayer between SiO<sub>2</sub> and HfO<sub>2</sub>, m<sub>e,SiO2</sub> and m<sub>e,HfO2</sub> are effective mass in  $SiO_2$  and  $HfO_2$ , respectively, and  $q\phi_{0.SiO_2}$  and  $q\phi_{0.HfO_2}$ are effective tunneling barrier height in SiO<sub>2</sub> and HfO<sub>2</sub>, respectively.  $\tau_0$ ,  $m_{e,SiO2}$  and  $m_{e,HfO2}$  can be obtained from other research. H4,16,17 Thus, only one parameter  $(\phi_{0,HfO2})$  is unknown.

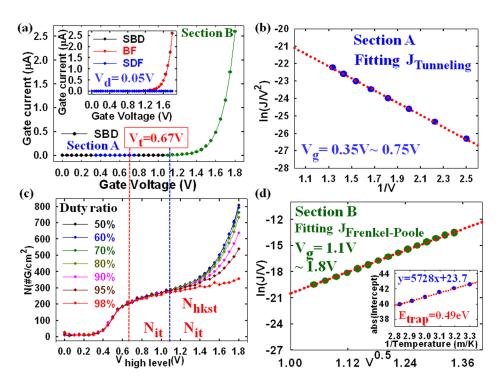

The inset in Figure 3(a) shows I<sub>g</sub>-V<sub>g</sub> characteristic curves with BF, SDF, and SDB for distinguishing gate current at 30 °C. Clearly, the  $I_g$ - $V_g$  characteristic curve in BF is similar to that in SDB, and the I<sub>g</sub>-V<sub>g</sub> characteristic curve in SDF is much smaller than either. These results indicate that electrons transfer from source/drain to the gate, rather than holes transferring from gate to body. Clearly, section A indicates the tunneling current in Fig. 3(b), from  $V_g = 0.35 \text{ V}$  to  $V_g = 0.75 \text{ V}$ , while section B is Frenkel-Poole current, shown in the inset of Fig. 3(d), from  $V_g = 1.1 \text{ V}$  to  $V_g = 1.8 \text{ V}$ .  $\varphi_{\rm B}\!=\!0.49\,{\rm eV}$  can be obtained by fitting the Frenkel-Poole mechanism in the inset in Fig. 3(d). 18-20 Figure 3(c) shows the N-V<sub>high level</sub> characteristic curves at different duty ratios. It can be observed that when  $V_g < 1.1 \text{ V}$ , N is interface traps  $(N_{it})$  only. On the contrary, when  $V_g > 1.1 \text{ V}$ , N is both highk bulk shallow traps (N<sub>hkst</sub>) and N<sub>it</sub>. A comparison of Fig. 3(c) with Fig. 3(a) shows that N is only N<sub>it</sub> when gate current is tunneling current and Frenkel-Poole current is very small. Conversely, N is both N<sub>it</sub> and N<sub>hkst</sub> when gate current is Frenkel-Poole current. This indicates that bulk traps charging electrons via the Frenkel-Poole mechanism and the traps discharging electrons through I<sub>cp</sub> may be the same. In order to confirm this theory,  $\varphi_B = \phi_{0,HfO2} = 0.49 \text{ eV}$  is substituted  $\begin{array}{ll} \text{into the equation } t=\tau_0 \text{ exp } (\alpha_{e,SiO2}d_{SiO2}+\alpha_{e,HfO2}d_{HfO2,trap}), \\ \text{with} \quad \alpha_{e,SiO2}=2(2\,m_{e,SiO2}q\varphi_{0,\,SiO2}/\hbar^2)^{0.5}, \quad \text{and} \quad \alpha_{e,HfO2} \end{array}$ =  $2(2 \, m_{e,HfO2} q \phi_{0,HfO2} / \hbar^2)^{0.5}$ , where  $m_{e, SiO2}$  is 0.95 $m_0$ ,  $m_{e,HfO2}$  is  $0.03m_0$ ,  $\tau_0 = 6.6 \times 10^{-14}$ (s),  $d_{SiO2}$  is 10 Å, and  $\phi_{0,SiO2} = 1.6 \,\text{eV} + \phi_{0,HfO2}$ . Finally, it can be acquired that d<sub>HfO2,trap</sub> is 13 Å. This is a reasonable value. While V<sub>g</sub> transits from  $V_{high\ level}$  to  $V_{base\ level}$ , electrons in the high-k bulk shallow traps near the gate and substrate discharge to gate and source/drain, respectively. Hence, only traps in the middle of the high-k bulk shallow traps can be measured by the charge pumping technique. In addition, the falling time is  $1 \times 10^{-7}$  (s), which matches the time at duty ratio of 98%,

FIG. 3. (a)  $I_g$ - $V_g$  characteristic curves with SDB. Inset shows  $I_g$ - $V_g$  characteristic curves with BF, SDF, and SDB. (b) Gate current in section A is fitted by tunneling model. (c) N- $V_{high\,level}$  characteristic curves with different duty ratios for charge pumping measurement. (d) Gate current in section B is fitted by Frenkel-Poole model.

that of  $1\times10^{-7}$  (s). This implies that electrons in the middle of the high-k bulk shallow traps have no time to tunnel to the substrate in the accumulation area. Thus, only interface traps can be measured by  $I_{cp}$  at a duty ratio value of 98%.

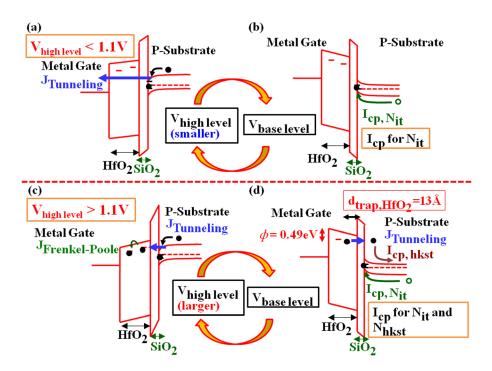

Combining the results above, the energy band diagram of the model for charge pumping measurement with anomalous traps can be acquired, as shown in Fig. 4. Figures 4(a) and 4(b) show the energy band diagram when pulses are applied to gate with the charge pumping technique at the high and base levels, respectively. When  $1.1 \text{ V} > \text{V}_{\text{high level}} > \text{V}_{\text{t}}$ , gate current is tunneling-path dominated, leading to high-k bulk shallow traps not charging electrons. Electrons merely charge to interface traps, as shown in Fig. 4(a). Subsequently, holes recombine with electrons in the interface

traps at  $V_{base\,level}$ , as shown in Fig. 4(b). Thus,  $I_{cp}$  only detects  $N_{it}$ . On the contrary, when  $V_g > 1.1\,V$ , the gate current is dominated by the Frenkel-Poole mechanism, causing high-k bulk shallow traps to charge electrons. Next, electrons charge in interface traps and high-k bulk shallow traps, as shown in Fig. 4(c). Then holes recombine with electrons in the interface traps at  $V_{base\,level}$ , and electrons discharge from high-k bulk shallow traps to the body by the tunneling mechanism. Therefore,  $I_{cp}$  measures not only interface traps but also high-k bulk shallow traps.

In summary, N-V<sub>high level</sub> characteristic curves are nearly the same in value for  $V_{high \, level} < 1.1 \, V$  with a rise in duty ratio. However, N decreases with an increase in duty ratio for  $V_{high \, level} > 1.1 \, V$ . This indicates that the electron discharge

FIG. 4. The energy band diagram of high-k/metal gate MOSFETs with charge pumping measurement (a) in  $V_{high \, level}$  and (b) in  $V_{base \, level}$ , when  $V_{high \, level} < 1.1 \, V$ . The energy band diagram of high-k/metal gate MOSFETs with charge pumping measurement (c) in  $V_{high \, level}$  and (d) in  $V_{base \, level}$ , while  $V_{high \, level} > 1.1 \, V$ .

time dominates the value of N. In addition, the values of  $e_p$  obtained by the slope of ln (N ( $t_{base\,level}=2.5\,\mu s$ )-N ( $t_{base\,level}$ ))- $\Delta t_{base\,level}$  are independent of temperature. Hence, electrons discharge from high-k bulk shallow traps via the tunneling mechanism. The distance of traps can be acquired by the equation  $t=\tau_0$  exp ( $\alpha_{e,SiO2}d_{SiO2}+\alpha_{e,HfO2}d_{HfO2,trap})$  and  $\varphi_{0,HfO2}=0.49\,eV$ , and  $\varphi_{0,HfO2}$  can be obtained from fitting the gate current with the Frenkel-Poole mechanism. From this,  $d_{HfO2,trap}$  can be calculated to be 13 Å, a reasonable value. This result is proof that traps are actually located in the high-k shallow bulk. This study shows that anomalous traps measured by the charge pumping technique in a HfO<sub>2</sub>/ metal gate at high gate voltage can be attributed to high-k bulk shallow traps.

Part of this work was performed at United Microelectronics Corporation. The work was supported by the National Science Council under Contract No. NSC 101-2120-M-110-002.

- <sup>1</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, S. C. Chen, C. T. Tsai, W. H. Lo, S. H. Ho, G. Xia, O. Cheng, and C. T. Huang, Surf. Coat. Technol. 205, 1470–1474 (2010).

- <sup>2</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, F. Y. Jian, W. H. Lo, S. H. Ho, C. E. Chen, W. L. Chung, J. M. Shih, G. Xia, O. Cheng, and C. T. Huang, IEEE Electron Device Lett. 32(7), 847–849 (2011).

- <sup>3</sup>W. H. Lo, T. C. Chang, C. H. Dai, W. L. Chung, C. E. Chen, S. H. Ho, O. Cheng, and C. T. Huang, IEEE Electron Device Lett. **33**(3), 303–305 (2012).

- <sup>4</sup>Y. J. Kuo, T. C. Chang, P. H. Yeh, S. C. Chen, C. H. Dai, C. H. Chao, T. F. Young, O. Cheng, and C. T. Huang, Thin Solid Films **517**, 1715 (2009).

- <sup>5</sup>Y. J. Kuo, T. C. Chang, C. H. Dai, S. C. Chen, J. Lu, S. H. Ho, C. H. Chao, T. F. Young, O. Cheng, and C. T. Huang, Electrochem. Solid-State Lett. 12, H32 (2009).

- <sup>6</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, S. H. Ho, T. Y. Hsieh, W. H. Lo, C. E. Chen, J. M. Shih, W. L. Chung, B. S. Dai, H. M. Chen, G. Xia, O. Cheng, and C. T. Huang, Appl. Phys. Lett. **99**, 012106 (2011).

- <sup>7</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, W. H. Lo, S. H. Ho, C. E. Chen, J. M. Shih, H. M. Chen, B. S. Dai, G. Xia, O. Cheng, and C. T. Huang, Appl. Phys. Lett. **98**, 092112 (2011).

- <sup>8</sup>C. H. Dai, T. C. Chang, A. K. Chu, Y. J. Kuo, Y. C. Hung, W. H. Lo, S. H. Ho, C. E. Chen, J. M. Shih, W. L. Chung, H. M. Chen, B. S. Dai, T. M. Tsai, G. Xia, O. Cheng, and C. T. Huang, Thin Solid Films 520, 1511 (2011).

- <sup>9</sup>W. H. Lo, T. C. Chang, J. Y. Tsai, C. H. Dai, C. E. Chen, S. H. Ho, H. M. Chen, O. Cheng, and C. T. Huang, Appl. Phys. Lett. **100**, 152102 (2012).

- <sup>10</sup>M. B. Zahid, R. Degraeve, M. Cho, L. Pantisano, D. R. Aguado, J. Van. Houdt, G. Groeseneken, and M. Jurczak, IEEE Int. Reliab. Phys. Symp. Proc. 2009, 21–25.

- <sup>11</sup>W. J. Zhu and T. P. Ma, IEEE Electron Device Lett. **25**(2), 89–91 (2004).

- <sup>12</sup>R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, and M. Metz, Electron Devices Lett. 25(6), 408–410 (2004).

- <sup>13</sup>H. Aozasa, I. Fujiwara, A. Nakamura, and Y. Komatsu, Jpn. J. Appl. Phys., Part 1 38, 1441–1447 (1999).

- <sup>14</sup>I. Lundström and C. Svensson, J. Appl. Phys. **43**, 5045 (1972).

- <sup>15</sup>T. Wang, N. K. Zous, J. L. Lai, and C. Huang, IEEE Electron Device Lett. 19(11), 411–413 (1998).

- <sup>16</sup>M. J. Chen and C. Y. Hsu, IEEE Electron Device Lett. 33(4), 468–470 (2012).

- <sup>17</sup>C. Y. Hsu, H. G. Chang, and M. J. Chen, IEEE Trans. Electron Devices 58(4), 953–959 (2011).

- <sup>18</sup>C. C. Yeh, T. P. Ma, N. Ramaswamy, N. Rocklein, D. Gealy, T. Graettinger, and K. Min, Appl. Phys. Lett. **91**, 113521 (2007).

- <sup>19</sup>K. Xiong, J. Robertson, M. C. Gibson, and S. J. Clark, Appl. Phys. Lett. 87, 183505 (2005).

- <sup>20</sup>S. H. Ho, T. C. Chang, C. W. Wu, W. H. Lo, C. E. Chen, J. Y. Tsai, H. P. Luo, T. Y. Tseng, O. Cheng, C. T. Huang, and S. M. Sze, Appl. Phys. Lett. **101**, 052105 (2012).