## The mechanisms of random trap fluctuation in metal oxide semiconductor field effect transistors

E. R. Hsieh and Steve S. Chung

Citation: Applied Physics Letters 101, 223505 (2012); doi: 10.1063/1.4768687

View online: http://dx.doi.org/10.1063/1.4768687

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/101/22?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Physical understanding of different drain-induced-barrier-lowering variations in high-k/metal gate n-channel metal-oxide-semiconductor-field-effect-transistors induced by charge trapping under normal and reverse channel hot carrier stresses

Appl. Phys. Lett. 103, 183502 (2013); 10.1063/1.4826918

Mechanism of random telegraph noise in junction leakage current of metal-oxide-semiconductor field-effect transistor

J. Appl. Phys. 111, 104513 (2012); 10.1063/1.4721658

Charge trapping induced drain-induced-barrier-lowering in HfO2/TiN p-channel metal-oxide-semiconductor-field-effect-transistors under hot carrier stress

Appl. Phys. Lett. 100, 152102 (2012); 10.1063/1.3697644

Direct observation of hot-electron energy distribution in silicon metal—oxide—semiconductor field-effect transistors Appl. Phys. Lett. **75**, 1113 (1999); 10.1063/1.124613

Extraction of metal-oxide-semiconductor field-effect-transistor interface state and trapped charge spatial distributions using a physics-based algorithm

J. Appl. Phys. 81, 1992 (1997); 10.1063/1.364055

## The mechanisms of random trap fluctuation in metal oxide semiconductor field effect transistors

E. R. Hsieh and Steve S. Chunga)

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan

(Received 18 July 2012; accepted 8 November 2012; published online 27 November 2012)

An effect, called random trap fluctuation (RTF), is proposed to study the threshold voltage ( $V_{th}$ ) fluctuation of metal oxide semiconductor field effect transistors (MOSFETs) under Fowler-Nordeim (FN) or hot carrier (HC) stress condition. Experiments have been demonstrated on n-channel MOSFETs, and it was found that not only the random dopant fluctuation (RDF) but also the stress-induced traps vary the  $V_{th}$  fluctuation. More importantly, the *stress-induced trap barrier* determines the  $V_{th}$  fluctuation. For devices after FN stress,  $V_{th}$  fluctuation is enhanced since the trap barrier regulates the transporting carriers. For devices after HC stress,  $V_{th}$  fluctuation is supressed since the carriers are backscattered into the channel by the trap barrier and fewer carriers with higher energy pass through the barrier. These results provide us a clear understanding on another source of  $V_{th}$  fluctuations in addition to the RDF as devices are further scaled. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.4768687]

Moore's law has driven complementary metal-oxide semiconductor (CMOS) devices scaling for several decades.<sup>1</sup> The phenomenon of device fluctuations becomes increasingly important. One of the most significant issues in the scaling is the threshold voltage  $(V_{th})$  fluctuation induced by the process or device structure;  $^{1-11}$  especially the discretedopant in the channel induced random dopant fluctuation (RDF),<sup>2</sup> which is the major source of V<sub>th</sub> fluctuation. It has been magnified by the scaling of device size (or area) because the electrical characteristics of the device become more and more sensitive to the number of dopants in the channel. Different configurations of dopant position will affect the value of the local V<sub>th</sub> in the channel, and the electrical characteristics will not be uniform any more while the numbers of dopants are reduced to quite a few. Recent studies have shown that the process-induced RDF, e.g., the nonuniform distribution of the generic dopants in the device channel, are required for the further scaling of device dimensions to drive the Moore's law. As a result, it has been a consensus to reduce the dopant concentrations in the device channel through the improvement of fabrication process, such as carbon co-implantation, 12 fully depleted silicon-oninsulator (FDSOI) or FinFET with undoped (lighter) channel, 13,14 which has been reported to reduce the V<sub>th</sub> fluctuation effectively. On the other hand, as far as the reliabilities are concerned, for the devices after the stress, the biastemperature instability (BTI) and random telegraph noise (RTN) may also raise the fluctuation of V<sub>th</sub> with the evolution of time, <sup>15–20</sup> as a result of the dynamic exchange of carrier charges between the traps and channel.

Nevertheless, these transient responses of the electrical characteristics for the devices after the stress have never been examined in view of the variability, and the correlations between the reliability and variability have not been reported. In this paper, we present a concept that the stress-induced

traps which caused the random trap fluctuation (RTF) can be considered as part of the fluctuations. Experimentally, for the device being stressed, the traps are generated in the oxide and at the interface with non-uniform distribution. It will affect the transport of carriers, giving rise to a similar fluctuation of the threshold voltage.  $^{21,22}$  As a consequence, we are interested in understanding the mechanisms behind this additional source of  $V_{th}$  fluctuation. In this paper, the impact of RTF on the  $V_{th}$  fluctuation, caused by the Fowler-Nordheim(FN) or hot carrier (HC) stress, has been investigated.

By applying the Pelgrom plot,<sup>23</sup> i.e.,

$$\sigma V_{th,fresh} = A_{VT} / \sqrt{LW}, \tag{1}$$

where L and W are the device length and width, respectively, the dopant fluctuation before the stress can be interpreted and quantified by the standard deviation of  $V_{th,fresh}$ , e.g.,  $\sigma V_{th,fresh}$ . The slope,  $A_{VT}$ , is an indicator of the  $V_{th,fresh}$  fluctuation. For the device after the stress, the stressed  $V_{th}$  will be shifted, attributed to the trap generation. If traps are generated in the gate dielectric or the interface randomly after the stress, it is reasonable to treat this single trap as a delta function, i.e.,

$$\sigma V_{th,shift} = q\sigma D_{trap}/C_{ox}$$

$$= q\sqrt{\int_{0}^{Tox} \Delta N_{trap}(x)\delta(x - x_{trap})dx/(LW)/C_{ox}}$$

$$\propto 1/\sqrt{LW}, \qquad (2)$$

where  $\sigma V_{th,shift}$  is the standard deviation of the threshold voltage shift after the stress.  $C_{ox}$  is the inversion capacitance; q is a constant value,  $1.6 \times 10^{-19}$  (coulomb);  $\sigma D_{trap}$  is the standard deviation of trap densities;  $\delta(x-x_{trap})$  is Dirac's delta-function, whose center is located at a trap position,  $x_{trap}$ , with value of unity or zero depending on the trap location. Now, the total variation of  $V_{th}$  after the stress,  $\sigma V_{th,stress}$ , can be considered as a root mean square of  $\sigma V_{th,shift}$  and  $\sigma V_{th,fresh}$ , e.g.,

a)schung@cc.nctu.edu.tw.

$$\sigma V_{th,stress} = \sqrt{\sigma V_{th,fresh}^2 + \sigma V_{th,shift}^2} \propto 1/\sqrt{LW},$$

(3)

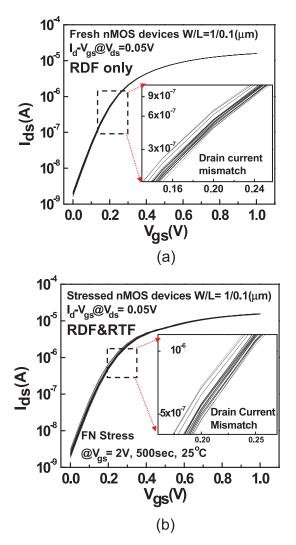

from which the actual  $\sigma V_{th,stress}$  also holds the Pelgrom's inversion square rule as does for  $\sigma V_{th,fresh}$  in Eq. (1). This can be judged from Fig. 1(b) in that the drain currents at the near threshold voltage region exhibit a parallel shift for the device after the stress.

It is well known that, after stresses, some charges trapped in defect states in the dielectric insulator of the gate exhibits a profound impact on the electric characteristics of nanoscale metal oxide semiconductor field effect transistors (MOSFETs).<sup>24</sup> These stress-induced traps will induce the electrostatic effect on the channel potential and will generate a localized barrier effectively, which will reflect the transporting carriers randomly. This trap-barrier leads to the V<sub>th</sub> fluctuation,<sup>25</sup> and we call it RTF. Experimentally, to observe the influence of RDF on the V<sub>th</sub> fluctuation, FN and HC stresses have been employed to generate different types of stress induced trap barriers. Fifty experimental samples, made by the state-of-the-art CMOS technology, are prepared for the experimental measurements. Equivalent oxide thickness (EOT) of these samples made by oxynitride (SiON) is

FIG. 1. (a) The measured drain current population on 50 sets of fresh n-MOSFETs with same dimensions and (b) the drain current population on 50 sets of n-MOSFETs with same dimensions after the FN-stress.

12 Å. Devices with various areas are measured to depict the Pelgrom plot. The threshold voltages of devices are determined by the  $G_{m,max}$  method.

By collecting 50 sets of  $I_D$ - $V_G$  curves measured at  $V_{DS} = 50 \, \text{mV}$  for fresh nMOS devices, the drain current population is shown in Fig. 1(a). In the enlarged insert of the figure, we can see the fluctuation of drain currents in response to the RDF effect, resulting in the  $V_{th}$  fluctuation before any stresses. In order to observe the stress-inudced  $V_{th}$  fluctuation, FN stress was carried out for those devices in Fig. 1(a). After the FN stress, traps were generated at Si/SiO $_2$  interface randomly. The FN stress then causes a fluctuation of the drain current such that the mismatch is significantly larger for stressed nMOS devices, compared to that of the fresh devices, as shown in Fig. 1(b). In general, the RTF will become increasingly significant since more traps will be generated as stress time evolutes.

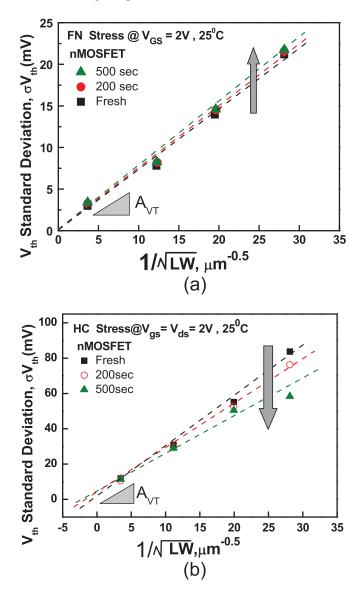

In order to understand the physics of RTF, Fig. 2(a) shows the Pelgrom plot of these nMOSFETs after FN stress

FIG. 2. The time evolution of the Pelgrom plot for n-MOSFETs (a) after FN stress and (b) after HC stress. The slope,  $A_{\rm VT}$ , indicates the degrees of  $V_{th}$  fluctuation. The  $A_{\rm VT}$  increases after the FN stress, but decreases after the HC stress. The device dimension from the left to right, W/L=0.3/0.25, 0.2/0.13, 0.1/0.065, and 0.05/0.028 ( $\mu m/\mu m$ ).

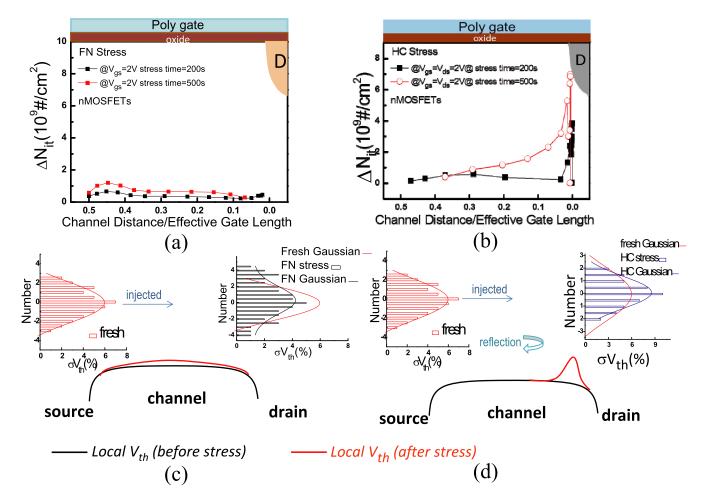

FIG. 3. The schematics to illustrate the dopant distribution, trap distribution, and the carrier transport path: (a) after the FN stress and (b) after the HC stress in n-MOSFETs.

with  $V_{GS}\!=\!2\,V$  for the fresh (0 s), 200 s and 500 s, respectively, showing the increase of the slope,  $A_{VT}$ , which is because during time evolution, random traps are increasingly generated such that the transporting carriers will go through more surface reflecting events from the interface of gate dielectric. On the other hand, we also applied HC stress to the devices with  $V_{GS}\!=\!V_{DS}\!=\!2\,V$  for the fresh (0 s), 200 s and 500 s, respectively. Surprisingly, it was observed an

abnormal behavior as compared to that from the FN stress, i.e., instead the  $A_{\rm VT}$  is decreased with increasing stress time after the HC stress, Fig. 2(b).

From the above two experimental observations, the evidence has been shown that the stress-induced  $V_{th}$  fluctuation will be dependent on the condition of electrical stress, i.e., FN or HC stress. The schematics in Fig. 3 illustrate the comparison of the generated traps between the two different

FIG. 4. The lateral profiling of interface traps,  $\Delta N_{it}$ , (a) after the FN stress and (b) after the HC stress, by the charge pumping measurement. The schematic of the fluctuation induced by the trap barriers (c) after the FN stress and (d) after the HC stress. The perturbation of carriers by the trap barrier induces a much wider distribution of the carriers (solid black line) in (c), while the perturbation of carrier by the trap barrier in (d) results in a loss of the carrier bounced back to the channel, which gives rise to a narrower distribution of the carriers (solid blue line).

stress methods. In Fig. 3(a), under the FN stress, since the applying electrical field during the stress is uniform, it can be reasonably assumed that the generated traps in the channel potential are generated more evenly and sparsely on the gate dielectric, i.e., there is a random while sparse distribution of traps throughout the whole channel. These fluctuations of stress-induced trap-barriers cause the disturbance of the carrier transport such that the V<sub>th</sub> of each transistor is raised as illustrated in Fig. 3(a), resulting in the random trap induced fluctuation. However, in Fig. 3(b), under the HC stress, since the high electrical field is located near the drain junction region, the generated traps are highly localized near the drain side. Compared to the random and sparse distribution of traps after the FN stress, traps caused by HC stress is confined only near the drain side and can be recognized as a trap barrier effectively. As carriers are traveling through this stress-induced trap barrier, those whose energies are within this barrier height will be reflected (backscattered), and only those whose energies are higher than the barrier height will reach the drain. In other words, the HC-stress induced trap barrier is an obstacle to reflect most of carriers, while just a small number of carriers can reach the drain side. As a result, the V<sub>th</sub> fluctuation is supressed after the HC stress.

To verify the above experimental observation, the interface traps profiling techniques<sup>26</sup> by the charge pumping measurement has been utilized to characterize the distribution of traps generated after FN and HC stresses. Fig. 4(a) shows the generated distributions of the interface traps ( $\Delta N_{it}$ ) after the FN stress, in which the increment of N<sub>it</sub> is more uniformly distributed along the channel except in the middle region of the channel, a little higher N<sub>it</sub> was observed. In comparison, Fig. 4(b) shows the distributions of the interface traps ( $\Delta N_{it}$ ) after the HC stress, in which a huge number of traps were generated and highly localized in the near drain region. It has been reported that the scattering events will be affected by the generated traps after the stress.<sup>27</sup> In Figs. 4(c) and 4(d), the changes in  $\sigma V_{th}$  distributions have been compared at the source and drain regions, respectively, from the experimental data of Fig. 2. In Fig. 4(c), the carriers travelling from the source with V<sub>th</sub> distribution, in Gaussian shape (solid red line), are scattered by the FN-stress-induced traps and resulted in a broader distribution of  $\sigma V_{th}$  (solid black line). In other words, after FN stress,  $\sigma V_{th}$  becomes larger. In contrast, in Fig. 4(d), the carriers travelling from the source to the drain resulted in a narrower  $\sigma V_{th}$  distribution. In other words, after the HC-stress,  $\sigma V_{th}$  becomes smaller.

In conclusion, a RTF effect is proposed to study the mechanisms of the stressed induced fluctuations of MOSFETs. Different fluctuations are observed for the devices under different stress conditions. RTF effect increases the  $V_{th}$  fluctuations when the stress generated trap are uniform in the channel; while the  $V_{th}$  fluctuation is suppressed as a result of the trap barrier with highly nonuniform localized distribution near the drain. In other words, distributions of trap-barriers determine the  $V_{th}$  fluctuation. These results provide us an additional source of  $V_{th}$  fluctuation resulting from the interface traps caused by the FN or HC stress, i.e.,  $\sigma(V_{th})^2 = \sigma(dopant)^2 + \sigma(N_{it})^2 + \sigma(others)^2$ . Furthermore, these results provide us a better understanding of

the device reliability in terms of both the process and stress induced fluctuations.

The authors would like to thank the Central R&D, UMC, Taiwan for advanced wafer fabrication support and this work was supported by the National Science Council, Taiwan, under Contract NSC-99-2221-E009-192.

- <sup>1</sup>G. Moore, Electronics **38**, 114 (1965).

- <sup>2</sup>T. Mizuno, J. Okamura, and A. Toriumi, IEEE Trans. Electron Devices 41, 2216 (1994).

- <sup>3</sup>I. D. Mayergoyz and P. Andrei, J. Appl. Phys. **90**, 3019 (2001).

- <sup>4</sup>T. Shinada, T. Kurosawa, H. Nakayama, Y. Zyu, M. Hori, and I. Ohdomari, Nanotechnology **19**, 345202 (2008).

- <sup>5</sup>M. Hori, T. Shinada, K. Taira, N. Shimamoto, T. Tanii, T. Endo, and I. Ohdomari, Nanotechnology **20**, 365205 (2009).

- <sup>6</sup>K. Inoue, F. Yano, A. Nishida, H. Takamizawa, T. Tsunomura, Y. Nagai, and M. Hasegawa, Appl. Phys. Lett. 95, 043502 (2009).

- <sup>7</sup>Y. Shimizu, H. Takamizawa, K. Inoue, T. Toyama, Y. Nagai, N. Okada, M. Kato, H. Uchida, F. Yano, T. Tsunomura, A. Nishida, and T. Mogami, Appl. Phys. Lett. **98**, 232101 (2011).

- <sup>8</sup>M. Hori, T. Shinada, Y. Ono, A. Komatsubara, K. Kumagai, T. Tanii, T. Endoh, and I. Ohdomari, Appl. Phys. Lett. **99**, 062103 (2011).

- <sup>9</sup>H. Takamizawa, Y. Shimizu, K. Inoue, T. Toyama, N. Okada, M. Kato, H. Uchida, F. Yano, A. Nishida, T. Mogami, and Y. Nagai, Appl. Phys. Lett. **99**, 133502 (2011).

- <sup>10</sup>H. Takamizawa, Y. Shimizu, K. Inoue, T. Toyama, N. Okada, M. Kato, H. Uchida, F. Yano, A. Nishida, T. Mogami, and Y. Nagai, Appl. Phys. Lett. **100**, 253504 (2012).

- <sup>11</sup>M. Hori, K. Taira, A. Komatsubara, K. Kumagai, Y. Ono, T. Tanii, T. Endoh, and T. Shinada, Appl. Phys. Lett. 101, 013503 (2012).

- <sup>12</sup>T. Tsunomura, A. Nishida, F. Yano, A. T. Putra, K. Takeuchi, S. Inaba, S. Kamohara, K. Terada, T. Mama, T. Hiramoto, and T. Mogami, VLSI Symp. Tech. Dig. 2009, 110.

- <sup>13</sup>K. J. Kuhn, Tech. Dig.—Int. Electron Devices Meet. **2007**, 471.

- <sup>14</sup>O. Weber, O. Faynot, F. Andrieu, C. B. Dufournet, F. Allain, P. Scheiblin, J. Foucher, N. Daval, D. Lafond, L. Tosti, L. Brevard, O. Rozeau, C. F. Beranger, M. Marin, F. Boeuf, D. Delprat, K. Bourdelle, B. Y. Nguyen, and S. Deleonibus, Tech. Dig.—Int. Electron Devices Meet. 2008, 245.

- <sup>15</sup>B. Kaczer, T. Grasser, Ph. J. Roussel, J. Franco, R. Degraeve, L.-A. Rabnarsson, E. Simon, G. Groeseneken, and H. Reisinger, Proc.—Int. Reliability Physics Symposium 2010, 26.

- <sup>16</sup>M. Toledano-Luque, B. Kaczer, E. Simon, P. J. Roussel, A. Veloso, T. Grasser, and G. Groeseneken, Mocroelectron. Eng. 88, 1243 (2011).

- <sup>17</sup>M. Toledano-Luque, B. Kaczer, P. J. Roussel, T. Grasser, T. Y. Hoffmann, and G. Groeseneken, Tech. Dig. VLSI Symposium 2011, 152.

- <sup>18</sup>M. Houssa, M. Aoulaiche, S. De Gendt, G. Groeseneken, M. M. Heyns, and A. Stesmans, Appl. Phys. Lett. 86, 093506 (2005).

- <sup>19</sup>A. Ghetti, C. M. Compagnoni, A. S. Spinelli, and A. Visconti, IEEE Trans. Electron Devices 56, 1746 (2009).

- <sup>20</sup>T. Grasser, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P. J. Wagner, F. Schanovsky, J. Franco, M. T. Luque, and M. Nelhiebel, IEEE Trans. Electron Devices 58, 3652 (2011).

- <sup>21</sup>P. Andricciola, H. P. Tuinhout, B. De Vries, N. A. H. Wils, A. J. Scholten, and D. B. M. Klaassen, Tech. Dig.—Int. Electron Devices Meet. 2009, 711.

- <sup>22</sup>J. R. Brews, Appl. Phys. Lett. **43**, 2306 (1972).

- <sup>23</sup>M. J. M. Pelgrom, IEEE J. Solid-State Circuit 24, 1433 (1989).

- <sup>24</sup>A. W. Krautschneider and S. Schwantes, Appl. Phys. Lett. **78**, 2790 (2001).

- <sup>25</sup> A. Asenov, R. Balasubramaniam, A. R. Brown, J. H. Davies, and S. Saini, Tech. Dig.—Int. Electron Devices Meet. 2000, 279.

- <sup>26</sup>S. S. Chung, H. J. Feng, Y. S. Hsieh, A. Liu, W. M. Linz, D. E. Chen, J. H. Ho, K. T. Huang, C. K. Yang, O. Chenp, Y. C. Sheng, D. Y. Wu, W. T. Shiau, S. C. Chien, K. Liao, and S. W. Sun, Tech. Dig.—Int. Electron Devices Meet. 2004, 477.

- <sup>27</sup>E. R. Hsieh, S. S. Chung, P. W. Liu, W. T. Chiang, C. H. Tsai, W. Y. Teng, C. I. Li, T. F. Kuo, Y. R. Wang, C. L. Yang, C. T. Tsai, and G. H. Ma, Tech. Dig.—Int. Electron Devices Meet. 2009, 780.