# Wafer-to-Wafer Alignment for Three-Dimensional Integration: A Review

Sang Hwui Lee, Kuan-Neng Chen, Member, IEEE, and James Jian-Qiang Lu, Fellow, IEEE

Abstract—This paper presents a review of the wafer-to-wafer alignment used for 3-D integration. This technology is an important manufacturing technique for advanced microelectronics and microelectromechanical systems, including 3-D integrated circuits, advanced wafer-level packaging, and microfluidics. Commercially available alignment tools provide prebonding wafer-to-wafer misalignment tolerances on the order of 0.25  $\mu$ m. However, better alignment accuracy is required for increasing demands for higher density of through-strata vias and bonded interstrata vias, whereas issues with wafer-level alignment uniformity and reliability still remain. Three-dimensional processes also affect the alignment accuracy, although the misalignment could be reduced to certain extent by process control. This paper provides a comprehensive review of current research activities over wafer-to-wafer alignment, including alignment methods, accuracy requirements, and possible misalignments and fundamental issues. Current misalignment concerns of the major bonding approaches are discussed with detailed alignment results. The fundamental issues associated with wafer alignment are addressed, such as alignment mechanisms, uniformity, reproducibility, thermal mismatch, and materials. Alternative alignment approaches are discussed, and perspectives for wafer-to-wafer alignment are [2010-0363]

Index Terms—Alignment, 3-D integration, wafer bonding, wafer-level packaging.

#### I. INTRODUCTION

THERE IS a greatly increased demand for ever high-performance high-functionality integration driven by computation, mobile, and game industries [1]–[8]. Historically, it has been satisfied by downscaling transistors following Moore's law. However, the interconnect RC delay has become a major source of circuit delays as the size of transistors gets reduced with ever increasing integration scale. Three-dimensional integration has been introduced, developed, and recognized as one of the solutions in the International Technology Roadmap for Semiconductors in reducing the length of interconnects and, furthermore, in satisfying the demand of

Manuscript received December 30, 2010; revised March 11, 2011; accepted March 26, 2011. Date of publication June 9, 2011; date of current version August 3, 2011. This work was supported in part by DARPA, in part by MARCO, and in part NYSTAR through Focus-Center NY: Rensselaer. Subject Editor D. D. Cho.

- S. H. Lee is with the Laboratory for Physical Sciences, College Park, MD 21029 USA (e-mail: leesh@ lps.umd.edu).

- K.-N. Chen is with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: knchen@mail.nctu.edu.tw).

- J. J.-Q. Lu is with the Department of Electrical, Computer, and Systems Engineering, Rensselaer Polytechnic Institute, Troy, NY 12180 USA (e-mail: lui@rpi.edu).

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JMEMS.2011.2148161

highly integrated electronic systems [1]–[24]. Whereas conventional integration connects circuits horizontally with long interconnection wires on one substrate, 3-D integration provides a new paradigm to vertically integrate various building blocks. Not only can 3-D integration shorten wires with smaller chip sizes, but also it is a new technology platform for heterogeneous integration by stacking and connecting dissimilar materials or different modules on one substrate.

Three-dimensional integration has emerged as a promising solution in driving the next generation of CMOS integration technology [1]–[20] and microelectromechanical systems (MEMS) [21]–[23]. The major processing of 3-D integration is composed of four basic unit processes: alignment, bonding, thinning, and interstrata interconnection [1]-[4]. These processes are under intensive development. For alignment, higher reliable alignment accuracy is required for higher density of through-strata vias (TSVs) and bonded interstrata vias (BISVs). For bonding, robust bonding interface and thermal management are quite challenging. For thinning, uniformity is a critical issue, whereas handling thinned wafers is difficult for some 3-D integration schemes. For interstrata interconnection, TSV technology has already been used for certain applications such as CMOS imagers, and various TSV technologies are being developed [14], [16], [19], [21], [23].

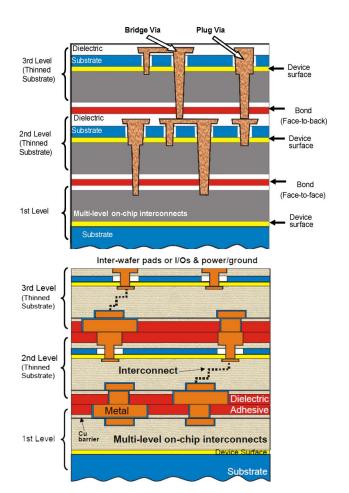

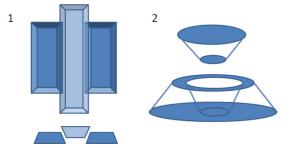

There are several 3-D technology platforms proposed [1]-[4], [10], [18], [24]-[28]. Fig. 1 schematically shows two 3-D platforms, i.e., via-first [28] and via-last [24]–[27]. They are classified by the sequence order of interstrata interconnection formation and wafer bonding. When wafer bonding is ahead of interstrata interconnection formation using TSVs, it is called "via-last." After two fully processed wafers are bonded, TSVs are formed to connect the top and bottom circuits. For the via-first 3-D process platform, a redistributed layer is formed on top of the fully processed device wafer. The redistribution layers are bonded directly face-to-face using BISVs. Depending on their applications, these platforms may use different materials, for example, for TSV formation, planarization on redistribution layer, alignment, and bonding dissimilar wafers [29], [30]. Various issues on wafer-level 3-D integration have been addressed [1]-[4], [10], [13], [31]. Among major 3-D processes, accurate alignment is essential between the bonded wafers to realize a high density of interstrata interconnects (i.e., TSVs and BISVs) and high volume throughput.

Historically, aligned wafer-to-wafer bonding was developed originally for MEMS process. Today, it is an important manufacturing technique not only for 3-D integration but also for advanced wafer-level packaging and microfluidics. The prebonding wafer-to-wafer alignment accuracy (i.e., pure

Fig. 1. Schematic representations of two major 3-D technology platforms for a monolithic 3-D hyperintegration showing (top) via-last and (bottom) via-first approaches [16]–[18].

mechanical wafer-to-wafer alignment accuracy) can be achieved on the order of 0.25  $\mu$ m using commercially available wafer-to-wafer alignment tools [30]–[35]. With continued efforts in developing wafer-to-wafer alignment tools, more precise accuracy toward the submicrometer regime of the wafer-level process can be achieved with tighter processing control [32]–[45]. However, it is difficult to improve the process-related misalignment by better alignment tools. The process-related misalignment has yet to be thoroughly studied, while it becomes more significant in MEMS and 3-D integration.

In this review paper, various alignment methods, accuracy requirements, and possible misalignment sources for MEMS and 3-D integration are addressed. Wafer-to-wafer alignment fundamentals, such as alignment mechanisms, uniformity, thermal mismatch, and materials, are discussed with detailed alignment results. Alternative alignment approaches and perspectives for wafer-to-wafer alignment are given.

#### II. REVIEW OF ALIGNMENT METHODS

Compared to conventional mask-to-wafer alignment based on photolithography, wafer-to-wafer alignment is much more complicated. It requires different alignment concepts to align two processed wafers with devices (such as CMOS transistors).

In principle, wafer-to-wafer alignment uses alignment marks on two wafers to monitor the alignment process within an align-

Fig. 2. Various types of alignment methods [21]–[28]. (a) Optical microscopy for transparent substrates. (b) Optical microscopy using through-wafer holes in combination. (c) IR transmission microscopy for IR transparent substrates. (d) Optical microscopy using front-to-backside alignment marks. (e) Intersubstrate microscopy for face-to-face wafer alignment. (f) SmartView alignment method. (g) 3DAlign method.

ment tool. Once two wafers are aligned, they are temporarily brought into contact; at this stage, for optical or infrared (IR) transparent wafer, the misalignment can be inspected by imaging overlaid marks. The aligned wafers are usually transferred to a bond tool for wafer bonding. The misalignment can be inspected right after bonding or after substrate thinning by optical microscopy images of overlaid marks or by cross-sectional scanning electron microscopy (SEM) images of overlaid marks using focused-ion-beam (FIB) technique.

Various alignment techniques [32]–[45] have been introduced for wafer-to-wafer alignment, as shown in Fig. 2: 1) using the method for transparent substrates; 2) using through-wafer holes in combination with optical microscopy; 3) using IR transmission microscopy; 4) using front-to-backside alignment marks; 5) using intersubstrate microscopy [35], [36]; 6) using the SmartView alignment method [32], [33], [37]–[40]; and 7) using the 3DAlign method [34], [41]–[43].

# A. Transparent Substrate

Similar to conventional mask alignment, optical microscope can view the alignment marks on the wafers through a transparent wafer (such as glass or some compound semiconductor wafers). Two wafers with alignment marks in a face-to-face fashion are aligned by moving the wafer stages until the alignment marks are overlapped. Alignment errors of  $\pm 5~\mu m$  are not uncommon using this approach.

#### B. Through-Wafer Holes

As shown in Fig. 2(b), the alignment marks on one of the aligning wafers can be seen through the holes drilled or etched on the other. The dimension and position of the through-holes are very critical in this approach since the wafer with holes does not have particular alignment marks. It is very difficult for drilling and etching to reach the precise micrometer-level accuracy of the via-hole dimensions through the wafer substrate (e.g.,  $\sim$ 725- $\mu$ m thickness for 200-mm silicon wafers). This technique is hardly to reach micrometer-level wafer-to-wafer alignment.

# C. IR Transmission Microscopy

Instead of a visible light, an IR light is placed on one side of the wafer (opposite to the optical microscope), as shown in Fig. 2(c). Silicon wafers can be aligned since silicon is transparent to IR light. However, it is limited to the silicon wafers with polished double side surfaces. Alignment errors could be as small as  $\pm 1~\mu m$  with this approach. However, the view is distorted by nontransparency of metal or heavily doped silicon layer.

# D. Backside Alignment With Digitalized Image

Alignment marks are placed on the frontside (bond) of the first wafer and on the backside (counter-bond) of the second wafer. Similar to a mask aligner, alignment marks on the first wafer—face down toward the bottom microscope—is captured and stored as a digitalized image. The second wafer—bond face upward and alignment mark downward—is moved in between the first wafer and the microscope. The alignment marks on the backside of the second wafer are viewed and aligned with the stored image of the alignment mark on the first wafer. An alignment tolerance of  $\pm 5~\mu \mathrm{m}$  can be reached. It is critical to register well the alignment marks on the backside of the second wafer.

# E. SmartView Alignment Method

Two pairs of microscopes (one pair on the "left" side and the other on the "right" side of the aligning wafers) are placed outside of the top and bottom wafers. The aligning wafers are placed "face-to-face" with a gap of less than 100  $\mu$ m and vacuum-sucked on the top and bottom wafer stages, respectively. The two wafer stages can be moved back and forth horizontally. After the pair of top and bottom microscopes are aligned with each other (i.e., calibrated), the bottom wafer stage is moved inbetween the pairs of microscopes; the marks in the top microscopes are aligned to the alignment marks on the bottom wafer. The bottom wafer position is stored, and the bottom stage is retreated. The top wafer stage is moved to the position against the bottom microscopes. The alignment marks on the top wafer are then aligned to the bottom microscopes. The bottom wafer stage is moved back to its stored alignment position. Finally, the two aligned wafers are vertically moved to contact each other and are clamped to hold the alignment for wafer bonding. Misalignment tolerances can be achieved on the order of 0.25  $\mu$ m in this method [32], [33], [36].

# F. 3DAlign Method

It comprises two microscope sets and a modified wafer table. For double side aligning, one set views directly down to the frontside of a wafer and another set views through a special mirror like a modified periscope to the bottom side, as shown in Fig. 2(g). To align a wafer pair, the second microscope set views the bottom side of the second wafer. Two viewed images are overlaid and aligned. A submicrometer misalignment tolerance was demonstrated with this method [34], [42], [43].

#### III. ALIGNMENT CONSIDERATION ON 3-D PLATFORMS

Unlike conventional mask alignment in photolithography, the addition of a fully processed wafer or a handling glass wafer makes alignment more complicated. The alignment approaches described in Section II must be considered with each 3-D platform. Alignment marks and bond surface should be designed in advance for a given 3-D platform. Moreover, wafer bonding may cause further misalignment. Two alignment approaches possible for 3-D platforms [31], [41] are considered here in this paper: 1) face-to-face and 2) face-to-back.

#### A. Face-to-Face

At the bonding interface, the alignment marks on one wafer face the ones on the other wafer. In this case, alignment marks can be fabricated on the layer of top global interconnects. The alignment marks can also be fabricated on the CMOS layer if the frontside of the wafer is bonded on a temporary handle wafer (silicon or glass) and if the bulk silicon substrate of this wafer is removed. It is possible to view the aligning marks in a conventional mask alignment microscope only if a transparent wafer substrate is used (such as glass wafer using visible light or silicon wafer using IR). In this case, the alignment marks can be fabricated on either the layer of top global interconnects or the CMOS layer. With a nontransparent silicon substrate, there are a few ways to overlay the marks in this aligning method. SmartView, IR microscope, and intermicroscope are practically used for the face-to-face wafer alignment.

# B. Face-to-Back

The alignment marks on both bonding wafers face toward a microscope, which means that the alignment marks on one wafer do not face those on the other wafer at the bonding interface. The backside alignment with digitalized image (as discussed in Section II-D) can be used with an optical microscope. With this approach, it is difficult to inspect the postbonding alignment accuracy with IR since the alignment marks on both wafers are not on the same focal plane. The face-to-face alignment method can also be used if alignment marks are fabricated on the backside of one wafer, although it is quite challenging to realize the alignment marks that are well aligned to the circuits on the wafer frontside.

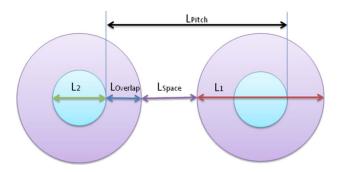

Fig. 3. Schematic of the bonding pads based on the via design rule.  $L_1$  and  $L_2$  are the diameters of the bonding pads on the first and second wafers,  $L_{\rm Overlap}$  is the minimum overlay between the bonding pads on the first and second wafers,  $L_{\rm Pitch}$  is the edge-to-edge distance of the bonding pads on the second wafer, and  $L_{\rm Space}$  is the distance between two bonding pads on the first wafer.

In all of the 3-D platforms, after alignment, two aligned wafers may experience further thermal/mechanical processes such as bonding, thinning (grinding and polishing), further interconnect or redistribution layer formation, TSV formation, etc. These thermal/mechanical processes may affect the alignment accuracy obtained during the room-temperature wafer-to-wafer alignment. Therefore, those processes have to be evaluated and controlled for 3-D integration.

# IV. ALIGNMENT IMPACT ON INTERCONNECT VIA DENSITY

Accurate alignment is a critical factor for high interstrata interconnection via density and multilevel stacking. Interstrata interconnection via density in wafer-level 3-D approach is directly related to the performance of the wafer-level alignment tool and the process control, which determines via pitch and size. The minimum pitch and overlap via size can be defined as follows [46]:

$$L_{\text{Pitch}} = L_{\text{Space}} + 2 \cdot L_{\text{Overlap}} + L_2$$

(1)

$$L_{\text{Overlap}} = M_{\text{Mean}} + 3 \cdot M_{\text{Sdv}} + M_{\text{Run-out}}$$

(2)

where  $L_2$  is the diameter of the bonding pads (as shown in Fig. 3),  $L_{Overlap}$  is the minimum overlay,  $L_{\rm Pitch}$  is the edge-to-edge distance of the bonding pads on the second wafer,  $L_{\rm Space}$  is the distance between two bonding pads on the first wafer,  $M_{\rm Mean}$  is the mean of the wafer-to-wafer misalignment,  $M_{\rm Sdv}$  is the standard deviation of the wafer-to-wafer misalignment, and  $M_{\rm Run-out}$  is the maximum run-out misalignment. The maximum run-out misalignment may be controlled as discussed in the following sections.

For instance, with the current alignment technology, let us consider that both the mean and the standard deviation are 1  $\mu$ m, and the maximum misalignment within a wafer with the best wafer bow control is also 1  $\mu$ m. For the minimum landing pad size of 5  $\mu$ m, the pitch size would be calculated as 12  $\mu$ m if both via size and line spacing are 1  $\mu$ m. The number of interwafer interconnects in an area of 10 mm² could be  $\sim 2 \times 10^4$  when the interstrata interconnection area ratio (i.e., area of interstrata interconnects/die area) is 1% [9]. However, if the mean and standard deviation are 0.25 and 0.1  $\mu$ m, the pitch size and the number of interstrata interconnects in the same area (10 mm²) could be 5.1  $\mu$ m and  $\sim 6 \times 10^4$ . The wafer-to-

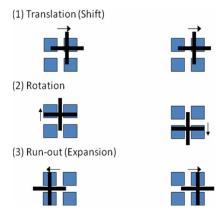

Fig. 4. Schematic of various misalignments. (a) Translation (shift). (b) Rotation. (c) Run-out (expansion).

wafer alignment accuracy and the maximum misalignment with wafer are key factors affecting the pitch size and the number of interstrata interconnects, whereas the via size is dictated by the technology of via formation. As a comparison, a pitch size of 0.156  $\mu$ m is projected for minimum global wiring pitch of microprocessor unit, and a pitch size of 0.1  $\mu$ m is projected for Metal 1 wiring pitch of DRAM interconnect [19].

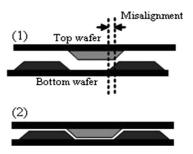

#### V. MISALIGNMENT CATEGORY

Misalignments, such as translation (shift), rotation, and runout (expansion) misalignment, have been studied in 2-D lithography in the form of mask-to-wafer alignment and in 3-D integration in the form of wafer-to-wafer alignment [38], [47], as shown in Fig. 4. Translation and rotation errors are steadily minimized by continued developments of commercial bond alignment tools, while run-out misalignment is still one of the most challenging issues in wafer-level 3-D integration because bonding/thinning processes inhibit maintaining the flatness of fully processed wafers in each layer-stacking process [47], [48]. Prior to wafer alignment and bonding, fully processed wafer may have certain compress or tensile stress on the device layer. Elevated bonding or debonding temperature enlarges the stress to induce wafer bow/warpage and nonlinear distortion [49]. Backside thinning makes internal shear stress dominated to the thin wafer, while a thick silicon substrate keeps the wafer flatness from the stress [49].

# A. Thermal-Induced Misalignment

Thermal management has been a big hurdle for high-performance integrated circuit (IC) processing and could be even more important in multilevel 3-D integration [47]–[75]. Thermal-induced wafer distortion and mismatched thermal expansion of the wafers are the two major concerns in wafer-to-wafer alignment. For 3-D processing, the thermal expansion (run-out) error can occur in a wafer bonding/debonding process. It is critical to use materials with matched coefficients of thermal expansion (CTEs) and to control the temperature profile of any thermal processes. Table I shows the CTEs for the materials typically used in these 3-D integration platforms. As the CTEs of copper and BCB are much bigger than that of silicon, it is very delicate to integrate 3-D ICs that include

360\*

|                                | CTE<br>(ppm/°C) | Melting point (°C) | Young's<br>modulus<br>(GPa) |

|--------------------------------|-----------------|--------------------|-----------------------------|

| Si                             | 2.5             | 1414               | 185                         |

| SiO <sub>2</sub>               | 0.42            | 1600-1725          | 75                          |

| Si <sub>3</sub> N <sub>4</sub> | 2.9             | 1900               | 210                         |

| GaAs                           | 5.6             | 1510               | 86                          |

| InP                            | 4.6             | 1330               | 61                          |

| Sapphire                       | 8.4             | 2040               | 345                         |

| Pyrex 7740                     | 3.2             | 820                | 72                          |

| Quartz                         | 0.6             | 1670               | 63                          |

| Cu                             | 16.8            | 1085               | 110-128                     |

| Au                             | 14.2            | 1065               | 72                          |

| Al                             | 26.5            | 660                | 70                          |

| In                             | 35              | 156                | 12.74                       |

| Sn                             | 25              | 232                | 50                          |

| BCB                            | 32              | 350*               | 8.5                         |

$\label{thm:table} TABLE\ \ I$  CTEs for the Materials Commonly Used in Some 3-D Platforms

Polyimide 2611

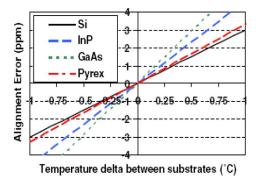

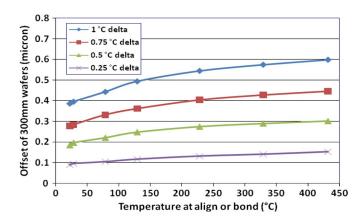

Fig. 5. Thermal expansion errors due to temperature differentials between bonded substrates [47].

copper or BCB. During wafer bonding, the temperatures on the two wafers that are to be bonded can be different because the aligned top and bottom wafers are usually heated separately by top and bottom hotplates. This temperature difference on the two wafers can result in different thermal expansions between these two wafers, leading to further misalignment (shown in Fig. 5). It is important to keep the bonding temperatures on the bond pair matched to avoid different thermal expansions.

It is also important to make sure that the stress of the device layer is released enough, thus reducing any wafer bow, which can also result in misalignment. Moreover, glass and silicon substrates are often used as transfer carriers. To minimize the residual stress from previous IC process, a CTE-matched low-stress polymer adhesive is required. In wafer bonding of dissimilar materials, the thermal expansion difference on the bonding pair would be significant; therefore, it is very difficult to keep the alignment unless the bonding process is done at room temperature or the bonding temperature profiles on the top and bottom wafers are so controlled to compensate the CTE mismatch.

# B. Wafer Stress and Nonlinear Wafer Distortion

Wafer stress and localized wafer thickness variation induce wafer warpage/bow and nonlinear wafer distortion. Backside

Fig. 6. Optical microscope images, taken at five spots on an aligned wafer pair, showing wafer-level "run-out" misalignments: 0.56- and 0.62- $\mu$ m errors in 43.6-mm gap of the x- and y-directions from the wafer center for oxide fusion bonding [48].

wafer thinning such as chemical–mechanical polishing (CMP), grinding, and lapping makes internal residual shear stress revealed to the thinned wafer so that the wafer flatness is distorted nonlinearly. All of these types of nonlinear wafer distortions may cause further misalignments, as shown in Figs. 6 and 12 and Table IV. The localized thickness variation from nonuniform deposition or thinning can also induce the random directional expansion of alignment offsets in the x- and y-directions [47], [48].

# VI. CASE STUDY OF THERMAL-INDUCED MISALIGNMENT

The correlation of misalignment and thermal management is discussed for four cases: 1) oxide-to-oxide bonding [49]–[52]; 2) metal bonding [53]–[65]; 3) adhesive bonding [66]–[71]; and 4) anodic bonding in MEMS application [72]–[75]. The postbonding thermal misalignment according to various wafer bonding methods for MEMS and 3-D integration and packaging applications is summarized in Table II. These following case studies show how the thermal mismatch affects alignment accuracy during 3-D processing.

# A. Oxide-Oxide Bonding

This case is for a SOI-based 3-D assembly with the layer-transfer technology and oxide-to-oxide bonding [49], [50]. The device layer of a bonding wafer is transferred to a glass handling wafer by bonding and removing the silicon substrate. The n- and p-FET device layers are bonded together using PECVD oxide layers, and they are connected through interwafer through silicon vias (i.e., TSVs) [50]. A low-temperature PECVD oxide of 500 nm is deposited to both n- and p-FET wafer surfaces. Oxide layers are annealed at 300 °C and are smoothed using a CMP processing. Face-to-face alignment and bonding at room temperature were performed and annealed at 400 °C [49]. Whereas this transparency of a glass wafer provides good optical alignment accuracy, the CTE of the thin top layer with glass substrate does not match that of the bottom Si wafer. Upon the best alignment accuracy in the center area,

<sup>\*</sup> Glass transition temperature

TABLE II

POSTBONDING ALIGNMENT ACCURACY IN VARIOUS BONDING

APPROACHES [45], [50], [57], [61], [64], [69], [71]

|                                    | Bonding          | Alignment accuracy |  |

|------------------------------------|------------------|--------------------|--|

| Bonding method                     | temperature (°C) | μm)                |  |

| Silicon direct                     | •                | . ,                |  |

| Si-Si                              | 300              | 0.2                |  |

| SiO <sub>2</sub> -SiO <sub>2</sub> | 400              | 0.5                |  |

| GaAs, InP                          | 400              | 0.5                |  |

| Metal compress                     |                  |                    |  |

| Cu-Cu                              | 400              | 0.5                |  |

| Au-Au                              | 400              | 0.5                |  |

| Metal Euctetic                     |                  |                    |  |

| An-Sn                              | 280              | 2                  |  |

| Au-Si                              | 363              | 2                  |  |

| Cu-Sn                              | 231              | 2                  |  |

| Polymer                            |                  |                    |  |

| BCB                                | 250              | 0.5                |  |

| Polyimide                          | 300              | 2                  |  |

| SU-8                               | 200              | 5                  |  |

| PMMA                               | 200              | 0.5                |  |

| Anodic                             | _                |                    |  |

| Pyrex 7740                         | 180-500          | 2-5                |  |

TABLE III

MISALIGNMENT RESULTS AFTER BONDING WITH

DIFFERENT PROFILES [53]

| Bonding profile     | A   | В   | С | D   |

|---------------------|-----|-----|---|-----|

| Misalignment x (μm) | 2   | 0.5 | 2 | 0.5 |

| Misalignment y (μm) | 1.5 | 0.5 | 1 | 0.5 |

the alignment errors become larger toward the edges (so called "run-out"), as shown in Fig. 6. This run-out error due to thermal expansion can be analyzed by the study of wafer bow in the layer-transfer process of SOI-based 3-D assembly. The glass handle wafer is delaminated by a laser ablation technique. Fig. 6 shows the optical microscope images of wafer-level "run-out" misalignments: a 0.6- $\mu$ m error in 43.6-mm gaps from the center. Misalignment is measured over the 200-mm wafer substrate in postalignment inspection before annealing. This run-out alignment error is caused mainly by the thermal stress of laminating the device layer to a glass handle wafer.

The alignment average (in micrometer), standard deviation (in micrometer), and run-out rate (in micrometer per millimeter) are measured as 0.16/0.26/0.0128 and 0.02/0.10/0.0156 for the x- and y-directions, respectively. Here, the run-out rate (in micrometer per millimeter) is defined as a misalignment error (in micrometer) over the distance (in millimeter) from the center of the wafer. The run-out error (expansion error), even after annealing, is 0.56 and 0.62  $\mu$ m in the x- and y-axes on the die in the distance of 90 mm from the center, as shown in Fig. 6. These run-out errors may be explained as follows: 1) the large wafer bows at the steps of postlamination and postbonding film preparation caused the expansion mismatch between the glass and silicon device layers along with the large glass wafer bow: 2) during the expansion mismatch, a large residual stress was built on a silicon device layer from the previous steps; 3) thus, the patterns in the thin device layer are stretched out during the wafer bow correction step (preoxide bonding). Most of the bonding/debonding process involves inevitable thermal process. As an example of device layer expansion over a glass handle wafer during layer-transfer process regardless of glass

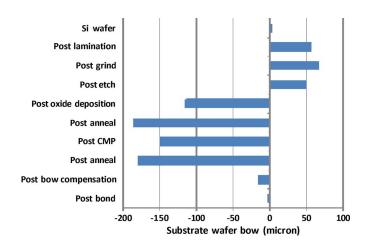

Fig. 7. Bow measurement at various process steps of the layer-transfer process. Bow compensation applied after the postanneal step [47], [50].

wafer bow correction, Fig. 7 shows the wafer bow data at each layer-transfer process step in the oxide bonding even before the aligning and bonding steps. However, the measured large runout after alignment means that the thermal expansion mismatch could not be corrected by bow correction of a glass handle wafer.

# B. Metal Bonding

1) Thermal Compression Copper-to-Copper Bonding: The in-wafer thermal expansion mismatch between the copper via pads and the silicon substrate is discussed with the thermal expansion and the mechanical motion such as down-force and clamping [53]–[59]. It has been reported that copper-to-copper bonding surface can slide out by shear force of large down-force during bonding [54]. The bonding parameters such as down-force, bonding temperature, temperature ramping rate, and bonding time are sensitive factors in retaining the alignment during bonding. Experimental studies showed that bonding-induced misalignment can be improved by controlling the bonding parameters.

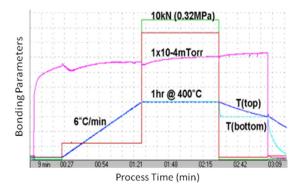

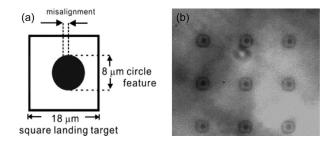

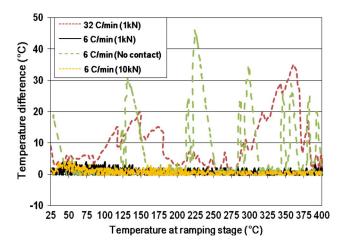

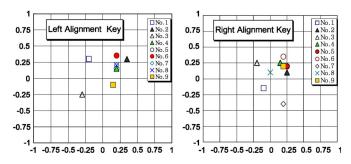

In one study [53], standard Cu interconnect damascene patterns were fabricated on both wafers, and then, an oxide layer was recessed by 40 nm lower than the Cu surface [58]. Cu round vias of  $8\mu m$  were fabricated on the upper wafers, whereas 18- $\mu$ m square landing pads were fabricated for the bottom wafers. In all bonding experiments, the bonding was conducted at 400 °C for 1 h, and no down-force was applied during the cooling cycle with a ~2-°C/min cooling rate, as shown in Fig. 8. The wafer-to-wafer alignment accuracy is measured using IR microscopy, looking at the alignment keys at the left and right wafer edges with a resolution in the range of 0.5  $\mu$ m. Typically, Cu-to-Cu blank wafer bonding can be obtained with a high down-force (10 kN) at 350 °C-400 °C for 1 h, but patterned copper bonding becomes more complicated with thermal mismatch between the copper film and the silicon substrate. The following four different bonding profiles were further investigated based on the profile shown in Fig. 8:

Profile A: a small prebonding force of 1 kN, a fast ramping of 32 °C/min, and a full bonding force of 10 kN at 400 °C for 1 h;

Fig. 8. Bonding process profile recorded. From the top in the middle area, (first line) down-force (10 kN), (second line) down-pressure, (third line) chamber pressure, and (fourth line) bonding temperature (top and bottom chucks) [48].

Fig. 9. (a) Schematic diagram of  $8-\mu m$  Cu interconnects (with a pitch-to-diameter ratio of 10:1) bonded to  $18-\mu m$  square landing pads. (b) IR image showing typical misalignment results after clamping and bonding for the same interconnect pattern geometry [53].

Profile B: a small prebonding force of 1 kN, a slow ramping of 6 °C/min, and a full bonding force of 10 kN at 400 °C for 1 h;

Profile C: no prebonding force, a slow ramping of 6°C/min, and a full bonding force of 10 kN at 400 °C for 1 h;

Profile D: a full prebonding force of 10 kN and a slow ramping of 6  $^{\circ}$ C/min, keeping the full bonding force at 400  $^{\circ}$ C for 1 h.

Fig. 9 shows the following: 1) a schematic diagram of an  $8-\mu m$  Cu via bonded to an  $18-\mu m$  square landing pad and 2) an IR image showing typical misalignment results after bonding. Table III shows the misalignment data for each bonding profile. Less misalignment error (within 0.5  $\mu$ m) is obtained for profiles B and D, indicating that thermal control is an important factor to copper bonding because intimate wafer contact with prebonding force and slow ramping rate ensure that the temperatures on the top and bottom wafers stay closely the same during temperature ramping-up. To emphasize the importance of the thermal control, Fig. 10 shows wafer offsets (possible misalignment between two wafers) versus wafer temperature for several temperature differences between the wafers. As shown, a 1° temperature variation between wafers at 400 °C could cause a 0.6- $\mu$ m offset of the 300-mm wafer ( $\sim$ 0.4  $\mu$ m even at room temperature) [57].

Fig. 11 shows the temperature differences between the top and bottom wafers for each bonding profile. For profiles B and D, with a slow ramping rate (6  $^{\circ}$ C/min), the temperature difference fluctuates within 5  $^{\circ}$ C. However, the temperature difference fluctuates up to 35  $^{\circ}$ C (varying slowly) for profile A

Fig. 10. Wafer offset versus temperature difference between wafers [57].

Fig. 11. Temperature difference and fluctuation during the ramping step. Fast ramping rate with 1-kN down-force, slow ramping rate with 1-kN down-force, slow ramping rate with no intimate contact between wafers, and slow ramping with 10-kN down-force [48].

(fast ramping and wafers in contact) and up to 45 °C (varying fast and frequently) for profile C (no intimate contact between wafers). A slow ramping rate (6 °C/min) avoids the large mismatch of the thermal expansions between wafers by keeping the temperature difference between wafers within 2°, as designed by the bonding tool. A fast ramping rate (32 °C/min) resulted in heating wafers with high overshoots due to a slow response of the heating to the thermal sensor's feedback. For profile C (no intimate contact between wafers), there is a large misalignment even at a low ramping rate, indicating that intimate contact between two wafers is essential to equalize the temperature of the wafers. The wafer contact step should be ahead of this temperature ramping. A 1-kN down-force should be enough to enable the intimate contact. To compare profile B with profile D, profile B is preferred because a large down-force could cause an undesired shear force during the temperature ramping [54].

Moreover, a large temperature difference with profiles A (fast ramping) and C (no intimate contact) could also cause a nonlinear and irregular expansion of the Cu/oxide damascene layer over Si substrate. This expansion may lead to possible nonlinear wafer warpage or bow along with surface morphology; thus, it should be avoided.

2) Eutectic Bonding: In MEMS and device packaging, eutectic bonding is widely used for hermetic seals and flip chip

bonding [60]–[65]. At eutectic point, a solid phase of alloy is directly transformed to a liquid phase. Using this soft bonding interface, metal alloy bonding is fulfilled without a high downforce. As an example of eutectic bonding, Au-Sn alloy has a composition ratio of Sn (20 wt%) and Au (80 wt%), and its eutectic point is 280 °C. The eutectic bonding was made under a down-pressure of 5000 mbar at 300 °C for 10 min. The liquid phase of alloys at eutectic point induces self-aligning to reduce the shearing force [60], [64]. However, since various metal alloys are bonded generally below 400 °C, a soft interface is able to provide a chance to heated wafer bond pair to be bowed or nonuniformly distorted. It causes a large thermal misalignment. A process control such as ramping time and a proper sequence of down-force and bonding temperature are required. Postbonding alignment accuracies of  $\sim$ 2  $\mu$ m can be expected [60], [65].

# C. Adhesive Wafer Bonding

- 1) Permanent Bonding: Adhesive wafer bonding is a simple robust bonding process for 3-D integration and packaging due to the ductile and thermal deformable properties of polymer adhesives [66]–[69]. However, improper polymer or bonding processes can lead to large misalignment. Thermal expansion mismatch in adhesive bonding is more significant than in metal bonding. The thermal-induced misalignment can be affected by polymer thickness variation, reflow, and shear force due to the nature of the polymer (low viscosity at certain temperature). For instance, a little shear force may cause a large misalignment for a bonding polymer with very low viscosity (at the reflow temperature). Benzocyclobutene (BCB) has been verified as a very promising polymer for adhesive dielectric bonding because it is a thermo-set polymer without outgassing and has a high viscosity provided by cross-linking after curing. It was reported that a small thermal-induced misalignment (on the order of 1  $\mu$ m) can be achieved using a partially cured BCB (with a high viscosity) in adhesive wafer bonding [64].

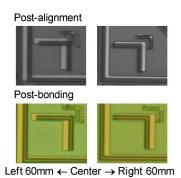

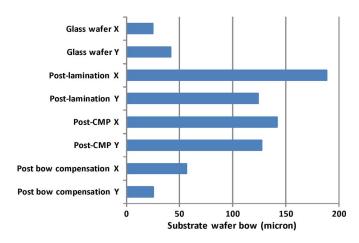

- 2) Temporary Bonding: Adhesive wafer bonding is also used for temporary handling support of the layer-transfer process [48], [70], [71]. Fig. 12 shows the change of alignment accuracy after wafer bonding, and Table IV shows the misalignment data over a 200-mm wafer substrate in postalignment inspection before annealing for polymer-to-polymer bonding [48]. Expansion errors occur even before the aligning step. The alignment average (in micrometer), standard deviation (in micrometer), and run-out rate (in micrometer per millimeter) for this polymer bonding are measured as -1.2/1.0/0.055 and 0.4/2.6/0.058 for the x- and y-directions, respectively. These misalignment data explain that a thick polymer bonding can induce severe misalignment. Fig. 13 summarizes the wafer bow data at each layer-transfer process step in this polymer bonding even before the aligning and bonding steps. This is a typical example of device layer expansion over a glass handle wafer during the layer-transfer process, regardless of glass wafer bow correction. It shows a large wafer bow (up to 200  $\mu$ m) during postlamination and postbonding film preparation. The wafer bow of prebonding wafers is much improved to  $\sim 50 \ \mu m$  by depositing a bow correction layer on the backside of the glass

Fig. 12. Alignment changes before and after bonding [48].

TABLE IV

MISALIGNMENT DATA AND WAFER-LEVEL ALIGNMENT YIELD [48]

| Bonding<br>Type | Shift x<br>(µm) | Shift y<br>(µm) | Rotation (radian) | Run-out x<br>(µm/mm) | Run-out y<br>(µm/mm) |

|-----------------|-----------------|-----------------|-------------------|----------------------|----------------------|

| Center          | 0.1             | 0.6             | -                 | -                    | -                    |

| Ave./Sigma      | -1.2/1.0        | 0.4/2.6         | -44.2             | 0.055                | 0.058                |

Fig. 13. Wafer bow measurement at each process step for temporary adhesive bonding [48].

wafer. However, the run-out errors with this polymer bonding are very large, i.e., 4.95 and 5.22  $\mu m$  in the x- and y-axis directions on the die in the distance of 90 mm from the center, as shown in Fig. 14. It means that thermal expansion mismatch could not be corrected by bow correction of a glass handle wafer.

# D. Anodic Wafer Bonding

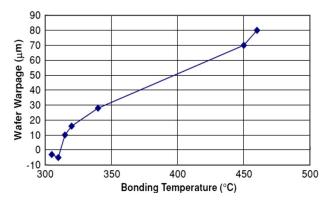

MEMS devices, including moving parts such as vibratory gyroscope and accelerometers, often suffer from misaligned wafer bonding and thermal stressed anodic bonding because the sensitive mechanical change is essential to the MEMS devices [72]–[75]. For example, in the decoupled vibratory gyroscope [72], resonators oscillating at their natural resonant frequency are very sensitive to the small deformation of the resonator induced by fabrication errors and/or thermal stress. Anodic bonding is the major process step causing thermal expansion mismatch in the fabrication of the gyroscope because the bonding is conducted at a temperature of 460 °C and at a voltage of 450 V. This high-temperature process brings out large wafer

Fig. 14. Wafer-level misalignments. Optical images taken at nine spots on the wafer along the x- and y-directions, showing misalignments due to the process of layer-transfer using polymer adhesive. 4.95- and 5.22- $\mu$ m errors in 90-mm gap of the x- and y-directions for polymer bonding [45].

Fig. 15. Wafer warpage of the SOI wafer bonded to glass with increasing bonding temperature [72].

bowing, degrading the device performance. Fig. 15 shows the bonding temperature dependence of wafer warpage. The wafer bowing increases up to 80  $\mu m$  as the bonding temperature elevates to 460 °C, while the bowing is 10  $\mu m$  at 330 °C. Alignment accuracy can be achieved within  $\pm 5~\mu m$  in the bow of 10  $\mu m$  of silicon/glass anodic bonding. For a certain material such as 7070 glass, it induces bowing itself when bonding temperature reaches the strain point. The bow is in the opposite direction to the bow due to thermal expansion mismatch. This is used for bow control [75].

# VII. TECHNIQUES TO ALIGNMENT ACCURACY IMPROVEMENT

In order to reach or keep submicrometer alignment accuracy, better alignment tools are obviously required. Some possible solutions [5], [76]–[90] have been developed to prevent or reduce large misalignment, including thermally distorted misalignment in terms of process control.

# A. Surface Heating

A temperature control unit can be employed to the alignment process. For example, if the top and bottom chucks are

Fig. 16. Schematic drawing for a conceptual mechanical interlocking mechanism. (a) Tapered surfaces slide in the misalignment range. (b) Key structures are interlocked [75].

heated separately, the stressed wafer warpage could be relaxed temporarily before in-contact. Local or global surface heating compensates the different wafer warpage of two aligning wafers correcting the expansion offset [5].

# B. Mechanical Interlocking

- 1) Anisotropic Etched Silicon Structure in MEMS: Using the anisotropic (KOH) etching of silicon, the concept of mating pyramid (convex) and groove (concave) elements can be used to improve the wafer alignment accuracy down to a few micrometers and better as a passive mechanical wafer alignment technique by sliding to mate and locking the structure [76], [77]. Potential applications of this technique are precision alignment for bonding of multiwafer MEMS devices and 3-D ICs, as well as one-step alignment for simultaneous bonding of multiple wafer stacks. Alignment accuracy can be achieved as better than 200 nm at the bonding interface [77].

- 2) Transfer–Join Approach: In this approach [6], [78], the pillarlike copper key structure (Cu stud) is plugged into polymer-pocketed copper pads. The pocketlike lock is provided at the bottom with a Cu pad that is to be bonded to the Cu stud later. The stud and the combined thickness of the adhesive and the insulator are adjusted so that the Cu-stud-to-Cu-pad contact is first established during the bonding to form a metal–metal bond. Under the continued bonding pressure, the stud height is compressed, and the adhesive is brought into contact with the opposing insulator surface and bonded. There is no sliding guideline between the stud and the pad. Only the polymer window to the pad keeps the stud from later expansion misalignment. For this approach, the bottom lock structures are designed to be larger than the key structures. Therefore, there is room to accommodate misalignment during operation.

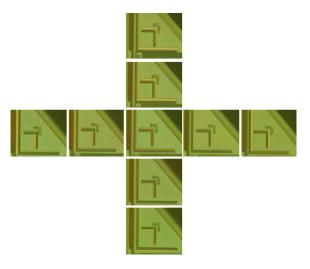

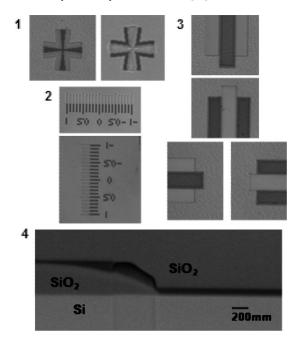

- 3) Tapered Keyed Structures: Similar to the anisotropic etched silicon structures in MEMS, a tapered structure on the bonding surface can be created to interlock the wafers mechanically [79]. The conceptual mechanism [80] is that the keyed structures can slide into each other along the tapered planes and are mechanically interlocked so that it can prevent wafers from shifting relative to each other and so that wafers can maintain their aligned position during the bonding process. Fig. 16 shows a conceptual mechanical interlocking mechanism: 1) the tapered surfaces slide in the misalignment range, and 2) the key structures are interlocked. The measured alignment accuracies are shown in Fig. 17. Preliminary results also indicate

Fig. 17. Wafer alignment accuracy using the keyed alignment structures after alignment, contact, and clamping, showing a standard deviation of the alignment accuracy within a quarter micrometer [75].

Fig. 18. Optical  $20\times$  images of the overlaid keyed structures. (a) Alignment marks. (b) Vernier structures for reading alignment accuracy. (c) Bar interlock structures. (d) SEM image of cross-sectional view of interlocked structures.

that these self-alignment structures at the wafer surfaces can adjust and improve the prebonding wafer-to-wafer alignment accuracy to well below 1  $\mu$ m, approaching 100 nm. Fig. 18 shows the optical 20× images of the keyed structures used for the measurement of alignment accuracy: overlaying alignment marks, vernier structures for reading alignment accuracy, bar interlock structures, and SEM image of the cross-sectional view of the interlocked structures. For the via-last process, this keyed interlocking concept is more feasible since the tapered key structure is easy to implement on the bonding surface (oxide or polymer adhesive).

For the via-first process, it should be patterned into the surface of copper/oxide or copper/dielectric redistributed with more process steps. This may affect the surface condition or may cause thermal distortions of aligning wafers. To prevent thermally induced postbonding misalignment, the keyed structures can provide the additional fiction into a mating surface to prevent bonding-induced thermal misalignments. As an example, the keyed alignment structures were aligned and bonded using a 0.2- $\mu$ m-thin BCB layer. Fig. 18(d) shows an FIB–SEM image of the cross section of the keyed alignment structures on

Fig. 19. Schematic of conceptual keyed structures. Pyramidlike and cornlike.

the left side of the wafer stack, describing that the misalignment is reduced and maintained.

To improve the sliding effect, the two design modifications of the keyed structure are discussed as follows, i.e., pyramid and corn structures, shown in Fig. 19. A pyramidlike structure offers a large contact area with long tapered plane, which enables a strong key-locking effective, whereas a large friction generated in a large rotation alignment error would hinder the locking effect. On the contrary, a cornlike structure has a small contact area, providing less locking effect but more freedom of error correction, especially rotation and run-out errors. The size and angle of the tapered structure determine allowable alignment tolerance, possibility, and thickness of the bonding layer. A stiffer tapered angle provides a shorter travel range to correct misalignment. Using vertical down-force when two wafers brought together, key-lock structures slide into each other in a horizontal direction to correct the misalignment. Tapered slope and down-force should be optimized to give enough force for the wafers to slide. The number of keyed structures can be two or more along the edge of the wafer. However, more keyed structures make the sliding and locking of keyed structures more difficult.

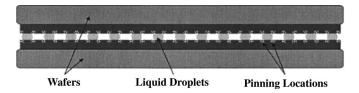

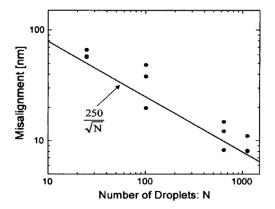

# C. Submicrometer Aligned Wafer Bonding Via Capillary Forces

The alignment concept of capillary forces and surface tension was introduced to die-to-die or die-to-wafer bonding [82]–[86]. A droplet of waterlike liquid can hold a die on another die or a substrate to an alignment accuracy of a micrometer since the strong surface tension can pull and keep a die in micrometer scale. The capillary-force-assisted self-alignment method is applied to wafer-to-wafer aligned bonding, shown in Fig. 20 [86]. In this process, liquid droplets are applied uniformly at the interface. The droplets via capillary forces minimize their surface energy at the pinning boundaries of the droplets. Fig. 21 shows the average misalignment across the wafer as a function of the number of droplets used. It explains that the misalignment is reduced over the increasing droplet density [86]. One critical huddle is to apply the droplets across the entire wafer. The other is to eliminate the unnecessary residual liquid at the wafer interface before wafer bonding.

# VIII. ALIGNMENT CHARACTERIZATION TECHNIQUES

Accurate alignment inspection and read-out offer iterative feedback correction and analysis for the development of

Fig. 20. Schematic of the capillary-force-assisted wafer bonding [86].

Fig. 21. Average misalignment across the wafer due to patterning error as a function of the number of droplets used [86].

alignment techniques. Alignment inspection is being investigated for commercialization of this 3-D technology [87]–[94]. Alignment accuracy is characterized usually at two stages: prebonding and postbonding. Prebonding alignment inspection is limited to in-focus checkup. Postbonding alignment is difficult to inspect since the aligned marks are at the bond interface. In practice, three methods are used for 3-D integration: optical, IR, and cross-sectional inspections. While the first two methods are nondestructive methods, optical inspection is limited to a transparent wafer. It requires a transparent handle wafer to view the alignment marks on the multistacked device layers. IR inspection provides the real-time reading of nontransparent silicon bonding. However, IR lights are attenuated along with the thickness of the silicon and cannot pass through multilayered metal lines. Cross-sectional destructive approach provides the most accurate alignment inspection. It may be feasible only at a research and development stage. To realize high-precision wafer-to-wafer alignment and nondestructive measurement of misalignments, a variety of inspection methods such as the 2-D Moiré method is developed [87], [89], [91].

# IX. SUMMARY AND CONCLUSION

The wafer-to-wafer alignment techniques and issues for wafer-level 3-D integration have been reviewed and discussed. Alignment accuracy directly affects the density of TSVs and BISVs (hence the applications of 3-D integration). Various wafer alignment approaches have been developed. An alignment accuracy of 1  $\mu$ m or smaller can be achieved, depending on the alignment approaches and 3-D applications. Thermal expansion at various wafer processing stages (i.e., prior to, during, and after wafer alignment) is a significant factor affecting 3-D wafer alignment for the major wafer bonding schemes. For oxide fusion bonding proposed using an SOI-based 3-D assembly process, a layer-transfer process affects the wafer-

level alignment yield. For copper bonding, modifying the bonding process parameters can reduce thermal-expansion-induced misalignments. For adhesive bonding, increasing the viscosity of the thermal setting material can prevent shear-bonding-force-induced misalignments. Keyed alignment structures using a mechanical interlocking mechanism can further improve the alignment accuracy and can prevent thermal-expansion-induced misalignments.

Wafer stress engineering, thermal process control, and 3-D platform selection are critical for 3-D wafer alignment. Precise alignment issues are yet to be fully addressed, whereas alignment tools are being developed toward deep submicrometer mechanical alignment accuracy at room temperature.

#### ACKNOWLEDGMENT

The authors would like to thank the IBM's Material Research Laboratory; the Central Scientific Services, T. J. Watson Research Center, Yorktown Heights, NY; and the Micro and Nanofabrication Clean Room, Rensselaer Polytechnic Institute, Troy, NY, for the work done in these facilities and EVGroup Inc. for their technical support.

#### REFERENCES

- [1] J.-Q. Lu, "3D hyper-integration and packaging technologies for micronano-systems," *Proc. IEEE*, vol. 97, no. 1, pp. 18–30, Jan. 2009.

- [2] J. U. Knickerbocker, P. S. Andry, B. Dang, R. R. Horton, M. J. Interrante, C. S. Patel, R. J. Polastre, K. Sakuma, R. Sirdeshmukh, E. J. Sprogis, S. M. Sri-Jayantha, A. M. Stephens, A. W. Topol, C. K. Tsang, B. C. Webb, and S. L. Wright, "Three dimensional silicon integration," *IBM J. Res. Develop.*, vol. 52, no. 6, pp. 553–569, Nov. 2008.

- [3] J. A. Burns, B. F. Aull, C. K. Chen, C.-L. Chen, C. L. Keast, J. M. Knecht, V. Suntharalingam, K. Warner, P. W. Wyatt, and D.-R. W. Yost, "A wafer-scale 3-D circuit integration technology," *IEEE Trans. Electron Devices*, vol. 53, no. 10, pp. 2507–2516, Oct. 2006.

- [4] S. J. Koester, A. M. Young, R. R. Yu, S. Purushothaman, K.-N. Chen, D. C. La Tulipe, Jr., N. Rana, L. Shi, M. R. Wordeman, and E. J. Sprogis, "Wafer level 3D integration technology," *IBM J. Res. Develop.*, vol. 52, no. 6, pp. 583–597, Nov. 2008.

- [5] C.-G. Hwang, "New paradigms in the silicon industry," in *IEDM Tech. Dig.*, Dec. 2006, pp. 19–26.

- [6] S. Q. Gu, P. Marchal, M. Facchini, F. Wang, M. Suh, D. Lisk, and M. Nowak, "Stackable memory of 3D chip integration for mobile applications," in *IEDM Tech. Dig.*, Dec. 2008, pp. 1–4.

- [7] L. Katehi, W. Chappell, S. Mohammadi, A. Margomenos, and M. Steer, "Heterogeneous wafer scale circuit architecture," *IEEE Microw. Mag.*, vol. 8, no. 1, pp. 52–69. Feb. 2007.

- vol. 8, no. 1, pp. 52–69, Feb. 2007.

[8] W. Haensch, "Why should we do 3D integration?" in *Proc. 45th ACM/IEEE Des. Autom. Conf.*, Anaheim, CA, Jun. 2008, pp. 674–675.

- [9] P. Ramm, A. Klumpp, J. Weber, N. Lietaer, M. Taklo, W. De Raedt, T. Fritzsch, and P. Couderc, "3D integration technology: Status and application development," in *Proc. ESSCIRC*, Seville, Spain, 2010, pp. 9–16.

- [10] P. Garrou, C. Bower, and P. Ramm, Handbook of 3D Integration Technology and Applications of 3D Integrated Circuits, Weinheim, Germany: Wiley-VCH, 2008. [Online]. Available: http://onlinelibrary.wiley.com/ book/10.1002/9783527623051

- [11] S. Borkar, "3D integration technology for energy efficient system design," in *Proc. Int. Symp. VLSI-TSA*, Hsinchu, Taiwan, Apr. 2010, pp. 100–103.

- [12] S. H. Christiansen, R. Singh, and U. Gösele, "Wafer direct bonding: From advanced substrate engineering to future applications in micro/ nanoelectronics," *Proc. IEEE*, vol. 94, no. 12, pp. 2060–2106, Dec. 2006.

- [13] C.-T. Ko and K.-N. Chen, "Wafer-level bonding/stacking technology for 3D integration," *Microelectron. Reliab.*, vol. 50, no. 4, pp. 481–488, Apr. 2010.

- [14] M. Koyanagi, T. Nakamura, Y. Yamada, H. Kikuchi, T. Fukushima, T. Tanaka, and H. Kurino, "Three-dimensional integration technology based on wafer bonding with vertical buried interconnections," *IEEE Trans. Electron Devices*, vol. 53, no. 11, pp. 2799–2808, Nov. 2006.

- [15] N. Maeda, H. Kitada, K. Fujimoto, K. Suzuki, T. Nakamura, A. Kawai, K. Arai, and T. Ohba, "Wafer-on-wafer (WOW) stacking with damascene-contact TSV for 3D integration," in *Proc. Int. Symp. VLSI-TSA*, Apr. 26–28, 2010, pp. 158–159.

- [16] M. Khbeis, G. Metze, P. Difonzo, and K. Moores, "Fabrication of high density substrate for advanced 3-D modules," in *Proc. IMAPS Adv. Tech. Workshop Adv. Substrates Next Gener. Semicond.*, Linthicum Heights, MD, 2008, pp. 28–33.

- [17] M. Sadaka, I. Radu, and L. D. Cioccio, "3D integration: Advantages, enabling technologies and applications," in *Proc. IEEE ICICDT*, Grenoble, France, Jun. 2–4, 2010, pp. 106–109.

- [18] Semiconductor Industry Association, Int. Tech. Roadmap for Semiconductors (ITRS): 2009 Edition. [Online]. Available: http://public.itrs.net/

- [19] K. Takahashi and M. Sekiguchi, "Through silicon via and 3-D wafer/chip stacking technology," in *Proc. IEEE Symp. VLSI Circuits, Dig. Tech. Papers*, 2006, pp. 89–92.

- [20] Y. S. Kim, A. Tsukune, N. Maeda, H. Kitada, A. Kawai, K. Arai, K. Fujimoto, K. Suzuki, Y. Mizushima, T. Nakamura, T. Ohba, T. Futatsugi, and M. Miyajima, "Ultra thinning 300-mm wafer down to 7-μm for 3D wafer integration on 45-nm node CMOS using strained silicon and Cu/low- k interconnects," in IEDM Tech. Dig., Dec. 7–9, 2009, pp. 1–42.

- [21] H. S. Yang and M. S. Bakir, "3D integration of CMOS and MEMS using mechanically flexible interconnects (MFI) and through silicon vias (TSV)," in *Proc. 60th ECTC*, Las Vegas, NV, Jun. 1–4, 2010, pp. 822–828.

- [22] T. Huesgen, G. Lenk, B. Albrecht, P. Vulto, T. Lemke, and P. Woias, "Optimization and characterization of wafer-level adhesive bonding with patterned dry-film photoresist for 3D MEMS integration," Sens. Actuators A, Phys., vol. 162, no. 1, pp. 137–144, Jul. 2010.

- [23] H.-T. Hsu, W.-S. Su, C.-C. Lee, H.-Y. Huang, H.-Y. Lin, and W. Fang, "3D integration of micro optical components on flexible on transparent substrate with through-hole-vias," in *Proc. IEEE 23rd Int. Conf. MEMS*, Jan. 24–28, 2010, pp. 536–539.

- [24] S. Farrens, "Wafer-bonding technologies and strategies for 3D ICs," in Wafer Level 3-D ICs Process Technology, C. Tan, R. Gutmann, and L. R. Reif, Eds. New York: Springer-Verlag, 2008, ch. 4, pp. 49–84.

- [25] M. Lapisa, G. Stemme, and F. Niklaus, "Wafer-level heterogeneous integration for MOEMS, MEMS, and NEMS," *IEEE J. Sel. Topics Quantum Electron.*, 2011, to be published.

- [26] J.-Q. Lu, A. Jindal, Y. Kwon, J. J. McMahon, K.-W. Lee, R. P. Kraft, B. Altemus, D. Cheng, E. Eisenbraun, T. S. Cale, and R. J. Gutmann, "3D system-on-a-chip using dielectric glue bonding and Cu damascene inter-wafer interconnects," in *Proc. Int. Symp. Thin Film Mater., Process., Reliab. 203rd Meeting Electrochem. Soc.*, 2003, vol. PV 2003-13, pp. 381–389

- [27] T. S. Cale, J.-Q. Lu, and R. J. Gutmann, "Three-dimensional integration in microelectronics: Motivation, processing, and thermomechanical modeling," *Chem. Eng. Commun.*, vol. 195, no. 8, pp. 847–888, Aug. 2008.

- [28] J.-Q. Lu, J. J. McMahon, and R. J. Gutmann, "Via-first inter-wafer vertical interconnects utilizing wafer-bonding of damascene-patterned metal/adhesive redistribution layers," presented at the 3D Packaging Workshop IMAPS Device Packaging Conf., Scottsdale, AZ, Mar. 2006, Paper WP64.

- [29] S. H. Lee and M. Khbeis, "Commercially off the shelf (COTS) 3D integration using low temperature wafer bonding," presented at the IMAPS Device Packaging Conf., Scottsdale, AZ, Mar. 7–11, 2011, Paper TP16.

- [30] S. Ogawa, M. Imada, and S. Noda, "Analysis of thermal stress in wafer bonding of dissimilar materials for the introduction of an InP-based light emitter into a GaAs-based three-dimensional photonic crystal," *Appl. Phys. Lett.*, vol. 82, no. 20, pp. 3406–3408, May 2003.

- [31] A. M. Young and S. J. Koester, "3D process technology considerations," in *Three Dimensional Integrated Circuit Design*, Y. Xie, J. Cong, and S. Sapatnekar, Eds. New York: Springer-Verlag, 2010, ch. 2, pp. 15–21.

- [32] W. H. Teh, C. Deeb, J. Burggraf, M. Wimplinger, T. Matthias, R. Young, C. Senowitz, and A. Buxbaum, "Recent advances in submicron alignment 300 mm copper-copper thermocompressive face-to-face wafer-to-wafer bonding and integrated infrared, high-speed FIB metrology," in *Proc. IEEE IITC*, Burlingame, CA, Jun. 6–9, 2010, pp. 1–3.

- [33] B. Kim, T. Matthias, M. Wimplinger, and P. Lindner, "Advanced wafer bonding solutions for TSV integration with thin wafers," in *Proc. IEEE Int. Conf. 3D Syst. Integr.*, San Francisco, CA, Mar. 2009, pp. 1–6.

- [34] H. W. van Zeijl and P. M. Sarro, "Alignment and overlay characterization for 3D integration and advanced packaging," in *Proc. 11th EPTC*, Dec. 9–11, 2009, pp. 447–451.

- [35] S. Farrens, "Vertical integration: A confederacy of alignment, bonding, and materials technologies," in *Proc. Mater. Res. Soc. Symp.*, 2007, vol. 970, p. 0970-Y04-05.

- [36] S. Farrens, "Wafer and die bonding technologies for 3D integration," in Proc. Mater. Res. Soc. Symp., Boston, MA, 2008, vol. 1112, p. 1112-E01-06.

- [37] T. Matthias, B. Kim, M. Wimplinger, and P. Lindner, "Thin wafer processing and chip stacking for 3D integration," in *Proc. 3rd ESTC*, Berlin, Germany, Sep. 13–16, 2010, pp. 1–6.

- [38] M. Wimplinger, J.-Q. Lu, J. Yu, Y. Kwon, T. Matthias, T. S. Cale, and R. J. Gutmann, "Fundamental limits of 3D wafer-to-wafer alignment accuracy," in *Proc. Mater. Res. Soc. Symp.*, 2004, vol. 812, p. 0812-F06-10

- [39] A. R. Mirza, "One micron precision, wafer-level aligned bonding for interconnect, MEMS and packaging applications," in *Proc. ECTC*, Las Vegas, NV, 2000, pp. 676–680.

- [40] T. Matthias, M. Wimplinger, S. Pargfrieder, and P. Lindner, "3-D process integration-wafer-to-wafer and chip-to-wafer bonding," in *Proc. Mater. Res. Soc. Symp.*, Boston, MA, 2007, vol. 0970, p. 0970-Y04-08.

- [41] F. Bijnen, W. Buel, M. Young, X. Zhou, and C. Gooch, "Back-side alignment strategy decouples process from alignment and achieves leading edge overlay performance," *Microelectron. Eng.*, vol. 83, no. 4–9, pp. 647–650, Apr.–Sep. 2006.

- [42] L. Marinier, W. Van Noort, R. Pellens, B. Sutedja, R. Dekker, and H. Van Zeijl, "Front- to back-side overlay optimization after wafer bonding for 3D integration," *Microelectron. Eng.*, vol. 83, no. 4–9, pp. 1229–1232, Apr.–Sep. 2006.

- [43] H. Van Zeijl, J. Slabbekoorn, and L. K. Nanver, "Front- to back wafer alignment, overlay and wafer distortion in substrate transfer technologies," in *Proc. of the SAFE/IEEE Workshop*, Veldhoven, The Netherlands, Nov. 29–30, 2000, pp. 163–167.

- [44] K. Warner, C. Chen, R. Donofrio, C. Keast, and S. Poesse, "An investigation of wafer-to-wafer alignment tolerances for three dimensional integrated circuit fabrication," in *Proc. IEEE Int. SOI Conf.*, Charleston, CA, 2004, pp. 71–72.

- [45] A. Klumpp, P. Ramm, and R. Wieland, "3D-integration of silicon devices: A key technology for sophisticated products," in *Proc. DATE Conf. Exhib.*, Mar. 8–12, 2010, pp. 1678–1683.

- [46] R. Chatterjee, M. Fayolle, P. Leduc, S. Pozder, B. Jones, E. Acosta, B. Charlet, T. Enot, M. Heitzmann, M. Zussy, A. Roman, O. Louveau, S. Maitrejean, D. Louis, N. Kernevez, N. Sillon, G. Passemard, V. Pol, V. Mathew, S. Garcia, T. Sparks, and Z. Huang, "Three dimensional chip stacking using a wafer-to-wafer integration," in *Proc. IEEE IITC*, San Francisco, CA, 2007, pp. 81–83.

- [47] S. Steen, "Overlay as the key to drive wafer scale 3D integration," Microelectron. Eng., vol. 84, no. 5–8, pp. 1412–1415, May–Aug. 2007.

- [48] S. H. Lee and J. Q. Lu, "Thermally induced misalignment for 3DI," presented at the IMAPS Device Packaging Conf., Scottsdale, AZ, Mar. 2008, Paper WP64.

- [49] D. La Tulipe, L. Shi, A. Topol, D. Frank, S. Steen, D. Pfeiffer, D. Posillico, D. Neumayer, S. Goma, J. Vichiconti, J. Rubino, A. Young, G. Singco, and M. Ieong, "Critical aspects of layer transfer and alignment tolerances for 3D integration processes," presented at the 3D Packaging Workshop IMAPS Device Packaging Conf., Scottsdale, AZ, Mar. 2006, Paper THP22.

- [50] A. W. Topol, D. C. La Tulipe, L. Shi, S. M. Alam, D. J. Frank, S. E. Steen, J. Vichiconti, D. Posillico, M. Cobb, S. Medd, J. Patel, S. Goma, D. DiMilia, M. T. Robson, E. Duch, M. Farinelli, C. Wang, R. A. Conti, D. M. Canaperi, L. Deligianni, A. Kumar, K. T. Kwietniak, C. D'Emic, J. Ott, A. M. Young, K. W. Guarini, and M. Ieong, "Enabling SOI-based assembly technology for three-dimensional (3D) integrated circuits (ICs)," in *IEDM Tech. Dig.*, Dec. 2005, pp. 363–366.

- [51] P. Gueguen, C. Ventosa, L. D. Cioccio, H. Moriceau, F. Grossi, M. Rivoire, P. Leduc, and L. Clavelier, "Physics of direct bonding: Applications to 3D heterogeneous or monolithic integration," *Microelectron. Eng.*, vol. 87, no. 3, pp. 477–484, Mar. 2010.

- [52] P. Leduc, F. de Crécy, M. Fayolle, B. Charlet, T. Enot, M. Zussy, B. Jones, J.-C. Barbé, N. Kernevez, N. Sillon, S. Maitrejean, D. Louis, and G. Passemard, "Challenges for 3D IC integration: Bonding quality and thermal management," in *Proc. IEEE IITC*, San Francisco, CA, 2007, pp. 210–212.

- [53] K.-N. Chen, S. H. Lee, P. S. Andry, C. K. Tsang, A. W. Topol, Y.-M. Lin, J.-Q. Lu, A. M. Young, M. Ieong, and W. Haensch, "Structure design and process control for Cu bonded interconnects in 3D integrated circuits," in *IEDM Tech. Dig.*, 2006, pp. 20–22.

- [54] W. Ruythooren, S. Stoukatch, K. Lambrinou, P. Moor, and B. Swinnen, "Direct Cu-Cu thermo-compression bonding for 3D-stacked IC

- integration," presented at the 3D Packaging Workshop IMAPS Device Packaging Conf., Scottsdale, AZ, Mar. 2006, Paper THA51, Paper WP64.

- [55] K. N. Chen, C. Cabral, Jr., S. H. Lee, P. S. Andry, and J. Q. Lu, "Investigations of Cu bond structures and demonstration of a wafer-level 3D integration scheme with W TSVs," in *Proc. Int. Symp. VLSI-TSA*, Hsinchu, Taiwan, Apr. 26–28, 2010, pp. 162–163.

- [56] P. Gueguen, L. Di Cioccio, P. Morfouli, M. Zussy, J. Dechamp, L. Bally, and L. Clavelier, "Copper direct bonding: An innovative 3D interconnect," in *Proc. 60th ECTC*, Las Vegas, NV, 2010, pp. 878–883.

- [57] S. Pozder, R. Chatterjee, A. Jain, Z. Huang, R. Jones, and E. Acosta, "Progress of 3D integration technologies and 3D interconnects," in *Proc. IEEE IITC*, San Francisco, CA, 2007, pp. 213–215.

- [58] K.-N. Chen, C. K. Tsang, A. W. Topol, S. H. Lee, B. K. Furman, D. L. Rath, J.-Q. Lu, A. M. Young, S. Purushothaman, and W. Haensch, "Improved manufacturability of Cu bond pads and implementation of seal design in 3D integrated circuits and packages," in *Proc. 23rd Int. VMIC Conf.*, Fremont, CA, Sep. 25–28, 2006, pp. 195–202.

- [59] K. N. Chen, Y. Zhu, W. W. Wu, and R. Reif, "Investigation and effects of wafer bow in 3D integration bonding schemes," *J. Electron. Mater.*, vol. 39, no. 12, pp. 2605–2610, Dec. 2010.

- [60] S. Farrens and S. Sood, Precision Wafer to Wafer Packaging Using Eutectic Metal Bonding, pp. 6–11. [Online]. Available: http://www.suss.com/fileadmin/files/technical\_publications/WP\_WLP\_ PrecisionWafertoWaferPackaging\_0801.pdf

- [61] M. Chiao and L. Lin, "Hermetic wafer bonding based on rapid thermal processing," Sens. Actuators A, Phys., vol. 91, no. 3, pp. 398–402, Jul. 2001.

- [62] J. Zhang, A. Tuantranout, N. Hoivik, W. Zhang, V. M. Bright, and Y. C. Lee, "Flip chip transfer MEMS on a transparent substrate for optical applications," in *Proc. Pacific Rim/ASME Int. Electron. Packag. Tech. Conf. Exhib.*, Kauai, HI, 2001, pp. 1–7.

- [63] S. Farrens and S. Sood, "Wafer level packaging: Balancing device requirements and materials properties," in *Proc. Pan Pacific Microelectron. Symp.*, Kauai, HI, Jan. 22–24, 2008.

- [64] A. Tuantranont, V. M. Bright, W. Zhang, J. Zhang, and Y. C. Lee, "Self-aligned assembly of microlens arrays with micromirrors," in *Proc. SPIE*, vol. 3878, *Micromachining and Microfabrication*, Santa Clara, CA, 1999, pp. 90–100.

- [65] V. Dragoi, E. Cakmak, and E. Pabo, "Metal wafer bonding for MEMS devices," *Romanian J. Inf. Sci. Technol.*, vol. 13, no. 1, pp. 65–72, 2010.

- [66] F. Niklaus, G. Stemme, J.-Q. Lu, and R. Gutmann, "Adhesive wafer bonding," J. Appl. Phys., vol. 99, no. 3, pp. 031101-1-031101-28, Feb. 2006.

- [67] Y. Kwon, J. Seok, J.-Q. Lu, T. S. Cale, and R. J. Gutmann, "Thermal cycling effects on critical adhesion energy and residual stress in benzocyclobutene-bonded wafers," *J. Electrochem. Soc.*, vol. 152, no. 4, pp. G286–G294, 2005.

- [68] F. Niklaus, R. J. Kumar, J. J. McMahon, J. Yu, J.-Q. Lu, T. S. Cale, and R. J. Gutmann, "Adhesive wafer bonding using partially cured ben-zocyclobutene for three-dimensional integration," *J. Electrochem. Soc.*, vol. 153, no. 4, pp. G347–G352, 2006.

- [69] H. Kim and K. Najafi, "Characterization of low-temperature wafer bonding using thin-film parylene," *J. Microelectromech. Syst.*, vol. 14, no. 6, pp. 1347–1355, Dec. 2005.

- [70] E. Cakmak, V. Dragoi, E. Capsuto, C. McEwen, and E. Pabo, "Adhesive wafer bonding with photosensitive polymers for MEMS fabrication," *Microsyst. Technol.*, vol. 16, no. 5, pp. 799–808, May 2010.

- [71] R. Puligadda, S. Pillarlamarri, W. Hong, C. Brubaker, M. Wimplinger, and S. Pargfrieder, "High-performance temporary adhesives for wafer bonding applications," in *Proc. MRS Symp.*, 2006, vol. 970, p. 0970-Y04-09.

- [72] M. C. Lee, S. J. Kang, K. D. Jung, S.-H. Cho, and Y. C. Cho, "A high yield rate MEMS gyroscope with a packaged SiOG process," *J. Micromech. Microeng.*, vol. 15, no. 11, pp. 2003–2010, Nov. 2005.

- [73] R. L. Liu, B. Paden, and K. Turner, "MEMS resonators that are robust to process-induced feature width variations," *J. Microelectromech. Syst.*, vol. 11, no. 5, pp. 505–511, Oct. 2002.

- [74] F. Niklaus, "Wafer-level 3D integration technology platforms for ICs and MEMS," in *Proc. 22nd Int. VMIC*, Fremont, CA, Oct. 2005, pp. 486–493.

- [75] T. Rogers and J. Cowal, "Selection of glass, anodic bonding conditions and material compatibility for silicon-glass capacitive sensors," *Sens. Actuators A, Phys.*, vol. 46, no. 1–3, pp. 113–120, Jan./Feb. 1995.

- [76] A. Slocum and A. Weber, "Precision passive mechanical alignment of wafers," J. Microelectromech. Syst., vol. 12, no. 6, pp. 826–834, Dec. 2003.

- [77] L. Jiang, G. Pandraud, P. French, S. Spearing, and M. Kraft, "A novel method for nanoprecision alignment in wafer bonding applications," *J. Micromech. Microeng.*, vol. 17, no. 7, pp. S61–S67, Jul. 2007.

- [78] H. B. Pogge, C. Prasad, and R. Yu, "Process for making fine pitch connection between devices and structure made by the process," U.S. Patent 6737 297, May 18, 2004.

- [79] S. H. Lee, F. Niklaus, J. J. McMahon, J. Yu, R. J. Kumar, H.-F. Li, R. J. Gutmann, T. S. Cale, and J.-Q. Lu, "Fine keyed alignment and bonding for wafer-level 3D ICs," in *Proc. Mater. Res. Soc. Symp.*, San Francisco, CA, 2006, p. 0914-F10-05.

- [80] F. Niklaus, "A method to maintain wafer alignment precision during adhesive wafer bonding," Sens. Actuators A, Phys., vol. 107, no. 3, pp. 273–278, Nov. 2003.

- [81] S. Kawashima, M. Imada, K. Ishizaki, and S. Noda, "High-precision alignment and bonding system for the fabrication of 3-D nanostructures," *J. Microelectromech. Syst.*, vol. 16, no. 5, pp. 1140–1144, Oct. 2007.

- [82] J. Fang and K. F. Böhringer, "Wafer-level packaging based on uniquely orienting self-assembly (the DUO SPASS processes)," J. Microelectromech. Syst., vol. 15, no. 3, pp. 531–540, Jun. 2006.

- [83] U. Srinivasan, D. Liepmann, and R. Howe, "Microstructure to substrate self-assembly using capillary forces," *J. Microelectromech. Syst.*, vol. 10, no. 1, pp. 17–24, Mar. 2001.

- [84] T. Fukushima, T. Konno, K. Kiyoyama, M. Murugesan, K. Sato, W.-C. Jeong, Y. Ohara, A. Noriki, S. Kanno, Y. Kaiho, H. Kino, K. Makita, R. Kobayashi, C.-K. Yin, K. Inamura, K.-W. Lee, J.-C. Bea, T. Tanaka, and M. Koyanagi, "New heterogeneous multi-chip module integration technology using self-assembly method," in *IEDM Tech. Dig.*, 2008, pp. 1–4.

- [85] C. G. Tsai, C. M. Hsieh, and J. A. Yeh, "Self-alignment of microchips using surface tension and solid edge," *Sens. Actuators A, Phys.*, vol. 139, no. 1/2, pp. 343–349, Sep. 2007.

- [86] M. R. Tupek and K. T. Turner, "Submicron aligned wafer bonding via capillary forces," J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct., vol. 25, no. 6, pp. 1976–1981, Nov. 2007.

- [87] C. Wang, S. Taniyama, Y.-H. Wang, and T. Suga, "High-precision alignment for low-temperature wafer bonding," *J. Electrochem. Soc.*, vol. 156, no. 3, pp. H197–H201, 2009.

- [88] E. Moona and H. I. Smith, "Nanometer-level alignment to a substrate-embedded coordinate system," J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct., vol. 26, no. 6, pp. 2341–2344, Nov. 2008.

- [89] C. Wang and T. Suga, "Measurement of alignment accuracy for wafer bonding by Moire method," *Jpn. J. Appl. Phys.*, vol. 46, no. 4B, pp. 1989– 1993, Apr. 2007.

- [90] H. T. Kim, K. W. Lee, H. J. Yang, and S. C. Kim, "A self-learning method for automatic alignment in wafer processing," in *Proc. 7th Int. Caribbean Conf. Devices, Circuits Syst.*, Cancu, Mexico, Apr. 28–30, 2008.

- [91] A. A. Ghazanfarian, X. Chen, M. McCord, R. Fabian, W. Pease, K. Nguyen, and H. Levinson, "Exploiting structure of wafer distortion in global alignment," *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct.*, vol. 16, no. 6, pp. 3642–3646, Nov. 1998.

- Struct., vol. 16, no. 6, pp. 3642–3646, Nov. 1998.

[92] H. Tsuda and H. Shirai, "Improvement of photolithography process by second generation data mining," *IEEE Trans. Semicond. Manuf.*, vol. 20, no. 3, pp. 239–244, Aug. 2007.

- [93] N. Li, W. Wu, and S. Chou, "Sub-20 nm alignment in nanoimprint lithography using Moire fringe," *Nano Lett.*, vol. 6, no. 11, pp. 2626–2629, Nov. 2006.

- [94] D. V. Campbell, "Process characterization vehicles for 3D integration," in *Proc. 60th ECTC*, Las Vegas, NV, Jun. 1–4, 2010, pp. 1112–1116.

Sang Hwui Lee was born in 1971 in Jinju, South Korea. He received the B.S. degree in electronic materials engineering from Gyeong-Sang National University, Jinju, South Korea, in 1995, and the Ph.D. degree in materials science and engineering from the New Jersey Institute of Technology (NJIT), Newark, in 2005, while focusing on MEMS-based resonating sensor techniques for a coriolis mass flow meter.

He has been a Research Scientist with the Microelectronics Integration Group at the Labora-

tory for Physical Sciences, College Park, MD, since 2008. From 2005 to 2007, he was a Postdoctoral Research Associate with the Center of Integrated Electronics, Rensselaer Polytechnic Institute, Troy, NY. His research interests include heterogeneous 3-D integration, wafer aligning/bonding/thinning, and submicrometer through-strata via for microelectronics and MEMS.

**Kuan-Neng Chen** (M'05) received the M.S. degree in materials science and engineering and the Ph.D. degree in electrical engineering and computer science from the Massachusetts Institute of Technology, Cambridge.

He is currently an Associate Professor in the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan. Prior to the faculty position, he was a Research Staff Member and Project Leader with the IBM Thomas J. Watson Research Center, Yorktown Heights, NY. He has been

conducting 3-D integrated circuit (3-D IC) research since 2000. His current research interests are 3-D IC, through-silicon via technology, wafer bonding technology, phase-change material devices, and nanodevices. He has authored more than 100 publications in book chapters, journals, and international conference proceedings. He is the holder of more than 40 patents and patent applications.

Dr. Chen received the Adventech Young Professor Award and the EDMA Outstanding Youth Award. He also received several IBM Awards, including five IBM Invention Plateau Invention Achievement Awards and two Awards from the Exploratory Technology Group. He is the Editor of the book 3D Integration for VLSI Systems. He is currently a committee member of IEEE 3D IC, IMAPS 3-D Packaging, IEEE INEC, International Electron Devices and Materials Symposia (IEDMS), and the International Symposium on Dry Process (DPS). He is an alternate council member of the Electronics Devices and Materials Association and a member of the Phi Tau Phi Scholastic Honor Society.

**James Jian-Qiang Lu** (M'97–SM'01–F'11) received the Dr.rer.nat. (Ph.D.) degree from the Technical University of Munich, Munich, Germany, in 1995.

He is an Associate Professor with Rensselaer Polytechnic Institute, Troy, NY, where he has been working on 3-D hyperintegration technology since 1999 and other programs. He has broad research experience from micronanoelectronics theory and design to materials, processing, devices, integration, and packaging (e.g., Si, GaAs, and GaN devices;

novel field-effect transistors; terahertz electronics; carbon nanotubes; and Si integrated circuit interconnects). His current research interests include 3-D hyperintegration design and technology and micronanobio interfaces for future chips, microelectromechanical systems, and smart lighting using LEDs. He has authored/coauthored more than 200 publications in refereed journals, conference proceedings, and books and has given a number of invited presentations, seminars, and short courses.

Dr. Lu is a Fellow and a Life Member of the International Microelectronics and Packaging Society (IMAPS) and a member of the American Physical Society and Materials Research Society. He is the Chair of 3D Packaging for the IMAPS National Technical Committee. He received the 2008 IEEE CPMT Exceptional Technical Achievement Award "for his pioneering contributions to and leadership in 3-D integration/packaging" and the 2010 IMAPS William D. Ashman Achievement Award "for his contributions and research in 3-D integration and packaging and for his leadership contributions at international symposiums and device packaging conferences and 3-D packaging workshops." He has served as a technical chair, workshop chair, session chair, panelist, and panel moderator for many conferences.