ELSEVIER

Contents lists available at ScienceDirect

# Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# Bipolar switching characteristics of low-power Geo resistive memory

C.H. Cheng<sup>a,\*</sup>, P.C. Chen<sup>b</sup>, S.L. Liu<sup>c</sup>, T.L. Wu<sup>c</sup>, H.H. Hsu<sup>c</sup>, Albert Chin<sup>c</sup>, F.S. Yeh<sup>a</sup>

- <sup>a</sup> Department of Electronics Engineering and Institute of Electronics Engineering, National Tsing-Hua Univ., Hsinchu, Taiwan, ROC

- <sup>b</sup> Department of Engineering and System Science, National Tsing-Hua Univ., Hsinchu, Taiwan, ROC

- <sup>c</sup> Department of Electronics Eng., National Chiao-Tung Univ., Hsinchu, Taiwan, ROC

#### ARTICLE INFO

Article history: Received 15 October 2010 Received in revised form 3 April 2011 Accepted 10 April 2011 Available online 4 May 2011

The review of this paper was arranged by Dr. Y. Kuk

Keywords:

Resistive random access memory (RRAM) Germanium oxide (GeO<sub>2</sub>)

#### ABSTRACT

We reported an ultra low-power resistive random access memory (RRAM) combining a low-cost Ni electrode and covalent-bond  $GeO_x$  dielectric. This cost-effective Ni/ $GeO_x$ /TaN RRAM device has very small set power of 2  $\mu$ W, ultra-low reset power of 130 pW, greater than 1 order of magnitude resistance window, and stable retention at 85 °C. The current flow at low-resistance state is governed by Poole–Frenkel conduction with electrons hopping via defect traps, which is quite different from the filament conduction in metal-oxide RRAM.

© 2011 Elsevier Ltd. All rights reserved.

#### 1. Introduction

As continuously scaling down the size of flash non-volatile memory (NVM) to sub-30 nm [1,2], the number of stored carriers becomes fewer that degrade the data retention and cycling endurance significantly [1]. The resistive random access memory (RRAM) [3-11] has a simple metal-insulator-metal (MIM) structure and bistable resistance states, which is a promising candidate beyond flash memory. Besides, the RRAM has a small cell size, large memory window for multiple level cell (MLC) operation and threedimensional integration capability. To reach the needed bistable resistance states, non-stoichiometric transition metal-oxides have been used. Good memory device performances have been reported using NiO [3,4], HfO<sub>2</sub> [5] and ZrO<sub>2</sub> [6], ZnO [7], CeO<sub>2</sub> [8], WO<sub>x</sub> [9], Cu-doped  $MoO_x$  (Cu- $MoO_x$ ) [10], and perovskite-type  $SrTiO_3$  [11] transition metal-oxides. In most cases, the high work-function Pt electrode was used in these devices to reach a stable switching behavior and lower down the leakage current, but it is difficult to pattern by Pt reactive-ion etching (RIE). Besides, these devices suffer the penalty of high forming power and high set/reset currents of >100 μA, even using expansive noble Pt metal. Recently, the low-power RRAMs with the low current of <10 µA have been reached in GeO<sub>x</sub>/SrTiO<sub>3</sub> and GeO<sub>x</sub>/HfON RRAM devices [12,13], but the effect of buffered  $GeO_x$  is still not clear.

In this study, we fabricated an ultra-low power RRAM device using covalent-bond  $GeO_2$  dielectric and low-cost Ni electrode. Very low 2  $\mu$ W set power, ultra-low 130 pW reset power, more

E-mail address: raymondchengu@hotmail.com (C.H. Cheng).

than 1 order of magnitude resistance window and stable data retention at  $85\,^{\circ}\text{C}$  were simultaneously reached in the cost-effective Ni/GeO<sub>x</sub>/TaN RRAM device.

#### 2. Experimental procedure

The covalent-bond GeO<sub>2</sub> RRAM devices were fabricated on standard Si wafers. To permit VLSI backend integration, the process began with depositing a 200 nm thick SiO<sub>2</sub> layer on Si substrate. Then the 100-nm-thick TaN was deposited by a sputter system with a fixed Ar/N<sub>2</sub> ratio of 5% as the bottom electrode. After that, the 7-nmn-thick amorphous Ge and 8-nm-thick GeO<sub>2</sub> were deposited by e-gun evaporation on bottom TaN. Finally, a 25-nm-thick Ni metal was evaporated and patterned via a metal mask as the top electrode. Similar high work-function Ni electrode was also used for DRAM MIM capacitors. The fabricated devices were characterized by *C-V* and *I-V* using HP4284A precision LCR meter and HP4156C semiconductor parameter analyzer, respectively. All the *I-V* characteristics given in this study were measured at a sweep rate of 10 ms/V.

## 3. Results and discussion

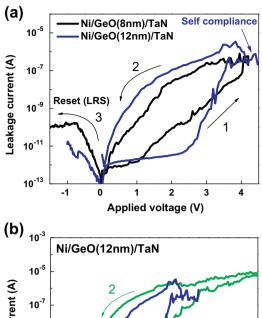

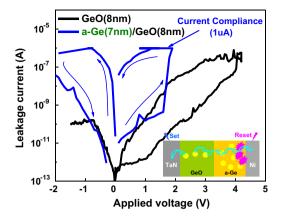

Fig. 1a shows the I-V switching characteristics of Ni/GeO<sub>x</sub>/TaN RRAM with different GeO<sub>x</sub> thickness of 8 and 12 nm. The RRAM with 8-nm-thick GeO<sub>x</sub> shows very small set current of 0.5  $\mu$ A at 4 V and ultra-low reset current of -0.17 nA at -0.75 V. The asymmetric bipolar switching is attributed to the different workfunction between top Ni (5.1 eV) and bottom TaN (4.6 eV) elec-

$<sup>\</sup>ast$  Corresponding author.

**Fig. 1.** Swept I-V curves of Ni/GeO<sub>x</sub>/TaN RRAM with different (a) film thickness and (b) area dimension. The arrows indicate the bias sweeping direction.

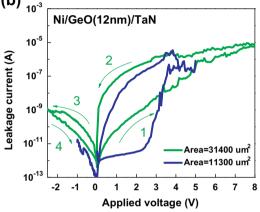

**Fig. 2.** *I–V* curves of HRS and LRS by fitting with Schottky emission and Poole-Frenkel conduction mechanism, respectively.

trodes. During set, a positive voltage is applied to top Ni and cause a high current flow. Since similar increasing current is also found in SiO<sub>2</sub> MOS capacitors by stress-induced leakage current (SILC) effect, the switching in RRAM may be related to electrons injection from low work-function bottom TaN to create defects and current conduction in GeO<sub>x</sub>. This is quite different from the metallic filament switching in metal-oxide RRAM, since no metal exists in GeO<sub>x</sub>. The RRAM with thicker 12 nm GeO<sub>x</sub> shows a larger resistance window, a close set current of  $\sim$ 0.5  $\mu$ A by self-compliance, and a much lower reset current of -5.4 pA at -0.68 V. The current vari-

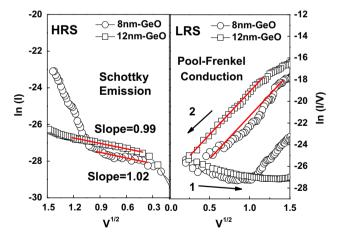

Fig. 3. Swept I-V curves of Ni/GeO<sub>2</sub>/TaN and Ni/a-Ge/GeO<sub>x</sub>/TaN RRAMs.

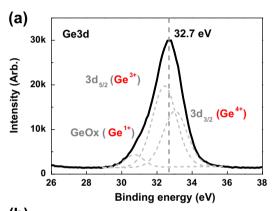

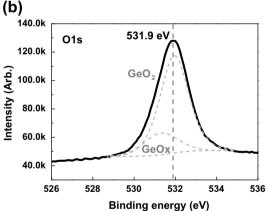

Fig. 4. The XPS spectra of: (a) Ge 3d and (b) O 1s core level in  $GeO_x$ .

ation during self-compliance may be due to electron trapping and de-trapping via  $\text{GeO}_x$  bulk defects. The dependence of  $\text{GeO}_x$  thickness on resistance window and set/reset currents indicate that the current conduction is related to bulk defects. In Fig. 1b, we can observe that the set and reset behaviors are dependence of different device sizes. From the device with large area of  $31400 \, \text{um}^2$ , the applied voltage of 8 V to form low-resistance state (LRS) is required and then recover to high-resistance state (HRS) by a voltage of  $-2.5 \, \text{V}$  which much larger than that of small-area device (11,300  $\, \text{\mu m}^2$ ). Meanwhile, the apparently higher set and reset currents contributed by defect-related size effect explain the importance of defect control in resistive  $\text{GeO}_x$  device again.

To understand the resistance switching phenomenon in covalent-bond Ni/GeO<sub>x</sub>/TaN RRAM, we have plotted the measured l-n(I) and ln(I/V) as the function of  $V^{1/2}$ . As shown in Fig. 2, good

matching between measured and simulated data is reached for both HRS and LRS. The current conduction at HRS is governed by Schottky emission that is usually found in low leakage DRAM MIM devices [14]. The current conduction at LRS is ruled by Poole–Frenkel conduction, where the electrons are transported by hopping conduction [15] via defect traps within  $GeO_x$ . These traps can be generated by electron injection from low work-function TaN into  $GeO_x$  during set process.

To further explore the conduction mechanism, we fabricated the Ni/amorphous-Ge(a-Ge)/GeO $_x$ /TaN RRAM device. The I-V switching characteristics and schematic diagram (inset) are shown in Fig. 3. The bilayer a-Ge/GeO $_x$  RRAM exhibits the current-compliance LRS current of 1  $\mu$ A, small set voltage of 1.6 V and large HRS/LRS ratio of >3 orders of magnitude. However, the current-compliance LRS current is also accompanied by a close reset current, which much larger than that of GeO $_x$  RRAM. The switching mechanism can be supposed that the injected electrons hop via vacancies in a-Ge/GeO $_x$  during set but the hopping paths cannot easily be annihilated by reverse bias current in a-Ge/GeO $_x$  case due to excess vacancies near top Ni electrode. This experiment confirms the importance of unique GeO $_x$  for self-compliance current and ultra-low reset current during set/reset operations.

The defects and chemical states of  $GeO_x$  were further examined by X-ray photoelectron spectroscopy (XPS). Fig. 4a and b show the XPS spectra of Ge 3d and O 1s core level in  $GeO_x$  film. The Ge 3d spectrum with triple deconvoluted peaks are assigned to the different oxidation state compounds of  $Ge^{1+}$ ,  $Ge^{3+}$  ( $3d_{5/2}$ ) and  $Ge^{4+}$  ( $3d_{3/2}$ ), indicating the existence of non-stoichiometric  $GeO_x$  and oxygen vacancies in the matrix. Similar oxygen vacancies are also observed by O 1s spectrum with a slight shift of peak to lower binding energy  $GeO_x$ . These oxygen vacancies in  $GeO_x$  may form conductive paths for electron hopping transport during set operation.

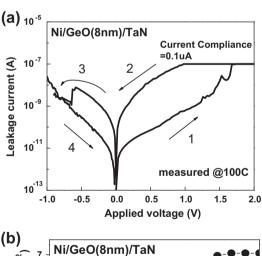

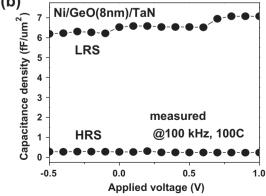

**Fig. 5.** (a) Swept I-V and (b) C-V characteristics of Ni/GeO<sub>x</sub>/TaN RRAM, measured at 100 °C.

To investigate high-temperature switching behaviors of GeO<sub>x</sub> RRAM, the I-V characteristic at 100 °C was measured, shown in Fig. 5a. The current-compliance LRS current of 0.1 uA and forward bias of 1.7 V are applied for the set operation. The decreased set voltage and the ultra-low setting energy (0.17  $\mu$ W) can be ascribed to occurrence of multi-conductive paths for electron hopping at high temperature 100 °C. Furthermore, the hopping paths still can be ruptured by a small reset current of  $\sim$ 8 nA at -0.6 V. The stable set and reset characteristics may be due to the resistance switching controlled by bulk-limited hopping conduction, even at the high temperature of 100 °C. In addition, the bipolar resistance switching also can be indentified by C-V curves, shown in Fig. 5b. The different capacitance densities at HRS and LRS explain that the free electrons hop along multiple conductive defects center and then affect interface charges, responsible for C-V characteristics [16].

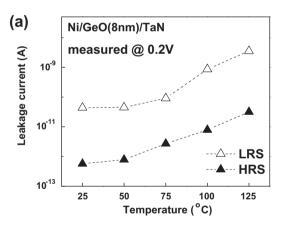

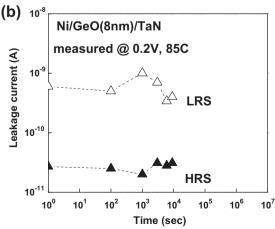

In Fig. 6a, an increasing trend of current is measured for both LRS and HRS states. A still large HRS/LRS resistance window, greater than one order of magnitude, is still obtained at 125 °C. The increasing HRS current with temperature is predicted well by Schottky emission mechanism [14] with higher thermal energy to overcome the Schottky barrier. The increasing LRS current with increasing temperature shows a negative temperature coefficient that is opposite to the metallic filament conduction in metal-oxide RRAM [3]. Such negative temperature coefficient was found previously in highly defective Silicon (Si) via hopping conduction mechanism [15]. Fig. 6b shows the retention characteristics of Ni/GeO<sub>x</sub>/TaN RRAM at elevated temperature of 85 °C. Stable HRS/LRS memory window is measured with retention time to  $9 \times 10^3$  s.

**Fig. 6.** (a) The temperature dependence of HRS/LRS and (b) 85  $^{\circ}$ C retention characteristics of Ni/GeO<sub>x</sub>/TaN RRAM.

#### 4. Conclusions

We have demonstrated an ultra-low power and cost-effective  $Ni/GeO_x/TaN$  RRAM. The low current at LRS is ruled by Poole–Frenkel conduction with electrons hopping via defect traps, which is also responsible for the low self-compliance current. This covalent-bond  $GeO_x$  as a host film or stacked layer should have the potential for future RRAM NVM application.

### Acknowledgement

This work was supported in part by National Science Council of Taiwan.

#### References

- [1] International Technology Roadmap for Semiconductors (ITRS); 2009. <a href="https://www.itrs.net">www.itrs.net</a>.

- [2] Lin SH, Chin Albert, Yeh FS, McAlister SP. IEDM Tech Dig 2008:843-6.

- [3] Russo U, Ielmini D, Cagli C, Lacaita AL, Spiga S, Wiemer C, et al. IEDM Tech Dig 2007:775–8

- [4] Yoon HS, Baek IG, Zhao J, Sim H, Park MY, Lee H, et al. Symp VLSI Tech Dig 2009:26–7.

- [5] Lee HY, Chen PS, Wu TY, Wang CC, Tzeng PJ, Lin CH, et al. Appl Phys Lett 2008;92:142911.

- [6] Liu Q, Long S, Wang W, Zuo Q, Zhang S, Chen J, et al. IEEE Electron Dev Lett 2009:30:335–7.

- [7] Xu N, Gao B, Liu LF, Sun Bing, Liu XY, Han RQ, et al. VLSI Symp Tech Dig 2008:100-1.

- [8] Sun X, Sun B, Liu L, Xu N, Liu X, Han R, et al. IEEE Electron Dev Lett 2009;30:334–6.

- [9] Chen WC, Chen YC, Lai EK, Yao YD, Lin P, Horng SF, et al. Dev Lett 2010;31:126-8.

- [10] Lee D, Seong DJ, Choi HJ, Jo I, Dong R, Xiang W, et al. IEDM Tech Dig 2006:797–800.

- [11] Sim H, Choi H, Lee D, Chang M, Choi D, Son Y, et al. IEDM Tech Dig 2005:777–80.

- [12] Cheng CH, Chin Albert, Yeh FS. IEEE Electron Dev Lett 2010;31:1020–2.

- [13] Cheng CH, Chin Albert, Yeh FS. IEDM Tech Dig 2010:448-51.

- [14] Chiang KC, Cheng CH, Pan HC, Hsiao CN, Chou CP, Chin Albert, et al. IEEE Electron Dev Lett 2007;28:235–7.

- [15] Chin A, Lee K, Lin BC, Horng S. Appl Phys Lett 1996;69:653.

- [16] Gomes HL, Benvenho ARV, de Leeuw DM, Colle M, Stallinga P, Verbakel F, et al. Org Electron 2008;9:119.