### ECS Transactions, 33 (5) 169-172 (2010) 10.1149/1.3481233 ©The Electrochemical Society

## Improved Performance of NILC Poly-Si Nanowire TFTs by Using Ni-Gettering

Bau-Ming Wang<sup>a</sup>, Tzu-Ming Yang<sup>a</sup>, YewChung Sermon Wu<sup>a</sup>, Chun-Jung Su<sup>b</sup>, and Horng-Chih Lin<sup>b</sup>

<sup>a</sup> Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan

<sup>b</sup> Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan

Nickel contamination inside nickel-metal induced lateral crystallization polycrystalline silicon is an issue to fabricate high performance nanowire thin film transistors. The phosphorous-doped  $\alpha$ -Si/chem-SiO<sub>2</sub> films were employed as Ni-gettering layers to investigate effect of Ni residues on the performance of NILC poly-Si NW TFTs. It was found that the performance of NW TFTs was greatly improved after Ni-gettering process.

# Introduction

Low-temperature polycrystalline silicon (poly-Si) thin-film transistors (TFTs) have attracted considerable interest for their application in active-matrix liquid crystal displays (AMLCDs) on cheap glass substrate (1). Recently, high performance poly-Si nanowire (NW) TFTs have been fabricated by nickel-metal induced lateral crystallization (NILC) (2-3). Since NILC grain could be formed parallel to the channel direction, it becomes feasible to form Si NWs with nearly monocrystalline structures (4). Unfortunately, poly-Si/oxide interfaces and poly-Si grain boundaries trap Ni and NiSi<sub>2</sub> precipitates, thus increasing leakage current (5-8) and shifting the threshold voltage (9). Since the poly-Si/oxide interfaces/volume ratio of NW TFTs was much higher than that of tradition NILC TFTs, effect of Ni residues on the performance of NILC NW TFTs should be investigate effect of Ni residues on the performance of NILC NW TFTs.

# Experimental

Two kinds of NWs were investigated in this study. One was designated as "NILC NW" which was a poly-Si NW fabricated with traditional NILC methods, and another was "GETR NW" which utilized the same traditional NILC method with an additional Ni-gettering process. An approach for making NILC NW channels similar to Ref. (2) and (10) was followed. The detailed procedures were basically identical to those described in the Ref. (10), like gate dielectric deposition and source/drain formation. In this study, the major difference was NILC process performed before NW channel was defined. NILC length was about 17  $\mu$ m after lateral crystallization at 540°C for 24 h.

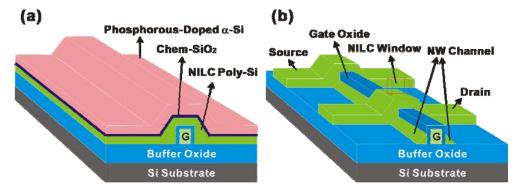

As for GETR NW, an additional Ni-gettering process (11) was carried out to reduce the Ni concentration in NILC film. The gettering structure (phosphorous-doped  $\alpha$ -Si/chem-SiO<sub>2</sub>) is shown in Fig. 1(a). After gettering at 550°C for 12 h, phosphorousdoped  $\alpha$ -Si and chem-SiO<sub>2</sub> layers were removed using 5% tetra-methyl ammonium hydroxide (TMAH) and 1% DHF solution, respectively. For comparison, NILC films were also subjected to an extended heat treatment as Ni-gettering condition. These two poly-Si films were then subjected to an anisotropic etching to form poly-Si spacers (NWs) in a self-aligned manner. The device structure is illustrated in Fig. 1(b).

Fig. 1 (a) Ni-gettering structure fabricated with phosphorous-doped  $\alpha$ -Si capped on the chem-SiO<sub>2</sub>. (b) The schematic of the proposed poly-Si NW TFT structure.

### **Results and Discussion**

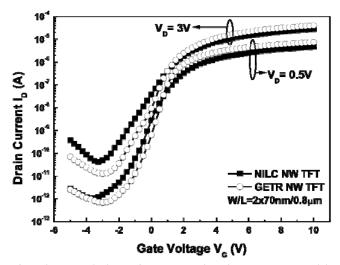

The TFT devices with a couple of NW channels have a nominal channel (L) of 0.8  $\mu$ m and an effective channel width (W) of 140 nm (2 × W<sub>NW</sub>). Typical I<sub>D</sub>-V<sub>G</sub> transfer characteristics of NW TFTs at V<sub>D</sub> = 0.5 and 3 V are compared in Fig. 2. The measured and extracted key device parameters are summarized in Table I. The threshold voltage (V<sub>TH</sub>) is defined at a normalized drain current of I<sub>D</sub> = (W/L) × 100 nA at V<sub>D</sub> = 0.5 V. The subthreshold swing (S.S.) is extracted at V<sub>D</sub> = 0.5 V. The field-effect mobility ( $\mu$ <sub>FE</sub>) is extracted from the maximum value of transconductance at V<sub>D</sub> = 0.5 V. The leakage current (I<sub>OFF</sub>) is defined as the minimum drain current along the gate voltage at V<sub>D</sub> = 3 V.

Fig.2  $I_D$ -V<sub>G</sub> transfer characteristics of NILC poly-Si NW TFTs with and without Nigettering.

As shown in TABLE I, ten NILC and GETR NW TFTs were measured. The performance of NILC NW TFTs was improved after Ni-gettering process. GETR NW TFTs had lower I<sub>OFF</sub>, higher I<sub>ON</sub>/I<sub>OFF</sub> ratio, and higher  $\mu_{FE}$  compared with NILC NW TFTs. This improvement indicates the trap state density (N<sub>trap</sub>) was effectively reduced using phosphorous-doped  $\alpha$ -Si gettering processes. The trap state density of the TFTs was extracted using Levinson and Proano's method (12). The trap density of GETR NW TFTs is  $2.52 \times 10^{12}$  cm<sup>-2</sup>, which is less than that of NILC NW TFTs ( $3.95 \times 10^{12}$  cm<sup>-2</sup>). Since GETR grains (boundaries) were similar to NILC grains, the reduction in N<sub>trap</sub> values implies that those Ni-related defects have been reduced using phosphorous-doped  $\alpha$ -Si/chem-SiO<sub>2</sub> gettering structure (11).

| Parameters                                | GETR           | NILC             |

|-------------------------------------------|----------------|------------------|

| (W/L=2x70nm/0.8μm)                        | NW TFTs        | NW TFTs          |

| I <sub>OFF</sub> (pA)                     | $13.0\pm5.4$   | $81.9 \pm 95.7$  |

| $I_{ON}/I_{OFF}$ ratio (10 <sup>6</sup> ) | $3.2 \pm 1.0$  | $1.4 \pm 1.2$    |

| $\mu_{FE}$ (cm <sup>2</sup> /V-s)         | $140.7\pm38.2$ | $117.3 \pm 17.8$ |

| S.S. (mV/dec)                             | $418\pm 63$    | $395\pm 66$      |

| $V_{TH}$ (V)                              | $0.35\pm0.22$  | $0.19\pm0.40$    |

**TABLE I.** Device characteristics for ten NILC NW TFTs with and without Ni-gettering.

Besides, as shown in TABLE I, the  $V_{TH}$  of the NILC NW TFT is 0.19 V, which is less than that of GETR NW TFT (0.35 V). This is because Ni residues could cause a high density of positive charge at the oxide/NILC poly-Si interface (13). The negative shift of  $V_{TH}$  of NILC NW TFT was due to the presence of these positive charges and nickelrelated donor-like defects.

#### Summary

In this study, high performance NILC NW poly-Si TFTs with a couple of 70-nm NW channels were fabricated, and then improved by Ni-gettering process. The phosphorous-doped  $\alpha$ -Si/chem-SiO<sub>2</sub> films were employed as Ni-gettering layers to reduce Ni residues within NILC poly-Si film. After Ni-gettering process, the performance of NILC NW TFTs was improved. GETR NW TFTs had lower I<sub>OFF</sub>, higher I<sub>ON</sub>/I<sub>OFF</sub> ratio, and higher  $\mu_{FE}$  compared with NILC NW TFTs.

## Acknowledgments

This work was funded by Sino American Silicon Products Incorporation and the National Science Council of the Republic of China under Grant No. 98-2221-E-009 -041-MY3. Technical supports from the National Nano Device Laboratory, Center for Nano Science and Technology and the Nano Facility Center of the National Chiao Tung University are also acknowledged.

#### References

- 1. M. Stewart, R. S. Howell, L. Pires, and M. K. Hatalis, *IEEE Trans. Electron Devices*, 48, 845 (2001).

- 2. C. J. Su, H. C. Lin, and T. Y. Huang, *IEEE Electron Device Lett.*, **27**, 582 (2006).

- 3. C. W. Chang, S. F. Chen, C. L. Chang, C. K. Deng, J. J. Huang, and T. F. Lei, *IEEE Electron Device Lett.*, **29**, 474 (2008).

- 4. J. Gu, S. Y. Chou, N. Yao, H. Zandbergen, and J. K. Farrer, *Appl. Phys. Lett.*, **81**, 1104 (2002).

- 5. P. J. van der Zaag, M. A. Verhejen, S. Y. Yoon, and N. D. Young, *Appl. Phys. Lett.*, **81**, 3404 (2002).

- G. A. Bhat, Z. Jin, H. S. Kwok, and M. Wong, *IEEE Electron Device Lett.*, 20, 97 (1999).

- 7. Z. Jin, K. Moulding, H. S. Kowk, and M. Wong, *IEEE Electron Device Lett.*, 20, 167 (1999).

- 8. D. Murley, N. Young, M. Trainor, and D. McCulloch, *IEEE Trans. Electron Devices*, **48**, 1145 (2001).

- 9. G. A. Bhat, H. S. Kwok, and M. Wong, Solid State Electron., 44, 1321 (2000).

- 10. H. C. Lin, M. H. Lee, C. J. Su, T. Y. Huang, C. C. Lee, and Y. S. Yang, *IEEE Electron Device Lett.*, **26**, 643 (2005).

- 11. B. M. Wang, and Y. S. Wu, J. Electro. Mater., 38, 767 (2009).

- 12. R. E. Proano, R. S. Misage, and D. G. Ast, *IEEE Trans. Electron Devices*, 36, 1915 (1989).

- 13. Y. Lee, S. Bae, and S. J. Fonash, IEEE Electron Device Lett., 26, 900 (2005).