# ECS Transactions, 33 (5) 193-195 (2010) 10.1149/1.3481236 ©The Electrochemical Society

# High Performance and Reliability of Poly-Si Thin-Film Transistors Using Nickel Drive-In Induced Laterally Crystallization

YewChung Sermon Wu, Chih-Pang Chang,

Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, Republic of China

In this study, polycrystalline silicon thin film transistors using drive-in Ni induced lateral crystallization (DILC) was proposed. In DILC,  $F^+$  implantation was used to drive Ni in the  $\alpha$ -Si layer. To reduce the Ni contamination, the remained Ni film was then removed, and subsequently annealed at 590°C. It was found DILC TFTs exhibit high field-effect mobility, low threshold voltage, low subthreshold slope, high on-state current, lower trap state density, smaller standard deviations, and low off-state leakage current compared with conventional Ni-metal-induced lateral crystallization (MILC) TFTs.

#### Introduction

Low-temperature polycrystalline silicon (LTPS) thin-film transistors (TFTs) have attracted considerable interest for their application in active-matrix organic emitting diode displays (AMOLED). Metal-induced lateral crystallization of Silicon (MILC) is one of these methods to fabricate LTPS film. In MILC, the crystallization of poly-Si was preceded by migration of nickel silicides through  $\alpha$ -Si, and resulting in needlelike Si grains. However, there were still some regions between poly-Si grains remained uncrystallized. These defects might degrade the transfer characteristics of TFT devices.

In this letter, a novel fabrication process has been developed to reduce the Ni concentration and minimizes the trap-state density of polycrystalline silicon (poly-Si) TFTs using nickel drive-in induced laterally crystallization (DILC). The DILC poly-Si was prepared by collision between fluorine ion (F+) implantation with nickel (Ni) through the designed pattern into amorphous-Si ( $\alpha$ -Si) layer after annealing at 590 °C for 3 hr.

# **Experimental**

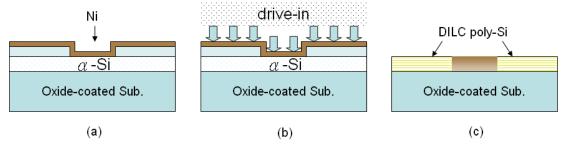

A 120-nm-thick undoped amorphous silicon ( $\alpha$ -Si) layer was deposited onto a 500-nm-thick oxide-coated silicon wafer by low pressure chemical vapor deposition (LPCVD) system. A 65-nm-thick cap-oxide was deposited and patterned to form 20- $\mu$ m-wide lines, and a 20-Å-thick Ni film was then deposited. Samples were subjected to F+ implantation to drive Ni in the  $\alpha$ -Si layer, as shown in Fig.1. For the  $\alpha$ -Si layer under the Ni line, the projection range was set at the middle of the  $\alpha$ -Si layer. At the same time, for the  $\alpha$ -Si layer under the oxide layer, it was located at the cap-oxide/ $\alpha$ -Si interface. The dosage of F+ ranged from 2×1012 to 2×1015 cm-2. The ion-accelerating energy was 35 KeV. The preparation of DILC poly-Si began with four-inch Si wafer. To reduce the Ni contamination/concentration, the remained Ni film and cap-oxide were then removed by chemical etching, and subsequently annealed at 590°C for 3 h to form the DILC poly-Si. For the purpose of comparison, conventional MILC was prepared (1). It is worthy to note

that this DILC processes do not need any additional thermal annealing step and are compatible with MILC TFT processes.

Figure 1. Schematic illustration of F+ implantation process to drive Ni in the  $\alpha$ -Si layer.

#### **Results and Discussion**

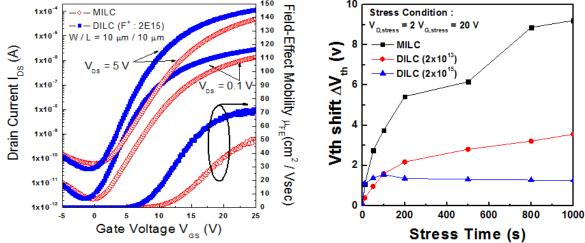

The I<sub>D</sub>-V<sub>G</sub> transfer characteristics are shown in Fig. 2 and the key parameters are summarized in the Table I. It was found that DILC TFTs have superior electrical characteristics, such as high field-effect mobility, low threshold voltage, low subthreshold slope, high on-state current and low off-state leakage current. This indicates that the trap-state density (Nt) in DILC poly-Si was effectively reduced. These results are similar to our previous study on improving the electrical properties of MILC TFTs using F+ implantation (2), in which MILC poly-Si was subjected to F+ implantation. It was also found F atoms can improve performance and reliability of MILC TFTs. Unfortunately, the minimum off currents were nearly unchanged due to the high Ni contamination. In contrast to this study, the Ni concentration inside the poly-Si was controlled/ limited by F+ implantation dosage. The Ni concentration inside the DILC poly-Si was less than that in MILC. As a result, the minimum off current of DILC was less than that of MILC TFT, as shown in Fig. 2.

Figure 2.  $I_D$ - $V_G$  characteristics of MILC and Figure 3. The threshold shift versus stress DILC poly-Si TFTs, respectively.

The other important issue of poly-Si TFTs is their reliability, which was examined under hot-carrier stress. As shown in Fig. 3, the Vth shift of DILC TFTs is greatly

improved. This is because weaker Si-H and Si-Si bonds were replaced by stronger Si-F bonds, which could not be broken under hot-carrier stress (3, 4), thus leading to improved electrical reliability.

Table I. Device characteristics for MILC and

| DILC poly-St 1718.                     |                      |                      |

|----------------------------------------|----------------------|----------------------|

|                                        | MILC                 | DILC                 |

| Mobility $\mu_{FE}$ (cm <sup>2</sup> / | 50.3                 | 72.3                 |

| Vs)                                    |                      |                      |

| Threshold Voltage                      | 10.49                | 6.83                 |

| $V_{TH}(V)$                            |                      |                      |

| Subthreshold Slope                     | 2.49                 | 1.64                 |

| S.S (V/dec.)                           |                      |                      |

| On / Off ratio                         | $7.89 \times 10^{5}$ | $3.03 \times 10^{6}$ |

## **Summary**

Significant improvements on the DILC poly-Si TFT devices performance, including higher field-effect mobility, superior subthreshold slope, lower threshold voltage, higher ON/OFF current ratio, lower trap-state density (Nt) and device reliability.

## Acknowledgments

This work was funded by Sino American Silicon Products Incorporation and the National Science Council of the Republic of China under Grant No. 98-2221-E-009 -041-MY3. Technical supports from the National Nano Device Laboratory, Center for Nano Science and Technology and the Nano Facility Center of the National Chiao Tung University are also acknowledged.

#### Reference

- 1. C. P. Chang, Y. S. Wu, *IEEE Electron Devices Lett.*, **30**, 130 (2009).

- 2. C. P. Chang, Y. S. Wu: *IEEE Electron Devices Lett.*, **28**, 990 (2007).

- 3. C. H. Tu, T. C. Chang, P. T. Liu, C. Y. Yang, H. C. Liu, W. R. Chen, Y. C. Wu, and C. Y. Chang, *IEEE Electron Devices Lett.*, **27**, 4, 262 (2006).

- 4. C. H. Tu, T. C. Chang, P. T. Liu, H. W. Zan, Y. H. Tai, C. Y. Yang, Y. C. Wu, H. C. Liu, W. R. Chen, and C. Y. Chang, *Electrochem. Solid-State Lett.*, **8**, 9, G246 (2005).