## ECS Transactions, 45 (7) 239-243 (2012) 10.1149/1.3701544 ©The Electrochemical Society

# The Influences of Oxygen Incorporation on the Defect Trap States of *a*-IGZO Thin-film Transistors

Chun-Chieh Lo and Tsung-Eong Hsieh\*

Department of Materials Science and Engineering, National Chiao Tung University 1001 Ta-Hsueh Road, Hsinchu, Taiwan 30010, R.O.C.

Thin-film transistors (TFTs) comprised of amorphous indiumgallium-zinc-oxide (a-IGZO) as the active channel layers were prepared by sputtering process at various Ar/O<sub>2</sub> gas flow ratios and electrical investigated. their properties were characterizations indicated that the TFT sample prepared at the condition of  $Ar/O_2$  ratio = 20:0.6 exhibits the best performance with field-effect mobility ( $\mu_{FF}$ ) = 5.2 cm<sup>2</sup>·V<sup>-1</sup>·sec<sup>-1</sup>, threshold voltage  $(V_{th}) = 0.7 \text{ V}$ , subthreshold gate swing (S.S.) = 0.9V-decade<sup>-1</sup> and on/off ratio =  $5 \times 10^6$ . Such a sample also exhibited the lowest interface trap density ( $D_{it} = 2.8 \times 10^{10} \text{ eV}^{-1} \cdot \text{cm}^{-2}$ ) and the highest capacitance density (334 nF·cm<sup>-2</sup>) as revealed by capacitance-voltage (C-V) analysis and the lowest leakage current density of 25 nA/cm<sup>2</sup> at 10 MV/cm (in case of positive bias on top electrode) as revealed by current-voltage (*I-V*) measurement.

#### Introduction

Transparent amorphous oxide semiconductors (AOSs) are promising materials for channel layer of thin-film transistors (TFTs). Their advantages include relatively high saturation mobility ( $\mu_{\text{sat}} > 10 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{sec}^{-1}$ ), low film roughness, low processing temperatures and high optical transparency in the visible-light wavelength region [1]. However, carrier concentrations in AOSs are correlated to the presence of charged defects such as oxygen vacancies. Therefore, a full understanding on the effects of defect evolution on physical properties of AOSs is a crucial issue for realizing their practical applications.

Recently, amorphous In-Ga-Zn-O (*a*-IGZO) thin films for active channel layer of transparent TFTs have attracted numerous research interests due to their unique physical properties and processing simplifications [2]. The feasibility of *a*-IGZO to large-area TFT fabrication has been demonstrated previously [3]. However, *a*-IGZO tends to be oxygen-deficient and the non-stoichiometry would greatly affect the electrical performance of TFT devices. Operational stability of *a*-IGZO TFTs have been studied by several research groups [4-5]; however, the influence of processing conditions on the defect trap states in TFTs was rarely reported. This work studies the effects of oxygen incorporation conditions during sputtering deposition on defect configurations of *a*-IGZO layer and their correlations to the performance of TFTs. *X*-ray diffraction (XRD) and UV-visible analyses were also performed so as to evaluate the crystallinity and optical transmittance of *a*-IGZO layer prepared in this work.

## **Experimental**

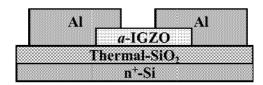

The IGZO sputtering target containing sole InGaZnO<sub>4</sub> phase was first prepared *via* a hybrid process of chemical dispersion and mechanical grinding developed previously [6]. The TFT samples were then prepared by sputtering deposition of 15-nm thick *a*-IGZO active channel layers on *n*-Si<sup>+</sup> substrates clad with 200-nm thick thermally grown SiO<sub>2</sub> layers at various Ar:O<sub>2</sub> gas flow ratios of 20:0, 20:0.6, 20:1.2 and 20:1.8 (in the unit of sccm) using the sole-phase target. The sputtering was carried out at RF power of 80 W and working pressure of 1 mtorr. Notably, no post annealing of *a*-IGZO layers was performed in this study. Subsequently, 300-nm thick aluminum (Al) metal lines serving as the source and drain electrodes of TFTs were deposited on the *a*-IGZO layers by *e*-beam evaporation within the shadow mask technique. The devices channel length and width of TFT was 0.1 and 1.4 mm, respectively. The cross-sectional structure of top-gate type *a*-IGZO TFTs prepared in this work is schematically illustrated in Fig. 1.

In order to clarify the role of bulk defects or interfacial traps on the electrical properties of *a*-IGZO TFTs, the metal-oxide-semiconductor (MOS) and metal-insulator-metal (MIM) structures were separately prepared for *C-V* and *I-V* characterizations. The MOS samples were for the study of trap states at *a*-IGZO/SiO<sub>2</sub> interface while the MIM samples were for the investigation of bulk defect states in *a*-IGZO layer. Their *C-V*, *I-V* and transfer characteristics of TFTs were separately measured by using a Wayne Kerr 6520B precision LCR meter at various frequencies and an HP 4156B semiconductor parameter analyzer in conjunction with a probe station (SANWA, WM-365A-1). XRD (MacScience M18XHF) and UV-Vis spectrometer (Hitachi, U3900H) were adopted to characterize the crystallinity and optical transmittances of *a*-IGZO layers, respectively.

Figure 1. Cross-sectional structure of a-IGZO TFT device.

#### **Results and Discussion**

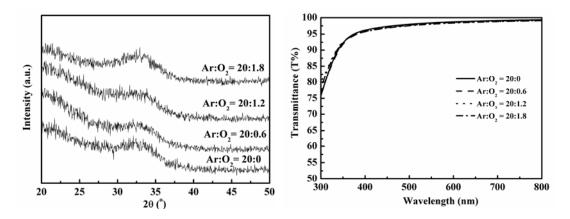

Figures 2(a) and 2(b) separately present the XRD profiles and optical transmittance of a-IGZO layers prepared at various Ar/O<sub>2</sub> gas flow ratios. Lack of distinctive diffraction peaks in the XRD profiles of Fig. 2(a) indicates that the change of Ar/O<sub>2</sub> gas flow ratio barely affects the amorphism of a-IGZO layers. Figure 2(b) depicts the average transmittances of all a-IGZO layers are greater than 93% in the visible-light wavelength region. The high optical transparency illustrates the feasibility of a-IGZO layer to the fabrication of fully transparent TFTs.

The transfer characteristics of TFTs prepared at various Ar:O<sub>2</sub> gas flow ratios are listed in Table I. Apparently, the devices prepared at Ar:O<sub>2</sub> gas flow ratio of 20:0.6 exhibits the best electrical performance with  $\mu_{FE} = 5.2 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{sec}^{-1}$ , S.S. = 0.9 V·decade<sup>-1</sup>,  $V_{th} = 0.7 \text{ V}$  and on/off ratio =  $5 \times 10^6$ .

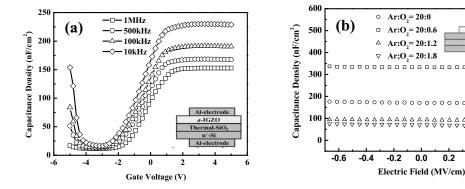

Figure 3(a) presents the typical C-V profiles of MOS samples containing a-IGZO layer prepared at Ar:O<sub>2</sub> gas flow ratio of 20:0.6 measured at the frequencies ranging from 10 kHz to 1 MHz. In accord with the C-V data, the trap density ( $D_{it}$ ) at a-IGZO/SiO<sub>2</sub> interface could be calculated in terms of the equation [7]:

$$D_{it} = \frac{1}{q^2} \left\{ \left( \frac{1}{C_{LF}} - \frac{1}{C_i} \right)^{-1} - \left( \frac{1}{C_{HF}} - \frac{1}{C_i} \right)^{-1} \right\}$$

(1)

where q is electron charge,  $C_i$  is the insulator layer capacitance,  $C_{LF}$  and  $C_{HF}$  are the lowand high-frequency capacitances of sample obtained by C-V measurement.

Figure 2. (a) XRD and (b) transmittance profiles of a-IGZO layers prepared at various gas flow ratios (sample thickness = 100 nm).

Table I. Transfer characteristics of a-IGZO TFTs prepared at various Ar:O<sub>2</sub> gas flow

| Tatios. |                   | 05.                                                                  |                              |                                        |                   |

|---------|-------------------|----------------------------------------------------------------------|------------------------------|----------------------------------------|-------------------|

| -       | Ar:O <sub>2</sub> | $\mu_{\rm FE}  ({\rm cm}^2 \cdot {\rm V}^{-1} \cdot {\rm sec}^{-1})$ | S.S. $(V \cdot decade^{-1})$ | $V_{\text{th}}\left(\mathbf{V}\right)$ | On/off ratio      |

| -       | 20:0              | 1.6                                                                  | 1.0                          | -2.7                                   | 5×10 <sup>4</sup> |

|         | 20:0.6            | 5.2                                                                  | 0.9                          | 0.7                                    | $5 \times 10^{6}$ |

|         | 20:1.2            | 1.8                                                                  | 1.1                          | 1.9                                    | $1 \times 10^{6}$ |

|         | 20:1.8            | 0.8                                                                  | 1.0                          | 6.8                                    | 5×10 <sup>5</sup> |

Figure 3. C-V profiles of (a) MOS sample containing a-IGZO layer prepared at Ar:O<sub>2</sub> gas flow ratio of 20:0.6 measured at various frequencies and (b) MIM samples (at)

0.2

0.4

containing a-IGZO layer prepared at various Ar:O<sub>2</sub> gas flow ratios measured at frequency of 1MHz.

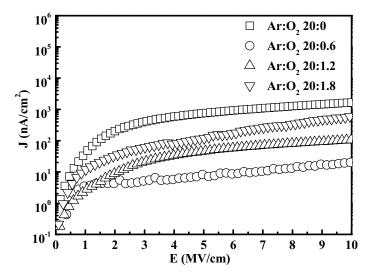

Table II summarizes the  $D_{it}$  values calibrated in terms of the C-V data of MOS sample and capacitance densities ( $C_{ox}$ ) deduced by the C-V measurements of MIM samples depicted in Fig. 3(b). The lowest interface trap density ( $D_{it} = 2.8 \times 10^{10}$  eV $^{-1} \cdot \text{cm}^{-2}$ ) and the highest  $C_{ox}$  (334 nF·cm $^{-2}$ ) were observed in the sample prepared at the condition of Ar:O<sub>2</sub> gas flow ratio = 20:0.6. It is known that the high  $C_{ox}$  implies the improved film quality and low bulk trap density [7]. Hence, the oxygen incorporation during sputtering affects not only the interface trap states, but also the bulk defect traps in the sample. As a result, the oxygen incorporation condition during sputtering has to be optimized so as to achieve the best TFT performance as indicated in Table I. Transfer characteristics of TFTs and C-V data of MOS samples presented above are also in agreement with the current density *versus* applied bias filed (J-E) profiles of MOS samples presented in Fig. 4 which depicts the lowest leakage current density of 25 nA/cm<sup>2</sup> at 10 MV/cm for the sample prepared at the condition of Ar:O<sub>2</sub> gas flow ratio = 20:0.6 (in case of positive bias on top electrode).

Table II. List of  $D_{it}$  and  $C_{ox}$  of MOS samples prepared at various Ar:O<sub>2</sub> gas flow ratios.

| Ar:O <sub>2</sub> | $D_{it} (\times 10^{11} \text{ eV}^{-1} \cdot \text{cm}^{-2})$ | $C_{ox}$ (nF·cm <sup>-2</sup> ) |

|-------------------|----------------------------------------------------------------|---------------------------------|

| 20:0              | 2.8                                                            | 174                             |

| 20:0.6            | 0.3                                                            | 334                             |

| 20:1.2            | 2.5                                                            | 95                              |

| 20:1.8            | 4.2                                                            | 80                              |

Figure 4. *J-E* profiles of MOS sample prepared at various Ar/O<sub>2</sub> ratios.

Electrical analyses presented above clearly illustrate that the oxygen incorporation during sputtering deposition of a-IGZO layer is a key factor affecting the TFT

performance. Appropriate oxygen incorporation suppressed both the defect trap states in the bulk of a-IGZO layer and at the a-IGZO/SiO $_2$  interface. On the other hand, insufficient oxygen incorporation caused severe derivation of stoichiometry whereas excessive oxygen addition might induce the sputtering etching and degrade the integrity of a-IGZO layer.

In summary, we investigated the effects of oxygen incorporation on the electrical performance of a-IGZO TFTs. The TFT prepared at the condition of Ar/O<sub>2</sub> gas flow ratio = 20:0.6 exhibited the best transfer characteristics with  $\mu_{\rm FE}$ = 5.2 cm<sup>2</sup>·V<sup>-1</sup>·sec<sup>-1</sup>,  $V_{\rm th}$  = 0.7 V, S.S. = 0.9 V·decade<sup>-1</sup> and on/off ratio =  $5\times10^6$ . C-V and I-V measurements also indicated the sample prepared at such a Ar:O<sub>2</sub> gas flow ratio possesses the lowest bulk defect trap and interface trap state as well as the lowest leakage current property. Optimization of oxygen incorporation condition during sputtering is hence a crucial issue for achieving the best electrical performance of a-IGZO TFTs.

## Acknowledgement

This work is supported by the National Science Council (NSC), Taiwan, R.O.C., under contract No. NSC100-2221-E009-055-MY3.

### References

- 1. H. Hosono, J. Non-Cryst. Solids, 352, 851 (2006).

- 2. K. Nomura, H. Ohta, A. Takaji, T. Kamlya, M. Hirano, and H. Hosono, *Nature*, **432**, 488 (2004)

- 3. K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono, *Jpn. J. Appl. Phys.*, **45**, 4303 (2006).

- 4. W. Lim, S. Kim, Y.L. Wang, J. W. Lee, D. P. Norton, S. J. Pearton, F. Ren, and I. I. Kravchenko, *J. Electrochem.*, **155**, H383 (2008).

- 5. A. Suresh and J. F. Muth, *Appl. Phys. Lett.*, **92**, 033502 (2008).

- 6. K.L. Ying, T.-E. Hsieh, and Y.-F. Hsieh, Ceram. Int., 35, 1165-1171 (2009).

- 7. S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3<sup>rd</sup> Ed., Wiley & Sons, New York (2007).

- 8. Y.C. Chang, M.L. Huang K.Y. Lee, Y.J. Lee, T.D. Lin, M. Hong, J. Kwo, T.S. Lay, C.C. Liao, and K.Y. Cheng, *Appl. Phys. Lett.*, **92**, 072901 (2008).