# Statistical Characterization and Modeling of the Temporal Evolutions of $\Delta V_{\rm t}$ Distribution in NBTI Recovery in Nanometer MOSFETs

Jung-Piao Chiu, Yu-Heng Liu, Hung-Da Hsieh, Chi-Wei Li, Min-Cheng Chen, and Tahui Wang, Senior Member, IEEE

Abstract—NBTI trapped charge characteristics and recovery mechanisms are examined by a statistical study of individual trapped charge emissions in nanoscale HfSiON/metal gate pMOS-FETs. We measure individual trapped charge emission times in NBTI recovery in a large number of devices. The characteristic time distributions of the first three emitted holes are obtained. The distributions can be well modeled by using a thermally-assisted tunnel (ThAT) detrapping model. NBTI trapped charge energy and spatial distributions and its activation energy distribution in the ThAT model are discussed and extracted. Based on the ThAT model and measured result of single-charge induced  $V_{\rm t}$  shifts, we develop a statistical NBTI recovery  $\Delta V_{\rm t}$  evolution model. Our model can well reproduce the temporal evolutions of a  $\Delta V_{\rm t}$  distribution in a number of NBTI stressed nanometer MOSFETs in relaxation.

*Index Terms*—Activation energy, charge emission time, negative bias temperature instability, recovery, statistical model.

# I. INTRODUCTION

FGATIVE Bias Temperature Instability (NBTI) has been recognized as one of the most important reliability issues in ultra-thin gate oxide CMOS devices [1]–[4]. The use of a high-k gate dielectric even expedites NBTI degradation [3], [4]. Unlike most reliability effects, NBTI  $V_{\rm t}$  degradation recovers partly after the removal of stress [5]. Several circuit techniques exploiting NBTI recovery have been proposed to alleviate NBTI severity in memory and logic circuits [6], [7]. To improve a design window that is tightened by several variability sources, the integration of NBTI degradation and recovery characteristics into a circuit simulation is called for in modern CMOS circuit design [8]. Hence, underlying degradation and recovery

Manuscript received August 22, 2012; revised January 6, 2013 and January 8, 2013; accepted January 10, 2013. Date of publication February 8, 2013; date of current version February 20, 2013. The authors would like to acknowledge financial support from National Science Council, Taiwan, under contract NSC 99-2221-E-009-169-MY3 and from Ministry of Education in Taiwan under ATU Program. The review of this paper was arranged by Editor B. Kaczer.

J.-P. Chiu, Y.-H. Liu, H.-D. Hsieh, C.-W. Li, and T. Wang are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: twang@cc.nctu.edu.tw).

M.-C. Chen is with National Nano Device Laboratories, Hsinchu 30078, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2013.2240390

mechanisms of NBTI must be understood in order to make a meaningful projection of a device/circuit lifetime. While the reaction-diffusion (RD) model [2], [9]–[11] and a charge trapping model [12]-[17] are commonly adopted for NBTI degradation, no consensus regarding NBTI recovery mechanisms has been reached. Hydrogen back-diffusion in the framework of the RD model was first proposed to explain a NBTI recovery phenomenon [11]. A  $\Delta V_t$  relaxation of the form of  $\Delta V_t(t) =$  $V_t(0)(1-\sqrt{t/2t_0}/\sqrt{1+t/t_0})$  is anticipated from the back diffusion theory. Wang et al. used a fast transient technique to characterize NBTI recovery and found a log(t) dependence of  $\Delta V_{\rm t}$  on relaxation time in a time span from  $10^{-3}$  s to  $10^2$  s [18]. Moreover, they characterized individual trapped hole emissions in small-area devices and proposed a thermally assisted charge tunnel detrapping (ThAT) model for a recoverable component in relaxation [18], [19]. A log(t) dependence was also reported in [20] where the authors proposed a dispersive transport model within the RD framework to overcome the apparent deficiency of the RD model with respect to relaxation time dependence. Alam et al. ascribed a log(t) recovery transient to a fast charge detrapping process on top of slower  $N_{\rm it}$  re-passivation as encapsulated by the RD model [21], [22]. More recently, Grasser et al. used a time dependent defect spectroscopy method to investigate NBTI recovery and concluded that NBTI recovery is due to thermally-assisted discharging of traps and no diffusion process is involved [17]. Their conclusions are consistent with [18].

In most of earlier works, NBTI behavior was characterized in large-area devices [20], [23] and studies were based on an average and continuous  $V_{\rm t}$  evolution [20]–[23]. In contrast, NBTI degradation/recovery proceeds in discrete steps in small area devices [18], [24]. Due to the discrete nature of a  $V_{\rm t}$ evolution, we are able to measure individual trapped charge emission times and each single trapped charge induced  $V_{\rm t}$  shift. Statistical characterization of NBTI degradation/recovery in small area devices therefore provides important information to help understand a responsible mechanism as well as trapped charge characteristics such as trapped charge energy and spatial distributions and its activation energy distribution. Moreover, a NBTI model accounting for an entire  $\Delta V_{\rm t}$  distribution is required in a worst-case circuit simulation. In this paper, a statistical model based on a ThAT model and an extracted activation energy distribution will be developed for a NBTI recovery  $\Delta V_{\rm t}$  distribution and its temporal evolutions.

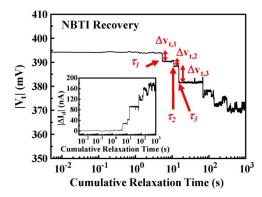

Fig. 1. Example  $\Delta I_{\rm d}$  and  $V_{\rm t}$  traces in NBTI relaxation.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1st, the 2nd and the 3rd trapped hole emission times, respectively.  $\Delta v_{\rm t,i}$  (i=1,2,3) represents a single emitted charge induced threshold voltage shift.

# II. STATISTICAL CHARACTERIZATION OF NBTI RECOVERY

We characterize NBTI recovery in high-k (HfSiON) gate dielectric and metal gate pMOSFETs. The devices have a nominal gate length of 35 nm, a gate width of 70 nm and an effective oxide thickness of  $\sim 1.0$  nm. The devices are first stressed at  $V_{\rm g} = -1.8~{

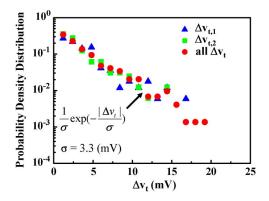

m V}$  for 100 sec. The recovery characterization scheme is similar to [13], i.e., in a relaxation-measurementrelaxation sequence. Both stress and recovery characterizations are performed at room temperature. In measurement phase, the drain voltage is -0.05 V and the gate voltage is chosen such that the pre-stress drain current is  $\sim$ 500 nA. Drain current variations are recorded using Agilent B1500. The cumulative relaxation time in each device measurement is 1000 s. A corresponding  $\Delta V_{\rm t}$  trace is obtained from a measured  $\Delta I_{\rm d}$  divided by a transconductance [25]. Fig. 1 shows example  $\Delta I_{\rm d}$  and  $V_{\rm t}$  traces in NBTI relaxation. Each abrupt  $V_{\rm t}$  change  $(\Delta v_{\rm t,i})$ in the trace is due to a single trapped hole emission, where idenotes a charge detrapping sequence number. Any identifiable RTN signals are not counted. We collect all  $\Delta v_{\rm t,i}$  in  $\sim$ 170 devices. The magnitude distributions of  $\Delta v_{t,1}, \Delta v_{t,2}$  and all collected  $\Delta v_{\rm t}$  are plotted in Fig. 2. Emitted trapped charges have a similar  $\Delta v_{\rm t}$  distribution, characterized by an exponential function  $f(|\Delta v_t|) = \exp(-|\Delta v_t|/\sigma)/\sigma$  with a  $\sigma$  of 3.3 mV. The origins and the distribution of the  $\Delta v_t$  have been studied thoroughly and the exponential distribution is realized due to a random substrate dopant induced current path percolation effect [24], [26].

#### A. Trapped Charge Emission Times

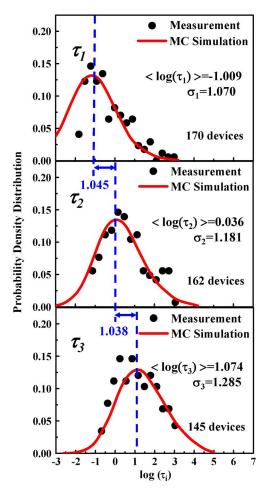

Individual trapped charge emission times, for example,  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  in Fig. 1, are clearly defined. We collect the first three emitted charge characteristic times ( $\tau_i$ , i=1,2,3). The emission characteristic times scatter over several decades of time. The probability density functions (PDFs) of the  $\log(\tau_i)$ , i=1,2,3, are shown in Fig. 3. The mean  $(\langle \log(\tau_i) \rangle)$  and the standard deviation ( $\sigma_i$ ) of the distributions are indicated in the figure. The relationship between the  $\langle \log(\tau_i) \rangle$  (i=1,2,3) is easily identified. The mean increases by the same amount with a sequence number, i.e.,  $\langle \log(\tau_{i+1}) \rangle - \langle \log(\tau_i) \rangle \approx 1.04$ . On the other side, the standard deviation  $\sigma_i$  increases with i from  $\sigma_1 =$

Fig. 2. Magnitude distributions of  $\Delta v_{\rm t,1}$ ,  $\Delta v_{\rm t,2}$  and all collected  $\Delta v_{\rm t,i}$  from NBTI recovery traces in 170 high-k/metal gate pMOSFETs.

Fig. 3. Probability density distributions of a trapped charge (hole) emission time in a  $\log(\tau)$  scale.  $\tau_1$ ,  $\tau_2$  and  $\tau_3$  are the 1st, the 2nd and the 3rd trapped hole emission times, respectively. The mean  $(\langle \log(\tau_i) \rangle)$  and the standard deviation  $(\sigma_i)$  of the distributions are indicated in the figure. The symbols are measurement result and the solid lines are from Monte Carlo simulation.

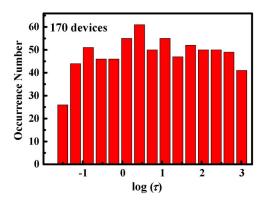

1.070 to  $\sigma_3=1.285$ , but its dependence on a sequence number i is more subtle and requires consideration of trapped charge spatial and energetic distributions and its activation energy. We collect all the charge emission times in about 170 devices and plot their occurrence number distribution in a  $\log(\tau)$  scale in Fig. 4. A rather uniform distribution from  $10^{-2}$  s to  $10^3$  s in Fig. 4 is obtained, implying a  $\log(t)$  dependence of a recovery  $\Delta V_t$  in a large area device.

Fig. 4. Histogram of all trapped charge emission times in a  $\log(\tau)$  scale collected from 170 devices. The occurrence number distribution is rather uniform in a period from  $10^{-2}$  s to  $10^3$  s.

# B. Trapped Charge Spatial and Energy Distributions

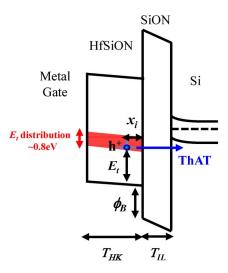

According to the ThAT model [19], a trapped charge tunnel emission time in a high-k MOSFET can be expressed as

$$\tau_i = \tau_0 \exp\left(\frac{E_a}{kT}\right) \exp(\alpha_{\rm IL} T_{\rm IL}) \exp(\alpha_k x_i)$$

(1)

$$\alpha_{\rm IL} = \frac{2\sqrt{2m_{\rm IL}^*q(E_t + \phi_B)}}{\hbar} \tag{1a}$$

$$\alpha_k = \frac{2\sqrt{2m_{\rm HK}^*qE_t}}{\hbar} \tag{1b}$$

where the pre-factor  $\tau_0$  is a lumped parameter,  $E_a$  is activation energy,  $T_{\rm IL}$  is an interfacial layer thickness,  $x_i$  denotes a trapped charge distance to the HK/IL interface and  $E_t$  is a trapped charge energy. Other variables have their usual definitions in [19]. The hole tunneling mass used in this work is  $m_{\rm IL}^*=0.41m_0$  [27] and  $m_{\rm HK}^*=0.18m_0$  [28]. According to (1), a tunneling front moves in a speed of  $d=2.3/\alpha_k$  per decade of time. A removable trapped charge density  $(N_t)$  in relaxation therefore can be extracted from the emission occurrence number versus  $\log(\tau)$  in Fig. 4 as follows:

$$N_t = \frac{\text{no. of emitted charges/device/decade}}{W \times L \times d}$$

$$= \frac{\alpha_k \times (\text{no. of emitted charges/device/decade})}{2.3 \times W \times L}.$$

(2)

Since the number of emitted charges exhibits a uniform distribution approximately in each decade of time in Fig. 4, we obtain a constant removable trapped charge density  $N_t$  in space. With respect to a trapped charge energy distribution, we calculated a voltage drop across an interfacial oxide in NBTI stress by a 2-D numerical device simulation [29]. Quantum corrections are not included in the simulation. The calculated voltage drop is about 0.8 V at a stress  $V_{\rm g}$  of -1.8 V. We therefore assume that removable trapped holes are uniformly distributed in an energy range of 0 to 0.8 eV above the Si valence band-edge, corresponding to an  $E_t$  value of 2.7 eV to 3.5 eV with respect to the valence band-edge of the HfSiON. This assumption is also adopted in [30] and is supported partly

Fig. 5. Schematic representation of a band diagram of a high-k/metal gate pMOSFET in relaxation.  $x_i$  and  $E_t$  represent a trapped charge position and energy

by a charge pumping measurement result [31]. Fig. 5 illustrates a removable trapped charge distribution and a band diagram in recovery. The calculated value of  $\alpha_k$  is from 7.2 to 8.1 nm $^{-1}$ . For simplification, we used an average  $\overline{\alpha_k} (=7.65~\text{nm}^{-1})$  in (2) and obtain a  $N_t$  of  $1.3\times 10^{18}~\text{cm}^{-3}$ . An average distance  $(\Delta x)$  between two adjacent trapped charges in the gate-to-substrate direction is about  $\Delta x = 1/WLN_t \sim 0.32~\text{nm}$ . In addition, the ratio of the emission times of two consecutive emitted trapped charges is

$$\langle \log(\tau_{i+1}) \rangle - \langle \log(\tau_i) \rangle = \frac{1}{2.3} \times [\overline{\alpha_k} \cdot (\langle x_{i+1} \rangle - \langle x_i \rangle)]$$

$$\equiv \frac{1}{2.3} \times (\overline{\alpha_k} \cdot \Delta x). \tag{3}$$

Equation (3) shows that the mean of the  $\log(\tau_i)$  increases with i by the same amount, i.e.,  $\alpha_k \Delta x/2.3 = 1.06$ , without regard to activation energy. Equation (3) is consistent with the measurement result in Fig. 3.

#### C. Activation Energy Distribution

Note that our NBTI emission time model (1), unlike a RTN model, does not have explicit electric field dependence. In contrary, an NBTI emission time model in [17] shows an exponential electric field dependence. The difference is in that a removable trapped hole in our model is assumed in an energy range above the valence band-edge in relaxation (Fig. 5). This assumption is reasonable because of a large voltage drop (0.8 V) across the interfacial oxide in NBTI stress. The measurement results in literature [17], [19] also do not support an exponential field dependence in NBTI recovery. Since an electric field is a secondary effect in NBTI recovery, the wide spread of the trapped charge emission times in NBTI recovery is believed mainly due to an activation energy distribution caused by local chemistry.

From (1),  $E_a$  can be expressed as

$$E_a = kT \left[ 2.3 \log(\tau_i) - 2.3 \log(\tau_0) - \alpha_{\text{IL}} T_{\text{IL}} - \alpha_k x_i \right].$$

(4)

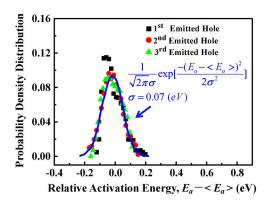

Fig. 6. Relative activation energy  $(E_a - \langle E_a \rangle)$  distributions extracted from the  $\tau_1$ ,  $\tau_2$  and  $\tau_3$ , respectively.  $\tau_0$  in (4) is chosen such that the  $\langle E_a \rangle$  is about 0.5 eV. The solid line is a Gaussian-distribution fit.

To extract an  $E_a$  distribution from the measured  $\tau_i$ , average values of  $\alpha_k$  and  $x_i$  are used in (4) for simplification. The average distance between two consecutive emitted charges is 0.32 nm. The extracted  $E_a$  distributions from  $\tau_1$ ,  $\tau_2$ , and  $\tau_3$ , respectively, are shown in Fig. 6. A good match between them is obtained. It should be remarked that the distortion of the  $E_a$  distribution of i = 1 is understood because our recovery measurement starts with a time delay of 5 ms. Thus, some emitted charges with very short  $\tau$  (< 5 ms) are not counted. In Fig. 6, an appropriate  $\tau_0$  is chosen such that the mean of an  $E_a$  distribution is about 0.5 eV [33]. The solid line in Fig. 6 represents a Gaussian distribution fit with a mean of 0.5 eV and a standard deviation of 0.07 eV. To examine the validity of the  $E_a$  extraction, we re-calculate the  $\tau$ 's distributions based on an extracted  $E_a$  distribution by a Monte Carlo method. In the Monte Carlo procedure, the number of removable trapped charges in each device is selected according to a Poisson distribution [24] with an average number of  $N_tWLT_{HK}$ , where  $T_{\rm HK}$  is the thickness of a high-k dielectric. The use of a Poisson distribution here is an approximation and its correctness has been discussed in [32]. Then, removable trapped charges are randomly placed in the HK layer. For each trapped charge, an  $E_t$  is selected in a range from 2.7 eV to 3.5 eV and an  $E_a$  is selected according to the distribution in Fig. 6. With a trapped charge location, energy and activation energy, an emission time is calculated according to (1). An emission sequence number is then assigned to each trapped charge according to its calculated emission time. A trapped charge with the shortest  $\tau$  has i = 1, and the second shortest one has i = 2 and so on. The Monte-Carlo simulated  $\tau_i$  (i = 1, 2, 3) distributions (solid lines) are plotted in Fig. 3. A reasonable agreement between simulation and measurement is obtained. The broadening of the  $\log(\tau_i)$ with a sequence number i in Fig. 3 can be partly explained as follows. We re-arrange the terms in (4) and obtain the following equation:

$$\log(\tau_i) = \frac{1}{2.3} \left[ \frac{E_a}{kT} + 2.3 \log(\tau_0) + \alpha_{\rm IL} T_{\rm IL} + \alpha_k x_i \right].$$

(5)

As i increases, the tunneling distance  $x_i$  is larger and the variance of the term  $(\alpha_k x_i)$  in the right hand side increases and so does the variance of  $\log(\tau_i)$ .

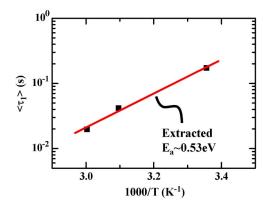

Fig. 7. Dependence of  $\langle \tau_1 \rangle$  on recovery temperature. The extracted activation energy is about 0.53 eV. Each data point is an average of ten readings.

The dependence of a hole emission time on recovery temperature is investigated. The temperature characterization is somewhat difficult because some of NBTI traps might be annealed at high temperatures. For this reason, we chose a single-NBTI trap device. We take an average of  $\tau_1$  from ten measurements on the same device by repeatedly re-filling a NBTI trap, i.e., a refilling-recovery-refilling sequence. The result in Fig. 7 shows a linear relationship between a hole emission time  $\langle \log(\tau) \rangle$  and 1/kT, suggesting a thermally- assisted process and Arrhenius activation energy.

# III. Modeling of a Recovery $\Delta V_{\mathrm{t}}$ Distribution

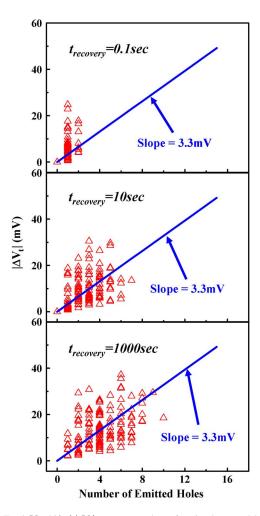

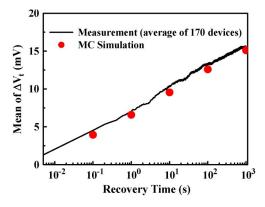

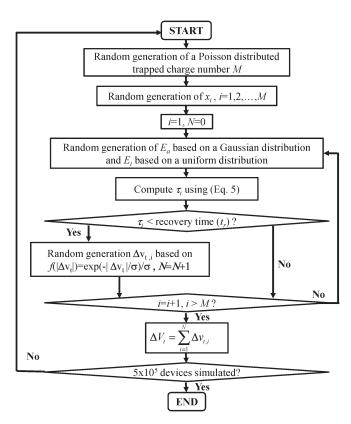

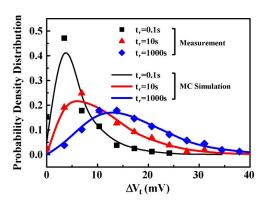

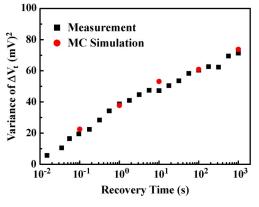

We measure threshold voltage shifts in a large number of devices at different recovery times. The number of emitted holes and a total threshold voltage shift  $(\Delta V_t)$  in each device are recorded. Fig. 8 shows the measurement results at a recovery time of 0.1 sec, 10 sec and 1000 sec. The y-axis is a total  $\Delta V_{\rm t}$  and the x-axis is the number of emitted holes. Each data point represents a device. A straight line with a slope of 3.3 mV, i.e., an average single-charge induced  $V_t$  shift, is drawn in the figure as a reference. The measurement results scatter along the line. The  $\Delta V_{\mathrm{t}}$  and the emitted charge number distributions broaden with recovery time in the measurement period. An average of recovery  $V_{\rm t}$  traces in 170 devices is plotted in Fig. 9, which reflects an observed recovery characteristic in a large-area device. A Monte Carlo  $\Delta V_{\mathrm{t}}$  distribution model based on the ThAT and extracted trapped charge spatial, energetic and activation energy distributions is developed. The simulation flowchart is shown in Fig. 10. For a recovery time  $t_r$ , the number of emitted charges (N) is computed by counting all the charges with  $\tau_i$  less than  $t_r$ . For each emitted charge, a  $\Delta v_{\rm t}$  is randomly selected based on the distribution  $f(|\Delta v_t|) = \exp(-|\Delta v_t|/\sigma)/\sigma$  with  $\sigma = 3.3$  mV. A total  $\Delta V_{\rm t}$  is then calculated as  $\Delta V_{\rm t} = \sum_{i=1}^N \Delta v_{t,i}$ . In total,  $5 \times 10^5$  devices are simulated. The simulated and measured  $\Delta V_{\rm t}$  distributions are shown in Fig. 11 at a recovery time of  $t_r = 0.1$  s, 10 s and 1000 s. Our model is in good agreement with measurement. The mean and the variance of the  $\Delta V_{\rm t}$  distributions versus recovery time are shown in Figs. 9 and 12 for comparison. Our model can reproduce the log(t)

Fig. 8. Total  $V_t$  shift  $(\Delta V_t)$  versus number of emitted trapped holes in a device at a recovery time of 0.1 s, 10 s and 1000 s. Each data point represents a device. A straight line with a slope of 3.3 mV is drawn as a reference.

Fig. 9. Evolution of  $\Delta V_{\rm t}$  with a recovery time. The solid line represents an average of measured  $\Delta V_{\rm t}$  traces in 170 devices. The symbols are the mean of Monte Carlo simulated  $\Delta V_{\rm t}$  distributions. A logarithmic time dependence of  $\Delta V_{\rm t}$  is obtained.

dependence in a large-area device as well as an overall  $\Delta V_t$  distribution and its temporal evolution in small-area devices. In short, the log(t) behavior is a result of a uniform spatial distribution of trapped charges while  $E_a$  and  $E_t$  distributions affect a  $\Delta V_t$  distribution and its temporal evolution in small-area devices.

Fig. 10. Simulation flowchart of a Monte Carlo based  $\Delta V_{\rm t}$  distribution model for NBTI relaxation.

Fig. 11. Probability density distributions of NBTI recovery  $\Delta V_{\rm t}$  in 70 nm  $\times$  35 nm pMOSFETs from measurement and from a Monte Carlo simulation. The recovery time is 0.1 s, 10 s, and 1000 s.

Fig. 12. Variance of a recovery  $\Delta V_{\rm t}$  distribution versus a recovery time in 70 nm  $\times$  35 nm pMOSFETs from measurement and from a Monte Carlo simulation.

#### IV. CONCLUSION

We perform statistical characterization to explore NBTI recovery mechanisms and trapped charge characteristics. Thermally-assisted trapped charge tunnel emission is believed to be a major mechanism in NBTI recovery. We extract trapped charge spatial and activation energy distributions in the ThAT model. A Monte Carlo based statistical model for a  $\Delta V_{\rm t}$  distribution in NBTI relaxation is developed for small area devices. Our model agrees with the measurement result of a  $\Delta V_{\rm t}$  distribution and its temporal evolution in NBTI relaxation very well.

#### REFERENCES

- [1] V. Reddy, A. T. Krishnan, A. Marshall, J. Rodriguez, S. Natarajan, T. Rost, and S. Krishnan, "Impact of negative bias temperature instability on digital circuit reliability," *Microelectron. Reliab.*, vol. 45, no. 1, pp. 31– 38, Jan. 2005.

- [2] M. A. Alam and S. Mahapatra, "A comprehensive model of PMOS NBTI degradation," *Microelectron. Reliab.*, vol. 45, no. 6, pp. 71–81, Jun. 2005.

- [3] S. Zafar, Y. H. Kim, V. Narayanan, C. Cabral, Jr., V. Paruchuri, B. Doris, J. Stathis, A. Callegari, and M. Chudzik, "A comparative study of NBTI and PBTI (charge trapping) in SiO<sub>2</sub>/HfO<sub>2</sub> Stacks with FUSI, TiN, Re Gates," in VLSI Symp. Tech. Dig., 2006, pp. 23–25.

- [4] S. Zafar, A. Kumar, E. Gusev, and E. Cartier, "Threshold voltage instabilities in high-k gate dielectric stacks," *IEEE Trans. Device Mater. Rel.*, vol. 5, no. 1, pp. 45–64, Mar. 2005.

- [5] S. Mahapatra, K. Ahmed, D. Varghese, A. E. Islam, G. Gupta, L. Madhav, D. Saha, and M. A. Alam, "On the physical mechanism of NBTI in silicon oxynitride p-MOSFETs: Can difference in insulator processing conditions resolve the interface trap generation versus hole trapping controversy?" in *Proc. Int. Rel. Phys. Symp.*, 2007, pp. 1–9.

- [6] T. Siddiqua and S. Gurumurthi, "Enhancing NBTI recovery in SRAM arrays through recovery boosting," *IEEE Trans. Very Large Scale Integr.* (VLSI) Syst., vol. 20, no. 4, pp. 616–629, Apr. 2012.

- [7] J. Shin, V. Zyuban, P. Bose, and T. M. Pinkston, "A proactive wearout recovery approach for exploiting micro-architectural redundancy to extend cache SRAM lifetime," in *Proc. Int. Symp. Comput. Archit.*, 2008, pp. 353–362.

- [8] H. Kufluoglu, V. Reddy, A. Marshall, J. Krick, T. Ragheb, C. Cirba, A. Krishnan, and C. Chancellor, "An extensive and improved circuit simulation methodology for NBTI recovery," in *Proc. Int. Rel. Phys. Symp.*, 2010, pp. 670–675.

- [9] K. O. Jeppson and C. M. Svensson, "Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices," *J. Appl. Phys.*, vol. 48, no. 5, pp. 2004–2014, May 1977.

- [10] S. Ogawa and N. Shiono, "Generalized diffusion-reaction model for the low-field charge build up instability at the Si-SiO<sub>2</sub> interface," *Phys. Rev.* B, vol. 51, no. 7, pp. 4218–4230, Feb. 1995.

- [11] M. A. Alam, "A critical examination of the mechanics of dynamic NBTI for PMOSFETs," in *IEDM Tech. Dig.*, 2010, pp. 345–348.

- [12] C. T. Chan, C. J. Tang, T. Wang, H. C.-H. Wang, and D. D. Tang, "Positive bias and temperature stress induced two-stage drain current degradation in HfSiON nMOSFETs," in *IEDM Tech. Dig.*, 2005, pp. 563–566.

- [13] C. T. Chan, C. J. Tang, T. Wang, H. C. -H. Wang, and D. D. Tang, "Characteristics and physical mechanisms of positive bias and temperature stress-induced drain current degradation in HfSiON nMOSFETs," *IEEE Trans. Electron Devices*, vol. 53, no. 6, pp. 1340–1346, Jun. 2006.

- [14] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichiger, P. Hehenberger, P.-J. Wagner, F. Schanovky, J. Franco, M. T. Luque, and M. Nelhiebel, "The paradigm shift in understanding the bias temperature instability: From reaction-diffusion to switching oxide traps," *IEEE Trans. Electron Devices*, vol. 58, no. 11, pp. 3652–3665, Nov. 2011.

- [15] T. Grasser, B. Kaczer, and W. Goes, "An energy level perspective of bias temperature instability," in *Proc. Int. Rel. Phys. Symp.*, 2008, pp. 28–38.

- [16] T. Grasser, B. Kaczer, W. Goes, T. Aichinger, P. Hehenberger, and M. Nelhiebel, "A two-stage model for negative bias temperature instability," in *Proc. Int. Rel. Phys. Symp.*, 2009, pp. 33–44.

- [17] T. Grasser, H. Reisinger, P.-J. Wagner, W. Goes, F. Schanovsky, and B. Kaczer, "The time dependent defect spectroscopy (TDDS) technique for the bias temperature instability," in *Proc. Int. Rel. Phys. Symp.*, 2010, pp. 16–25.

- [18] C. T. Chan, H. C. Ma, C. J. Tang, and T. Wang, "Investigation of post-NBTI stress recovery in pMOSFETs by direct measurement of single oxide charge de-trapping," in VLSI Symp. Tech. Dig., 2005, pp. 90–91.

- [19] T. Wang, C. T. Chan, C. J. Tang, C. W. Tsai, H. C.-H. Wang, M. H. Chi, and D. D. Tang, "A novel transient characterization technique to investigate trap properties in HfSiON gate dielectric mosfets—From single electron emission to PBTI recovery transient," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 1073–1079, May 2006.

- [20] B. Kaczer, V. Arkhipov, R. Degraeve, N. Collaert, G. Groeseneken, and M. Goodwin, "Disorder-controlled-kinetics model for negative bias temperature instability and its experimental verification," in *Proc. Int. Rel. Phys. Symp.*, 2005, pp. 381–387.

- [21] A. E. Islam, H. Kufluoglu, D. Varghese, S. Mahapatra, and M. A. Alam, "Recent issues in negative bias temperature instability: Initial degradation, field dependence of interface trap generation, hole trapping effects and relaxation," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2143–2154, Sep. 2007.

- [22] S. Mahapatra, A. E. Islam, S. Deora, V. D. Maheta, K. Joshi, and M. A. Alam, "A critical re-evaluation of the usefulness of R-D framework in predicting NBTI stress and recovery," in *Proc. Int. Rel. Phys. Symp.*, 2011, pp. 614–623.

- [23] H. Reisinger, O. Blank, W. Heinrigs, A. Muhlhoff, W. Gustin, and C. Schlunder, "Analysis of NBTI degradation- and recovery-behavior based on ultra-fast Vt-measurements," in *Proc. Int. Rel. Phys. Symp.*, 2006, pp. 448–453.

- [24] B. Kaczer, T. Grasser, P. J. Roussel, J. Franco, R. Degraeve, L.-A. Ragnarsson, E. Simoen, G. Groeseneken, and H. Reisinger, "Origin of NBTI variability in deeply scaled pFRTs," in *Proc. Int. Rel. Phys. Symp.*, 2010, pp. 26–32.

- [25] M. Denais, A. Bravaix, V. Huard, C. Parthasarathy, G. Ribes, F. Perrier, Y. Rey-Tauriac, and N. Revil, "On-the-fly characterization of NBTI in ultra-thin gate oxide PMOSFETs," in *IEDM Tech. Dig.*, 2004, pp. 109– 112.

- [26] J. P. Chiu, Y. T. Chung, T. Wang, M. C. Chen, C. Y. Lu, and K. F. Yu, "A comparative study of NBTI and RTN amplitude distributions in high-k gate dielectric pMOSFETs," *IEEE Electron Device Lett.*, vol. 33, no. 2, pp. 176–178, Feb. 2012.

- [27] H. Y. Yu, Y. T. Hou, M. F. Li, and D.-L. Kwong, "Hole tunneling current through oxynitride/oxide stack and the stack optimization for p-MOSFETs," *IEEE Electron Device Lett.*, vol. 23, no. 5, pp. 285–287, May 2002.

- [28] Y. T. Hou, M. F. Li, H. Y. Yu, Y. Jin, and D.-L. Kwong, "Quantum tunneling and scalability of HfO<sub>2</sub> and HfAlO gate stacks," in *IEDM Tech. Dig.*, 2002, pp. 731–734.

- [29] ISE TCAD Manual Release 10.0, Integr. Syst. Eng., Zurich, Switzerland, 2004.

- [30] Z. Q. Teo, D. S. Ang, and G. A. Du, "Observation of two gate stress voltage dependence of NBTI induced threshold voltage shift of ultrathin oxynitride gate P-MOSFET," in *Proc. Int. Rel. Phys. Symp.*, 2009, pp. 1002–1004.

- [31] Y. Y. Liao, S. F. Horng, Y. W. Chang, T. C. Lu, K. C. Chen, T. Wang, and C. Y. Lu, "Profiling of nitride-trap-energy distribution in SONOS flash memory by using a variable-amplitude low-frequency charge-pumping technique," *IEEE Electron Device Lett.*, vol. 28, no. 9, pp. 828–830, Sep. 2007.

- [32] J. P. Chiu, C. W. Li, and T. Wang, "Characterization and modeling of trap number and creation time distributions under negative-bias-temperature stress," *Appl. Phys. Lett.*, vol. 101, no. 8, pp. 082906-1–082906-3, Aug. 2012.

- [33] M. Toledano-Luque, B. Kaczer, E. Simoen, P. J. Roussel, A. Veloso, T. Grasser, and G. Groeseneken, "Temperature and voltage dependences of the capture and emission times of individual traps in high-k dielectrics," *Microelectron. Eng.*, vol. 88, no. 7, pp. 1243–1246, Jul. 2011.

**Jung-Piao Chiu** received the B.S. degree in electronics engineering from National Chiao Tung University, Taiwan, in 2007, and is currently working toward the Ph.D. degree.

His research interests are reliability analysis in advanced CMOS and Flash memory devices.

**Yu-Heng Liu** is currently working toward the Ph.D. degree in the Department of Electronics Engineering and the Institute of Electronic from NCTU, Taiwan.

His research interests are reliability analysis in high-k and NVM devices.

Min-Cheng Chen received Ph.D. degree of electrics institute from National Chiao Tung University, Taiwan, in 2004. Now, he is an associate researcher of National Nano Device Laboratories, Taiwan.

His research interests include nanoelectronic semiconductor devices integration.

**Hung-Da Hsieh** received the M.S. degree in electrics engineering from National Chiao Tung University, Taiwan, in 2012.

His research interests include electric characterization and reliability study of high-k CMOS devices.

**Tahui Wang** (S'85–M'86–SM'94) received the BS degree in electrical engineering from National Taiwan University and the PhD degree from the University of Illinois, Urbana-Champaign.

Currently, he is a Professor at National Chiao-Tung University, and an Editor of IEEE ELECTRON DEVICE LETTERS.

**Chi-Wei Li** is currently working toward the M.S. degree with the Department of Electronics Engineering and the Institute of Electronics from NCTU, Taiwan.

His research interests are reliability analysis in high-k devices and RTN.