# Improving Breakdown Voltage of LDMOS Using a Novel Cost Effective Design

Ming-Hung Han, Hung-Bin Chen, Chia-Jung Chang, Chi-Chong Tsai, and Chun-Yen Chang, Life Fellow, IEEE

Abstract—A reduced surface field (RESURF) laterally diffused metal oxide semiconductor (LDMOS) device with the concept of charge compensation using p-implant layer (PIL) without additional process step is proposed in standard 0.18-\mu m technology. By simply using the p-type drift drain (PDD) implantation of ptype LDMOS into n-type LDMOS, breakdown voltage  $(V_{BD})$  is substantially improved. For a thorough study of device phenomena, hydrodynamic transport simulations are first performed to analyze the electric field distributions at high voltage bias in order to explain increases in breakdown voltage and predict its optimal design parameter. Then fabrication of the devices is performed and shows that the breakdown voltages increase significantly. The measurement results show a 12% improvement in  $V_{BD}$  and a 5% improvement in figure of merit (FOM). Throughout the fabrication process, the enlarged breakdown voltage obtained by the PIL without additional process and device area show the potential of cost effective. Because such devices have good offstate breakdown voltage and specific on-resistance, they are very competitive with similar technologies and promising system-onchip (SOC) applications.

Index Terms—RESURF, LDMOS, implantation, breakdown voltage

#### I. INTRODUCTION

**→** OMPLEMENTARY metal-oxide-semiconductor (CMOS) technologies, which integrate logic circuits, radio frequency (RF) circuits and power switches on a single chip, currently require power devices with reduced specific on-resistance (Ron,sp), improved breakdown voltage (V<sub>BD</sub>) and current driving capability. Suitable power devices using CMOS must be developed to achieve the goal of system-on-chip (SOC) technology [1]-[11], particularly in the low voltage range such as 30 V rating for RF wireless system, display driver, and DC-DC converter applications [12]–[17], [24]–[28]. Recently, laterally diffused-metal-oxidesemiconductor (LDMOS) with double reduced surface field (RESURF) technologies, which using the concept of charge compensation, perform with thin epitaxial layers or well implants to design high-voltage devices with a low R<sub>on,sp</sub>

Manuscript received December 12, 2012; revised January 25, 2013 and March 6, 2013; accepted April 11, 2013. Date of publication April 16, 2013; date of current version May 1, 2013.

C.-Y. Chang, M.-H. Han, and H.-B. Chen are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mails: cyc@mail.nctu.edu.tw; minghung-han@gmail.com; chenlays@hotmail.com).

C.-J. Chang and C.-C. Tsai are with the Himax Technologies, Hsinchu 300, Taiwan (e-mails: cj\_chang@himax.com.tw; cctsai@himax.com.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TSM.2013.2258359

are proposed [18]–[23]. Many studies of double RESURF show that high breakdown voltages can be maintained while increasing drift region doping concentration up to double that in single RESURF devices in order to achieve a good trade-off between off-state V<sub>BD</sub> and R<sub>on,sp</sub>. Additionally, many studies have improved the characteristics of lateral devices with CMOS-compatible processes, including silicon on insulator (SOI) [26]–[28] and Bipolar CMOS (BiCMOS) [29], [30] technologies; however, their novel mask designs, large device areas, and complex processes increase fabrication costs [24]–[30].

In this work, we propose a simple p-implant layer (PIL) implant methodology to implement the idea of charge compensation in RESURF LDMOS devices to improve off-state breakdown voltage and attain low  $R_{on,sp}$  without adding any new process step in standard 0.18- $\mu$ m CMOS technology. The paper is organized as follows. In §2, we describe the device structure, simulation technique, and fabrication process flow. In §3, we study the simulation and experimental results to examine the breakdown voltage with different PIL design. Finally, conclusions and future work are drawn.

# II. SIMULATION METHODOLOGY AND FABRICATION PROCESS

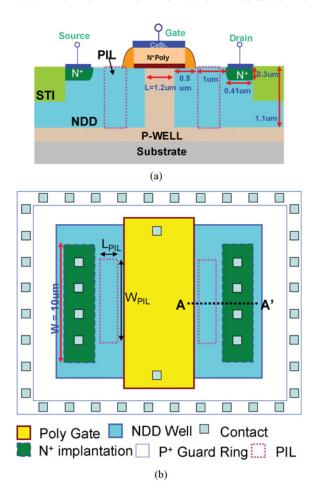

Fig. 1 show the LDMOS device structure and layout design in this work. In simulations of the explored devices have an oxide thickness 45 nm, a channel length (L) of  $1.2 \mu m$ , and a channel width (W) of  $10 \,\mu m$ . The overlap between gate and n-type drift drain (NDD) region is  $0.5 \mu m$ , the space between gate edge and source/drain is  $1 \mu m$ , source/drain junction length and depth are 410 nm and 300 nm, respectively, and the NDD region depth is 1.1  $\mu$ m. The p-well doping concentration is  $2 \times 10^{17} \, \text{cm}^{-3}$ , the doping concentrations in the source, drain and poly-gate are all  $1 \times 10^{20}$  cm<sup>-3</sup>, and the NDD doping concentration in the drift region is  $2 \times 10^{17}$  cm<sup>-3</sup>. To achieve the concept of charge balance, the PIL is used, in which the depth is the same as the NDD region depth, 1.1  $\mu$ m, and the width and length of PIL (W<sub>PIL</sub>, and L<sub>PIL</sub>) are design parameters, as shown in Fig. 1. For accurate numerical results under high voltage conditions, device simulations are performed by solving 3D hydrodynamic transport equations and drift-diffusion equations using commercial tool Synopsys Sentaurus Device [31]. The Shockley-Read-Hall recombination model is considered. Fig. 2 displays the process flow of the proposed n-type LDMOS. The transistor fabrication

Fig. 1. The (a) device structure and parameters and (b) layout design of LDMOS used in this work. The position of p-implant layer (PIL) is also indicated.

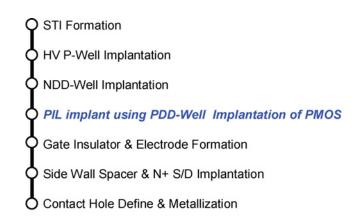

process is based on a 0.18- $\mu$ m high voltage (HV) CMOS technology developed by Maxchip Electronics Corporation. This technology is applicable in both HV LDMOS with and without PIL. The n-type LDMOS is fabricated from a (100) oriented p-type wafer with doping concentration of  $1 \times 10^{15}$  cm<sup>-3</sup>, and the fabrication process begins by defining the active region and then performing shallow trench isolation (STI). The HV p-well ion implantations are then performed. The NDD ion implantation in the drift region is then carried out after the p-well drive-in. For implementation of PIL, the p-type drift drain (PDD) implantation is used when implant PDD region of p-type LDMOS (PMOS). Then gate electrode, nitride spacer side wall, and source/drain annealing are performed. A thick inter-level oxide deposition of TEOS is followed by contact lithography and oxide etching to form the contact window. The final step of the LDMOS transistors fabrication sequence is metallization and passivation.

### III. RESULTS AND DISCUSSIONS

Since the PDD implantation of PMOS is utilized to maintain simple process and low cost, the dose and depth of PIL are thus fixed in this work. To find the optimal design of PIL, we firstly use the simulation to search the highest  $V_{\rm BD}$  by tuning

Fig. 2. The fabrication process flow of the 0.18  $\mu$ m n-type LDMOS device in this work. To implement p-implant layer, we use PDD-Well implantation of p-type LDMOS after NDD-Well implantation.

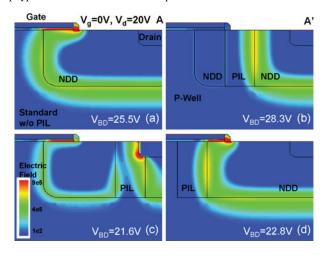

Fig. 3. The simulated electric field distributions of (a) standard device (without PIL), and with PIL located (b) at middle of NDD region, (c) connect to the drain, and (d) connect to the channel at bias condition  $V_g = 0 \, V$  and  $V_d = 20 \, V$ . The VBDs of the devices are shown in the bottom and positions of A and A' are indicated in Fig. 1(b).

the position, width, and length of PIL. The characteristics of simulated standard device are calibrated to that of the experimental data. Fig. 3 compares the electric field distributions of standard (3(a)), PIL locate at the middle of NDD region (3(b)), PIL connect to the drain (3(c)), and PIL connect to the channel (3(d)) before device breakdown ( $V_g = 0V$  and  $V_d = 20V$ ) for discussing the PIL position effect to device V<sub>BD</sub>. The L<sub>PIL</sub> and  $W_{PIL}$  in Fig. 3 are set to 500 nm and 10  $\mu$ m, respectively, and the positions of A and A' are indicated in Fig. 1(b). The off-state ( $V_g = 0 \text{ V}$ ) breakdown voltages which are defined as the voltage at  $I_d = 1\mu A$  in  $I_d$ - $V_d$  curves of different devices are also presented in the bottom of each plot. In Fig. 3(a), it is clearly showed that the electric field concentrates at the channel surface and NDD/P-well junction. Additionally, after the use of PIL in the NDD region, the electric field in channel surface is reduced, therefore, the V<sub>BD</sub> improves significantly, as shown in Fig. 3(b). However, once the PIL connect to the drain, an additional junction is produced, which provide a large electric field due to the large concentration gradient between drain and PIL, result in the degradation of V<sub>BD</sub>, as presented in Fig. 3(c). Fig. 3(d) displays another extreme case, the PIL

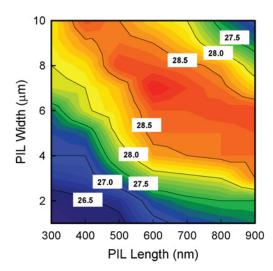

Fig. 4. The contour plot of simulated breakdown voltages of LDMOS with PIL for different PIL length  $L_{\text{PIL}}$  and PIL width  $W_{\text{PIL}}$ .

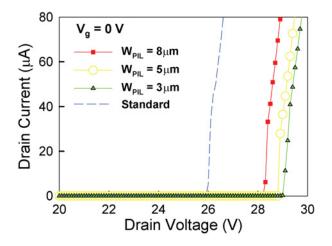

Fig. 5. Measured off-state (Vg = 0 V) I-V characteristic of the LDMOS with different PIL design.

connect to the p-well and directly changes the device channel length. Although the electric field distribution does not greatly alter, since the standard LDMOS device in this work is well designed, the change of channel length substantially affects the device performances, including the V<sub>BD</sub>. On the other hand, it has to mention that although the use of PIL may reduce the current and degrade the Ron,sp owing to the opposite doping type of PIL, since the depth of PIL is the same as NDD region depth, the current distribution in NDD region will not change significantly, thus the current crowding effect in device with PIL is similar to that in standard device when operating near breakdown. Fig. 4 shows the contour plot of V<sub>BD</sub> as a function of LPIL and WPIL with position of PIL located at the center of NDD region (from NDD edge under the gate to drain edge). The simulation results show that if the area of PIL (L<sub>PIL</sub>xW<sub>PIL</sub>) becomes too small or too large, the V<sub>BD</sub> will not improve according to the calculation of Poisson equation for charge balance condition. Moreover, the simulation results also indicate that there provide a large design window to perform  $V_{BD}>28\,V$  (10% improvement). To confirm the simulation

TABLE I SUMMARY OF DEVICES CHARACTERISTICS FOR DIFFERENT PIL DESIGN

| L <sub>PIL</sub> | $W_{PIL}$ | R on,sp         | V <sub>BD</sub> (V) | $V_{\mathrm{BD}}$ | FOM                                     |

|------------------|-----------|-----------------|---------------------|-------------------|-----------------------------------------|

| (µm)             | (μm)      | $m\Omega xmm^2$ |                     | improvement %     | (V <sub>BD</sub> / R <sub>on,sp</sub> ) |

| 0.42             | 8         | 33.3            | 28.1                | 8.9               | 0.84                                    |

| 0.42             | 5         | 20              | 28.6                | 10.8              | 1.43                                    |

| 0.42             | 3         | 14.2            | 28.9                | 12                | 2.04                                    |

| 0*               | 0*        | 13.3            | 25.8                | 0                 | 1.94                                    |

No p-implant layer (PIL), standard device.

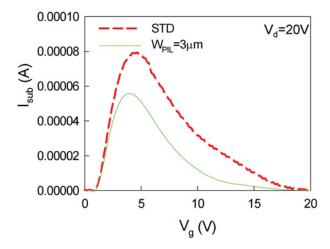

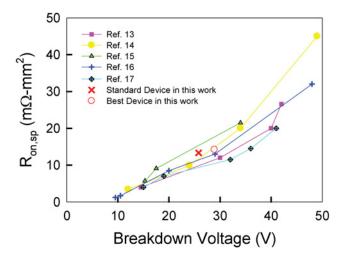

results, three kinds of PIL designed devices are fabricated according to the optimal simulated results. However, due to the position of PIL is important, and considers the thermal diffusion of Boron in PIL when forms the gate insulator/electrode and source/drain implantation annealing, the minimum design rule of  $L_{PIL}$ , 0.42  $\mu$ m, is used. The design parameter in fabricated devices considers the WPIL only, the performances of  $W_{PIL} = 3 \mu m$ , 5  $\mu m$ , and 8  $\mu m$  are measured and discussed. It has to notice that the LPIL and WPIL in fabricated devices are layout dimensions, which may not equal to the physical PIL length and PIL width used in the simulation due to thermal diffusion of Boron in PIL. According to the fabrication experience and theoretical calculation of thermal budget, the physical dimensions of the PIL in fabricated devices are about  $L_{PIL} = 750 \,\text{nm}$ , and  $W_{PIL} = 8.3$ , 5.3, and 3.3  $\mu$ m, respectively. Fig. 5 displays the measured  $I_d$ - $V_d$  characteristics at Vg = 0 Vfor LDMOS devices with different PIL. The off-state breakdown voltages improve about 9%, 11%, and 12% for W<sub>PIL</sub> =  $8 \mu \text{m}$ ,  $5 \mu \text{m}$ , and  $3 \mu \text{m}$ , compare with standard LDMOS. Using PDD-Well implantation of PMOS to perform PIL in ntype LDMOS is a good way to improve V<sub>BD</sub> while maintaining simple process and low cost. Additionally, since the substrate current I<sub>sub</sub> is an important predictor to monitor the device lifetime [32], [33], I<sub>sub</sub> of standard and best device in this work are measured and compared to discuss the reliability of the devices. Although the implantation of PIL may cause damage to the NDD region and degrade the performance, the reduction of measured I<sub>sub</sub> of device with PIL revealing the use of PIL improves the reliability of the device due to the reduced electrical field in NDD region, as demonstrated in Fig. 6. Table I summarizes the comprehensive comparison of electrical characteristics. The Fig. of merit (FOM) which is defined by V<sub>BD</sub>  $/R_{on,sp}$ , is used to evaluate device efficiency. The value of  $R_{on,sp}$ is extracted from  $I_d$ - $V_d$  curve for on-state ( $V_g = 18 \text{ V}$ ) and  $V_d =$ 0.1 V. The best FOM of the devices in this study is 2.04, which is 5% better than that of standard device. Fig. 7 compares the  $R_{on,sp}$  vs  $V_{BD}$  of several LDMOSs in recent years [13]–[17], in which the devices in literatures provide various rated of breakdown voltage. It is a trade-off between breakdown voltage and specific on-resistance. The devices in this work show competitive with respect to similar technologies and device with  $W_{PIL} = 3 \mu m$  improves  $V_{BD}$  significantly which keep the comparable R<sub>on,sp</sub>.

## IV. CONCLUSION AND FUTURE WORK

This study successfully implemented a RESURF LDMOS device with PIL in standard  $0.18-\mu m$  technology. By simply

Fig. 6. Measured substrate currents I<sub>sub</sub> of the standard and best LDMOSs.

Fig. 7. Comparison of  $R_{on,sp}$  vs  $V_{BD}$  between devices in this work and similar technologies.

using the PDD implantation of p-type LDMOS as PIL into NDD region of n-type LDMOS, a device fabricated with best PIL area achieves a  $V_{\rm BD}$  improvement of 12% with a small increase of  $R_{\rm on,sp}$ . Throughout the whole fabrication process, no additional process step and not increase in device area are required. Because of their good off-state  $V_{\rm BD}$  and  $R_{\rm on,sp}$ , the devices have potential use in SOC applications. We are currently working on using NDD implantation into PMOS with the same idea proposed in this work, which may improve the performances of PMOS simultaneously for CMOS application.

### ACKNOWLEDGMENT

The authors would like to thank the Maxchip Electronics Corp. for devices fabrication and many useful discussions.

#### **REFERENCES**

- A. A. Abidi, "RF CMOS Comes of Age," *IEEE J. Solid-State circuits*, vol. 39, no. 4, pp. 549–561, Apr. 2004.

- [2] L. Lorenz, G. Deboy, A. Knapp, and M. Marz, "COOLMOS<sup>TM</sup>- a new milestone in high voltage power MOS," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 1999, pp. 3–10.

- [3] M. Shindo, M. Morikawa, T. Fujioka, K. Nagura, K. Kurotani, K. Odaira, T. Uchiyama, and I. Yoshida, "High power LDMOS for cellular base station applications," in *Proc. Int. Symp. Power Semiconductor Devices* ICs, May 2001, pp. 107–110.

- [4] X.-B. Chen and J. K. O. Sin, "Optimization of the specific on-resistance of the COOLMOSTM," *IEEE Trans. Electron. Devices*, vol. 48, no. 2, pp. 344–348, Feb. 2001.

- [5] J. Cai, C. Ren, N. Balasubramanian, and J. K. O. Sin, "A novel high performance stacked LDD RF LDMOSFET," *IEEE Electron. Device Lett.*, vol. 22, no. 5, pp. 236–238, May 2001.

- [6] J. Ramos and M. Steyaert, "STI/LOCOS compatible LDMOS structure in standard CMOS," *Electron. Lett.*, vol. 39, no. 19, pp. 1417–1418, Sep. 2003

- [7] J. Scholvinl, D. R. Greenberg, and J. A. del Alamo, "RF power potential of 90 nm CMOS: Device options, performance, and reliability," in *Proc. IEDM Symp. Tech. Dig.*, Dec. 2004, pp. 455–458.

- [8] A. Moscatelli, C. Contiero, P. Galbiati, and C. Raffaglio, "A 12V complementary RF LDMOS technology developed on a 0.18 um CMOS platform," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2004, pp. 37–40.

- [9] T. Yan, H. Liao, Y. Z. Xiong, R. Zeng, J. Shi, and R. Huang, "Cost-effective integrated RF power transistor," *IEEE Electron. Device Lett.*, vol. 27, no. 10, pp. 856–858, Oct. 2006.

- [10] S.-Y. Huang, K.-M. Chen, G.-W. Huang, C.-Y. Chang, C.-C. Hung, V. Liang, and B.-Y. Chen, "Design for integration of RF power transistors in 0.13 um advanced CMOS technology," in *Proc. IEEE Microwave Theory Tech. Symp.*, Jun. 2007, pp. 323–326.

- [11] H. Xiao, L. Zhang, R. Huang, F. Song, D. Wu, H. Liao, W. Wong, and Y. Wang, "A novel RF LDMOS fabricated with standard foundry technology," *IEEE Electron. Device Lett.*, vol. 30, no. 4, pp. 386–388, Apr. 2009.

- [12] S. Ono, Y. Yamaguchi, Y. Kawaguchi, and A. Nakagawa, "30 V Sub-micron shallow junction planar-MOSFET for DC-DC converters," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2004, pp. 401–404.

- [13] S. Pendharkar, R. Pan, T. Tamura, B. Todd, and T. Efland, "7 to 30 V state-of-art power device implementation in 0.25pm LBC7 BiCMOS-DMOS process technology," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2004, pp. 419–422.

- [14] D. Riccardi, A. Causio, I. Filippi, A. Paleari, L. Vecchi, A. Pregnolato, P. Galbiati, and C. Contiero, "BCD8 from 7 V to 70 V: a new 0.18 μm technology platform to address the evolution of applications towards smart power ICs with high logic contents," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2007, pp. 73–76.

- [15] I.-Y. Park, Y.-K. Choi, K.-Y. Ko, C.-J. Yoon, B.-K. Jun, M.-Y. Kim, H.-C. Lim, N.-J. Kim and K.-D. Yoo, "BD180 a new 0.18 μm BCD (Bipolar-CMOS-DMOS) technology from 7 V to 60 V," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2008, pp. 64–67.

- [16] K. Shirai, K. Yonemura, K. Watanabe, and K. Kimura, "Ultra-low on-resistance LDMOS implementation in 0.13μm CD and BiCD process technologies for analog power IC's," in *Proc. Int. Symp. Power Semi-conductor Devices ICs*, May 2009, pp. 77–80.

- [17] K.-Y. Ko, I.-Y. Park, Y.-K. Choi, C.-J. Yoon, J.-H. Moon, K.-M. Park, H.-C. Lim, S.-Y. Park, N.-J. Kim, K.-D. Yoo, and L. N. Hutter, "BD180LV-0.18 um BCD technology with best-in-class LDMOS from 7 V to 30 V," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2010, pp. 71–74.

- [18] A. W. Ludikhuize, "A review of RESURF technology," in Proc. Int. Symp. Power Semiconductor Devices and ICs, May 2000, pp. 11–14.

- [19] D. R. Disney, A. K. Paul, M. Darwish, R. Basecki, and V. Rumennik, "A new 800V lateral MOSFET with dual conduction paths," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2001, pp. 399–402.

- [20] M.-H. Kim, J.-J. Kim, Y.-S. Choi, C.-K. Jeon, S.-L. Kim, H.-S. Kang, and C.-S. Song, "A low on-resistance 700 V charge balanced LDMOS with intersected well structure," in *Proc. Eur. Solid-State Device Res. Conf.*, Sep. 2002, pp. 367–370.

- [21] L. Vestling, J. Olsson, and K.-H. Eklund, "Drift region optimization of lateral RESURF devices," *Solid-State Electron.*, vol. 46, no. 8, pp. 1177–1184, Aug. 2002.

- [22] M. Imam, Z. Hossain, M. Quddus, J. Adams, C. Hoggatt, T. Ishiguro, and R. Nair, "Design and optimization of double-RESURF high-voltage lateral devices for a manufacturable process," *IEEE Trans. Electron Devices*, vol. 50, no. 7, pp. 1697-1701, Jul. 2003.

- [23] G. Sheu, S.-M. Yang, Y.-F. Chang, and S.-C. Tsaur, "An analytical model of surface electric field distributions in ultrahigh-voltage buried p-top lateral diffused metal–oxide–semiconductor devices," *Jpn. J. Appl. Phys.*, vol. 49, no. 7, pp. 074301–074308, Jul. 2010.

- [24] H. Wang, H. P. E. Xu, W. T. Ng, K. Fukumoto, K. Abe, A. Ishikawa, Y. Furukawa, H. Imai, T. Naito, N. Sato, K. Sakai, S. Tamura, and K. Takasuka, "A novel orthogonal gate edmos transistor with improved dv/dt capability and figure of merit (FOM)," *IEEE Electron. Device Lett.*, vol. 29, no. 12, pp. 1386–1388, Dec. 2008.

- [25] S.-Y. Huang, C.-C. Hung, V. Liang, W.-S. Liao, T.-L. Li, J.-H. Li, C.-Y. Tzeng, G.-W. Huang, and K.-M. Chen, "Novel pseudo-drain (PD) RF power cell in 0.13 um CMOS technology," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, 2008, pp. 259–262.

- [26] S. Matsumoto, Y. Hiraoka, T. Sakai, T. Yachi, T. Ishiyama, T. Kosugi, and M. Muraguchi, "A quasi-SOI power MOSFET for radio frequency applications formed by reversed silicon wafer direct bonding," *IEEE Trans. Electron. Devices*, vol. 48, no. 7, pp. 1448–1453, Jul. 2001.

- [27] S. Matsumoto and M. Mino, "Impact of the pattern layout on radio-frequency performance of thin-film SOI power MOSFETs," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2004, pp. 245–248.

- [28] O. Bon, O. Gonnard, F. Gianesello, C. Raynaud, and F. Morancho, "First 15 V complementary LDMOS transistors in thin SOI 65 nm low power technology," in *Proc. Int. Symp. Power Semiconductor Devices ICs*, May 2007, pp. 209–212.

- [29] K.-E. Ehwald, B. Heinemann, W. Roepke, W. Winkler, H. Rucker, F. Fuernhammer, D. Knoll, R. Barth, B. Hunger, H. E. Wulf, R. Pazirandeh, and N. Ilkov, "High performance RF LDMOS transistors with 5 nm gate oxide in a 0.25 pm SiGe:C BiCMOS technology," in *IEDM Symp. Tech. Dig.*, Dec. 2001, pp. 895–898.

- [30] D. Muller, A. Giry, F. Judong, C. Rossato, F. Blanchet, B. Szelag, A. Monroy Aguirre, R. Sommet, D. Pache, and O. Noblanc, "High-performance 15-V novel LDMOS transistor architecture in a 0.25-μm BiCMOS process for RF-Power applications," *IEEE Trans. Electron. Devices*, vol. 54, no. 4, pp. 861–868, Apr. 2007.

- [31] User's Manual for Synopsys Sentaurus Device.

- [32] C.Hu, S. C. Tam, F.-C. Hsu, P.-K. Ko, T.-Y. Chan, and K. W. Terrill, "Hot-electron-induced MOSFET degradation-model, monitor, and improvement," *IEEE Trans. Electron. Devices*, vol. 32, no. 2, pp. 375–385, Feb. 1985.

- [33] C.-C. Cheng, J.F Lin, and T. Wang, "Impact of self-heating effect on hot carrier degradation in high-voltage LDMOS," in *IEDM Symp. Tech. Dig.*, Dec. 2007, pp. 881–884.

Ming-Hung Han is pursuing the Ph.D. degree at the Institute of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan. His current research interests include modeling and simulation of semiconductor nanodevices and circuits, high voltage power CMOS, and Si-based solar cell.

**Hung-Bin Chen** is pursuing the Ph.D. degree at the Institute of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan. His current research interests include the study and investigation of junctionless nanodevices, high voltage power CMOS, and flash memories.

Chia-Jung Chang is with Himax Technologies, Hsinchu, Taiwan.

Chi-Chong Tsai is the Vice President of Himax Technologies, Hsinchu,

Chun-Yen Chang (F'88–LF'05) has contributed to microelectronics, microwave, and optoelectronics, including the establishment of the first Si planar center (1964) at National Chiao Tung University (NCTU), the first MOSFET (1966), the first LED (1970), the quantum transport for metal-semiconductor (MS) (1970), and the MS contact theory (1971), which formed the strong VLSI for Taiwanese hi-tech industries. He was the Founding Director of National Nano Device Laboratories (1988), the President of the NCTU (1998), an initia-

tor of the "National System on Chip Program" (2002), and a Foreign Associate of the National Academy of Engineering U.S.A. (2000).