# Symmetric Vertical-Channel Nickel-Salicided Poly-Si Thin-Film Transistors With Self-Aligned Oxide Overetching Structures

Yi-Hong Wu, Po-Yi Kuo, *Associate Member, IEEE*, Yi-Hsien Lu, Yi-Hsuan Chen, Tsung-Yu Chiang, Kuan-Ti Wang, Li-Chen Yen, and Tien-Sheng Chao

Abstract—This paper reports the impacts of NH $_3$  plasma treatment time, oxide overetching depth, and gate oxide thickness on symmetric vertical-channel Ni-salicided poly-Si thin-film transistors (VSA-TFTs) for the first time. OFF-state currents may be improved by increasing the oxide overetching depth. The ON/OFF current ratio may be also improved by increasing the oxide overetching depth. The NH $_3$  plasma optimum treatment time of VSA-TFTs is significantly shorter than that of conventional topgate horizontal-channel TFTs. The performance of VSA-TFTs is degraded by NH $_3$  plasma treatment for too long a time. VSA-TFTs with 15-nm gate oxide thickness display better subthreshold swing (< 150 mV/dec) than VSA-TFTs with 30-nm gate oxide thickness. OFF-state currents can be improved by increasing  $L_{\rm mask}$ , even when the oxide overetching depth and the gate oxide thickness are changed.

Index Terms—NH<sub>3</sub> plasma treatment, Ni-salicided, oxide overetching depth, polycrystalline-silicon thin-film transistors (poly-Si TFTs), vertical channel, vertical-channel Ni-salicided poly-Si TFTs (VSA-TFTs).

# I. INTRODUCTION

ECENTLY, polycrystalline-silicon thin-film transistors (poly-Si TFTs) have attracted considerable attention because of their diversity of applications, including nanowire transistor, nonvolatile memory, and 3-D circuit integration [1]–[7]. One effective approach to obtaining high-performance poly-Si TFTs and enhancing device density is to scale down the channel length. However, it is difficult to reduce channel length due to the limits of photolithography resolution. Therefore, vertical-channel thin-film transistors (VTFTs) have been widely researched and developed to overcome the limits of photolithography [8]-[10]. In these previous works, VTFTs have shown great potential for 3-D integration since the channel lengths are determined by the thicknesses of the poly-Si or silicondioxide film, instead of photolithographic process limitations. However, these works using asymmetric source/drain (S/D) have encountered circuit design difficulties. S/D parasitic series resistance and contact resistance remain problems for device scaling and reduce device performance.

Manuscript received January 14, 2011; revised March 10, 2011 and March 30, 2011; accepted April 4, 2011. Date of publication May 10, 2011; date of current version June 22, 2011. This work is supported by the National Science Council, Taiwan, under Contract NSC-97-2221-E-009-152-MY3. The review of this paper was arranged by Editor A. Schenk.

The authors are with the Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: Kuopoyi.ee91g@gmail.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2142312

Conventional top-gate poly-Si TFTs suffer from large OFF-state leakage currents due to their high electric field in the drain depletion region, which results in field emission via grain boundary traps [11], [12]. In order to reduce the leakage currents, a variety of methods have been proposed to reduce the electric field near the drain region, including the lightly doped drain, field-induced drain, high-k spacer offset-gated structure, and Si/Ge T-Gate structure [13]–[17]. Nevertheless, those structures require additional masks or extra materials (HfO<sub>2</sub>, Ge), complicating fabrication processes.

It is well known that the numerous grain boundaries and intragranular defects in poly-Si channel film result in the degradation of poly-Si TFT performance. To achieve high-performance poly-Si TFTs, it is necessary to reduce the defects in the poly-Si channel film. Hence, many plasma treatment methods are used to passivate the defects in the poly-Si channel film, including  $H_2$ ,  $O_2$ ,  $N_2$ , and  $NH_3$  plasmas [18]–[24]. Based on the literatures, the  $NH_3$  plasma treatment offers better performance enhancement, hot-carrier stress endurance, and thermal stability than other plasma treatment methods.

In our previous work, the VSA-TFTs have been successfully fabricated and demonstrated [25]. The parasitic series resistance of S/D and the floating  $n^+$  region may be significantly reduced by Ni-salicidation, resulting in improved ON-state currents. The ON-state currents will not be limited by the parasitic series resistance of S/D and the floating  $n^+$  region when the gate bias is increased. The OFF-state currents can be improved by modifying the oxide overetching, the equivalent dual-gate structure, and the floating  $n^+$  region length without additional masks. The performance can be improved by increasing the NH $_3$  plasma treatment time in the conventional top-gate horizontal-channel TFTs [23], [24].

However, the effects of  $NH_3$  plasma treatment time on the VSA-TFTs were not investigated in our previous work. In this paper, the  $n^+$  S/D and floating  $n^+$  region of VSA-TFTs were fully Ni-salicided. We study the effects of  $NH_3$  plasma treatment time, oxide overetching depth, and gate oxide thickness on the VSA-TFTs with self-aligned oxide overetching structures for the first time.

## II. EXPERIMENT

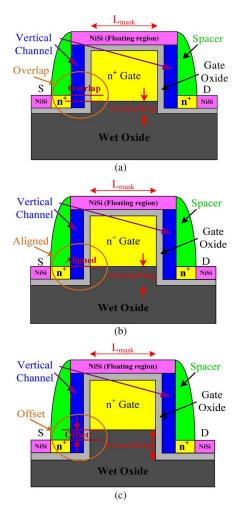

Fig. 1 shows a schematic cross-sectional diagram of VSA-TFTs with 30-nm gate oxide thickness, 50-nm channel thickness, and oxide overetching depths of about (a) 40, (b) 80,

Fig. 1. Schematic cross-sectional diagram of VSA-TFTs with 30-nm gate oxide thickness, 50-nm channel thickness, and oxide overetching depths of about (a) 40, (b) 80, and (c) 120 nm.

and (c) 120 nm. In Fig. 1(a), VSA-TFTs with 40-nm oxide overetching depth showing a roughly 40-nm overlap region between the gate and S/D n<sup>+</sup> edges are designated "overlap VSA-TFTs." VSA-TFTs with 80-nm oxide overetching depth showing an aligned gate and S/D n<sup>+</sup> edges are designated "alignment VSA-TFTs" [see Fig. 1(b)]. VSA-TFTs with 120-nm oxide overetching depth showing a roughly 40-nm offset region between the gate and S/D n<sup>+</sup> edges are designated "offset VSA-TFTs" [see Fig. 1(c)]. Furthermore, VSA-TFTs with 15-nm gate oxide thickness, 50-nm channel thickness, and 80-nm oxide overetching depth are designated "GO-15-nm VSA-TFTs." The GO-15-nm VSA-TFTs also have a 15-nm offset region between the gate and S/D n<sup>+</sup> edges. Conventional top-gate horizontal-channel devices with a gate oxide of 15 nm, a self-aligned n<sup>+</sup> S/D, and Ni-salicided processes were also fabricated to serve as controls. Finally, all the devices were fabricated using NH<sub>3</sub> plasma treatment (NH<sub>3</sub> plasma treatment times will be discussed in Section III). The key processes of VSA-TFTs were discussed in detail in our previous work [25]. We fabricated all devices under identical process conditions, and all process temperatures were below 700 °C.

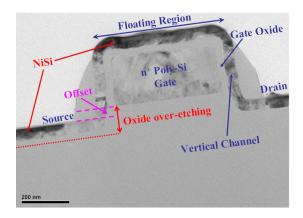

Fig. 2 shows the cross-sectional transmission electron microscope (TEM) microphotograph of the offset VSA-TFTs with fully Ni-salicided  $n^+$  S/D and an floating  $n^+$  region. In the

Fig. 2. Cross-sectional TEM microphotograph of offset VSA-TFTs with fully Ni-salicided  $n^+$  S/D and a floating  $n^+$  region.

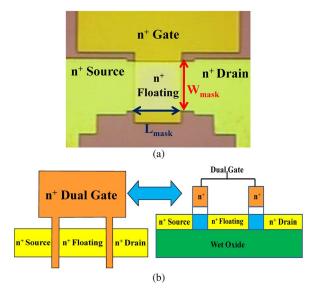

Fig. 3. (a) Top-view optical microscope microphotograph of VSA-TFTs without Ni-salicidation and (b) effective dual-gate structure of VSA-TFTs.

VSA-TFTs, the poly-Si thickness in the channel is 50-nm, and the effective channel length  $L_{\rm eff}$  is defined by  $2\times$  the total thickness of the poly-Si gate (about 200 nm). The offset between gate and S/D n<sup>+</sup> edges was achieved by modifying wet oxide over etching resulting in about 40-nm offset region. Fig. 3 displays the top-view optical microscope microphotograph of VSA-TFTs without Ni-salicidation and effective dual gate structure of VSA-TFTs. The VSA-TFTs inherently own an effective dual gate structure. The length of floating n<sup>+</sup> region is defined by mask channel length  $L_{\rm mask}$ , whereas the mask channel width  $W_{\rm mask}$  is equal to the effective channel width [see Fig. 3(a)]. The equivalent dual-gate structure [see Fig. 3(b)] can moderate the lateral electrical field in the drain depletion region, significantly reducing leakage currents and increasing the ON/OFF current ratio [26], [27].

# III. RESULTS AND DISCUSSION

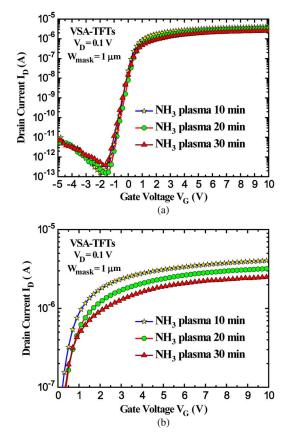

Fig. 4 displays the transfer characteristics of the VSA-TFTs with different  $NH_3$  plasma treatment times, along with an enlarged ON-state currents graph of the VSA-TFTs with different  $NH_3$  plasma treatment times. VSA-TFTs fabricated with a 10-min  $NH_3$  plasma treatment time have lower OFF-state

Fig. 4. (a) Transfer characteristics and (b) enlarged ON-state currents graph of the VSA-TFTs with different  $NH_3$  plasma treatment times.

currents (defined as the minimum drain currents) and higher ON-state currents than VSA-TFTs fabricated with other NH<sub>3</sub> plasma treatment times. This is attributed to the hydrogen passivation of the defect states, the nitrogen pileup at the SiO<sub>2</sub>/poly-Si interface, and the strong Si–N bond formation that terminates the dangling bonds in the grains and at the grain boundaries in the channel region [23], [24]. Because the poly-Si channels are deposited after the gate oxide in VSA-TFTs, the exposed poly-Si channels are easily damaged under too long NH<sub>3</sub> plasma treatment time, resulting in poor electric characteristics. The mechanisms of the damage to the gate oxide integrity and the SiO<sub>2</sub>/poly-Si interface during long NH<sub>3</sub> treatment times include electrostatic charging damages [28]. Therefore, we believe that NH<sub>3</sub> plasma treatment time of 10 min is the optimum condition for the VSA-TFTs in this independent experiment.

By the same token, the hidden poly-Si channels under the top gate in conventional devices require longer  $NH_3$  plasma treatment times to achieve improved characteristics [23], [24]. We used 30-min  $NH_3$  plasma treatment times to passivate the conventional top-gate horizontal-channel TFTs. The  $NH_3$  plasma optimum treatment time of VSA-TFTs is significantly shorter than that of conventional top-gate horizontal-channel TFTs.

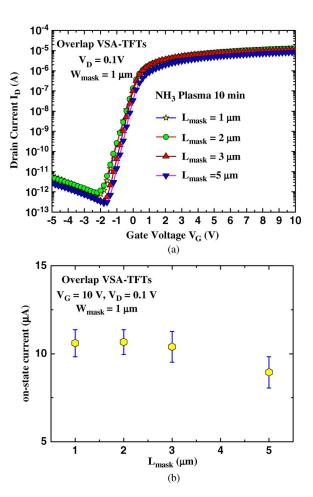

Fig. 5 shows the transfer characteristics and the ON-state current distribution of overlap VSA-TFTs with  $W_{\rm mask}=1~\mu{\rm m}$  and different  $L_{\rm mask}$ . The OFF-state currents can be improved by increasing the  $L_{\rm mask}$ . This may be attributed to the mitigation of the OFF-state peak lateral electric field in the drain depletion region [25]. In Fig. 5(b), the ON-state currents are degreased with increasing  $L_{\rm mask}$ . The ON-state currents can be main-

Fig. 5. (a) Transfer characteristics and (b) ON-state current distribution of overlap VSA-TFTs with  $W_{\rm mask}=1~\mu{\rm m}$  and different  $L_{\rm mask}$ .

tained at approximately the same value from  $L_{\rm mask}=1~\mu{\rm m}$  to  $L_{\rm mask}=2~\mu{\rm m}$  due to the Ni-silicidation in the floating n<sup>+</sup> region. However, the ON-state currents are slightly degraded when  $L_{\rm mask}=3~\mu{\rm m}$  and significantly degraded when  $L_{\rm mask}=5~\mu{\rm m}$ . This result is consistent with Fig. 5(a). The series resistance in the floating n<sup>+</sup> region rises with increasing  $L_{\rm mask}$ , and therefore,  $L_{\rm mask}$  may not be indefinitely increased.

We believe that the value of a subthreshold swing (S.S.) may indicate the gate control ability in the channel. It is easier to lose the gate control ability in shorter channel devices, resulting in degradation of the S.S. The VSA-TFTs with small  $L_{\rm mask}$  have shorter effective channel lengths than the VSA-TFTs with large  $L_{\rm mask}$ , and thus have more serious short-channel effects. VSA-TFTs with large  $L_{\rm mask}$  can suppress the short-channel effect resulting in improved S.S. The overlap VSA-TFTs with  $L_{\rm mask}=3~\mu{\rm m}$  have good S.S. (S.S. = 292 mV/dec) and the largest ON/OFF current ratio. Accordingly, the optimum value of  $L_{\rm mask}$  is 3  $\mu{\rm m}$  in this paper.

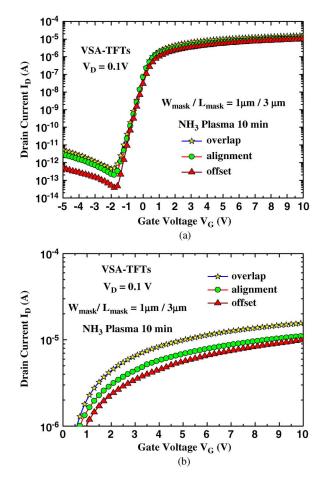

Fig. 6 exhibits the transfer characteristics and the enlarged ON-state currents graph of VSA-TFTs with  $W_{\rm mask}/L_{\rm mask}=1~\mu{\rm m}/3~\mu{\rm m}$  and various oxide overetching depths. The OFF-state currents can be improved by increasing the oxide overetching depth. The electric field in the drain depletion region may be diminished as a result of increasing the offset region between the gate and the S/D n<sup>+</sup> edges [13]–[17]. However, the ON-state currents will be reduced by increasing

Fig. 6. (a) Transfer characteristics and (b) enlarged ON-state currents graph of the VSA-TFTs with  $W_{\rm mask}/L_{\rm mask}=1~\mu{\rm m}/3\mu{\rm m}$  and various oxide overetching depths.

the oxide overetching depth [see Fig. 6(b)]. The overlap VSA-TFTs have higher ON-state current than the alignment and offset VSA-TFTs due to shorter effective channel length. The offset VSA-TFTs have the lowest ON-state currents, caused by the series resistance in the offset region. The offset VSA-TFTs can suppress the short-channel effect, resulting in improved S.S. Although the ON-state currents of offset VSA-TFTs are slightly smaller than the others, the offset VSA-TFTs display an obvious improvement in the OFF-state currents resulting in the largest ON/OFF current ratio, exceeding  $10^8$ .

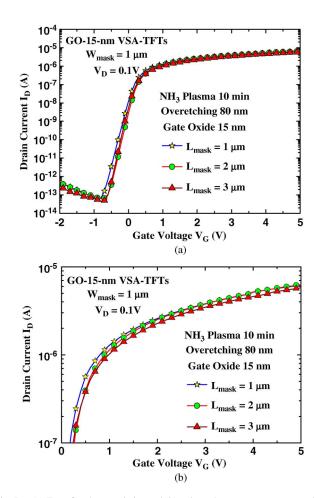

Fig. 7 shows the transfer characteristics and the enlarged ON-state currents graph of the GO-15-nm VSA-TFTs with  $W_{\rm mask}=1~\mu{\rm m}$  and different  $L_{\rm mask}$ . The OFF-state currents can be improved by increasing the  $L_{\rm mask}$ , and the ON-state currents are nearly identical. The enlarged ON-state currents graph shows that the ON-state currents of the various  $L_{\rm mask}$  are different. However, the difference in the ON-state currents for the various  $L_{

m mask}$  is very small. Hence, the ON-state currents can be maintained at the same level from the  $L_{\rm mask}=1~\mu{\rm m}$ to the  $L_{\rm mask}=3~\mu{\rm m}$ . These results are consistent with Fig. 5 and our previous work, implying that VSA-TFTs can improve the OFF-state currents by increasing  $L_{

m mask}$ , even though the thermal oxide overetching depth and the gate oxide thickness are changed. Moreover, the S.S. of the GO-15-nm VSA-TFTs with  $L_{\text{mask}} = 1 \ \mu\text{m}$  is 144 mV/dec, the S.S. of the GO-15-nm VSA-TFTs with  $L_{\rm mask}=2~\mu{\rm m}$  is 130 mV/dec, and the S.S. of

Fig. 7. (a) Transfer characteristics and (b) enlarged ON-state currents graph of the GO-15-nm VSA-TFTs with  $W_{\rm mask}=1~\mu{\rm m}$  and different  $L_{\rm mask}$ .

the GO-15-nm VSA-TFTs with  $L_{\rm mask}=3~\mu{\rm m}$  is 127 mV/dec. The GO-15-nm VSA-TFTs with  $L_{\rm mask}=1~\mu{\rm m}$  have shorter effective channel lengths and more serious short-channel effects than the others, resulting in degradation of S.S. The S.S. of the GO-15-nm VSA-TFTs is better than that of the offset VSA-TFTs (the S.S. of the offset VSA-TFT with  $L_{\rm mask}=3~\mu{\rm m}$  is 269 mV/dec). In other words, the GO-15-nm VSA-TFTs have better gate control ability than the offset VSA-TFTs due to their thinner gate oxide thickness. Therefore, the S.S. in the VSA-TFTs can be improved by decreasing the gate oxide thickness.

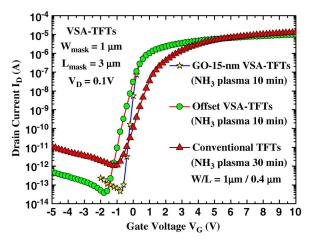

Fig. 8 displays the transfer characteristics of GO-15-nm VSA-TFTs and offset VSA-TFTs with  $W_{\rm mask}/L_{\rm mask}=1~\mu{\rm m}/3\mu{\rm m}$ . The transfer characteristics of conventional TFTs with  $W_{\rm mask}/L_{\rm mask}=1~\mu{\rm m}/0.4~\mu{\rm m}$  are also shown for comparison. It is obvious that the GO-15-nm VSA-TFTs and the offset VSA-TFTs outperform conventional TFTs. The conventional TFTs have slightly higher ON-state currents only in the high gate voltage due to their shorter effective channel length.

Several important parameters of GO-15-nm VSA-TFTs, offset VSA-TFTs, and conventional top-gate horizontal-channel TFTs are listed in Table I.  $I_{\rm on}$  is defined as the drain current at  $V_G=5$  V and  $V_D=0.1$  V, whereas  $I_{\rm off}$  is defined as the minimum drain current at  $V_D=0.1$  V. In Table I, the field-effect mobility of GO-15-nm VSA-TFTs is smaller than that of the offset VSA-TFTs. We believe that the vertical electric field of the channels in the GO-15-nm VSA-TFTs is

Fig. 8. Transfer characteristics of GO-15-nm VSA-TFTs and offset VSA-TFTs with  $W_{\rm mask}/L_{\rm mask}=1~\mu{\rm m}/3\mu{\rm m}$ . Transfer characteristics of conventional TFTs with  $W_{\rm mask}/L_{\rm mask}=1~\mu{\rm m}/0.4~\mu{\rm m}$  are also shown for comparison.

TABLE I

SELECTED IMPORTANT PARAMETERS OF GO-15-nm VSA-TFTs,

OFFSET VSA-TFTs, AND CONVENTIONAL TOP-GATE

HORIZONTAL-CHANNEL TFTs

|                      | S.S<br>(mV/dec) | Mobility (cm <sup>2</sup> /V·s) | I <sub>off</sub><br>(pA) | I <sub>on</sub> (uA) | on/off<br>ratio     |

|----------------------|-----------------|---------------------------------|--------------------------|----------------------|---------------------|

| GO-15-nm<br>VSA-TFTs | 127             | 50                              | 0.05                     | 5.76                 | >10 <sup>8</sup>    |

| Offset<br>VSA-TFTs   | 269             | 67                              | 0.04                     | 5.59                 | >10 <sup>8</sup>    |

| Conventional<br>TFTs | 399             | 29                              | 1.04                     | 4.83                 | 3.8x10 <sup>6</sup> |

higher than that of the offset VSA-TFTs due to their thinner gate oxide thickness resulting in more serious carrier scattering and degraded drain current. Therefore, the drain ON-state currents of GO-15-nm VSA-TFTs are not much higher than that of the offset VSA-TFTs. The VSA-TFTs have higher mobility, lower OFF-state current, and better S.S. than conventional TFTs. It appears that the OFF-state currents of the GO-15-nm VSA-TFTs could be further improved by employing an optimum oxide overetching depth.

## IV. CONCLUSION

In this paper, we have investigated the effects of  $\mathrm{NH_3}$  plasma treatment time, oxide overetching depth, and gate oxide thickness on VSA-TFTs. VSA-TFTs with 10-min  $\mathrm{NH_3}$  plasma treatment time have lower OFF-state currents and higher ON-state currents than VSA-TFTs with longer  $\mathrm{NH_3}$  plasma treatment times. The OFF-state currents and ON/OFF current ratio may be improved by increasing the oxide overetching depth. The S.S. can be improved by decreasing the gate oxide thickness; the S.S. of GO-15-nm VSA-TFTs is less than 150 mV/dec. The OFF-state currents can be improved by increasing the  $L_{\mathrm{mask}}$ , even though the thermal oxide overetching depth and the gate oxide thickness are changed. Compared with the conventional top-gate horizontal-channel TFTs, the VSA-TFTs have better characteristics in S.S., ON/OFF current ratio, and field-effect mobility.

#### ACKNOWLEDGMENT

The authors would like to thank the Nano Facility Center of National Chiao Tung University and the National Nano Device Laboratory for providing process equipment.

#### REFERENCES

- [1] Y.-H. Lu, P.-Y. Kuo, Y.-H. Wu, Y.-H. Chen, and T.-S. Chao, "Novel sub-10-nm gate-all-around Si nanowire channels poly-Si TFTs with raised source/drain," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 173–175, Feb 2011

- [2] W. C. Chen, H. C. Lin, Y. C. Chang, C. D. Lin, and T. Y. Huang, "In situ doped source/drain for performance enhancement of double-gated poly-Si nanowire transistors," *IEEE Trans. Electron Devices*, vol. 57, no. 7, pp. 1608–1615, Jul. 2010.

- [3] W. C. Chen, H. C. Lin, Z. M. Lin, C. T. Hsu, and T. Y. Huang, "A study on low temperature transport properties of independent double-gated poly-Si nanowire transistors," *Nanotechnology*, vol. 21, no. 43, pp. 954–956, Oct. 2010.

- [4] T. Y. Chiang, M. W. Ma, Y. H. Wu, P. Y. Kuo, K. T. Wang, C. C. Liao, C. R. Yeh, and T. S. Chao, "MILC-TFT with high-κ dielectrics for one-time-programmable memory application," *IEEE Electron Device Lett.*, vol. 30, no. 9, pp. 954–956, Sep. 2009.

- [5] T. Y. Chiang, W. C. Y. Ma, Y. H. Wu, K. T. Wang, and T. S. Chao, "A novel PN-diode structure of SONOS-type TFT NVM with embedded siliconnanocrystals," *IEEE Electron Device Lett.*, vol. 31, no. 11, pp. 1239–1241, Nov. 2010.

- [6] E. K. Lai, H. T. Lue, Y. H. Hsiao, J. Y. Hsieh, C. P. Lu, S. Y. Wang, L. W. Yang, T. Yang, K. C. Chen, J. Gong, K. Y. Hsieh, R. Liu, and C. Y. Lu, "A multi-layer stackable thin-film transistor (TFT) NAND-type flash memory," in *IEDM Tech. Dig.*, 2006, pp. 523–526.

- [7] H. Wang, M. Chan, S. Jagar, Y. Wang, and P. K. Ko, "Submicron super TFTs for 3-D VLSI applications," *IEEE Trans. Electron Devices*, vol. 21, no. 9, pp. 439–441, Sep. 2000.

- [8] T. Zhao, M. Cao, K. C. Saraswat, and J. D. Plummer, "A vertical sub-micron poly silicon thin-film transistor using a low temperature process," *IEEE Electron Device Lett.*, vol. 15, no. 10, pp. 415–417, Oct. 1994.

- [9] C. S. Lai, C. L. Lee, T. F. Lei, and H. N. Chern, "A novel vertical bottom-gate polysilicon thin film transistor with self-aligned offset," *IEEE Electron Device Lett.*, vol. 17, no. 5, pp. 199–201, May 1996.

- [10] M. Z. Lee, C. L. Lee, and T. F. Lei, "Novel vertical polysilicon thinfilm transistor with excimer-laser annealing," *Jpn. J. Appl. Phys.*, vol. 42, no. 4B, pp. 2123–2126, Apr. 2003.

- [11] J. G. Fossum, A. O. Conde, H. Shichijo, and S. K. Banerjee, "Anomalous leakage current in LPCVD polysilicon MOSFETs," *IEEE Trans. Electron Devices*, vol. ED-32, no. 9, pp. 1878–1884, Sep. 1985.

- [12] K. R. Olasupo and M. K. Hatalis, "Leakage current mechanism in submicron polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 43, no. 8, pp. 1218–1223, Aug. 1996.

- [13] C. T. Liu, C. H. D. Yu, A. Kornblit, and K. H. Lee, "Inverted thin-film transistor with a simple self-aligned lightly doped drain structure," *IEEE Trans. Electron Devices*, vol. 39, no. 12, pp. 2803–2809, Dec. 1992.

- [14] M. H. Juang and Y. M. Chiu, "Effects of a lightly-doped-drain (LDD) implantation condition on the device characteristics of polycrystalline-Si thin-film transistors," *Semicond. Sci. Technol.*, vol. 21, no. 3, pp. 291–294, Mar. 2006.

- [15] K. Tanaka, K. Nakazawa, S. Suyama, and K. Kato, "Characteristics of field-induced-drain (FID) poly-Si TFTs with high ON/OFF current ratio," *IEEE Trans. Electron Devices*, vol. 39, no. 4, pp. 916–920, Apr. 1992.

- [16] Z. Xiong, H. Liu, C. Zhu, and J. K. O. Sin, "Characteristics of high-κ spacer offset-gated polysilicon TFTs," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1304–1308, Aug. 2004.

- [17] P. Y. Kuo, T. S. Chao, P. S. Hsieh, and T. F. Lei, "Characteristics of self-sligned Si/Ge T-gate poly-Si thin-film transistors with high ON/OFF current ratio," *IEEE Trans. Electron Devices*, vol. 54, no. 4, pp. 1171– 1176, May 2007.

- [18] H. N. Chern, C. L. Lee, and T. F. Lei, "H<sub>2</sub>/O<sub>2</sub> plasma on polysilicon thinfilm transistor," *IEEE Electron Device Lett.*, vol. 14, no. 3, pp. 115–117, Mar. 1993.

- [19] H. N. Chern, C. L. Lee, and T. F. Lei, "The effects of H<sub>2</sub>—O<sub>2</sub>-plasma treatment on the characteristics of polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 40, no. 12, pp. 2301–2306, Dec. 1993.

- [20] J. Y. Lee, C. H. Han, and C. K. Kim, "ECR plasma oxidation effects on performance and stability of polysilicon thin film transistors," in *IEDM Tech. Dig.*, 1994, pp. 523–526.

- [21] M. W. Ma, T. Y. Chiang, W. C. Wu, T. S. Chao, and T. F. Lei, "Characteristics of HfO<sub>2</sub>/poly-Si interfacial layer on CMOS LTPS-TFTs with HfO<sub>2</sub> gate dielectric and O<sub>2</sub> plasma surface treatment," *IEEE Trans. Electron Devices*, vol. 55, no. 12, pp. 3489–3493, Dec. 2008.

- [22] Y. S. Lee, H. Y. Lin, T. F. Lei, T. Y. Huang, T. C. Chang, and C. Y. Chang, "Comparison of N<sub>2</sub> and NH<sub>3</sub> plasma passivation effects on polycrystalline silicon thin-film transistors," *Jpn. J. Appl. Phys.*, vol. 37, no. 7, pp. 3900–3903, Jul. 1998.

- [23] F. S. Wang, M. J. Tsai, and H. C. Cheng, "The effects of NH<sub>3</sub> plasma passivation on polycrystalline silicon thin-film transistors," *IEEE Electron Device Lett.*, vol. 16, no. 11, pp. 503–505, Nov. 1995.

[24] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH<sub>3</sub> plasma passivation"

- [24] H. C. Cheng, F. S. Wang, and C. Y. Huang, "Effects of NH<sub>3</sub> plasma passivation on n-channel polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 44, no. 1, pp. 64–68, Jan. 1997.

- [25] Y. H. Wu, P. Y. Kuo, Y. H. Lu, Y. H. Chen, and T. S. Chao, "Novel symmetric vertical channel nickel-salicided poly-Si thin-film transistors with high ON/OFF current ratio," *IEEE Electron Device Lett.*, vol. 31, no. 11, pp. 1233–1235, Nov. 2010.

- [26] I. H. Song, S. H. Kang, W. J. Nam, and M. K. Han, "A high-performance multichannel dual-gate poly-Si TFT fabricated by excimer laser irradiation on a floating a-Si thin film," *IEEE Electron Device Lett.*, vol. 24, no. 9, pp. 580–582, Sep. 2003.

- [27] Y. C. Wu, T. C. Chang, P. T. Liu, C. W. Chou, Y. C. Wu, C. H. Tu, and C. Y. Chang, "Reduction of leakage current in metal-induced lateral crystallization polysilicon TFTs with dual-gate and multiple nanowire channels," *IEEE Electron Device Lett.*, vol. 26, no. 9, pp. 646–648, Sep. 2005.

- [28] K. Y. Lee, Y. K. Fang, C. W. Chen, K. C. Huang, M. S. Liang, and S. G. Wuu, "The electrostatic charging damage on the characteristics and reliability of polysilicon thin-film transistors during plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 18, no. 5, pp. 187–189, May 1997.

memories.

Yi-Hong Wu was born in Chiayi, Taiwan, in 1984. He received the B.S. and M.S. degrees in electronics engineering from Feng Chia University, Taichung, Taiwan, in 2006 and 2008, respectively. He is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interest includes the studies of semiconductor device physics, including low-temperature polycrystalline-silicon thin-film transistor (TFT), novel structure poly-Si TFTs, and nonvolatile Flash

transistors.

**Po-Yi Kuo** (A'10) was born in Pingtung, Taiwan, in 1978. He received the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2007.

He joined the Department of Electrophysics, National Chiao Tung University, as a Postdoctoral Researcher in October 2008. His current research topics are the gate-all-around nanowire transistors, vertical-channel thin-film transistors, Si/Ge heterojunction devices, floating-body effect random-access memory, and the tunneling field-effect thin-film

**Yi-Hsuan Chen** was born in Taipei, Taiwan, in 1987. She received the B.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, in 2009, where she is currently working toward the Ph.D. degree in the Department of Electrophysics.

Her research interests include the studies of semiconductor device physics, low-temperature polycrystalline-silicon thin-film transistors, and non-volatile Flash memories.

**Tsung-Yu Chiang** was born in Yunlin, Taiwan, in 1984. He received the B.S. degree in physics from National Chung Cheng University, Chiayi, Taiwan, in 2006. He is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interest includes the studies of semiconductor device physics, including low-temperature polycrystalline-silicon thin-film transistor, metalgate/high-k technology, strain technique, and nonvolatile Flash memories.

**Kuan-Ti Wang** was born in Kaohsiung, Taiwan, in 1983. He received the B.S. degree in electronic engineering from Chang Gung University, Taoyuan, Taiwan, in 2006. He is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interests include dynamic threshold metal-oxide-semiconductor field-effect transistor, metal-gate/high-k technology, and nonvolatile flash memory.

Li-Chen Yen was born in Taipei, Taiwan, in 1985. He received the B.S. degree in electronics engineering from Ming Chuan University, Taoyuan, Taiwan, in 2006 and the M.S. degree from Chang Gung University, Taoyuan, Taiwan, in 2008. He is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interest includes the studies of semiconductor device physics, including low-temperature polycrystalline-silicon thin-film transistor, non-

volatile Flash memories, high-k technology, nanowire transistors, and biosensors.

Yi-Hsien Lu was born in Yunlin, Taiwan, in 1983. He received the B.S. degree in physics from National Chung Hsing University, Taichung, Taiwan, in 2005 and the M.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, in 2007, where he is currently working toward the Ph.D. degree in the Department of Electrophysics.

His current research topic is the fabrication and characterization of novel structure poly-Si thin-film transistors.

**Tien-Sheng Chao** was born in Penghu, Taiwan, in 1963. He received the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1992.

In July 1992, he joined the National Nano Device Laboratories as an Associate Researcher, where he became as a Researcher in 1996. He was engaged in developing thin-dielectrics preparations, cleaning processes, and complementary metal-oxide-semiconductor devices fabrication. In 2001, he joined the Department of Electrophysics,

National Chiao Tung University, where he has been a Professor since 2002.