Contents lists available at SciVerse ScienceDirect

# Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# Mobility model extraction for surface roughness of SiGe along (110) and (100) Orientations in HKMG bulk FinFET devices

Chien-Hung Chen <sup>a</sup>, Yiming Li <sup>b,\*</sup>, Chieh-Yang Chen <sup>b</sup>, Yu-Yu Chen <sup>b</sup>, Sheng-Chia Hsu <sup>b</sup>, Wen-Tsung Huang <sup>b</sup>, Sheng-Yuan Chu <sup>a,\*</sup>

#### ARTICLE INFO

Article history: Available online 29 March 2013

Keywords: Mobility FinFET Interface roughness Silicon germaniums Device simulation Orientations

### ABSTRACT

In this work, the FinFET HKMG MOS devices are fabricated on silicon wafer with p-substrate. The interface roughness between the SiGe and SiO $_2$  is experimentally extracted and calculated as a function of root mean square by analysis of high resolution transmission electron microscopy. The surface-roughness dependent mobility model is then incorporated into device simulation to study the mobility of SiGe along (110) and (100) orientations of the devices. We further analyze four devices with different surface roughness along (100) and (100) orientations to demonstrate the influence of surface roughness on the total effective mobility.

© 2013 Elsevier B.V. All rights reserved.

### 1. Introduction

MOS devices scaling is being continued and requires an ultimate thin gate dielectric [1]. In such devices, high mobility alternative channels have been researched to continue on the high performance roadmap, where highly scaled Si channel CMOS has faced various limitations. SiGe, the high mobility channels, potentially provide high injection velocity to achieve projected high performance metrics [2].

Various mobility models of SiGe can reasonably fit the measured dependence of effective mobility on doping concentration and bias in the inversion layer; however, for the FinFET HKMG MOS devices, there are few mobility models that considering the influence of surface roughness between the SiGe and SiO<sub>2</sub>. In this work, we fabricate FinFETs on silicon wafer with p-substrate and measure the interface roughness between the SiGe and SiO<sub>2</sub> by using high resolution transmission electron microscopy (HRTEM). The influence of surface roughness is then modelled as the spatial parameters of the surface, where the correlation length L and the surface roughness  $\Delta$  are calculated as a function of root mean square. The surface-roughness dependent mobility model is incorporated into device simulation for SiGe along (110) and (100) orientations of the devices. Four devices with different surface roughness along (100) and (100) orientations are further designed

and simulated to show the influence of surface roughness on the total effective mobility.

# 2. Experiment and extraction

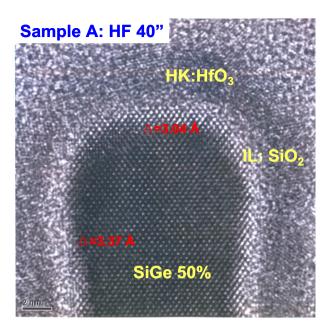

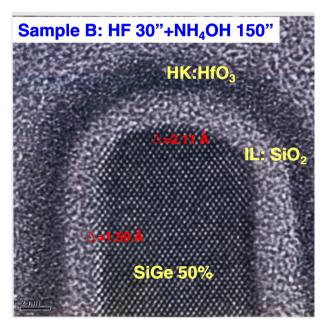

We fabricate the HKMG bulk FinFET on a p-substrate, where the advanced 193 nm immersion lithography and optimized etching processes are utilized for SiGe fin and STI formation [3,4]. The photo resistance layer is removed by HBrO<sub>2</sub> plasma, the silicon nitride is then etched by  $CF_4 + CH_2F_2$  and silicon is etched by HBrCl<sub>2</sub> + He-O<sub>2</sub>. SiGe is deposited by atomic layer deposition; 2-nm chemical oxide and 3-nm HfO<sub>3</sub> film are deposited by chemical vapor deposition. Finally, we use sputter to form an 8-nm-thick TiN film [5]. To get the two different kinds of surface roughness, the two clean processes are proposed in this experiment; the SAMPLE A is used by HF 100:1 40 s, and NH<sub>4</sub>OH 150 s + HF 100:1 40 s clean treatment is used on the SAMPLE B. The HRTEM photos of the fabricated SAMPLE A and the SAMPLE B are shown in Figs. 1 and 2.

The spatial parameters of the surface, the correlation length L and the surface roughness  $\Delta$  are then calculated [6]. The calculated root mean square surface nano-roughness of the SAMPLE A is 3.37 Å on (110) and 3.04 Å on (100). Their maximum is 6.15 Å and 4.05 Å, respectively. However, the result of the SAMPLE B is 1.59 Å on (110) and 2.11 Å on (100). Their maximum is 2.58 Å and 3.38 Å, respectively, as shown in Table 1. Thus, we further design four different devices with different surface roughness according to the results of the SAMPLE A and SAMPLE B for the device simulation. The simulation device 1 is with the same  $\Delta$  and L as

<sup>&</sup>lt;sup>a</sup> Department of Electrical Engineering, National Cheng-Kung University, Tainan 701, Taiwan

<sup>&</sup>lt;sup>b</sup> Deptartment of Electrical and Computer Engineering, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>\*</sup> Corresponding author. Tel.: +886 3 5712121x52974; fax: +886 3 5726639. *E-mail addresses*: ymli@faculty.nctu.edu.tw (Y. Li), chusy@mail.ncku.edu.tw (S.-Y. Chu).

Device 3

Device 4

**Fig. 1.** The HRTEM of the Sample A with the HF 40 s clean treatment on the interface between SiGe and  $SiO_2$  film. The calculated root mean square surface nano-roughness is 3.37 Å on (110) and 3.04 Å on (100). Their maximum is 6.15 Å and 4.05 Å, respectively.

**Fig. 2.** The HRTEM of the Sample B with the HF 30 s and NH<sub>4</sub>OH 150 s clean treatment on the interface between SiGe and  $SiO_2$  film. The calculated root mean square surface nano-roughness is 1.59 Å on (110) and 2.11 Å on (100). Their maximum is 2.58 Å and 3.38 Å, respectively.

the SAMPLE A. The simulation device 4 is with the same  $\Delta$  and L as the SAMPLE B. The simulation device 2 is with the same  $\Delta$  and L as the SAMPLE A on (100) and as the SAMPLE B on (110). The simulation device 3 is with the same  $\Delta$  and L as the SAMPLE B on (100) and as the SAMPLE A on (110).

# 3. Results and discussion

To evaluate the carrier's mobility, we use the Mathiessen's rule that approximates the total mobility [7,8], at low longitudinal field as the sum of three terms, as expressed in Eq. (1)

**Table 1** Surface roughness delta and correlation length of the Sample A and the Sample B. The simulation device 1 is with the same  $\Delta$  and L as the Sample A. The simulation device 4 is with the same  $\Delta$  and L as the Sample A. The simulation device 2 is with the same  $\Delta$

and L as the Sample A on (100) and as the Sample B on (110). The simulation device 3

is with the same  $\Delta$  and L as the Sample B on (100) and as the Sample A on (110). Surface orientation (100)(110)Sample  $\Delta$  (Å) L(Å)  $\Delta$  (Å) L(Å) 3.04 10.80 3.37 11.10 R 10.76 1.59 10.76 2.11 Simulated Device 1 Α Device 2 Α Α

B

В

В

В

$$\frac{1}{\mu_{\text{total}}} = \frac{1}{\mu_{\text{ph}}} + \frac{1}{\mu_{\text{co}}} + \frac{1}{\mu_{\text{sr}}}, \tag{1}$$

where the  $\mu_{\rm ph}$  is the phonon limited mobility, the  $\mu_{\rm co}$  is the Coulomb limited mobility, and the  $\mu_{\rm sr}$  is the surface limited mobility. For the devices at the high field, for example,  $E_{\rm eff} > 0.8$  MV/cm, the surface roughness mobility decreases with increasing the surface roughness. The mobility contribution attributed to surface roughness scattering is given by Eq. (2), where F is the transverse electric field normal to SiGe–SiO<sub>2</sub> interface and the  $F_{\rm ref}$  is a reference field [9–11]. Table 2 lists the parameters used in the device simulation.

$$\mu_{\rm sr} = \left[ \frac{\left( F_{\perp} / F_{\rm ref} \right)^{A^*}}{\delta} + \frac{F_{\perp}^3}{\eta} \right]^{-1}. \tag{2}$$

At low temperature and high normal electric field, the surface roughness scattering is known to strongly degrade the surface mobility, and it is also strongly dependent on the detail of technology, as Eq. (3), where the  $\delta$  is a constant that depends on the details of the fabrication technology, such as the oxide growth conditions, the crystal orientation, and so on; therefore, we can correct the parameter by the extracted surface roughness, as Eq. (4) in the device simulation.

$$\mu_{\rm sr}(E_\perp) = \frac{\delta}{E_\perp^2} \ . \tag{3}$$

$$\delta \propto (\Delta \cdot L)^{-2}.\tag{4}$$

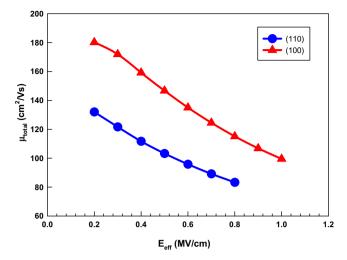

As shown in Fig. 3, the plot of the total mobility  $\mu_{\rm total}$  vs.  $E_{\rm eff}$  is the simulation results on the SiGe channel. The total mobility is decreased when the strength of applied electric field is increased. The total mobility the along (100) orientation is higher than that of (100) orientation, but the degradation of mobility versus the strength of applied electric field along (100) orientation is larger

**Table 2**The used mobility model parameters.

| Parameter | Electrons  | Holes      | Units                 |

|-----------|------------|------------|-----------------------|

| В         | 3.61E + 07 | 1.51E + 07 | cm/s                  |

| C         | 1.70E + 04 | 4.18E + 03 | $cm^{5/3}/(sV^{2/3})$ |

| τ         | 0.0233     | 0.0119     | 1                     |

| κ         | 1.7        | 0.9        | 1                     |

| δ         | 3.58E + 18 | 4.10E + 15 | V/s                   |

| A         | 2.58       | 2.18       | 1                     |

| α         | 6.85E-21   | 7.82E-21   | 1                     |

| ν         | 0.0767     | 0.123      | 1                     |

| η         | 5.82E + 30 | 2.05E + 30 | $V^2/(cm^*s)$         |

| κ         | 1.7        | 0.9        | 1                     |

**Fig. 3.** The simulation results of the electron mobility vs.  $E_{\rm eff}$  on SiGe. Red spot line is (100) and blue spot line is (110).

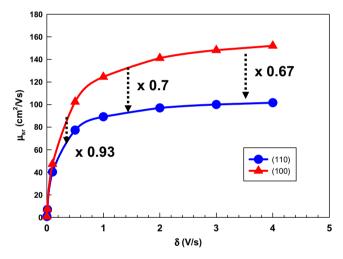

**Fig. 4.** The simulation results of the electron mobility vs.  $\delta$  on SiGe. Red spot line is (100) and blue spot line is (110).

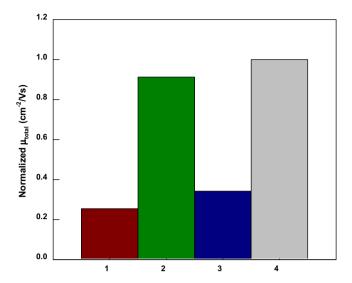

than that of (110) orientation. The red spot line is the (100) orientation and the blue spot line is the (110) orientation. Fig. 4 shows the simulation result of the surface limited mobility vs. the  $\delta$ , defined in Eq. (4), on the SiGe channel, where the red spot line is (100) and the blue spot line is (110). When the  $\delta$  approaches to zero, the device has largest surface roughness thus the device has the lowest  $\mu_{\rm sr}$ . When the  $\delta$  increases (i.e., the surface roughness is reduced), the device attains its largest  $\mu_{sr}$  for (110) and (100) orientations. Notably, the mobility along (110) orientation has 93-67% degradations, as marked in Fig. 4, to (100) orientation when the  $\delta$  increases. Fig. 5 indicates the simulated result of the electron mobility. The results of the designed four devices indicate the simulation device 2 and the simulation device 4 have higher mobility than those of the simulation device 1 and the simulation device 3 due to the surface roughness on (110) dominates the carrier's transport. Notably, the silicon fin height along the orientation of (110) is the major weight of the device's effective width.

**Fig. 5.** The normalized  $\mu_{\text{total}}$  with respect to the  $\mu_{\text{total}}$  of the simulation device 4. The simulation device 2's  $\mu_{\text{total}}$  is comparable with to the mobility of the simulation device 4. The mobility of the simulation device 1 and the simulation device 3 is dropped due to their large surface roughness.

#### 4. Conclusions

In this study, we have extracted SiGe/SiO<sub>2</sub> interface roughness along different orientations and modeled the corresponding mobility of the HKMG bulk FinFETs. The parameters of the surface roughness mobility model have been incorporated into device simulation. The influence of surface roughness on the total effective mobility has been demonstrated and the surface roughness along the SiGe surface (110) limits the total effective mobility.

## Acknowledgements

This work was supported in part by National Science Council (NSC), Taiwan under Contract No. NSC 101-2221-E-009-092 and by tsmc, Hsinchu, Taiwan under a 2012–2013 Grant. Mr. Chien-Hung Chen would like to thank for the sample fabrication and characterization from National Nano Device Laboratories, Hsinchu, Taiwan.

# References

- [1] Y. Li, H.-W. Cheng, Y.-Y. Chiu, C.-Y. Yiu, H.-W. Su, IEDM Tech. Dig. (2011) 107– 110.

- [2] K. Akarvardar, C.D. Young, M.O. Baykan, O. Injo, N. Tat, K.-W. Ang, M.P. Rodgers, S. Gausepohl, P. Majhi, C. Hobbs, P.D. Kirsch, R. Jammy, IEEE Electron Device Lett. 33 (2012) 351–353.

- [3] Y. Li, C.-H. Hwang, M.-H. Ham, Nanotechnology 21 (2010) 095203.

- [4] Y. Li, C.-H. Hwang, IEEE Trans. Electron Devices 54 (2007) 3426–3429.

- [5] N. Fasarakis, A. Tsormpatzoglou, D.H. Tassis, I. Pappas, K. Papathanasiou, M. Bucher, G. Ghibaudo, C.A. Dimitriadis, IEEE Trans. Electron Devices 59 (2012) 3306–3312.

- [6] S.M. Goodnick, D.K. Ferry, C.W. Wilmsen, Phys. Rev. B. 32 (1985) 8171–8186.

- [7] S. Takagi, M. Takenaka, Jpn. J. Appl. Phys. 50 (2011) 010110.

- [8] J. Chen, T. Saraya, K. Miyaji, K. Shimizu, T. Hiramoto, VLSI Symp. Tech. Dig. (2008) 32–33.

- [9] C. Lombardi, S. Manzini, A. Saporito, M. Vanzi, IEEE Trans. Electron Devices 7 (1988) 1164–1170.

- [10] M.N. Darwish, J.L. Lentz, M.R. Pinto, P.M. Zeitzoff, T.J. Krutsick, H.H. Vuong, IEEE Electron Device Lett. 44 (1997) 1529–1538.

- [11] J. Oh, S.-H. Lee, K.-S. Min, J. Huang, B.G. Min, B. Sassman, K. Jeon, W.-Y. Loh, J. Barnett, I. Ok, C.-Y. Kang, C. Smith, D.-H. Ko, P.D. Kirsch, R. Jammy, VLSI Symp. Tech. Dig. (2010) 39–40.