# Realizations of High-Order Switched-Capacitor Filters Using Multiplexing Technique

Chung-Yu Wu, Member, IEEE, Jenn-Chyou Bor, and Bor-Shenn Jeng

Abstract—A new SC design methodology using multiplexing technique is proposed to realize arbitrary high-order filters. In this methodology, the filter transfer function is transformed as the combination of biquads and their outputs are computed sequentially by the multiplexing SC biquad circuit. Four basic function SC circuits are introduced and a filter can be implemented by various combinations of these circuits. This makes the proposed method more versatile and practical. Because of the efficient use of multiplexing techniques, the realized high-order filters have less op-amps, switches, and capacitors, and thus small chip area, but at the cost of increasing clock phases. An eighthorder Butterworth low-pass filter design example is presented to demonstrate how to apply the proposed method to the design of high-order filters. Moreover, an eighth-order low-pass filter has been designed and fabricated in 1.2  $\mu$ m CMOS double-poly double-metal process. Both computer simulation and experimental results have successfully verified the function correctness and the performance of the proposed design method.

### I. INTRODUCTION

WITCHED-CAPACITOR (SC) technique has been widely applied to the design of analog sampled-data filters. In the conventional design method of SC filters [1]-[3], the number of operational amplifiers (op-amps) is proportional to the order of the realized transfer functions. Thus the realization of high-order filters requires large chip area and power dissipation. Moreover, the noise generated by the opamps is also increased. To solve this problem, the number of op-amps in SC filters has to be reduced. In this approach, a few new design methods have been proposed [4]-[7]. The recent work [4] has demonstrated a multiplexing scheme which uses any number of op-amps, from 1 to N, to realize an arbitrary Nth-order filter function. The design method is to use the noninverting stray-insensitive integrator [8] and the multiplexing technique to implement the state-space equations of the form

$$(z-1)\mathbf{X} = \mathbf{A}\mathbf{X} + \mathbf{b}u$$

$$y = \mathbf{c}^T\mathbf{X} + du$$

where the matrices A, b, c, and d are constants, X is the state variable, u is the input, y is the output, and z is the z-transform operator. Although the structure can obtain a very significant op-amp number reduction, it still has some

Manuscript received October 15, 1992; revised June 13, 1994.

C.-Y. Wu and J.-C. Bor are with the Integrated Circuit and System Laboratory, Department of Electronics Engineering and Institute of Electronics, Engineering Building 4th, National Chiao Tung University, 300, Taiwan, R.O.C.

B.-S. Jeng is with Telecommunication Laboratory, Chungli, Taiwan, R.O.C. IEEE Log Number 9405321.

disadvantages. The major disadvantage is mentioned below. The number of capacitors and switches used in this SC circuit is mainly proportional to the number of nonzero coefficients in the  $N \times N$  matrix  $\bf A$ . However, in order to obtain low capacitor ratio, low sensitivity, and wide dynamic range, the matrix  $\bf A$  must be chosen so that the number of nonzero elements in  $\bf A$  is as many as possible. Therefore, the components in the realized SC circuit become numerous and the layout routing becomes complicated. This may offset the chip area reduction gained from the reduced op-amp count.

In this paper, a new design method to implement arbitrary high-order filter functions is proposed. In the proposed method, the multiplexed SC differentiators and integrators are used as the building blocks. As the order of the filter transfer function increases, the number of op-amps used in the SC filter is fixed and the number of clock phases increases. The resulting circuit architecture is flexible and the number of capacitors and switches used in the circuit is only proportional to the order of filter function. Therefore, the entire circuit is not very complex and the efficient layout can be achieved easily.

The concept of the proposed design method is to transform the transfer function of the high-order filter into a cascade of second-order transfer functions and use a multiplexing SC circuit to compute the outputs of these second-order transfer functions sequentially and realize the desired highorder transfer functions. Therefore, due to the efficient use of the multiplexing technique, fewer components can be used to implement high-order filters. The discrete-time theory of this design method is described in Section II. According to this methodology, four basic functions are defined. The SC circuits to implement these functions are also presented in Section II. By using these basic building blocks, the high-order filters can be implemented. In Sections III and IV, a general highorder low-pass filter and design examples have been used to demonstrate how to use the basic functions to implement highorder filters, respectively. The experimental results to verify the performance of the proposed new structures are described in Section V. Finally, the conclusion is given.

# II. DESIGN METHODOLOGY

# A. Discrete-Time Theory

The z-domain transfer function of an arbitrary Mth-order discrete-time linear system can be described as

$$H(z) = \frac{Y(z)}{U(z)} = \frac{\sum_{j=0}^{M} \beta_j z^{-j}}{1 + \sum_{i=1}^{M} \alpha_i z^{-i}}$$

(1)

where  $\alpha_i$  and  $\beta_j$  are constant coefficients, U(z) is the z-transform of the input sequence u[m], Y(z) is the z-transform of the output sequence y[m], and m is an integer. Applying the mathematical technique, the above equation can be transformed into the product of N second-order transfer functions (biquads) where  $N = \lfloor (M+1)/2 \rfloor$  is the largest integer of (M+1)/2. This is given by

$$H(z) = \prod_{i=1}^{N} \frac{D_i + E_i z^{-1} + F_i z^{-2}}{1 + B_i z^{-1} + C_i z^{-2}}$$

(2)

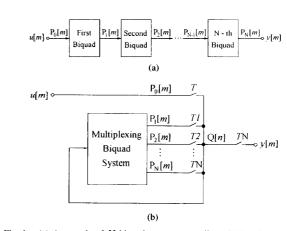

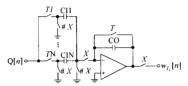

where  $B_i, C_i, D_i, E_i$  and  $F_i$  are constant coefficients. Therefore, this linear system can be considered as a cascade of N biquads, shown in Fig. 1(a). Assume that  $\mathbf{P}_0(z) = U(z)$  represents the z-transform of the input sequence of the first biquad in the linear system.  $\mathbf{P}_N(z) = Y(z)$  represents the z-transform of the output sequence of the Nth biquad in the linear system.  $\mathbf{P}_i(z), 1 \leq i \leq N-1$ , represents the z-transform of the output sequence in the i-th biquad which is also the input sequence in the (i+1)th biquad under the multiplexing operation. Actually,  $\mathbf{P}_0(z)$  is the system input,  $\mathbf{P}_N(z)$  is the system output, and  $\mathbf{P}_i(z)$  is the intermediate outputs of the system. By using  $\mathbf{P}_i(z)$ , (2) can be rewritten as

$$H(z) = \prod_{i=1}^{N} \frac{\mathbf{P}_{i}(z)}{\mathbf{P}_{i-1}(z)}$$

(3)

where

$$\frac{\mathbf{P}_{i}(z)}{\mathbf{P}_{i-1}(z)} = \frac{D_{i} + E_{i}z^{-1} + F_{i}z^{-2}}{1 + B_{i}z^{-1} + C_{i}z^{-2}}.$$

(4)

To implement (3) with less hardware, the multiplexing technique is applied to the computation of each of the biquad outputs sequentially. The block diagram of such a multiplexing system is shown in Fig. 1(b), and its output sequence is defined as

$$Q[n] \equiv P_i[m],$$

$n = m(N+1) + i, \ 0 < i < N$  (5)

where the sampling period  $T_x$  of Q[n] is 1/(N+1) times the sampling period  $T_t$  of  $P_i[m]$ , and  $P_i[m]$  is the inverse z-transform of  $P_i(z)$ . The operation to compute the desired system output can be divided into two steps: 1) setting the initial condition and 2) computing each of the biquad outputs sequentially in every  $T_t$  period following the first step. Both steps are explained as follows.

Initialization Step: During the clock phase T, i.e., n=m(N+1), the multiplexing system is initialized with the new system input values. At this time, the output of the multiplexing system is set as

$$Q[n] = P_0[m] = u[m].$$

Through the initialization step, the associated data stored in this system is updated.

Fig. 1. (a) A cascade of N biquad systems to realize a high-order transfer function in (1). (b) A multiplexing system to compute the outputs of N biquads sequentially and realize the high-order transfer function.

Computation Step: During clock phases T1 to TN, i.e., n=m(N+1)+i and  $1\leq i\leq N$ , the multiplexing system produces the outputs of the N biquads. Applying the inverse z-transform to (4) and substituting  $P_i[m]$  by Q[n], it can be transformed into

$$Q[n] = -B_i Q[n - N - 1] - C_i Q[n - 2N - 2]$$

$$+ D_i Q[n - 1] + E_i Q[n - N - 2]$$

$$+ F_i Q[n - 2N - 3].$$

(6)

By using (6), the desired output can be calculated.

# B. Realization of Four Basic Functions

To develop the multiplexing system described above, the most important thing is to implement the multiplexing biquad system for the computation step. According to (6) and the general SC design method, four basic functions are defined to realize this system. These functions and their realization are described below. As to the initialization step, it can be implemented by adding some capacitor branches to the multiplexing biquad system circuit to set the required initial values

Slow Multiplexed Differentiator: The relationship between the input sequence Q[n] and output sequence  $w_{D_t}[n]$  of the slow multiplexed differentiator is defined as

$$w_{D_t}[n] \equiv \begin{cases} 0, & n = m(N+1) \\ h_{D_t}^i D_t \{Q[n]\}, & n = m(N+1) + i, 1 \le i \le N \end{cases}$$

where

$$D_t\{Q[n]\} \equiv Q[n] - Q[n-N-1] = P_i[m] - P_i[m-1]$$

and  $h^i_{D_t} \leq 0$ .

The above equation is similar to the form of the backward-Euler differentiation, except that the delay of the subtrahend is N+1. Thus it is called the slow multiplexed differentiator. Its coefficient is time-varying and periodic with the period  $T_t$ . Therefore, to implement this function, the multiplexing technique can be applied to an ordinary SC differentiator to

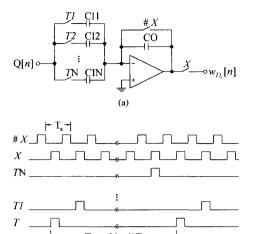

Fig. 2. (a) The circuit of slow multiplexed differentiator. (b) The associated clock waveforms.

produce the desired output. This results in the reduction of the components used. The designed SC slow multiplexed differentiator circuit and the associated clock waveforms are shown in Fig. 2 where the core structure of the SC differentiator proposed in [9], [10] has been used. The capacitor values are related to the coefficients as follow:

$$\frac{\mathrm{CI}i}{\mathrm{CO}} = -h_{D_t}^i, \qquad 1 \le i \le N.$$

In this circuit, the capacitor array controlled by the clock phases  $T1, T2, \ldots$ , and TN is used to hold N points of the past input and each capacitor in the array is accessed in turn every  $T_t$ . Therefore, the difference between Q[n] and Q[n-N-1] can be easily obtained. #X and X are non-overlapping clocks with the clock period  $T_x$  for Q[n], whereas the clock T has a clock period  $T_t = (N+1)T_x$  for  $P_t[m]$ .

Slow Multiplexed Integrator: The relationship between the input sequence Q[n] and output sequence  $w_{I_t}[n]$  of the slow multiplexed integrator is defined as

$$w_{I_t}[n] \equiv \begin{cases} 0, & n = m(N+1) \\ h_{I_t}^i I_t \{Q[n]\}, & n = m(N+1) + i, 1 \le i \le N \end{cases}$$

(8)

where

$$I_t\{Q[n]\} \equiv \sum_{i=0}^m Q[j(N+1)+i] = \sum_{i=0}^m P_i[j] \text{ and } h^i_{I_t} \leq 0.$$

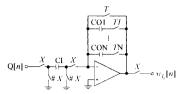

Similar to the slow multiplexed differentiator, the realization of this function can be obtained by modifying the SC backward-Euler integrator into the time-sharing structure. This circuit is shown in Fig. 3 where the integrator proposed in [8] is adopted as the core structure and the clock T is used to obtained zero output at n=m(N+1). In this circuit, the past N-point results are stored in the capacitor array controlled by the clock phases  $T1, T2, \ldots$ , and TN. Thus it is called the slow multiplexed integrator. The operation clock waveforms are the same as

Fig. 3. Circuit of the slow multiplexed integrator.

those in Fig. 2. The capacitor values in the slow multiplexed integrator are related to the coefficients as follows:

$$\frac{\mathrm{CI}}{\mathrm{CO}i} = -h_{I_t}^i, \qquad 1 \le i \le N.$$

In this circuit, there is a serious disadvantage. When all the clock phases are off, the op-amp is under open-loop condition, and its output will be rapidly saturated to the level of power supply. Although it can be recovered in the next clock phase, this still degrades circuit performance. When using this circuit to implement (6), therefore, the architecture of overall SC circuits must be carefully designed to avoid this problem.

Fast Multiplexed Differentiator: The relationship between the input sequence Q[n] and the output sequence  $w_{D_x}[n]$  of the fast multiplexed differentiator is defined as

$$w_{D_x}[n] \equiv \begin{cases} 0, & n = m(N+1) \\ h_{D_x}^i D_x \{Q[n]\}, & n = m(N+1) + i, 1 \le i \le N \end{cases}$$

(9)

where

$$D_x\{Q[n]\} \equiv Q[n] - Q[n-1]$$

and  $h_{D_x}^i \le 0$ .

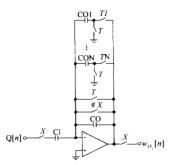

This function is similar to the ordinary form of differentiation except the coefficient is time-varying and periodic with the period  $T_t$ . Therefore, a capacitor array is adopted as the output capacitor of the SC differentiator. By turning on the switches in the capacitor array, the effective output capacitor can be adjusted to the required value. The resultant circuit is shown in Fig. 4 where the capacitor ratios and the coefficients are related by

$$\frac{\mathrm{CI}}{\mathrm{CO}i + \mathrm{CO}} = -h_{D_x}^i, \qquad \dot{1} \le i \le N.$$

The capacitor CO is used to reduce the value of all  ${\rm CO}i$  and prevent the op-amp from entering the open-loop condition. The switch controlled by the clock phase T is to produce zero output when n=m(N+1). The major difference between this differentiator and the slow multiplexing differentiator is the differentiation is performed for the two samples with one  $T_x$  delay rather than  $(N+1)T_x$  delay. Thus it is called the fast multiplexed differentiator.

Fast Multiplexed Integrator: The relationship between the input sequence Q[n] and the output sequence  $w_{I_x}[n]$  of the fast multiplexed integrator is defined as

$$w_{I_x}[n] \equiv \begin{cases} 0, & n = m(N+1) \\ I_x\{h_{I_x}^iQ[n]\}, & n = m(N+1) + i, 1 \le i \le N \end{cases}$$

(10)

Fig. 4. Circuit of the fast multiplexed differentiator.

Fig. 5. Circuit of the fast multiplexed integrator.

where

$$I_x\{Q[n]\} \equiv \sum_{j=1}^i Q[m(N+1)+j] \quad \text{and} \quad h^i_{I_x} \leq 0.$$

Similar to the fast multiplexed differentiator, this function can be implemented by changing the input capacitor of the SC integrator into a capacitor array. Thus, the effective input capacitor value can be varied in different clock phases. Since the integration must restart with the new initial condition after N+1 points, the switch controlled by the clock phase T is used to reset the stored charges on the capacitor. The circuit is shown in Fig. 5 where the capacitor ratios and the coefficient are related by

$$\frac{\mathrm{CI}i}{\mathrm{CO}} = -h_{I_x}^i, \qquad 1 \le i \le N.$$

Since the integrator in Fig. 5 performed the integration on the samples with one  $T_x$  delay rather than one  $T_t$  delay in the slow multiplexed integrator, it is called the fast multiplexed integrator.

# III. FILTER DESIGN PROCEDURE

In order to demonstrate how to apply the proposed new multiplexing design methodology described in Section II to the design of high-order filters, a general low-pass filter design procedure is described. First, the s-domain transfer function of a general low-pass filter is decomposed into the product of the

biquads as

$$H_N(s) = \frac{Y(s)}{U(s)} = \sum_{i=1}^N \frac{1 + b_i s + c_i s^2}{1 + d + (b_{i+1} + e_i)s + (c_{i+1} + f_i)s^2}$$

(11)

where  $b_i$ ,  $c_i$ , d,  $e_i$  and  $f_i$  are constant coefficients. Then (11) is transformed into the z-domain. Since all basic function circuits described in Section II are backward-Euler type, it is convenient to adopt the backward-Euler transformation

$$s = \frac{1 - z^{-1}}{T_{\star}}$$

where  $T_t$  is the sampling period of input and output signals. Therefore, the z-domain transfer function can be expressed as (12) (see below.) Using (2)–(5) to define  $P_i[m]$  and Q[n], the operation of the multiplexing biquad system in Fig. 1(b) can be described as

$$Q[n] = Q[n-1] + b_i T_t^{-1} (Q[n-1] - Q[n-N-2])$$

$$+ c_i T_t^{-2} ((Q[n-1] - Q[n-N-2])$$

$$- (Q[n-N-2] - Q[n-2N-3]))$$

$$- dQ[n] - (b_{i+1} + e_i) T_t^{-1} (Q[n] - Q[n-N-1])$$

$$- (c_{i+1} + f_i) T_t^{-2} ((Q[n] - Q[n-N-1])$$

$$- (Q[n-N-1] - Q[n-2N-2])).$$

(13)

According to (7), (9), and (10), it is straightforward to change (13) into

$$Q[n] = I_x \{ D_x \{ -b_{i+1} T_t^{-1} D_t \{ Q[n] \} \}$$

$$+ D_x \{ -c_{i+1} T_t^{-2} D_t \{ D_t \{ Q[n] \} \} \}$$

$$- dQ[n] - e_i T_t^{-1} D_t \{ Q[n] \}$$

$$- f_i T_t^{-2} \{ D_t \{ Q[n] \} \} \}.$$

$$(14)$$

Since the four basic linear operators in Section II have the following relations as

$$\begin{split} I_x\{D_x\{Q[n]\}\} &= Q[n] \\ D_t\{h[n]Q[n]\} &= h[n]D_t\{Q[n]\} \end{split}$$

if h[n] is a periodic sequence with the period  $T_t$ , (14) can be rewritten as

$$Q[n] = -\alpha \beta D_t \{ \hat{b}_i Q[n] \} - I_x \{ \hat{e}_i \beta D_t \{ \hat{b}_i Q[n] \} \}$$

$$- I_x \{ \hat{d}Q[n] \} - \gamma D_t \{ \hat{c}_i D_t \{ \hat{b}_i Q[n] \} \}$$

$$- I_x \{ \hat{f}_i D_t \{ \hat{c}_i D_t \{ \hat{b}_i Q[n] \} \} \}$$

(15)

where

$$\begin{array}{ll} b_i = \alpha \beta \hat{b}_{i-1} T_t, & c_i = \gamma \hat{b}_{i-1} \hat{c}_{i-1} T_t^2, \\ d = \hat{d}, & e_i = \beta \hat{b}_i \hat{e}_i T_t, & f_i = \hat{b}_i \hat{c}_i \hat{f}_i T_t^2 \end{array}$$

$$H_N(z) = \frac{Y(z)}{U(z)} = \sum_{i=1}^N \frac{1 + b_i (1 - z^{-1}) T_t^{-1} + c_i (1 - z^{-1})^2 T_t^{-2}}{1 + d + (b_{i+1} + e_i) (1 - z^{-1}) T_t^{-1} + (c_{i+1} + f_i) (1 - z^{-1})^2 T_t^{-2}}$$

(12)

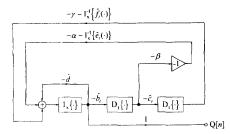

Fig. 6. The block diagram of (15).

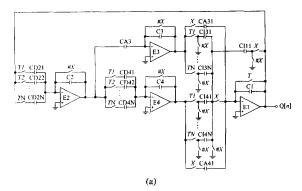

Fig. 7. (a) The circuit of the multiplexing biquad. (b) The entire circuit to realize (11).

The block diagram to represent the above equation is shown in Fig. 6. Assuming

$$\alpha, \beta, \gamma, \hat{d}, \hat{e}_i, \hat{f}_i \geq 0, \qquad \hat{b}_i, \hat{c}_i > 0,$$

we have

$$b_i, c_i, d, e_i, f_i \geq 0.$$

From Fig. 6, it can be seen that the multiplexing biquad can be implemented by using the SC inverter [10], slow multiplexed differentiators, and fast multiplexed integrator. The resultant circuit is shown in Fig. 7(a).

As to the initialization step, its operation is to produce the initial conditions of the multiplexed biquad required in the clock phase T1. From the circuit of the multiplexed biquad, it can be observed that these initial conditions are the voltages stored in the capacitors C1, CA31, and CA41. For the capacitors CA31 and CA41, their stored voltages must be set as following:

$$\begin{split} V(\text{CA31}) &= \beta D_t \{ \hat{b}_0 Q[m(N+1)] \} \\ V(\text{CA41}) &= D_t \{ \hat{c}_0 D_t \{ \hat{b}_0 Q[m(N+1)] \} \}. \end{split}$$

As Q[m(N+1)] = u[m], we can use the structure of the multiplexing biquad to compute these values by substituting u[m] for x[n] in the clock phase T. Therefore, the correct initial values can be stored in these capacitors. Since the resulting voltage value in the capacitor C1 is meaningless, the switch controlled by the clock phase T is used to reset this value and prevent it from disturbing other operations. As to the capacitor C1, the required initial voltage during the clock phase T1 is u[m]. It is easy to perform this initialization step by adding a capacitor branch connected to the op-amp E1. The entire circuit of the multiplexing low-pass filter system is shown in Fig. 7(b) where the capacitor branches CD20 and CD40 are added to compute the initial values stored in CA31 and CA41 during the clock phase T, and the capacitor branch CIN is used to store u[m] during the clock phase T and send it to C1 during the clock phase T1.

According to (14)-(15) and Fig. 6, the relationship between the capacitor ratios in Fig. 7(b) and the coefficients of (11) can be described as

$$1 = \frac{\text{CIN}}{C1} \tag{16}$$

$$b_{i+1} = T_t \frac{\text{CD2}i}{C2} \frac{\text{CA3}}{C3} \frac{\text{CA31}}{C1}, \qquad 0 \le i \le N$$

(17)

$$1 = \frac{1}{C1}$$

$$b_{i+1} = T_t \frac{\text{CD2}i}{C2} \frac{\text{CA3}}{C3} \frac{\text{CA31}}{C1}, \qquad 0 \le i \le N$$

$$c_{i+1} = T_t^2 \frac{\text{CD2}i}{C2} \frac{\text{CD4}i}{C4} \frac{\text{CA41}}{C1}, \qquad 0 \le i \le N$$

(18)

$$d = \frac{\text{CI11}}{C1}$$

$$e_{i} = T_{t} \frac{\text{CD2}_{i}}{C2} \frac{\text{CA3}}{C3} \frac{\text{CI3}_{i}}{C1},$$

$$f_{i} = T_{t} \frac{\text{CD2}_{i}}{C2} \frac{\text{CD2}_{i}}{C4} \frac{\text{CI4}_{i}}{C1},$$

$$1 \le i \le N$$

$$(20)$$

$$e_i = T_t \frac{\text{CD2}i}{C2} \frac{\text{CA3}}{C3} \frac{\text{CI3}i}{C1}, \qquad 1 \le i \le N$$

(20)

$$f_i = T_t^2 \frac{\text{CD2}i}{C^2} \frac{\text{CD4}i}{C^4} \frac{\text{CI4}i}{C^1}, \qquad 1 \le i \le N. \tag{21}$$

As mentioned above, the circuit in Fig. 7(b) can be directly used to implement (11) when  $b_i, c_i, d, e_i$ , and  $f_i$  are all nonnegative. To implement (11) for different coefficients, this circuit needs some modification. For negative  $b_i$  and  $e_i$ , they can be realized by adding suitable capacitor branches between the output of op-amp E2 and the input of op-amp E1. For the negative  $c_i$  and  $f_i$ , they can be realized by using the SC inverter E3. As to the negative d, it can be realized by using the SC inverter E3. Also, increasing the capacitor ratio CIN/C1 has the same effect.

Although it is simple and straightforward to develop the multiplexing low-pass system by using the backward-Euler mapping to transform  $H_N(s)$  into  $H_N(z)$ , this transformation causes Q-value degradation in  $H_N(z)$ . Therefore, the sampling frequency must be much larger than the cut-off frequency of the low-pass system, and the pre-warping technique must be applied to minimize the approximating error. If this error is still not tolerable, the bilinear transformation can be used to realize the four basic functions and obtain  $H_N(z)$ . Similar design procedure can also be developed to design high-order filters.

The architecture of the circuit shown in Fig. 7(b) has a disadvantage in that the feedback paths to the op-amp E1 are of global feedback. It is lack of local feedback. Although these global feedback paths are all negative, it is possible to make the SC circuit oscillate if the global feedback is large enough. This is due to the extra time delay of the global feedback path which is passing the op-amps E2, E3, and E4. There are three compensation methods to eliminate this effect. The first one is to add redundant components to the circuit to increase the local negative feedback. The second method is to partially change the architecture of the circuit to increase the local negative feedback. The last one is to use fully-differential op-amps instead of single-ended-output op-amps to decrease the time delay. These methods have their own advantages and disadvantages. They can be used according to the application need and its requirement.

# IV. DESIGN EXAMPLE

Consider the design of a low-pass filter which has a flat passband with 3 dB attenuation at 0.5 kHz and a passband gain of unity. The stopband attenuation should be at least 70 dB for f > 1.5 kHz. The sampling frequency is 16 kHz.

Since this filter has a flat passband, the Butterworth approximation is adopted to develop its transfer function. According to the computer program, the order of Butterworth filter must be larger than seven to satisfy the filter requirement. Hence, we choose M=8 and use the backward-Euler mapping to transform this transfer function into z-domain. Since this mapping will result in Q-value degradation at the center of the filter passband, the Q-value and the 3 dB frequency must be adjusted to minimize this effect. Therefore, the z-domain transfer function can be obtained as

$$\begin{split} H(z) &= \frac{1}{1 + 1.2280(1 - z^{-1}) + 19.613(1 - z^{-1})^2} \\ &\times \frac{1}{1 + 4.4209(1 - z^{-1}) + 19.613(1 - z^{-1})^2} \\ &\times \frac{1}{1 + 6.8646(1 - z^{-1}) + 19.613(1 - z^{-1})^2} \\ &\times \frac{1}{1 + 8.1872(1 - z^{-1}) + 19.613(1 - z^{-1})^2}. \end{split}$$

Using the circuit in Fig. 7(b) to implement this transfer function, the capacitor values can be easily calculated by (16)–(21). These values are

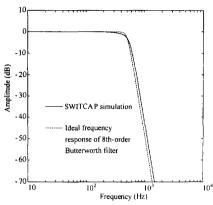

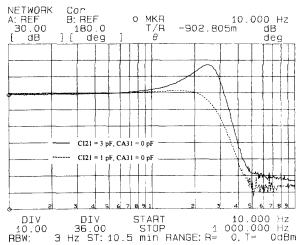

and other capacitors are unit capacitors. The SWITCAP [11] simulation result and the ideal frequency response of the

Fig. 8. SWITCAP simulation results and ideal calculation results of the 8th-order low-pass filter example.

8th-order Butterworth low-pass filter are shown in Fig. 8. Although there is some difference in the transition region, it still meets the filter specification.

### V. EXPERIMENT RESULTS

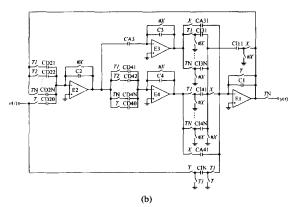

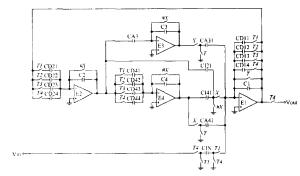

To verify the proposed design method, an 8th-order low-pass filter is designed and fabricated in 1.2  $\mu$ m CMOS double-poly double-metal process. The circuit to implement this filter is shown in Fig. 9, and its z-domain transfer function can be expressed as

$$\begin{split} H(z) &= \frac{(1+\mathrm{CA31}(1-z^{-1})+4(1-z^{-1})^2)^3}{(1+(4+\mathrm{CA31}-\mathrm{CI21})(1-z^{-1})+12(1-z^{-1})^2)^4}. \end{split}$$

The chip photomicrograph is shown in Fig. 10. The op-amps in the circuit of Fig. 9 are of the simple two-stage type. The sampling period of the input signal is 1.6E-4 second and the capacitor values are

$$\begin{aligned} & \text{CD11} = \text{CD12} = \text{CD13} = \text{CD14} = 4 \text{ pF}, \quad \text{CI41} = 8 \text{ pF}, \\ & \text{CIN} = C1 = \text{CA3} = C3 = 1 \text{ pF}. \end{aligned}$$

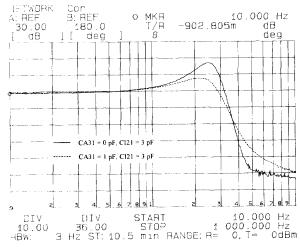

The capacitor values of CA31 and CI21 can be tuned from 1 pF to 4 pF and used to control the decay speed in the transition region and the Q-value, respectively. To demonstrate the capability of the compensation scheme in eliminating the circuit instability caused by the global feedback, the capacitor values of CD21, ..., CD24, CD41, ..., CD44, C2, and C4 are set to 4 pF to increase the time-delay of the global feedback. The second compensation method mentioned in Section III is applied to the filter circuit. Basically, the function of the capacitor array CD11, ..., CD14 is the same as that of the capacitor array CI31, ..., CI3N in Fig. 7(b). However, in the transient step, this capacitor array can increase the local feedback. Therefore, this circuit is more stable. The measured frequency response with different values of CA31 is shown in Fig. 11. It can be seen that the decay speed in the transition region increases as CA31 decreases. This result agrees with the responses from the theoretical calculation and the SWITCAP simulation.

Fig. 9. The experimental low-pass filter with the compensation circuit.

Fig. 10. Chip photomicrograph of the fabricated low-pass filter in Fig. 9.

Fig. 11. The measured frequency response of the fabricated low-pass filter in Fig. 9 with different values of CA31.

The measured results with different values of CI21 are also shown in Fig. 12. The Q value of the filter increases as CI21 increases. This is also consistent with the theoretical calculation and SWITCAP simulation results.

Fig. 12. The measured frequency response of the fabricated low-pass filter in Fig. 9 with different values of CI21,

### VI. CONCLUSION

Based upon the multiplexing technique which uses a SC biquad in the time-sharing way, a new design method for high-order SC filters is proposed and analyzed. By using the new design method, the realized SC high-order filters have less op-amps, switches, and capacitors, and thus smaller chip area, as compared to those realized by using the conventional method. As the filter order increases, only a few switches and capacitors, as well as extra clock phases, are required, but the number of op-amps remains the same. Thus the proposed design method is useful in those applications where power dissipation and chip area are critical issues while many clock phases are available.

Further work on applying the design method to high-order bandpass SC filter design and other special SC filter design and applications will be addressed in the near future.

### ACKNOWLEDGMENT

The authors would like to acknowledge the suggestions and comments of the reviewers, which led to substantial improvements in the paper.

# REFERENCES

- [1] P. Allen and E. Sanchez-Sinencio, Switched-Capacitor Circuits. New York: Van Nostrand Reinhold, 1984.

- R. Gregorian and G. C. Temes, Analog MOS Integrated Circuits for

- Signal Processing. New York: Wiley, 1986.

[3] J. Taylor and J. Mavor, "Exact design of stray-insensitive switchedcapacitor LDI ladder filters from unit element prototypes," IEEE Trans. Circuits Syst., vol. CAS-33, pp. 613-622, June 1986.

- [4] G. W. Roberts, W. M. Snelgrove, and A. S. Sedra, "Switched-capacitor realization of Nth-order transfer function using a single multiplexed op-amp," IEEE Trans. Circuits Syst., vol. CAS-34, pp. 140-148, Feb.

- [5] F. Montecchi, "Time-shared switched-capacitor ladder filters insensitive to parasitic effects," IEEE Trans. Circuits Syst., vol. CAS-31, pp.

- [6] K. R. Laker, P. E. Fleischer, and A. Ganesan, "Parasitic insensitive, biphase switched capacitor filters realized with one operational amplifier per pole pair," Bell Syst. Tech. J., vol. 61, no. 5, pp. 685-707, May 1982.

- [7] D. J. Allstot and K.-S. Tan, "Simplified MOS switched capacitor ladder filter structures," IEEE J. Solid-State Circuits, vol. SC-16, pp. 724-729,

- [8] B. J. Hosticka, R. W. Brodersen, and P. R. Grey, "MOS sampleddata recursive filters using switched capacitor integrators," IEEE J. Solid-State Circuits, vol. SC-12, pp. 600–608, Dec. 1977.

[9] C.-Y. Wu, T.-C. Yu, and S.-S. Chang, "New monolithic switched-

- capacitor differentiators with good noise rejection," IEEE J. Solid-State

- Circuits, vol. 24, pp. 177–180, Feb. 1989.

[10] T.-C. Yu, C.-Y. Wu, and S.-S. Chang, "Realization of IIR/FIR and Npath filters using a novel switched-capacitor technique," IEEE Trans.

Chung-Yu Wu (S'75-M'77) was born in Chiayi, Taiwan, R.O.C., in 1950. He received the B. S. degree from the Department of Electrophysics, and the M.S. and Ph.D. degrees from the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, in 1972, 1976, and 1980, respectively.

During 1975-1976, he studied ferroelectric films on silicon and their device applications. From 1976 to 1979, he engaged in the development of integrated differential negative resistance devices and their circuit applications, with support from the

National Electronics Mass Plan (Seimconductor Devices and Integrated Circuit Technologies) of the National Science Council. From 1980 to 1984 he was an Associate Professor in the Department of Electrical Engineering, Portland State University, Portland, OR. Presently, he is a Professor in the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University. His research interests have been in analog and digital integrated circuits and systems, special semiconductor devices, and neural networks.

Dr. Wu is a member of Eta Kappa Nu and Phi Tau Phi.

Jenn-Chyou Bor was born in Hualian, Taiwan, R.O.C., in 1966. He received the B.S. degree from the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, in 1988. He is currently working toward the Ph.D. degree at the same University.

His main research interests have been in switched-capacitor filters and neural network integrated circuits and systems.

Bor-Shenn Jeng received the B.S. degree in physics from the National Normal University, Taiwan, in 1969; and the M. S. degree in geophysics and the Ph.D. degree in optical sciences from the National Central University, Taiwan, in 1973 and 1990, respectively.

He taught physics at the Chinese Cultural University from 1973 to 1974, and has been with the Telecommunication Laboratories, Directorate General of Telecommunications, Taiwan, since 1974. Currently, he is the director of the Basic and Applied

Technology Laboratory, Telecommunication Laboratories, and the project leader of the digital signal processing project, where he has been working on multimedia, intelligent human/machine interface, Chinese character recognition, generation and compression, etc. He has published more than 100 technical papers in the areas of physics and signal processing.

Dr. Jeng is the recipient of the Distinguished Performance in Information Sciences Award, conferred by the National Science Council, Republic of China, in 1988, and the highest technology award conferred by the government of the Republic of China, the Distinguished Performance in Technology Award, conferred by the Executive Yuan, in 1989.