## Mechanism of Schottky barrier height modulation by thin dielectric insertion on n-type germanium

Bing-Yue Tsui and Ming-Hong Kao

Citation: Applied Physics Letters 103, 032104 (2013); doi: 10.1063/1.4813834

View online: http://dx.doi.org/10.1063/1.4813834

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/103/3?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Fermi level de-pinning of aluminium contacts to n-type germanium using thin atomic layer deposited layers Appl. Phys. Lett. **104**, 012102 (2014); 10.1063/1.4858961

Fermi-level unpinning and low resistivity in contacts to n-type Ge with a thin ZnO interfacial layer Appl. Phys. Lett. **101**, 182105 (2012); 10.1063/1.4764909

Control of Schottky barrier heights by inserting thin dielectric layers

Appl. Phys. Lett. 101, 172907 (2012); 10.1063/1.4764521

Schottky barrier height reduction for metal/n-GaSb contact by inserting TiO 2 interfacial layer with low tunneling resistance

Appl. Phys. Lett. 98, 172106 (2011); 10.1063/1.3584862

Increase in current density for metal contacts to n-germanium by inserting TiO 2 interfacial layer to reduce Schottky barrier height

Appl. Phys. Lett. 98, 092113 (2011); 10.1063/1.3562305

## Mechanism of Schottky barrier height modulation by thin dielectric insertion on n-type germanium

Bing-Yue Tsui<sup>a)</sup> and Ming-Hong Kao

Department of Electronics Engineering, National Chiao Tung University, ED641, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

(Received 15 May 2013; accepted 28 June 2013; published online 16 July 2013)

Although high channel electron mobility has been reported after some passivation techniques, the performance of n-channel Ge metal-oxide-semiconductor field-effect transistor is still limited by the high Schottky barrier height at the metal/n-Ge contact interface, which comes from the Fermi level pinning effect. Recent experiments demonstrated that the Schottky barrier height can be reduced by inserting a thin dielectric layer between metal and Ge. However, the mechanism has not been well clarified. In this paper, the metal induced gap state model, the dipole layer model, and the fixed charge model are verified by varying contact metals, dielectric thicknesses, as well as the annealing temperatures. The pinning factor is improved slightly by dielectric insertion but its value is independent of the dielectric thickness and is still much lower than the ideal value of the non-pinning case. This pinning effect is consistent with the Fermi level pinning at the metal/TiO2 interface. After thermal process, no interfacial layer forms at the TiO<sub>2</sub>/Ge interface and the TiO<sub>2</sub> crystallizes gradually after annealing but the Schottky barrier height increases. Since the amount of fixed charges in the thin dielectric layer estimated from a metal-insulator-semiconductor structure is about  $2 \times 10^{11}$  cm<sup>-2</sup> and is insufficient to produce the observed 0.5 eV Schottky barrier height reduction, it is thus recommended that the main mechanism comes from the change of interface dipoles and the annealing effect is attributed to the short-range ordering of the TiO<sub>2</sub> layer. Furthermore, dielectric with low conduction band offset which has good thermal stability should be explored. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4813834]

Improving the performance of Si-based metal-oxidesemiconductor field-effect transistor (MOSFET) devices by scaling down has encountered many limitations. Because Ge has higher electron (3900 vs 1400 cm<sup>2</sup>/Vs) and hole (1900 vs 500 cm<sup>2</sup>/Vs) bulk mobility than Si, it becomes one of the potential candidates to replace Si as the channel material in the future. Although high channel electron mobility has been measured after some passivation techniques, the driving current of n-channel Ge MOSFET is still poor than that of Si MOSFET due to the high contact resistance between metal and n<sup>+</sup> Ge source/drain region.<sup>2-5</sup> To reduce contact resistance, high doping concentration and low Schottky barrier height are the most critical factors. Unfortunately, the low solid-state solubility of n-type dopants in Ge causes incomplete activation.<sup>6–8</sup> Furthermore, the specific contact resistance at the metal/n<sup>+</sup> Ge contact is high due to the high Schottky barrier height at the metal/n-Ge interface, which comes from the Fermi level pinning (FLP) effect.<sup>9,10</sup>

Recent experiments demonstrated that the Schottky barrier height can be reduced by inserting a thin dielectric layer between metal and Ge as a tunneling barrier. Several dielectrics have been employed. They are  $\mathrm{Si_3N_4}$ ,  $^{12-15}$   $\mathrm{Ge_3N_4}$ ,  $^{16}$   $\mathrm{MgO}$ ,  $^{17-19}$   $\mathrm{Al_2O_3}$ ,  $^{15,19-25}$   $\mathrm{GeO_x}$ ,  $^{23}$  and  $\mathrm{TiO_2}$ ,  $^{23-25}$  Schottky barrier height as low as 65 meV has been reported on the Al/  $\mathrm{TiO_2}$ /Ge structure.  $^{24}$  Three possible mechanisms have been proposed. Originally, it was proposed that the inserted dielectric layer can block the electron wave function from metal to semiconductor and therefore decrease the number

of metal induced gap states (MIGS). 11,14,17,18,23 Latter researches suggest that the dipole formed at the metal/semiconductor interface would cause potential drop to modulate the Schottky barrier height. 13,15,21,22,26–29 Hu *et al.* proposed that the fixed charges in the non-ideal dielectric layers would also cause an extra potential drop across the dielectric layer. <sup>29</sup> In this work, sequential experiments were designed to clarify which mechanism dominates the Schottky barrier height modulation on Ge. The thickness effect and the post deposition annealing effect on the Schottky barrier height are also investigated.

N-type Sb doped (100)-oriented Ge wafer with resistivity of  $0.01~\Omega$ -cm was used. Samples were dipped in diluted HF solution (H<sub>2</sub>O:HF = 20:1) and DI-water for 1 min circularly by three times to clean the surfaces. Then samples were loaded to an atomic layer deposition (ALD) system to deposit thin TiO<sub>2</sub> layer immediately. The TiO<sub>2</sub> layer was deposited using Tetrakis(dimethylamino) titanium (TDMAT) and H<sub>2</sub>O as precursors at 250 °C. The thicknesses of 1 nm and 7 nm are grown by 22 and 154 cycles, respectively. Some samples were then in-situ deposited by a 5-nm-thick TiN layer in the same ALD system using TDMAT as precursor and N2 plasma. After ALD deposition, samples were annealed in vacuum furnace at 300 °C, 400 °C, and 600 °C for 30 min. Then a 300-nm-thick Al was deposited on these samples by a thermal coater and was patterned by a typical lithography process and reactive ion etching process. The samples without TiN contact metal were deposited with different metals, including Pt by a sputtering system, and Ni and Co by an e-gun system. The contact metal was patterned by lift-off process. The other processes were identical to

a) Author to whom correspondence should be addressed. Electronic mail: bytsui@mail.nctu.edu.tw

those of the samples using TiN as contact metal. Finally, after removing the native oxide on the sample backside by buffered oxide etchant (BOE), backside contact was completed with a 300-nm-thick Al deposition by a thermal coater. The electrode area is  $4.9 \times 10^{-4} \, \mathrm{cm}^{-2}$  for all metals.

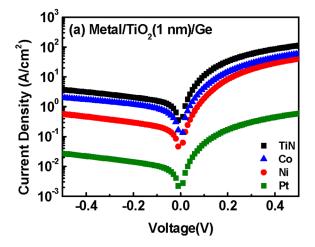

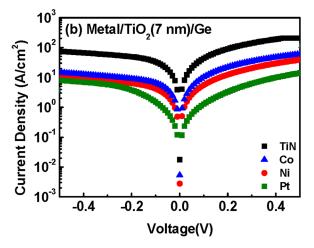

The work functions of Pt, Ni, Co, and TiN are 5.65 eV, 5.15 eV, 5 eV, and 4.5 eV, respectively. 30,31 Metal with further lower work function was not used in this experiment because the Schottky barrier height on the 7-nm-thick TiO<sub>2</sub> contact would be very low (about 0.04 eV for TiN) so that we cannot extract the Schottky barrier height accurately. Figs. 1(a) and 1(b) show the I-V characteristics of the 1-nm-thick and 7-nm-thick TiO<sub>2</sub> contacts, respectively. With higher work function metal, the current densities are lower, which indicates that Schottky barrier height increases with the work function.

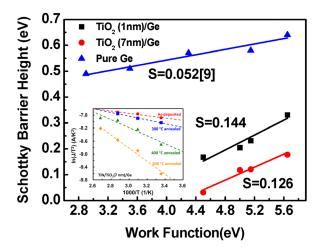

Fig. 2 shows the extracted Schottky barrier height of the 1-nm-thick and 7-nm-thick TiO<sub>2</sub> contacts with different contact metals. The Schottky barrier height of the pure metal/Ge contact is also shown in the figure. These Schottky barrier height values were extracted by the thermionic emission model at reverse bias at temperatures from 25 °C to 100 °C. <sup>20</sup> The inset shows an example of the TiN/TiO<sub>2</sub>(7 nm)/Ge contacts. The slopes of the linear regression lines give the pinning

FIG. 1. Current-voltage characteristics of the Schottky contacts with different contact metals. The contact structure is (a) metal/ $TiO_2$  (1 nm)/Ge and (b) metal/ $TiO_2$  (7 nm)/Ge.

FIG. 2. Extracted effective Schottky barrier height of the contacts without  $TiO_2$  insertion layer, with 1-nm-thick  $TiO_2$  insertion layer, and with 7-nm-thick  $TiO_2$  insertion layer. The inset shows the extraction of the Schottky barrier height of the  $TiN/TiO_2$  (7 nm)/Ge contacts as an example.

factors S. The pinning factor is about 0.052 for the pure Ge junction which is consistent with that reported in literatures.<sup>9,10</sup> For the contacts with TiO<sub>2</sub> insertion layer, the pinning factor is 0.144 for the contacts with 1-nm-thick TiO<sub>2</sub> and 0.126 for the contact with 7-nm-thick TiO<sub>2</sub>. These values are larger than that of the pure Ge junction which means that the FLP effect is mitigated by the TiO<sub>2</sub> insertion layer. The improvement of pinning factor compared with pure Ge may come from the alleviating of MIGS effect. However, it should be noticed that the pinning factors of the contacts with both TiO<sub>2</sub> thicknesses are about the same, which indicates that the depinning effect of the 7-nm-thick TiO<sub>2</sub> is not better than that of the 1-nm-thick TiO<sub>2</sub>. In the case of complete depinning, the pinning factor should approach to 1; the small pinning factors indicate that the FLP effect is not solved completely by the TiO<sub>2</sub> insertion layer. According to the MIGS model, the pinning factor S can be estimated as  $S = \frac{1}{1+0.1(\epsilon_{\infty}-1)^2}$ , where  $\epsilon_{\infty}$  is the electronic component of dielectric constant. Applying this model at the metal/TiO2 interface, the pinning factor S is estimated to be 0.153 as  $\varepsilon_{\infty}(\text{TiO}_2) = 8.427.^{33}$  Since the calculated pinning factor is close to the experimental pinning factor, it is possible that the FLP with TiO<sub>2</sub> insertion is due to the FLP at the metal/TiO<sub>2</sub> interface.

Since the lower Schottky barrier height of the 7-nm-thick TiO<sub>2</sub> contact than the 1-nm-thick contact cannot be explained by the more effective suppression of the MIGS effect by the thicker dielectric, but because the pinning position is changed more for thicker TiO<sub>2</sub> layer. The change of pinning position may result from two factors, fixed oxide charges or dipoles formed at metal/TiO<sub>2</sub> interface and/or TiO<sub>2</sub>/Ge interface; both can introduce an additional potential drop in the current conduction path and results in the reduction of the Schottky barrier height.<sup>29</sup>

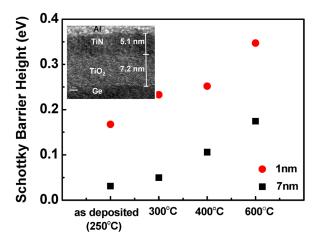

Either dipoles or fixed charges may be changed after thermal process, which in turn changes the effective Schottky barrier height. Fig. 3 shows the Schottky barrier heights of the contacts with 1-nm-thick and 7-nm-thick  $\rm TiO_2$  insertion layer before and after annealing in vacuum at  $\rm 300\,^{\circ}C$ ,  $\rm 400\,^{\circ}C$ , and  $\rm 600\,^{\circ}C$  for 30 min. As the annealing temperature increases, the Schottky barrier height increases,

FIG. 3. Extracted effective Schottky barrier height of the contacts after thermal annealing. The inset is the cross-sectional TEM micrograph of the contact with 7-nm-thick  $\rm TiO_2$  insertion layer after 600 °C annealing.

too. It is noticed that the increments of the Schottky barrier height of the 1-nm-thick and the 7-nm-thick TiO<sub>2</sub> contacts are similar, and the Schottky barrier heights of the 7-nmthick TiO<sub>2</sub> contact are still lower than those of the 1-nmthick TiO<sub>2</sub> contact after annealing. To observe if there is a new interfacial layer formed after annealing, the crosssectional structure of the 600 °C annealed TiN/TiO<sub>2</sub>/Ge contact was inspected by the high-resolution transmission-electron-microscope (TEM) and the micrograph is inserted in Fig. 3. It is clearly that there is no interfacial layer formed at the TiO<sub>2</sub>/Ge interface and the TiN/TiO<sub>2</sub> interface. This result suggests that the Schottky barrier height increment is not due to new layer formation after annealing. If the Schottky barrier height modulation mechanism of the TiO2-inserted contacts mainly results from the fixed charges in TiO2 and these charges are reduced by the annealing process, the Schottky barrier height of the 7-nm-thick TiO<sub>2</sub> contact should be close to that of the 1-nm-thick TiO2 contact. However, this prediction conflicts with the experimental results. It could be estimated that if the Schottky barrier height modulation comes from the fixed charges, the charge density should be as high as  $3 \times 10^{13} \text{ cm}^{-2}$  to produce a 0.5 eV Schottky barrier height reduction assuming the relative dielectric constant of TiO2 is 80.<sup>34</sup> Lee has studied the C-V characteristics of the TiO<sub>2</sub>/Ge and TiO<sub>2</sub>/SiO<sub>2</sub>/Ge structures.<sup>35</sup> Although the TiO<sub>2</sub>/Ge sample showed distorted C-V curve due to its high leakage current, the difference in total charge between the two samples is only  $2 \times 10^{11}$  cm<sup>-2</sup>, which is much lower than that required to produce a 0.5 eV Schottky barrier height reduction. Therefore, it is recommended that the Schottky barrier height modulation of the TiO2-inserted contact is mainly caused by the interface dipoles.

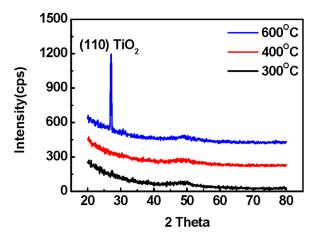

Fig. 4 shows the XRD spectra of the 7-nm-thick  $TiO_2$ -inserted junction after annealing at  $300\,^{\circ}\text{C}$ ,  $400\,^{\circ}\text{C}$ , and  $600\,^{\circ}\text{C}$  for  $30\,\text{min}$ , respectively. The  $TiO_2$  and TiN layers remain in amorphous state after  $400\,^{\circ}\text{C}$  annealing. The (110)-oriented rutile phase of  $TiO_2$  is detected on the  $600\,^{\circ}\text{C}$  annealed sample. However, Raman analysis suggested short-range ordering in the amorphous  $TiO_2$  phase at annealing temperatures of  $200-400\,^{\circ}\text{C}$ . Thus, it is postulated that with the increase in annealing temperature, the  $TiO_2$  layer is gradual crystallized and the interface dipoles change

FIG. 4. X-ray diffraction spectra of the contacts with 7-nm-thick TiO<sub>2</sub> insertion layer after annealing at 300, 400, and 600 °C.

simultaneously. The change of dipoles affects the stability of the Schottky barrier height modulation.

In summary, we examined the three possible mechanisms, MIGS model, dipole model, and fixed charge model, of the dielectric insertion induced Schottky barrier height modulation of the metal/TiO<sub>2</sub>/n-type Ge contact. The main cause is not the release of FLP effect but the shift of pinning position. Interface dipole plays more significant role than the fixed charge. Thermal annealing in vacuum at temperature as low as 300 °C changes the interface dipole due to the short-range ordering of the TiO<sub>2</sub> layer so that the Schottky barrier height changes. The Schottky barrier height of the Al/TiO<sub>2</sub>(7 nm)/Ge contact increases from 0.03 to 0.11 eV after 400 °C annealing. Beyond 400 °C, the Schottky barrier height would be too high to maintain good contact property.

The authors would like to thank the Nano Facility Center of National Chiao-Tung University for providing the experimental facilities. This work was supported in part by the Ministry of Education in Taiwan under ATU Program, and was supported in part by the National Science Council, Taiwan, R.O.C. under the contract No. NSC 100-2221-E-009-010-MY2.

<sup>&</sup>lt;sup>1</sup>H. Shang, M. M. Frank, E. P. Gusev, J. O. Chu, S. W. Bedell, K. W. Guarini, and M. Ieong, IBM J. Res. Dev. **50**, 377 (2006).

<sup>&</sup>lt;sup>2</sup>D. Kuzum, T. Krishnamohan, A. Nainani, Y. Sun, P. A. Pianetta, H. S. P. Wong, and K. C. Saraswat, Tech. Dig. - Int. Electron Devices Meet. 453 (2009).

<sup>&</sup>lt;sup>3</sup>L. Hutin, C. L. Royer, J.-F. Damlencourt, J. M. Hartmann, H. Grampeix, V. Mazzocchi, C. Tabone, B. Previtali, A. Pouydebasque, M. Vinet, and O. Faynot, IEEE Electron Dev. Lett. 31, 234 (2010).

<sup>&</sup>lt;sup>4</sup>R. Zhang, T. Iwasaki, N. Taoka, M. Takenaka, and S. Takagi, IEEE Transactions on Electron Devices **59**, 335 (2012).

<sup>&</sup>lt;sup>5</sup>R. Zhang, P. C. Huang, J. C. Lin, N. Taoka, M. Takenaka, and S. Takagi, IEEE Trans. Electron Devices **60**, 927 (2013).

<sup>&</sup>lt;sup>6</sup>C. T. Chung, C. W. Chen, J. C. Lin, C. C. Wu, C. H. Chien, and G. L. Luo, Tech. Dig. - Int. Electron Devices Meet. 383 (2012).

<sup>&</sup>lt;sup>7</sup>D. P. Brunco, B. De Jaeger, G. Eneman, J. Mitard, and G. Hellings, J. Electrochem. Soc. **155**, H552 (2008).

<sup>&</sup>lt;sup>8</sup>C. O. Chui, L. Kulig, J. Moran, W. Tsai, and K. C. Saraswat, Appl. Phys. Lett. 87, 091909 (2005).

<sup>&</sup>lt;sup>9</sup>S. Brotzmann and H. Bracht, J. Appl. Phys. **103**, 033508 (2008).

<sup>&</sup>lt;sup>10</sup>A. Dimoulas, P. Tsipas, A. Sotiropoulos, and E. K. Evangelou, Appl. Phys. Lett. 89, 252110 (2006).

Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Lett. 91, 123123 (2007).

M. Kobayashi, A. Kinoshita, K. C. Saraswat, H.-S. P. Wong, and Y. Nishi, J. Appl. Phys. 105, 023702 (2009).

- <sup>13</sup>J. F. Wager and J. Robertson, J. Appl. Phys. **109**, 094501 (2011).

- <sup>14</sup>M. Kobayashi, A. Kinoshita, K. C. Saraswat, H. S. Wong, and Y. Nishi, IEEE Symp. VLSI Technol. 54 (2008).

- <sup>15</sup>L. Lin, J. Robertson, and S. J. Clark, Microelectron. Eng. 88, 1461 (2011).

- <sup>16</sup>R. R. Lieten, S. Degroote, M. Kuijk, and G. Borghs, Appl. Phys. Lett. 92, 022106 (2008).

- <sup>17</sup>D. Lee, S. Raghunathan, R. J. Wilson, D. E. Nikonov, K. C. Saraswat, and S. X. Wang, Appl. Phys. Lett. **96**, 052514 (2010).

- <sup>18</sup>Y. Zhou, W. Han, Y. Wang, F. Xiu, J. Zou, R. K. Kawakami, and K. L. Wang, Appl. Phys. Lett. **96**, 102103 (2010).

- <sup>19</sup>Y. Zhou, M. Ogawa, M. Bao, W. Han, R. K. Kawakami, and K. L. Wang, Appl. Phys. Lett. **94**, 242104 (2009).

- <sup>20</sup>Y. Zhou, M. Ogawa, X. Han, and K. L. Wang, Appl. Phys. Lett. 93, 202105 (2008).

- <sup>21</sup>A. M. Roy, J. Y. J. Lin, and K. C. Saraswat, IEEE Electron Device Lett. 31, 1077 (2010).

- <sup>22</sup>B. E. Coss, C. Smith, W.-Y. Loh, P. Majhi, R. M. Wallace, J. Kim, and R. Jammy, IEEE Electron Device Lett. 32, 862 (2011).

- <sup>23</sup>T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Express 1, 051406 (2008).

- <sup>24</sup>B. E. Coss, C. Smith, W.-Y. Loh, P. Majhi, R. M. Wallace, J. Kim, and R. Jammy, IEEE Electron Device Lett. 32, 862 (2011).

- <sup>25</sup>J.-Y. Jason Lin, A. M. Roy, A. Nainani, Y. Sun, and K. C. Saraswat, Appl. Phys. Lett. 98, 092113 (2011).

- <sup>26</sup>B. E. Coss, P. Sivasubramani, B. Brennan, P. Majhi, R. M. Wallace, and J. Kima, J. Vac. Sci. Technol. B 31, 021202 (2013).

- <sup>27</sup>J. Hu, K. C. Saraswat, and H.-S. P. Wong, J. Appl. Phys. **107**, 063712 (2010)

- <sup>28</sup>B. E. Coss, W.-Y. Loh, R. M. Wallace, J. Kim, P. Majhi, and R. Jammy, Appl. Phys. Lett. **95**, 222105 (2009).

- <sup>29</sup> J. Hu, A. Nainani, Y. Sun, K. C. Saraswat, and H.-S. Philip Wong, Appl. Phys. Lett. **99**, 252104 (2011).

- <sup>30</sup>H. B. Michaelson, J. Appl. Phys. **48**, 4729 (1977).

- <sup>31</sup>A. Yagishita, T. Saito, K. Nakajima, S. Inumiya, K. Matsuo, T. Shibata, Y. Tsunashima, K. Suguro, and T. Arikado, IEEE Trans. Electron Devices 48, 1604 (2001).

- <sup>32</sup>Y. C. Yeo, T. J. King, and C. Hu, J. Appl. Phys. **92**, 7266 (2002).

- <sup>33</sup>J. G. Traylor, H. G. Smith, R. M. Nicklow, and M. K. Wilkinson, Phys. Rev. B 3, 3457 (1971).

- <sup>34</sup>S. K. Kim, W.-D. Kim, K.-M. Kim, C. S. Hwanga, and J. Jeong, Appl. Phys. Lett. 85, 4112 (2004).

- <sup>35</sup>S. Y. Lee, W. Lee, H.-S. Jung, H. K. Kim, and C. S. Hwang, in ALD 2011 (poster), Cambridge, 26–29 June 2011.

- <sup>36</sup>A. F. Khan, M. Mehmood, M. Aslam, and S. I. Shah, J. Colloid Interface Sci. 343, 271 (2010).