# An Efficient Method for Analyzing On-Chip Thermal Reliability Considering Process Variations

YU-MIN LEE, National Chiao Tung University PEI-YU HUANG, Industrial Technology Research Institute

This work provides an efficient statistical electrothermal simulator for analyzing on-chip thermal reliability under process variations. Using the collocation-based statistical modeling technique, first, the statistical interpolation polynomial for on-chip temperature distribution can be obtained by performing deterministic electrothermal simulation very few times and by utilizing polynomial interpolation. After that, the proposed simulator not only provides the mean and standard deviation profiles of on-chip temperature distribution, but also innovates the concept of thermal yield profile to statistically characterize the on-chip temperature distribution more precisely, and builds an efficient technique for estimating this figure of merit. Moreover, a mixed-mesh strategy is presented to further enhance the efficiency of the developed statistical electrothermal simulator.

Experimental results demonstrate that (1) the developed statistical electrothermal simulator can obtain accurate approximations with orders of magnitude speedup over the Monte Carlo method; (2) comparing with a well-known cumulative distribution function estimation method, APEX [Li et al. 2004], the developed statistical electrothermal simulator can achieve  $215\times$  speedup with better accuracy; (3) the developed mixed-mesh strategy can achieve an order of magnitude faster over our baseline algorithm and still maintain an acceptable accuracy level.

Categories and Subject Descriptors: B.7.2 [Integrated Circuits]: Design Aids; B.8.2 [Performance and Reliability]: Performance Analysis and Design Aids

General Terms: Design, Algorithms, Performance, Reliability

Additional Key Words and Phrases: Electrothermal simulation, thermal analysis, chip temperature, thermal reliability, process variation, simulation

### **ACM Reference Format:**

Lee, Y.-M. and Huang, P.-Y. 2013. An efficient method for analyzing on-chip thermal reliability considering process variations. ACM Trans. Des. Autom. Electron. Syst. 18, 3, Article 41 (July 2013), 32 pages. DOI: http://dx.doi.org/10.1145/2491477.2491485

### 1. INTRODUCTION

As technology scales down to the sub-90nm node, on-chip power densities increase rapidly. Hence, power dissipation and thermal management have become important issues of VLSI design. High on-chip temperature distribution and thermal gradients

Preliminary versions of this article appeared in *Proceedings of the IEEE International Systems-on-Chip Conference (SoCC'10)* [Chang et al. 2010] and in *Proceedings of the IEEE/ACM International Asia and South Pacific Design Automation Conference (ASP-DAC'12)* [Huang et al. 2012].

This work was supported in part by the National Science Council of Taiwan under grants NSC 99-2220-E-009-035, 100-2221-E-009-074, and 101-2221-E-009-168, and by the Industrial Technology Research Institute, Taiwan.

Authors' addresses: Y.-M. Lee, Department of Electrical and Computer Engineering, National Chiao Tung University, HsinChu, Taiwan; email: yumin@nctu.edu.tw; P.-Y. Huang, Industrial Technology Research Institute, Taiwan.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 2013 ACM 1084-4309/2013/07-ART41 \$15.00 DOI: http://dx.doi.org/10.1145/2491477.2491485

drastically degrade the circuit performance and design reliability, operating temperatures seriously affect gate delays [Kumar and Kursun 2006], and nonuniform on-chip temperature distribution induces timing faults [Bota et al. 2004]. Since on-chip power consumption is proportional to operating temperatures, thermal runaway might occur if thermal-related issues are not carefully considered in package design [Vassighi and Sachdev 2006]. To ensure design qualities, such as performance, power consumption, and reliability, researchers have been devoted to dealing with thermal-related issues in physical design [Tsai et al. 2006; Liu et al. 2008]. To provide the related thermal cost for optimization engines of physical design, several efficient deterministic thermal simulators [Wang and Chen 2003; Huang et al. 2006; Yang et al. 2007; Huang and Lee 2009] have been developed to predict on-chip temperature profile. However, these thermal simulators only provide thermal information with deterministic on-chip power consumption.

As predicted by the international technology roadmap for semiconductors (ITRS), leakage power consumption increases dramatically and has become a dominant portion of total power consumption [ITRS 2010]. Moreover, the scaling down of technology causes physical parameter variations to be non-ignorable, and this fact leads to substantial on-chip leakage power fluctuations. As pointed out by Pang and Nikolic, 8% of process variations can lead to about 25% of on-chip leakage power fluctuations [2009]. Therefore, physical parameter variations are essential to be considered for on-chip power estimation techniques [Chang and Sapatnekar 2007; Shen et al. 2010b, 2010a]. Since on-chip temperature is transferred from on-chip power consumption, its distribution is impacted by process variations inducing leakage power fluctuations. However, deterministic thermal analyzers [Wang and Chen 2003; Huang et al. 2006; Yang et al. 2007; Huang and Lee 2009, which did not take process variations into account in their power models, are not adequate to precisely provide thermal reliability estimation under process variations. Therefore, the on-chip temperature profile should be treated statistically under process variations, and statistical thermal simulation techniques are essential, especially for leakage dominated technologies [Huang et al. 2009; Jaffari and Anis 2008l.

To provide the statistical characteristics of on-chip temperature distribution, Jaffari and Anis [2008] proposed a recursive log-normal approximation algorithm to obtain mean and standard deviation profiles of the on-chip temperature distribution. Compared with the Monte Carlo (MC) simulations, they have successfully demonstrated its efficiency and accuracy for estimating mean and standard deviation profiles of the temperature distribution in the macro-architectural level. Instead of constructing the different leakage power model for each different macro/gate type, they built the different leakage power model for each bin (grid) on a die. Since optimization engines, such as floorplanners or placers, might disturb positions of macros or gates, their related leakage power models need to be rebuilt after an optimization loop is executed. Therefore, the efficiency of their approach will be degraded while casting into thermal-aware design flows, because their approach needs to execute the time-consuming HSPICE simulation numerous times and fit curves for reestablishing leakage power models. In addition, their recursive log-normal approximation algorithm is restricted to the form of their proposed leakage power models. However, the leakage power model is getting more complicated for maintaining an acceptable accuracy level as the technology continuously scales down. To overcome the leakage power model restriction, a statistical thermal simulation framework that has high capability of adopting complex and accurate power models for any technology generations is required.

Besides the leakage power model issues, the figure of merit for on-chip temperature distribution is still ambiguous if only its mean and standard deviation profiles are

reported.<sup>1</sup> Therefore, instead of only reporting mean and standard deviation profiles, a more precise figure of merit for the statistical characteristics of on-chip temperature distribution should be addressed to ensure the thermal reliability or to provide the thermal related cost for thermal-aware design engines.

In this work, a statistical simulation framework is developed for characterizing the on-chip temperature distribution. With the aim of dealing with the restriction issues of leakage power models, providing a more precise figure of merit for ensuring thermal reliability and being more easily incorporated into statistical performance analysis and design engines, technical key points and advantages of this work are summarized as follows.

- (1) Compared with the bin-based model [Jaffari and Anis 2008], a cell-based model is adopted for characterizing leakage powers. With the precharacterizing property, the reestablishing process of leakage power models can be avoided, while macros or gates are exchanged by optimization engines, such as floorplanners or placers.

- (2) Adopting the concept of sparse collocation-based methods, a statistical electrothermal simulation framework is developed to generate the statistical polynomial expression of on-chip temperature distribution. Compared with that of Jaffari and Anis [2008], the developed framework is more flexible for complex and precise leakage powers models.

- (3) This work not only provides the mean and standard deviation profiles of on-chip temperature distribution, but also introduces the concept of *thermal yield profile* to statistically characterize the on-chip temperature distribution more precisely, and builds an efficient estimating technique for this figure of merit.

- (4) Without sacrificing the accuracy, a mixed-mesh strategy is presented and integrated into the baseline method of our statistical electrothermal simulation engine to further enhance its efficiency.

The rest of this article is organized as follows. Section 2 motivates the concept and essentialness of on-chip *thermal yield profile*, investigates the accuracy of existing cell-based leakage power models, and indicates that complex leakage current models are required for maintaining acceptable accuracy level. After that, the problem formulation and the modeling technique of device parameters are described in Section 3. Then, the developed statistical electrothermal simulator is detailed in Section 4, and experimental results are given in Section 5. Finally, the conclusion and potential applications of the developed simulation framework are presented in Section 6.

### 2. MOTIVATION ILLUSTRATIONS

### 2.1. Concept of On-Chip Thermal Yield Profile

Because of process variations, on-chip temperature at an arbitrary position  ${\bf r}$  is a random variable. Therefore, the deterministic thermal analysis with nominal on-chip power profile can no longer be a good figure of merit for identifying the hotspot location of the chip. Moreover, even if the temperature at any arbitrary position  ${\bf r}$  has been treated as a random variable, it will still be ambiguous if only the mean  $(\mu_T({\bf r}))$  and standard deviation  $(\sigma_T({\bf r}))$  profiles of on-chip temperature distribution are delivered. For example, only using the mean profile of on-chip temperature distribution as a figure of merit is very likely (about 50%) to incorrectly indicate hotspot locations. Furthermore, as both  $\mu_T({\bf r})$  and  $\sigma_T({\bf r})$  are delivered, by utilizing the Chebyshev inequality, a large temperature value will be estimated to ensure the lower bound

<sup>&</sup>lt;sup>1</sup>Please see the interpretation stated in Section 2.1.

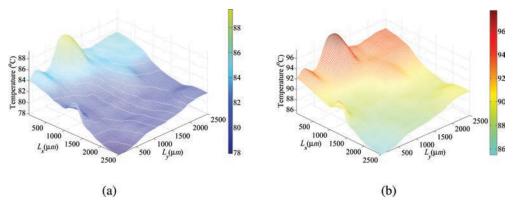

Fig. 1. An example to demonstrating the gap between the temperature profile that really achieves 90% thermal reliability and the temperature profile that satisfies the lower bound of 90% thermal reliability in the Chebyshev inequality: (a) the temperature profile that really achieves 90% thermal reliability,  $T_{\rm Real}^{90}(\mathbf{r})$ ; (b) the temperature profile that satisfies the lower bound of 90% thermal reliability in the Chebyshev inequality,  $T_{\rm Chebyshev}^{90}(\mathbf{r})$ .

of 90% thermal reliability, that is,  $T_{\text{Chebyshev}}^{90}(\mathbf{r})$  needs to be  $\mu_T(\mathbf{r}) + 3\sigma_T(\mathbf{r})$  to ensure  $\mathbf{Prob}(T(\mathbf{r}) \leq T_{\text{Chebyshev}}^{90}(\mathbf{r})) \geq 0.9$ . Here,  $T(\mathbf{r})$  is the on-chip temperature distribution.

Since the Chebyshev inequality does not always get a tight lower bound for any type of random variables, there will be a gap between the temperature profile,  $T_{\rm Real}^{90}({\bf r})$ , that really achieves 90% thermal reliability (i.e.,  ${\bf Prob}(T({\bf r}) \leq T_{\rm Real}^{90}({\bf r})) = 0.9$ ), and  $T_{\rm Chebyshev}^{90}({\bf r})$ . As shown in Figure 1, the gap between  $T_{\rm Real}^{90}({\bf r})$  and  $T_{\rm Chebyshev}^{90}({\bf r})$  can achieve about 10°C in our experimental results. Therefore, using the temperature profile of the Chebyshev bound might be an immoderately conservative constraint for thermal reliability. This undesirable phenomenon can result in immoderate guard-banding for circuit design.

On the other hand, from the aspect of circuit design, the specifications of circuit performance and the timing constrains of primary I/Os are usually specified in the system-level design stage. Moreover, in the timing and thermal cooptimization process, timing issues usually take higher priority than thermal issues. Designers try to minimize the circuit delay and meet the temperature requirement. Therefore, in the presence of process variations, to identify possible hotspot regions of a chip, the thermal yield profile, T yield( $\mathbf{r}$ , T<sub>spec</sub>( $\mathbf{r}$ )), can be defined as the probability profile of the on-chip temperature at an arbitrary position  $\mathbf{r}$  being at or less than a specified temperature T<sub>spec</sub>( $\mathbf{r}$ ).

The thermal yield profile can identify the hotspot regions and can also quantify the probability of a region that could be a hotspot. Therefore, it is a suitable figure of merit for the thermal-related cost in timing-thermal cooptimization physical design stages.

### 2.2. Leakage Power Modeling

Leakage currents of a gate not only depend on physical device parameters and operating temperatures but also on its input patterns [Chang and Sapatnekar 2007]. To build leakage power models, different input patterns, physical parameters, and operating temperatures are set for each gate in the cell library, and HSPICE simulation is

<sup>&</sup>lt;sup>2</sup>For example, given a standard normal random variable x with  $\mathbf{Prob}(x \le 1.28\sigma_x) = 0.9$ , however, the Chebyshev inequality requires a larger reference value to obtain the same probability as the lower bound, i.e.,  $\mathbf{Prob}(x \le 3\sigma_x) \ge 0.9$ .

|                     | $f_g(L,t_{ox},T)$                                                                                                                                                                             | maximum<br>error | average<br>error | error > 3% |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------|

| Without temperature | $t_{ox}, L, t_{ox}^2, L^2$ [Chang and Sapatnekar 2007; Shen et al. 2010b]                                                                                                                     | 6.48%            | 2.70%            | 4.37%      |

| With                | $L, t_{ox}, T$                                                                                                                                                                                | 3.20%            | 0.97%            | 0.35%      |

| temperature         | $\dagger L, t_{ox}, T, t_{ox}^2$                                                                                                                                                              | 1.55%            | 0.29%            | 0.00%      |

|                     | $f_s(L, t_{ox}, T)$                                                                                                                                                                           | maximum<br>error | average<br>error | error > 3% |

| Without             | $L, t_{ox}, t_{ox}^2, t_{ox}^{-1}$ [Chang and Sapatnekar 2007]                                                                                                                                | 347.32%          | 70.65%           | 98.27%     |

| temperature         | $[L, t_{ox}, Lt_{ox}, L^2, t_{ox}^2, t_{ox}^{-1}, Lt_{ox}^{-1}, L^{-1}t_{ox}]$<br>[Shen et al. 2010b, 2010a]                                                                                  | 314.13%          | 70.52%           | 100.00%    |

|                     | $L, T, t_{ox}$ [Yu et al. 2009]                                                                                                                                                               | 32.23%           | 8.73%            | 76.62%     |

| With                | $(L, t_{ox}, T)$ are fully expanded to 2nd order $\Longrightarrow$ $L, t_{ox}, T, Lt_{ox}, t_{ox}T, TL, L^2, t_{ox}^2, T^2$                                                                   | 10.31%           | 1.53%            | 8.47%      |

| temperature         | $\dagger (L, t_{ox}, T)$ are fully expanded to 3rd order $\Longrightarrow$ $L, t_{ox}, T, Lt_{ox}, t_{ox}T, TL, L^2, t_{ox}^2, T^2, Lt_{ox}T, L^2t_{ox}, t_{ox}^2T, T^2L, L^3, t_{ox}^3, T^3$ | 1.31%            | 0.19%            | 0.00%      |

Table I. Accuracy Comparison of  $I_g$  and  $I_s$  with HSPICE Simulation Results for an NAND Gate

$\dagger$  The adoptive forms of  $f_g$  and  $f_s$  in this work. Note: The second column shows the fitting components of  $f_g$  and  $f_s$  adopted by existing and proposed models.

performed with the industry design kit to generate data of the leakage currents. After that, average leakage currents of the input patterns are fitted by the least squares method. With leakage currents exponentially relating with physical parameters and operating temperatures and using the least squares fitting method, two major leakage currents—gate tunneling leakage current  $(I_g)$  and subthreshold leakage current  $(I_s)$  for each gate type can be fitted [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b; Yu et al. 2009l.

$$I_g(L, t_{ox}, T) = a_0 \exp(f_g(L, t_{ox}, T)),$$

(1)

$$I_s(L, t_{ox}, T) = b_0 \exp(f_s(L, t_{ox}, T)).$$

(2)

Here,  $a_0$  and  $b_0$  are fitting constants, L is the channel length,  $t_{ox}$  is the oxide thickness, T is the operating temperature, and  $f_g(\cdot)$  and  $f_s(\cdot)$  are specific fitting forms.<sup>3</sup>

Basically,  $I_g$  occurs in both on and off states, and  $I_s$  is the off-state leakage mechanism. Therefore, the leakage power of a gate can be represented as follows [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b; Yu et al. 2009].

$$P_{leak}(L, t_{ox}, T) = V_{dd}I_g + (1 - Sw)V_{dd}I_s,$$

(3)

where  $V_{dd}$  is the supply voltage and Sw is the switching activity.

To adopt suitable leakage power models, different cell-based leakage current models are investigated [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b; Yu et al. 2009]. To examine their accuracy, we have implemented their proposed models and compared their results with that of HSPICE simulation under TSMC 65nm design kit. Since leakage currents are temperature-dependent, simulation results show that the ignorance of temperature effect in the models [Chang and Sapatnekar 2007; Shen et al. 2010b, 2010al leads to considerable errors. As shown in the second row of Table I, the

$<sup>^3</sup>$ Variations of the device channel length and oxide thickness are considered in this work, since leakage power is more sensitive to these parameters [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b]. It should be noted that although only these two parameters are considered, the developed framework can be easily extended to include any other process variation types, such as the channel dopant variation.

| Leakage Current | maximum error | average error | error > 3% |  |  |  |  |  |

|-----------------|---------------|---------------|------------|--|--|--|--|--|

| Subthreshold    | 35.53%        | 9.82%         | 79.34%     |  |  |  |  |  |

| Gate Tunneling  | 4 51%         | 1.07%         | 6.32%      |  |  |  |  |  |

Table II. Error of Leakage Current Models Proposed by [Jaffari and Anis 2008] for an NAND Gate under 65nm Technology Node

model adopted by Chang and Sapatnekar [2007] and Shen et al. [2010b] can provide acceptable accuracy for the gate tunneling leakage current because of its insensitivity to operating temperatures. However, since the subthreshold leakage current is sensitive to operating temperatures, as shown in the sixth and seventh rows of Table I, the models [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b] are not adequate for preserving the accuracy.

To simultaneously take temperatures and process variations into account, Yu et al. proposed a first-order exponential model,  $b_0 \exp(b_1L + b_2t_{ox} + b_3T)$ , for the subthreshold leakage current [2009]. Their model can provide accurate results for the 90nm technology node. However, since the variability of subthreshold leakage current, because of operating temperatures and physical device parameters, will increase for more advanced technologies, considerable errors occur for simulation results under the 65nm technology node, as shown in the eighth row of Table I. To improve the accuracy for modeling leakage currents, the orders of fitting components for  $f_g(L, t_{ox}, T)$  and  $f_s(L, t_{ox}, T)$  shown in Eqs. (1) and (2) are increased. As shown in the fourth and tenth rows of Table I, compared with some models [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b; Yu et al. 2009], our models can present accurate results for both gate tunneling and subthreshold leakage currents. As demonstrating by the test results, exquisite approaches are still required for modern statistical power analyzers [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b] to refine the estimated result, while the temperature-dependent leakage power model is included.

Besides the cell-based leakage current models [Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b; Yu et al. 2009], Jaffari and Anis proposed a bin (grid)-based leakage power model that also simultaneously contains temperature and process variation effects [2008]. Adopting the bin (grid)-based leakage power model, Haghdad and Anis developed a power yield analysis engine that simultaneously considers temperature and process variation effects [2012]. However, the power dissipation of several bins might be changed because of disturbing macros/cells after each optimization iteration of thermal-aware design engines, such as floorplanners or placers. Therefore, the time-consuming HSPICE simulation and least-squares fitting process need to be reperformed for rebuilding leakage power models of the disturbed bins (grids). This will degrade its efficiency of providing thermal reliability information or thermal-related cost for thermal-aware design engines. We have implemented their leakage power models for examining the accuracy. With the fitting forms adopted in Jaffari and Anis [2008] and Haghdad and Anis [2012], both subthreshold and gate tunneling leakage currents of each gate type in the cell library are fitted as  $a_0(1+a_1T+a_2T^2)\exp(a_3L+a_4t_{ox})$ . The fitting results are also compared with those of HSPICE simulations under the TSMC 65nm model card, and listed in Table II. The results show that their adopted leakage power models present considerable errors under the 65nm technology node, although adequate accuracy of these models for the 90nm technology node has been reported [Jaffari and Anis 2008]. As shown in Table II, their adopted leakage power models result in the maximum error being 35.53% and the average error being 9.82% for the subthreshold leakage current of an NAND gate under the 65nm technology node.

Demonstrating results, more accurate leakage power models should be adopted in the electrothermal analysis frameworks [Jaffari and Anis 2008; Haghdad and Anis 2012] to refine the estimated results, since the temperature is transferred from power consumption. Although the electrothermal analysis frameworks proposed [Jaffari and

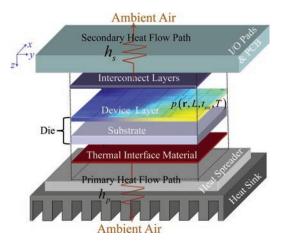

Fig. 2. Compact thermal model of physical design stages.

Anis 2008; Haghdad and Anis 2012] can be very efficient, their baseline temperature calculation frameworks require exquisite extending strategies, because their lognormal temperature approximation algorithm can not be applied to the leakage power models that are not expressed as log-normal random variables, that is, the first-order regression models for  $f_g(L, t_{ox}, T)$  and  $f_s(L, t_{ox}, T)$  in Eqs. (1) and (2) are not sufficient for the accuracy.

Compared with the framework in Jaffari and Anis [2008] and Haghdad and Anis [2012], our proposed thermal reliability estimator can handle accurate and more complicated leakage power models and present accurate estimated results.

### 3. PROBLEM FORMULATION AND PHYSICAL PARAMETER MODELING

### 3.1. Problem Formulation

The compact thermal model for physical design stages is shown in Figure 2 [Wang and Chen 2003; Huang et al. 2006; Yang et al. 2007; Huang and Lee 2009]. It consists of three portions. The primary heat flow path is composed of the thermal interface material, heat spreader, and heat sink. The secondary heat flow path contains interconnect layers, I/O pads, and the print circuit board. Functional blocks of the die are modeled as many power-generating sources attached to a thin layer close to the top surface of the die with the thickness being equal to the junction depth of device [Lallement et al. 2004]. Due to variations of physical parameters, the power consumption of functional blocks is treated statistically. Therefore, the profile of power generating sources,  $p(\mathbf{r}, L, t_{ox}, T)$ , shown in Figure 2 is modeled as a function of device channel length L, oxide thickness  $t_{ox}$ , and on-chip temperature distribution T.

Combining the compact thermal model and the statistical power consumption of functional blocks, the on-chip temperature distribution  $T(\mathbf{r}, L, t_{ox})$  can be governed by the statistical steady state heat transfer equation.<sup>4</sup>

$$\nabla \cdot (\kappa(\mathbf{r}, T) \nabla T(\mathbf{r}, L, t_{ox})) = -p(\mathbf{r}, L, t_{ox}, T), \tag{4}$$

<sup>&</sup>lt;sup>4</sup>Since the time constant of heat conduction is much larger than the clock period of the circuit [Wang and Chen 2003; Skadron et al. 2004], steady-state characteristics of the on-chip temperature distribution are more concerned in thermal-aware physical design engines [Han and Koren 2007; Chakraborty et al. 2008; Tsai et al. 2006]. The scope of this article is to provide a simulation framework for thermal-aware physical design engines, although temporary characteristics of the on-chip temperature distribution are also important for the post-floorplanning or placement real-time task scheduling or workload assignment [Reda et al. 2011].

```

Set T_{\text{nom}} and T_{\text{nom}}^{\text{old}} to be the room temperature values;

1

2

Obtain thermal conductivity by using T_{nom};

Obtain P_{\text{nom}} by T_{\text{nom}}, and nominal values of L and t_{ox},

and set P_{\text{nom}}^{\text{old}} to be P_{\text{nom}}; error<sub>P</sub> \leftarrow 1.0;

5

While error_P > \varepsilon_P

error_T \leftarrow 1.0;

6

7

While error_T > \varepsilon_T

8

Obtain T_{\text{nom}} by the 1-D thermal model [Huang and Lee 2009] with P_{\text{nom}}^{\text{old}};

9

Update thermal conductivity \kappa by using T_{nom};

error<sub>T</sub> \leftarrow \frac{|T_{\text{nom}} - T_{\text{nom}}^{\text{old}}|}{T_{\text{nom}}};

T_{\text{nom}}^{\text{old}} \leftarrow T_{\text{nom}};

10

11

EndWhile

12

13

Obtain P_{\text{nom}} by T_{\text{nom}}, and nominal values of L and t_{ox};

error<sub>P</sub> \leftarrow \frac{|P_{\text{nom}} - P_{\text{nom}}^{\text{old}}|}{|P_{\text{nom}}|};

P_{\text{nom}}^{\text{old}} \leftarrow P_{\text{nom}};

14

15

16

```

Fig. 3. An iterative scheme for computing the appropriate thermal conductivity and approximated average of steady-state nominal temperature values.  $T_{\text{nom}}$  is the average of on-chip mean temperature values, and  $P_{\text{nom}}$  is the total nominal power consumption after executing an iteration. With nominal values of the physical device parameters and  $T_{\text{nom}}$ ,  $P_{\text{nom}}$  can be obtained by summing up the power values of all gates in the design.

subject to the boundary condition

$$\kappa(\mathbf{r}_{b_s}, T) \frac{\partial T(\mathbf{r}_{b_s}, L, t_{ox})}{\partial \vec{n}_{b_o}} + h_{b_s} T(\mathbf{r}_{b_s}, L, t_{ox}) = f_{b_s}(\mathbf{r}_{b_s}). \tag{5}$$

Here,  $\mathbf{r}=(x,y,z)\in D$ ,  $D=(0,L_x)\times (0,L_y)\times (-L_z,0)$  is the domain of die,  $L_x$  and  $L_y$  are the lateral sizes of die,  $L_z$  is the thickness of die,  $\kappa(\mathbf{r},T)$  is the thermal conductivity  $(W/m\cdot{}^{\circ}C)$  of die, and  $\nabla$  is a diverge operator.  $b_s$  is any specific boundary surfaces of the die,  $\mathbf{r}_{b_s}$  is the position on  $b_s$ ,  $h_{b_s}$  is the heat transfer coefficient on  $b_s$ ,  $f_{b_s}(\mathbf{r}_{b_s})$  is the heat flux function on  $b_s$ , and  $\partial/\partial \vec{n}_{b_s}$  is the differentiation along the outward direction which is normalized to  $b_s$ .  $p(\mathbf{r}, \dot{L}, t_{ox}, T)$  is the power density profile that consists of the deterministic dynamic power density profile  $p_d(\mathbf{r})$ , the statistical gate tunneling leakage power density profile  $p_g(\mathbf{r}, L, t_{ox}, T)$ , and the statistical subthreshold leakage power density profile  $p_s(\mathbf{r}, L, t_{ox}, T)$ . Since the major part of device current flows through the channel, power density distribution has its value only when  $\mathbf{r} \in (0, L_x) \times (0, L_y) \times (-j_d, 0)$ . Here,  $j_d$  is the junction depth of device [Lallement et al. 2004].

Generally, the values of  $\kappa(\mathbf{r},T)$  are temperature dependent. In practice, they can be treated as appropriate constant values while performing temperature-aware physical design procedures [Tsai et al. 2006]. Given nominal values of the physical device parameters, the appropriate thermal conductivity can be computed by using the approximated average of steady-state nominal temperatures calculated by an iterative computation scheme shown in Figure 3.

With the appropriate thermal conductivity, the statistical steady-state heat transfer equation can be rewritten as

$$\kappa \nabla^2 T(\mathbf{r}, L, t_{ox}) = -p(\mathbf{r}, L, t_{ox}, T), \tag{6}$$

subject to the boundary condition

$$\kappa \frac{\partial T(\mathbf{r}_{b_s}, L, t_{ox})}{\partial \vec{n}_{b_s}} + h_{b_s} T(\mathbf{r}_{b_s}, L, t_{ox}) = f_{b_s}(\mathbf{r}_{b_s}), \tag{7}$$

where  $\kappa$  is the thermal conductivity of the die that is obtained by utilizing the procedure presented in Figure 3.

With Eqs. (6) and (7), the goals of this work are to estimate the mean profile, the standard deviation profile, and the thermal yield profile of on-chip temperature distribution.

### 3.2. Physical Parameter Modeling

Generally, variations of physical parameters can be classified into two categories, dieto-die (D2D) variations and within-die (WID) variations. Due to different stages of the fabrication process, D2D and WID variations can be treated as two independent variation sources. Since D2D variations are smooth within a die, it is reasonable to model all devices having the same D2D variation. On the other hand, WID variations present considerable gradients within a die, and they are spatially correlated because spatial imperfection of the chemical-mechanical polishing and lithography processes. As indicated by the measured results of Cline et al. [2006] and Cheng et al. [2011], distributions of the physical parameters are similar to those of the Gaussian random variables; generally, WID variations are assumed to be a correlated Gaussian random process, and D2D variations are treated as a Gaussian random variable for all devices [Bhardwaj et al. 2008; Chang and Sapatnekar 2007; Shen et al. 2010a, 2010b].

Combining the models of D2D and WID variations, the physical parameter  $Par(\mathbf{r}_{xy})$  with its nominal value  $\mu_{Par}(\mathbf{r}_{xy})$  at position  $\mathbf{r}_{xy} = (x, y) \in (0, L_x) \times (0, L_y)$  can be represented as

$$Par(\mathbf{r}_{xy}) = \mu_{Par}(\mathbf{r}_{xy}) + \delta_{WID}(\mathbf{r}_{xy}) + \delta_{D2D}, \tag{8}$$

where  $\delta_{WID}(\mathbf{r}_{xy})$  is a Gaussian random process of WID variations, and  $\delta_{D2D}$  is a Gaussian random variable of D2D variations.

Since the spatial correlation of  $\delta_{WID}(\mathbf{r}_{xy})$  has different decreasing rates in the x-direction and y-direction [Cline et al. 2006], the following spatial covariance function [Bhardwaj et al. 2008] is adopted for modeling the spatial correlation of  $\delta_{WID}(\mathbf{r}_{xy})$ .

$$C(\mathbf{r}_{x_1y_1}, \mathbf{r}_{x_2y_2}) = \sigma^2 \exp\left(-\frac{|x_1 - x_2|}{\lambda_x} - \frac{|y_1 - y_2|}{\lambda_y}\right),\tag{9}$$

where  $\mathbf{r}_{x_1y_1} = (x_1, y_1)$  and  $\mathbf{r}_{x_1y_2} = (x_2, y_2)$ ,  $\lambda_x$  and  $\lambda_y$  are correlation lengths of  $\delta_{WID}$  in the x- and y-directions, respectively, and  $\sigma$  is the standard deviation of  $\delta_{WID}(\mathbf{r}_{xy})$ .

In this work, the Karhunen-Loève (KL) expansion is utilized to simplify  $\delta_{WID}(\mathbf{r}_{xy})$ , since its number of transformed random variables is much smaller than that of principal component analysis (PCA) [Bhardwaj et al. 2008]. By applying the KL expansion,  $\delta_{WID}(\mathbf{r}_{xy})$  with the spatial covariance function shown in Eq. (9) can be approximated as

$$\delta_{WID}(\mathbf{r}_{xy}) \approx \sum_{l=1}^{N_{Par}} \sqrt{\chi_l} \vartheta_l(\mathbf{r}_{xy}) \zeta_l. \tag{10}$$

Here,  $N_{Par}$  is the truncation number, each  $(\chi_l, \vartheta_l(\mathbf{r}_{xy}))$  is an eigen-pair of  $C(\mathbf{r}_{x_1y_1}, \mathbf{r}_{x_2y_2})$ , and  $\zeta_l$ 's are independent standard normal random variables.

<sup>&</sup>lt;sup>5</sup>Although this specific spatial covariance function is adopted, the Karhunen-Loève expansion of a Gaussian random process with an arbitrary spatial covariance function can be efficiently obtained by a finite-element method [Schwab and Todor 2006]. Hence, more advanced spatial covariance functions [Gao et al. 2011; Liu 2007; Cheng et al. 2011] can also be incorporated into our framework.

The closed-form expressions of an eigen-pair  $(\chi_l, \vartheta_l(\mathbf{r}_{xy}))$  for  $C(\mathbf{r}_{x_1y_1}, \mathbf{r}_{x_2y_2})$  shown in Eq. (9) can be derived as follows [Zhang and Lu 2004].

$$\chi_{l} = \frac{4\sigma^{2}\lambda_{x}\lambda_{y}}{(\lambda_{x}^{2}\nu_{x,i}^{2} + 1)(\lambda_{y}^{2}\nu_{y,j}^{2} + 1)},$$

(11)

$$\vartheta_l(\mathbf{r}_{xy}) = \vartheta_{x,i}(x)\vartheta_{y,j}(y), \tag{12}$$

where l, i, and j are indices, and the mapping between (i, j) and l is one to one.  $\vartheta_{x,i}(x)$  and  $\vartheta_{y,j}(y)$  are equal to

$$\vartheta_{x,i}(x) = \frac{\lambda_x \nu_{x,i} \cos(\nu_{x,i} x) + \sin(\nu_{x,i} x)}{\sqrt{\left(\lambda_x^2 \nu_{x,i}^2 + 1\right) L_x / 2 + \lambda_x}},\tag{13}$$

$$\vartheta_{y,j}(y) = \frac{\lambda_y \nu_{y,j} \cos(\nu_{y,j} y) + \sin(\nu_{y,j} y)}{\sqrt{(\lambda_y^2 \nu_{y,j}^2 + 1) L_y / 2 + \lambda_y}}.$$

(14)

Here,  $v_{x,i}$  and  $v_{y,j}$  are positive values that satisfy

$$(\lambda^2 \nu^2 - 1)\sin(\nu \gamma) = 2\lambda \nu \cos(\nu \gamma),\tag{15}$$

with  $(\nu = \nu_{x,i}, \gamma = L_x, \lambda = \lambda_x)$  and  $(\nu = \nu_{y,j}, \gamma = L_y, \lambda = \lambda_y)$ , respectively.

To get reasonable truncation numbers of KL expansions for the physical parameters L and  $t_{ox}$ , in this work,  $N_{Par}$  for Par = L or  $Par = t_{ox}$  is decided by the following criterion.

$$\frac{\chi_{N_{Par}+1}}{\sum_{i=1}^{N_{Par}+1} \chi_i} \le \varepsilon, \tag{16}$$

with  $\varepsilon = 1\%$ .

Generally, devices located adjacently have similar physical characteristics [Chang and Sapatnekar 2007; Shen et al. 2010b, 2010a]. Therefore, the active layer is partitioned into several rectangular grids for modeling physical parameters. After that, with the KL expansion, the device channel length  $L_m$  and oxide thickness  $t_{ox_m}$  in the mth modeling grid can be approximated as

$$L_m = \mu_{L_m} + \boldsymbol{g}_{L_m}^T \boldsymbol{\eta}_L, \tag{17}$$

$$t_{ox}\underline{m} = \mu_{t_{ox}\underline{m}} + \boldsymbol{g}_{t_{ox}\underline{m}}^T \boldsymbol{\eta}_{t_{ox}}. \tag{18}$$

Here,  $\mu_{L_{\underline{m}}}$  and  $\mu_{t_{ox}\underline{m}}$  are nominal values of  $L_{\underline{m}}$  and  $t_{ox}\underline{m}$ , respectively.  $\mathbf{g}_{L_{\underline{m}}}$  and  $\mathbf{g}_{t_{ox}\underline{m}}$  are coefficient vectors for  $\mathbf{\eta}_L$  and  $\mathbf{\eta}_{t_{ox}}$ , respectively.  $\mathbf{\eta}_L = [\eta_{L_1}, \dots, \eta_{L_{N_L}}]^T$  and  $\mathbf{\eta}_{t_{ox}} = [\eta_{t_{ox}1}, \dots, \eta_{t_{ox}N_{tox}}]^T$  are standard normal random vectors constituted by the KL expanded WID and D2D random variables for representing the device channel length and the oxide thickness in all modeling grids, respectively.

In the rest of this article,  $\xi$  is employed to represent  $[\eta_{L_1}, \ldots, \eta_{L_{N_L}}, \eta_{t_{ox1}}, \ldots, \eta_{t_{oxN_{t_{ox}}}}]^T$  for the sake of notation simplicity.

### 4. STATISTICAL ELECTRO-THERMAL SIMULATOR

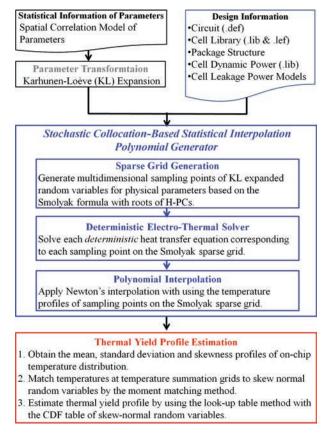

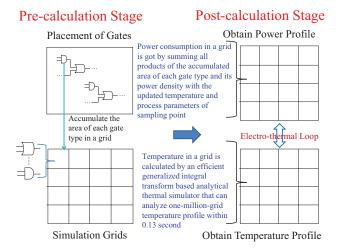

The executing flow of the proposed statistical electrothermal simulator is summarized in Figure 4. Given the information of physical parameters, the KL expansion is performed to transform the spatial correlated physical parameters into a set of uncorrelated random variables. Then, the statistical polynomial expression of the on-chip temperature distribution is generated by the developed stochastic collocation-based

Fig. 4. Flow of the developed statistical electrothermal simulator.

statistical interpolation polynomial generator. After that, the on-chip thermal yield profile is estimated by the developed thermal yield profile estimation engine.

The stochastic collocation-based statistical interpolation polynomial generator, the thermal yield profile estimation engine, and a mixed-mesh strategy for enhancing the statistical electrothermal simulator will be described in the following three sections.

### 4.1. Stochastic Collocation-Based Statistical Interpolation Polynomial Generator

The generator takes three steps to construct the statistical interpolation polynomial of the on-chip temperature distribution. First, the multidimensional sampling points of KL expanded random variables are generated by using the Smolyak sparse grid formula with sampling points being the roots of Hermite polynomials (HPs). Then, for each sampling point of the physical parameters, its corresponding temperature profile can be obtained by solving the corresponding deterministic heat transfer equation. Finally, the approximated expression of on-chip temperature distribution is built by utilizing Newton's interpolation polynomial formula. The details are presented in the rest of this section.

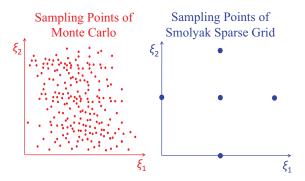

4.1.1. Smolyak Sparse Grid Generation. The primary advantage of Smolyak sparse grid formulation is to construct an interpolating polynomial for approximating a multivariate function  $u \in C^r$  by using much fewer samples of the desired function than those of the full tensor product interpolation formula and the MC method but still to

Fig. 5. The number of sampling random variables comparison between the Monte Carlo method and the Smolyak sparse grid formulation. Here, the samples of Smolyak sparse grid are adopted for achieving a level-two approximation.

maintain an acceptable error bound [Smolyak 1963; Barthelmann et al. 2000]. Here,  $C^r$  is the set of all functions that have continuous derivatives of all orders up to r. With this stochastic collocation technique, the statistical interpolation polynomial of on-chip temperature distribution can be efficiently constructed.

The MC method randomly generates samples of the random variables and hence requires a large number of samples for achieving an accurate estimate. In contrast, the Smolyak sparse grid technique uses the roots of HPs or the extrema of the Chebyshev polynomial [Barthelmann et al. 2000] to generate samples of the random variables and employs these fewer samples to effectively interpolate the desired solution. For example, Figure 5 illustrates that the number of possible sample points of the MC method is much larger than that of the Smolyak sparse grid formulation for a two-dimensional random variable.

According to the Smolyak sparse grid formulation [Smolyak 1963], on-chip temperature distribution can be explicitly approximated as follows [Barthelmann et al. 2000].

$$\widehat{T}_{q}^{N_{KL}}(\mathbf{r},\boldsymbol{\xi}) = \sum_{q=N_{KL}+1 \le |\mathbf{i}| \le q} (-1)^{q-|\mathbf{i}|} \binom{N_{KL}-1}{q-|\mathbf{i}|} (\mathcal{Q}^{i_1}(T) \otimes \cdots \otimes \mathcal{Q}^{i_n}(T) \otimes \cdots \otimes \mathcal{Q}^{i_{N_{KL}}}(T)).$$

(19)

Here,  $N_{KL} = N_{t_{ox}} + N_L$  is the number of random variables in  $\xi$ ,  $q = N_{KL} + l$ ,  $l \ge 1$  is the formulation level, and  $|\mathbf{i}| = \sum_{n=1}^{N_{KL}} i_n$ , with each  $i_n \ge 1$ .  $\mathcal{Q}^{i_n}(T)$  is an interpolating polynomial of  $T(\mathbf{r}, \xi)$  by only utilizing a single random variable  $\xi_n$ ,  $i_n$  is the index to decide the sample number  $(m_{i_n})$  for  $\mathcal{Q}^{i_n}(T)$ , and  $\otimes$  is the cross product operator for functions. As suggested by Barthelmann et al. [2000],  $m_{i_n=1}$  is set to 1, and  $m_{i_n}$  is equal to  $2^{i_n-1}+1$  for  $i_n>1$ . From Eq. (19), only the corresponding temperature values of a small set of samples for  $\xi$  need to be known [Barthelmann et al. 2000]. This set is called the sparse grid and can be represented as

$$\mathcal{H}(q, N_{KL}) = \bigcup_{q-N_{KL}+1 \le |\mathbf{i}| \le q} (\hbar^{i_1} \times \dots \times \hbar^{i_n} \times \dots \times \hbar^{i_{N_{KL}}}), \tag{20}$$

where  $\hbar^{i_n} = \{\xi_n^1, \dots, \xi_n^{m_{i_n}}\}$  is the set of sample points used by  $\mathcal{Q}^{i_n}(T)$ , and  $\times$  is the cross product operator for sets.

The number of sample points from the Smolyak sparse grid formulation is in the order of  $O(N_{KL}^l/l!)$ , and the runtime complexity for obtaining  $\widehat{T}_q^{N_{KL}}(\mathbf{r}, \boldsymbol{\xi})$  is in the order of  $t_{\text{det}} \cdot O(N_{KL}^l/l!)$ . Here,  $t_{\text{det}}$  is the runtime complexity for performing the deterministic

electrothermal simulation once. The Smolyak sparse grid formulation ensures a error bound,  $\frac{c_{N_{KL},r}\cdot(\log N_{\mathcal{H}})^{(r+1)(N_{KL}-1)}}{N_{\mathcal{H}}^r}$ , for the function having bounded derivatives up to order r [Barthelmann et al. 2000]. Here,  $N_{\mathcal{H}}$  is the number of sample points in  $\mathcal{H}(q,N_{KL})$ , and  $c_{N_{KL},r}$  is a constant that depends on  $N_{KL}$  and r. According to our experience, the accurate estimation of the thermal yield profile can be obtained by setting level l to be 1. The number of sample points for the Smolyak sparse grid formulation can be much less than that of the MC method. A simple example is presented in Appendix A to illustrate the Smolyak sparse grid formulation.

The sampling values of  $\hbar^{i_n}$  for each  $i_n$  must be properly decided. Adopting the roots of H-PCs with its order corresponding to each  $i_n$  can achieve the most accurate result, as  $\xi$  is a normal random vector [Phillips 2003]. Choosing the extrema of the Chebyshev polynomial with its order corresponding to  $i_n$  can achieve the nested sparse grid structure, that is,  $\hbar^{i_n=j} \subset \hbar^{i_n=k}$  as j < k, and the acceptable accuracy [Barthelmann et al. 2000]. In this work, we select the roots of H-PCs as the sampling values, since the result is shown to be very accurate by using the low-level approximation, and the nested sparse grid structure is still preserved for  $q = N_{KL} + 1.6$

4.1.2. Deterministic Electrothermal Solver: Temperature Profile Calculation for a Given Sample Point. After constructing the sparse grid  $\mathcal{H}(q, N_{KL})$  of  $\xi$ , the samples of channel length and oxide thickness in the mth modeling grid corresponding to the jth sampling vector  $\xi^j$  in  $\mathcal{H}(q, N_{KL})$  can be calculated by Eqs. (17) and (18), respectively, and the deterministic power density profile corresponding to  $\xi^j$  can also be obtained. Hence, we have the deterministic steady-state heat transfer equation as

$$\kappa \nabla^2 T(\mathbf{r}, \boldsymbol{\xi}^j) = -p(\mathbf{r}, \boldsymbol{\xi}^j, T), \tag{21}$$

subject to the boundary condition

$$\kappa \frac{\partial T(\mathbf{r}_{b_s}, \boldsymbol{\xi}^j)}{\partial \vec{n}_{b_s}} + h_{b_s} T(\mathbf{r}_{b_s}, \boldsymbol{\xi}^j) = f_{b_s}(\mathbf{r}_{b_s}). \tag{22}$$

Here,  $T(\mathbf{r}, \boldsymbol{\xi}^j)$  and  $p(\mathbf{r}, \boldsymbol{\xi}^j, T)$  are the deterministic temperature and power density profiles with the sampling point  $\boldsymbol{\xi}^j$ , respectively. Since the power density profile in Eq. (21) is temperature dependent, a deterministic electrothermal solver is summarized in Figure 6 and built to obtain each  $T(\mathbf{r}, \boldsymbol{\xi}^j)$ .

The implementation of the developed deterministic electrothermal solver is illustrated in Figure 7. The accumulated area of each gate type in each simulating temperature grid can be precalculated and stored in the precalculation stage. With this precalculated data, the deterministic power density profile for each sampling point in  $\mathcal{H}(q,N_{KL})$  can be obtained and updated in the order of  $O(N_xN_yN_{type})$  during the electrothermal simulation loop. Here,  $N_x$  and  $N_y$  are the division numbers of the simulation grid along x- and y-directions, respectively, and  $N_{type}$  is the number of gate types for the given design. Generally,  $N_{type}$  is determined by the specific cell library, and it is far less than the number of simulation grids,  $N_xN_y$ . After obtaining or updating the deterministic power density profile, an efficient deterministic thermal simulator [Huang and Lee 2009] is adopted to solve the deterministic heat transfer equation. These updating and solving procedures are repeated until the result is converged.

<sup>&</sup>lt;sup>6</sup>If high-order approximation is needed for the accuracy, we suggest using the extrema of the Chebyshev polynomial because the nested sparse grid structure is always preserved. Hence, the number of sample points can be smaller.

```

Algorithm: Temperature Profile Calculation for a Sample Point

Input: A sampling point \xi^j, initial temperature T_{\xi^j}^{ini} and p_d(\mathbf{r})

Output: Temperature profile T(\mathbf{r}, \boldsymbol{\xi}^j)

1 Begin

2 T(\mathbf{r}, \boldsymbol{\xi}^j) \leftarrow T_{\boldsymbol{\xi}^j}^{ini};

Obtain t_{oxm}(\xi^j) and L_m(\xi^j) for each mth modeling grid according to \xi^j;

While (MaxError > \epsilon)

6

T_{pre}(\mathbf{r}, \boldsymbol{\xi}^j) \leftarrow T(\mathbf{r}, \boldsymbol{\xi}^j);

Update p_{leak}(\mathbf{r}, \boldsymbol{\xi}^j, T_{pre}) by T_{pre}(\mathbf{r}, \boldsymbol{\xi}^j);

7

p(\mathbf{r}, \boldsymbol{\xi}^j, T_{pre}) \leftarrow p_{leak}(\mathbf{r}, \boldsymbol{\xi}^j, T_{pre}) + p_d(\mathbf{r});

†Solve (21) and (22) with p(\mathbf{r}, \boldsymbol{\xi}^j, T_{pre}) to obtain a new T(\mathbf{r}, \boldsymbol{\xi}^j);

if (T(\mathbf{r}, \boldsymbol{\xi}^j) = \infty) then Thermal runaway;

10

MaxError \leftarrow \max_{\mathbf{r}} \left| T(\mathbf{r}, \boldsymbol{\xi}^j) - T_{pre}(\mathbf{r}, \boldsymbol{\xi}^j) \right|;

12 EndWhile

13 End

```

†Any deterministic thermal simulators can be used to execute *Line* 9. Here, the simulator developed in [Huang and Lee 2009] is adopted.

Fig. 6. Deterministic electrothermal solver for each sampling point  $(\xi^j)$  in the sparse grid.  $p_{leak}$ ,  $p_d$ , and p are the leakage, dynamic, and total power density profiles for each sampling point, respectively.

Fig. 7. Implementation of solving the deterministic heat transfer equation.

4.1.3. Temperature Profile Construction by Using Polynomial Interpolation. With each obtained  $T(\mathbf{r}, \boldsymbol{\xi}^j)$ , the polynomial interpolation technique can be applied to construct the interpolating polynomial for the statistical temperature. As suggested by Barthelmann et al. [2000], the Lagrange polynomial can be applied to construct the interpolating polynomial  $\mathcal{Q}^{i_1}(T) \otimes \cdots \otimes \mathcal{Q}^{i_{NKL}}(T)$  for each different  $|\mathbf{i}|$ . However, the suggested interpolation method requires performing the cross-product operation of functions; this can be slightly complicated for the implementation. Therefore, we adopt Newton's interpolating method to globally interpolate  $T(\mathbf{r}, \boldsymbol{\xi})$ , because it can be implemented more easily and can interpolate the same polynomial as Barthelmann's method [Phillips 2003]. Therefore, the Smolyak's error bound can still be preserved.

**Algorithm:** Stochastic Collocation-Based Statistical Interpolation Polynomial Generation **Input:** Design information such as .def, .lef, and .lib files;

Geometry of the die and Package structure;

Leakage power models;

Spatial correlation models of the device channel length and oxide thickness.

**Output:** The statistical interpolation polynomial,  $\widehat{T}(\mathbf{r}, \boldsymbol{\xi})$ , of the on-chip temperature distribution.

# 1 Begin 2 Set thermal parameters and the initial average mean temperature, μ<sub>T</sub><sup>ini</sup>, of the die by 1-D thermal model; 3 For m ← 1 to N<sub>g</sub> 4 Obtain g<sub>L<sub>m</sub></sub> of L<sub>m</sub> and g<sub>toxm</sub> of t<sub>oxm</sub> by the KL expansion; 5 EndFor 6 Generate ℋ(q, N<sub>KL</sub>) for the KL expanded random variables. 7 For n ← 0 to N<sub>H</sub> − 1 8 Obtain T(r, ξ<sup>n</sup>) by using the algorithm presented in Fig. 6. 9 EndFor 10 Solve (25) to obtain Newton's interpolation formula in (23). 11 End

Fig. 8. Stochastic collocation-based statistical interpolation polynomial generation algorithm.

With Newton's interpolation formula, the on-chip temperature at an arbitrary position  $\mathbf{r}^*$  of the die can be approximated as

$$\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) = \sum_{j=0}^{N_{\mathcal{H}}-1} \widehat{u}_j(\mathbf{r}^*) \phi_j(\boldsymbol{\xi}). \tag{23}$$

Here, each  $\phi_j(\xi)$  is a fundamental polynomial with respect to the jth sampling vector  $\xi^j$ , and the form of each  $\phi_j(\xi)$  can be found in Phillips [2003].  $N_{\mathcal{H}}$  is the number of sampling vectors in the sparse grid  $\mathcal{H}(q,N_{KL})$ . Each  $\hat{u}_j(\mathbf{r}^*)$  is an unknown coefficient that needs to be determined.

Based on the basic idea of interpolation that the approximated function must match each known data, the interpolated polynomial in Eq. (23) satisfies the following equation for each  $\xi^n$ .

$$\sum_{j=0}^{N_{\mathcal{H}}-1} \hat{u}_j(\mathbf{r}^*) \phi_j(\boldsymbol{\xi}^n) = T(\mathbf{r}^*, \boldsymbol{\xi}^n). \tag{24}$$

With the property of fundamental polynomial described in [Phillips 2003], Eq. (24) can be rewritten as the matrix form for finding each  $\hat{u}_j(\mathbf{r}^*)$  at position  $\mathbf{r}^*$ .

$$\begin{bmatrix} \phi_{0}(\boldsymbol{\xi}^{0}) & 0 & \cdots & 0 \\ \phi_{0}(\boldsymbol{\xi}^{1}) & \phi_{1}(\boldsymbol{\xi}^{1}) & \cdots & 0 \\ \vdots & \vdots & \ddots & \vdots \\ \phi_{0}(\boldsymbol{\xi}^{N_{\mathcal{H}}-1}) & \phi_{1}(\boldsymbol{\xi}^{N_{\mathcal{H}}-1}) & \cdots & \phi_{N_{\mathcal{H}}-1}(\boldsymbol{\xi}^{N_{\mathcal{H}}-1}) \end{bmatrix} \begin{bmatrix} \hat{u}_{0}(\mathbf{r}^{*}) \\ \hat{u}_{1}(\mathbf{r}^{*}) \\ \vdots \\ \hat{u}_{N_{\mathcal{H}}-1}(\mathbf{r}^{*}) \end{bmatrix} = \begin{bmatrix} T(\mathbf{r}^{*}, \boldsymbol{\xi}^{0}) \\ T(\mathbf{r}^{*}, \boldsymbol{\xi}^{1}) \\ \vdots \\ T(\mathbf{r}^{*}, \boldsymbol{\xi}^{N_{\mathcal{H}}-1}) \end{bmatrix}$$

(25)

Each  $\hat{u}_i(\mathbf{r}^*)$  can be calculated by using the forward substitution.

The algorithm for generating the statistical interpolation polynomial of on-chip temperature distribution is shown in Figure 8.

### 4.2. Thermal Yield Profile Estimation Engine

With the generated statistical interpolation polynomial of on-chip temperature distribution, the mean, standard deviation, and skewness profiles of on-chip temperature

distribution are computed. After that, the temperature at each arbitrary position is approximated to be a corresponding skew normal random variable by the moment matching technique. Finally, the on-chip thermal yield profile is estimated by looking up the cumulative distribution function (CDF) table of those corresponding skew normal random variables. The detailed description of this thermal yield profile estimation engine is shown next.

As mentioned in Section 2.1, the on-chip thermal yield profile at an arbitrary position  $\mathbf{r}^*$  of the die can be defined as

$$Tyield(\mathbf{r}^*, T_{\text{spec}}(\mathbf{r}^*)) \stackrel{\text{def}}{=} \mathbf{Prob}(T(\mathbf{r}^*, \boldsymbol{\xi}) \le T_{\text{spec}}(\mathbf{r}^*)).$$

(26)

With the definition given in Eq. (26), our target is to approximate the CDF of  $T(\mathbf{r}^*, \boldsymbol{\xi})$ . To obtain the approximated expression of  $T(\mathbf{r}^*, \boldsymbol{\xi})$ , the formulation level l is set as 1 for generating the sparse grid  $\mathcal{H}(q, N_{KL})$  with  $q = N_{KL} + l$  in Eq. (20). Then, applying Newton's interpolating method, the approximated expression of  $T(\mathbf{r}^*, \boldsymbol{\xi})$ , shown in Eq. (23), can be rewritten as<sup>7</sup>

$$\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) = \sum_{k=1}^{N_{KL}} \left( \hat{a}_k(\mathbf{r}^*) \xi_k^2 + \hat{b}_k(\mathbf{r}^*) \xi_k \right) + \hat{c}(\mathbf{r}^*), \tag{27}$$

where  $\hat{a}_k(\mathbf{r}^*)$ ,  $\hat{b}_k(\mathbf{r}^*)$ , and  $\hat{c}(\mathbf{r}^*)$  are the coefficients and can be obtained by performing the algorithm shown in Figure 8.

After several manipulations, Eq. (27) can be rewritten as

$$\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) = \sum_{k=1}^{N_{KL}} \widehat{a}_k(\mathbf{r}^*) \chi_k(\mathbf{r}^*, \boldsymbol{\xi}_k) + \widetilde{c}(\mathbf{r}^*).$$

(28)

Here, each  $\chi_k(\mathbf{r}^*, \xi_k) = (\xi_k + \frac{\hat{b}_k(\mathbf{r}^*)}{2\hat{a}_k(\mathbf{r}^*)})^2$  is a non-central chi-square random variable, because  $\xi_k$  is a normal random variable,  $\tilde{c}(\mathbf{r}^*) = \hat{c}(\mathbf{r}^*) - \sum_{k=1}^{N_{KL}} \frac{\hat{b}_k^2(\mathbf{r}^*)}{4\hat{a}_k(\mathbf{r}^*)}$  is a constant, and  $\chi_k(\mathbf{r}^*, \xi_k)$ 's are independent because  $\xi_k$ 's are independent. Therefore,  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  is a weighted sum of independent non-central chi-square random variables.

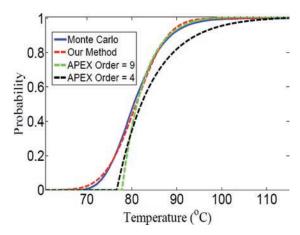

The estimation of Eq. (26) can be done by calculating the CDF of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  represented in Eq. (28). Since  $\boldsymbol{\xi}$  is an independent normal random vector, theoretically, the PDF of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  could be obtained by convolving the PDFs of  $\chi_k(\mathbf{r}^*, \boldsymbol{\xi}_k)$ 's. However, it is not practical because of numerous numerical convolutions. The moment matching-based CDF estimation techniques are another choice for efficiently approximating the CDF of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ . APEX [Li et al. 2004], a state-of-the-art method, approximates the CDF of a random variable with the similar form of Eq. (27) by linearly combining exponential waveforms and can achieve an arbitrarily required matching order of statistical moments. Padé approximation is essential during performing APEX, although it cannot guarantee being stable for obtaining poles/zeros, even in the low-order approximation. To remedy this unstable issue, the technique proposed by Tutuianu et al. [1996] can be adopted to obtain the first two dominated pole/zero pairs for APEX. However, the first two dominated pole/zero pairs only can construct an approximated CDF of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  that

<sup>&</sup>lt;sup>7</sup>To get a more accurate approximated expression of  $T(\mathbf{r}^*, \boldsymbol{\xi})$ , one can set the formulation level l as 2 to capture the cross-product terms of  $\xi_k$ 's in the second-order polynomial approximation. As shown in Appendix C, with cross-product terms of  $\xi_k$ 's, the second-order polynomial approximated expression of  $T(\mathbf{r}^*, \boldsymbol{\xi})$  can be transformed to the form that is consistent with Eq. (27). Therefore, the proposed thermal yield profile estimation engine can be extended to the second-order polynomial approximation that has cross-product terms of  $\xi_k$ 's.

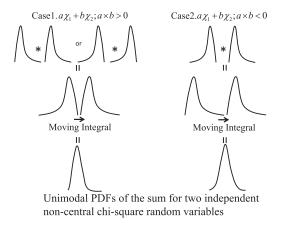

Fig. 9. Sketch of PDF for the weighted sum of two independent non-central chi-square random variables. Case 1: the convolution result of two right-skewed distributions or two left-skewed distributions. Case 2: the convolution result of one left-skewed distribution and one right-skewed distribution.

matches up to the first two statistical moments. Refer to Li et al. [2004] and Tutuianu et al. [1996] for the details of APEX and the stable two-pole technique, respectively.

Here, we are going to develop a moment matching-based technique to match the statistical moments of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  up to the third order for approximating the CDF of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ . The basic idea of this approach is to approximate a random variable with a unimodal and skewed PDF by matching its mean, variance, and skewness to be a skewnormal random variable. To explain the unimodal PDF property of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ , the sketches of PDFs corresponding to two different cases for the weighted sum of two independent non-central chi-square random variables are shown in Figure 9. Case 1 shows the convolution result of two right-skewed distributions or two left-skewed distributions, and Case 2 presents the convolution result of one left-skewed distribution and one right-skewed distribution. Although, depending on the leading coefficients, the skewness of resulting random variables might increase or decrease, both resulting random variables have unimodal PDFs. Since  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  is the weighted sum of independent non-central chi-square random variables, its PDF can be obtained by performing the convolution of two random variables successively. Therefore, it still has a unimodal PDF.

As indicated in Azzalini [2005], the skew-normal random variable is suitable for approximating the random variable with unimodal and skewed PDF. Hence, the skew-normal random variable can be a suitable model for approximating  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ .

From the representation of Eq. (28), the thermal yield at an arbitrary location  $\mathbf{r}^*$  can be approximated as

$$Tyield(\mathbf{r}^*, T_{\text{spec}}(\mathbf{r}^*)) \approx \mathbf{Prob}(\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) \leq T_{\text{spec}}(\mathbf{r}^*))$$

$$= \mathbf{Prob}(\Delta \widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) \leq \rho_{\widehat{T}}(\mathbf{r}^*)), \tag{29}$$

where  $\rho_{\widehat{T}}(\mathbf{r}^*) = \frac{T_{\mathrm{spec}}(\mathbf{r}^*) - \mu_{\widehat{T}}(\mathbf{r}^*)}{\sigma_{\widehat{T}}(\mathbf{r}^*)}$ , and  $\Delta \widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) = \frac{\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) - \mu_{\widehat{T}}(\mathbf{r}^*)}{\sigma_{\widehat{T}}(\mathbf{r}^*)}$ .  $\mu_{\widehat{T}}(\mathbf{r}^*)$  and  $\sigma_{\widehat{T}}(\mathbf{r}^*)$  are the mean and the standard deviation of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ , respectively; they can be computed in the order of  $O(N_{KL})$ , since  $\chi_k(\mathbf{r}^*, \boldsymbol{\xi}_k)$ 's are independent.

To approximate  $\Delta \widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  to be a skew-normal random variable,  $Z \sim SN(\upsilon_{\mathbf{r}^*}, \omega_{\mathbf{r}^*}, \alpha_{\mathbf{r}^*})$ , the parameters  $\upsilon_{\mathbf{r}^*}$ ,  $\omega_{\mathbf{r}^*}$ , and  $\alpha_{\mathbf{r}^*}$  [Azzalini 2005] need to be calculated. The first three

moments of Z can be formulated as follows with these parameters.

$$\mathbf{E}\{Z\} = \upsilon_{\mathbf{r}^*} + \omega_{\mathbf{r}^*} \delta_{\mathbf{r}^*}, \tag{30}$$

$$Var\{Z\} = \omega_{\mathbf{r}^*}^2 (1 - \delta_{\mathbf{r}^*}^2), \tag{31}$$

Skew{Z} =

$$\frac{4-\pi}{2} \frac{\delta_{\mathbf{r}^*}^3}{\sqrt{\left(1-\delta_{\mathbf{r}^*}^2\right)^3}}$$

, (32)

where

$$\delta_{\mathbf{r}^*} = \sqrt{\frac{2}{\pi}} \frac{\alpha_{\mathbf{r}^*}}{\sqrt{1 + \alpha_{\mathbf{r}^*}^2}}.$$

(33)

After matching the first three moments of  $\Delta \widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  with Eqs. (30)–(32), we have

$$\nu_{\mathbf{r}^*} = -\omega_{\mathbf{r}^*} \delta_{\mathbf{r}^*}, \tag{34}$$

$$\omega_{\mathbf{r}^*} = \sqrt{\frac{1}{1 - \delta_{\mathbf{r}^*}^2}},\tag{35}$$

$$\alpha_{\mathbf{r}^*} = \sqrt{\frac{\pi}{2}} \frac{\delta_{\mathbf{r}^*}}{\sqrt{1 - \frac{\pi}{2}\delta_{\mathbf{r}^*}^2}},$$

(36)

where

$$\delta_{\mathbf{r}^*} = \sqrt{\frac{\gamma_{\Delta \widehat{T}}^{\frac{3}{3}}(\mathbf{r}^*)}{\left(\frac{4-\pi}{2}\right)^{\frac{2}{3}} + \gamma_{\Delta \widehat{T}}^{\frac{3}{3}}(\mathbf{r}^*)}}.$$

(37)

Here,  $\gamma_{\Delta \widehat{T}}(\mathbf{r}^*)$  is the skewness of  $\Delta \widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ , and the sign of  $\delta_{\mathbf{r}^*}$  is the same as the sign of  $\gamma_{\Lambda \widehat{T}}(\mathbf{r}^*)$ .

To obtain  $\gamma_{\Delta \widehat{T}}(\mathbf{r}^*)$ ,  $\mathbb{E}\{\Delta \widehat{T}^3(\mathbf{r}^*, \boldsymbol{\xi})\}$  is needed and can be calculated as

$$\mathbb{E}\{\Delta\widehat{T}^{3}(\mathbf{r}^{*},\boldsymbol{\xi})\} = \frac{\mathbb{E}\{\widehat{T}^{3}(\mathbf{r}^{*},\boldsymbol{\xi})\} - 3\sigma_{\widehat{T}}^{2}(\mathbf{r}^{*})\mu_{\widehat{T}}(\mathbf{r}^{*}) - \mu_{\widehat{T}}^{3}(\mathbf{r}^{*})}{\sigma_{\widehat{T}}^{3}(\mathbf{r}^{*})},$$

(38)

where  $\mu_{\widehat{T}}(\mathbf{r}^*)$  and  $\sigma_{\widehat{T}}(\mathbf{r}^*)$  are the mean and standard deviation of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$ , respectively. As shown in Eq. (38), E $\{\widehat{T}^3(\mathbf{r}^*, \boldsymbol{\xi})\}$  is needed. However, the computational complexity of obtaining its value is  $O(N_{KL}^3)$  if the expression of  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  shown in Eq. (28) is directly used. To reduce the complexity,  $\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi})$  can be rewritten as

$$\widehat{T}(\mathbf{r}^*, \boldsymbol{\xi}) = \sum_{k=1}^{N_{KL}} \hat{a}_k(\mathbf{r}^*) \hat{\chi}_k(\mathbf{r}^*, \boldsymbol{\xi}_k) + \widehat{d}(\mathbf{r}^*), \tag{39}$$

<sup>&</sup>lt;sup>8</sup>Theoretically, the skew-normal random variable has an upper-bound skewness that can be achieved. In Appendix B, we examine the preceding stability issue, and address a method that can stably achieve the more higher-order approximation if more accurate approximation is required.

where  $\hat{\chi}_k(\mathbf{r}^*, \xi_k) = \chi_k(\mathbf{r}^*, \xi_k) - \mu_{\chi_k}(\mathbf{r}^*)$ ,  $\hat{d}(\mathbf{r}^*) = \tilde{c}(\mathbf{r}^*) - \sum_{k=1}^{N_{KL}} \hat{a}_k(\mathbf{r}^*) \mu_{\chi_k}(\mathbf{r}^*)$ , and  $\mu_{\chi_k}(\mathbf{r}^*) = \mathbb{E}\{\chi_k(\mathbf{r}^*, \xi_k)\}$ . Since  $\hat{\chi}_k(\mathbf{r}^*, \xi_k)$ 's have zero mean and are independent, we have

$$\mathbf{E}\left\{\left(\sum_{k=1}^{N_{KL}}\hat{a}_{k}(\mathbf{r}^{*})\hat{\chi}_{k}(\mathbf{r}^{*},\xi_{k})\right)^{i}\right\} = \sum_{k=1}^{N_{KL}}\hat{a}_{k}^{i}(\mathbf{r}^{*})\mathbf{E}\left\{\hat{\chi}_{k}^{i}(\mathbf{r}^{*},\xi_{k})\right\},\tag{40}$$

for i = 1, 2, and 3.

Therefore,  $\mathbb{E}\{\widehat{T}^3(\mathbf{r}^*, \boldsymbol{\xi})\}$  can be obtained in the order of  $O(N_{KL})$ , and the computational complexity of evaluating  $\mathbb{E}\{\Delta\widehat{T}^3(\mathbf{r}^*, \boldsymbol{\xi})\}$  is also  $O(N_{KL})$ .

With  $\upsilon_{\mathbf{r}^*}$ ,  $\omega_{\mathbf{r}^*}$ , and  $\alpha_{\mathbf{r}^*}$ ,  $Tyield(\mathbf{r}^*, T_{\mathrm{spec}}(\mathbf{r}^*))$  can be estimated by the CDF of the matched skew-normal random variable. Finally, we have

$$Tyield(\mathbf{r}^*, T_{\text{spec}}(\mathbf{r}^*)) \approx \Phi(\beta_{\mathbf{r}^*}) - 2T_{Owen}(\beta_{\mathbf{r}^*}, \alpha_{\mathbf{r}^*}). \tag{41}$$

Here,  $\Phi(\cdot)$  is the CDF of the standard normal random variable,  $T_{Owen}(\cdot)$  is Owen's T function [Azzalini 2005], and  $\beta_{\mathbf{r}^*} = \frac{\rho_{\widehat{T}}(\mathbf{r}^*) - \nu_{\mathbf{r}^*}}{\rho_{\mathbf{r}^*}}$ .

With Eqs. (34)–(36) and Eq. (41),  $Tyield(\mathbf{r}^*, T_{\mathrm{spec}}(\mathbf{r}^*))$  can be efficiently evaluated by the lookup table method.

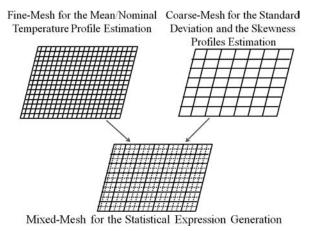

### 4.3. Mixed-Mesh Strategy for Enhancing the Statistical Electrothermal Simulator

As stated in Section 4.1.3, the deterministic electrothermal solver presented in Figure 6 needs to be executed  $N_{\mathcal{H}}$  times to generate the statistical interpolation polynomial of on-chip temperature distribution shown in Eq. (23) with the level-1 Smolyak sparse grid formula. Hence, although the developed thermal yield profile estimation engine can be done efficiently, the total runtime for obtaining the thermal yield profile is still dominated by the statistical interpolation polynomial generation. Here, we will present a mixed-mesh strategy to speed up the statistical interpolation polynomial generator without sacrificing the accuracy of the estimated thermal yield profile.

The developed mixed-mesh strategy is inspired by the following observations. The statistical interpolation polynomial generator needs to perform the deterministic electrothermal solver once for calculating the temperature profile with nominal device parameters and execute the deterministic electrothermal solver  $N_{\mathcal{H}}$ -1 times for obtaining temperature variations corresponding to the nominal temperature profile. The temperature profile from the first part contributes the major portion of the mean profile of temperature distribution, and the temperature variations from the second part contribute a large portion of the variance and skewness profiles of temperature distribution. In practice, the magnitude of the mean temperature profile is larger than those of the variance and skewness profiles of temperature distribution, since process variations of parameters are usually within a controllable range.

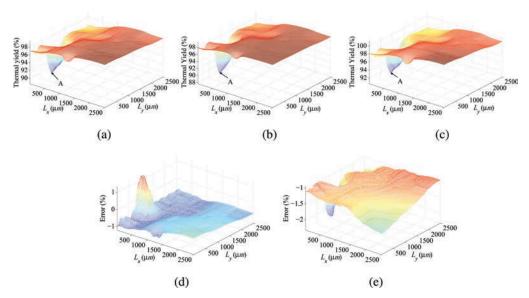

Based on the preceding observations, the mixed-mesh strategy for generating the statistical interpolation polynomial of on-chip temperature distribution is illustrated in Figure 10. Since the mean profile contributes a major portion to the thermal yield profile, the nominal temperature profile is built by the deterministic electrothermal solver with a fine mesh having  $N_{\rm F}N_{\rm F}$  grids to preserve the estimation accuracy of the mean temperature profile. Then, the difference between the maximum and minimum temperature values,  $\Delta \overline{T}_{\rm max}$ , of the nominal temperature profile is calculated, and an allowable temperature resolution,  $T_{\rm res}$ , is chosen. After that, the remaining  $N_{\rm H}-1$  deterministic electrothermal simulations are executed with a coarse mesh having  $N_{\rm C}N_{\rm C}$  grids. Here,  $N_{\rm C}$  is equal to  $\lceil \Delta \overline{T}_{\rm max}/T_{\rm res} \rceil$ . Finally, the mean, variance, and skewness profiles of on-chip temperature distribution can be approximated by the generated

statistical interpolation polynomial, and these temperature profiles are utilized to calculate the thermal yield profile.

With the proposed mixed-mesh strategy, the runtime for generating the statistical interpolation polynomial of on-chip temperature distribution can be significantly reduced. In this work, an effective deterministic thermal simulator [Huang and Lee 2009] is adopted as the kernel of our developed deterministic electrothermal solver. The computational complexity of the deterministic thermal simulator presented in Huang and Lee [2009] is  $O(N_{\rm M}N_{\rm M}\log N_{\rm Base})$ . Here,  $N_{\rm M}N_{\rm M}$  is the mesh size, and  $N_{\rm Base}$  is the number of bases for expressing the deterministic temperature profile. Generally, by using the average chip temperature calculated by the iterative computation scheme of the 1D thermal model shown in Figure 3 to be the initial operating temperature, the number of electrothermal loops for achieving convergence can be less than a small value. Hence, the computational complexity of the developed deterministic electrothermal solver is also  $O(N_{\rm M}N_{\rm M}\log N_{\rm Base})$ .

Therefore, the computational complexity of our baseline algorithm (the fine mesh is used for each deterministic electrothermal simulation) stated in Figure 4 is  $O(N_{\mathcal{H}}N_{\mathrm{F}}N_{\mathrm{F}}\log N_{\mathrm{Base}})$ , and the computational complexity by utilizing the developed mixed-mesh strategy can be reduced to  $O((N_{\mathrm{F}}N_{\mathrm{F}}+(N_{\mathcal{H}}-1)N_{\mathrm{C}}N_{\mathrm{C}})\log N_{\mathrm{Base}})$ .

The computational complexity ratio of the developed mixed-mesh strategy for generating the statistical interpolation polynomial to the deterministic electrothermal solver with nominal device parameters is equal to  $1+(N_{\mathcal{H}}-1)\times(N_{\mathcal{C}}/N_{\mathcal{F}})^2$ . In our experimental results, an accurate thermal yield profile can be estimated with  $N_{\mathcal{H}}=53$ ,  $N_{\mathcal{F}}=128$ ,  $N_{\mathcal{C}}=16$ , and  $T_{\rm res}=0.65^{\circ}{\rm C}$ . The computational complexity ratio is 1.8125. Therefore, the mixed-mesh strategy does enhance the efficiency of the developed statistical electrothermal simulator for catching up with that of a deterministic electro-thermal simulator.

### 5. EXPERIMENTAL RESULTS

The developed statistical electrothermal simulator is implemented in C++ language and tested on a Linux system with Intel Xeon 3.0-GHz CPU and 32GB memory. The die size is  $2.5~\text{mm} \times 2.5~\text{mm} \times 0.5~\text{mm}$ . The junction depth is set to 20nm for the 65nm

$<sup>^9</sup>$ As reported in Huang and Lee [2009], it took only 0.13 seconds to obtain the temperature profile of a chip with one million functional blocks and  $1024 \times 1024$  simulation mesh.

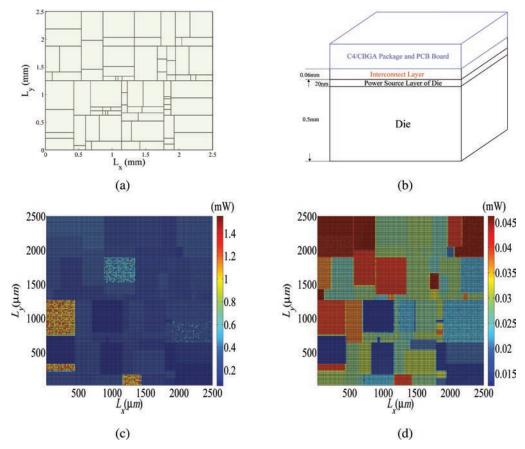

Fig. 11. Power map of the test chip: (a) floorplan, (b) geometries of the die and package, (c) the mean profile of the power map, (d) the standard deviation profile of the power map. Here,  $L_x$  and  $L_y$  are the width and length of the test die, respectively.

technology [Lallement et al. 2004], and the Debye length is 2nm [Bienacel et al. 2004]. The floorplan of a test chip having 1.2 million functional gates is shown in Figure 11(a), and the geometries of chip and package are shown in Figure 11(b).

By applying the modeling skill of thermal parameters mentioned in Figure 3 of Section 3.1 and the modeling skill for both heat transfer paths mentioned in Huang et al. [2006], the thermal conductivity and the equivalent heat transfer coefficients of the primary and secondary heat flow paths for executing the deterministic thermal simulator [Huang and Lee 2009] are summarized in Table III. The boundary condition of each vertical surface is set to be isothermal [Huang and Lee 2009].

The device parameters, the truncation points of KL expansions for the channel length  $(N_L)$  and the oxide thickness  $(N_{t_{ox}})$ , and the number of device modeling grid  $(N_{\text{KL}_g})$  are summarized in Table IV. Both  $N_L$  and  $N_{t_{ox}}$  are decided by using the criterion stated in Eq. (16) with  $\varepsilon=1\%$ . To model the spatial correlation, both  $\eta_x/L_x$  and  $\eta_y/L_y$  are set to 0.98 for the correlation function shown in Eq. (9) [Cline et al. 2006]. The active layer of the test chip is divided into  $128\times128$  simulated grids.

The estimated mean and standard deviation profiles of the power map under the settings of 60% WID and 40% D2D variations to the total variations are shown in Figures 11(c)–(d), respectively.

| Parameter   | Value                         |

|-------------|-------------------------------|

| κ           | 104.6 W/(m.°C)                |

| $h_p$       | 12,000 W/(m <sup>2</sup> .°C) |

| $\dot{h_s}$ | 2,017 W/(m <sup>2</sup> ·°C)  |

Table III. Equivalent Thermal Parameters

$h_p$ : the equivalent primary heat transfer coefficient.

$h_s$ : the equivalent secondary heat transfer coefficient.

Table IV. Parameters and Truncation Points for the Channel Length and Oxide Thickness

| Nominal L Nominal tox |            | $3\sigma_L$ | $3\sigma_{t_{ox}}$ | $N_L$ | $N_{t_{ox}}$ | $N_{\mathrm{KL}_g}$ |

|-----------------------|------------|-------------|--------------------|-------|--------------|---------------------|

| 65nm                  | 65nm 1.5nm |             | 5%                 | 13    | 13           | 49                  |

### 5.1. Electrothermal vs. Nonelectrothermal Simulations

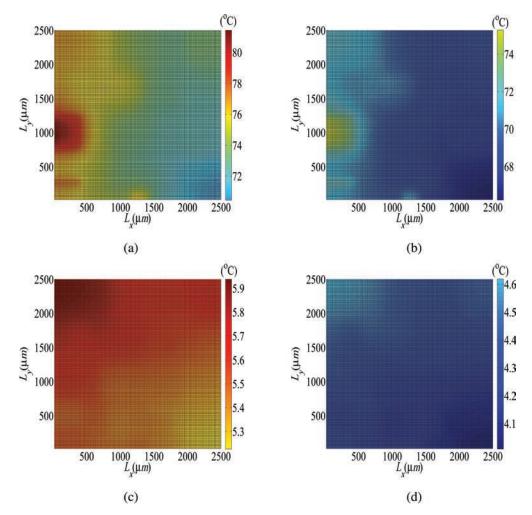

With the number of grids being 100 for modeling device parameters and the ratios of WID and D2D variations to the total variations being 60% and 40%, respectively, the MC method with  $2 \times 10^4$  samples is employed to demonstrate essentialness of the electrothermal simulation loop. The estimated mean and standard deviation profiles of the on-chip temperature distribution with and without considering the temperature-dependent issue of leakage power are shown in Figures 12(a) and 12(c), and Figures 12(b) and 12(d), respectively. For the mean profile estimation, the difference between Figure 12(a) and Figure 12(b) is over 16%. For the standard deviation profile estimation, the difference between Figure 12(c) and Figure 12(d) is over 31%. These results indicate that statistical electrothermal analysis is essential.

### 5.2. Accuracy and Efficiency

This section is going to demonstrate the correctness and efficiency of the developed statistical electrothermal simulator and show its efficiency improvement by using the mixed-mesh strategy.

Given three different ratio pairs of the WID and D2D variations to the total variations, (WID, D2D) = (40%, 60%), (50%, 50%), or (60%, 40%), the results from  $2 \times 10^4$  MC simulations, which satisfy the maximum absolute relative error of variance is less than 1%, are utilized as the reference solution.

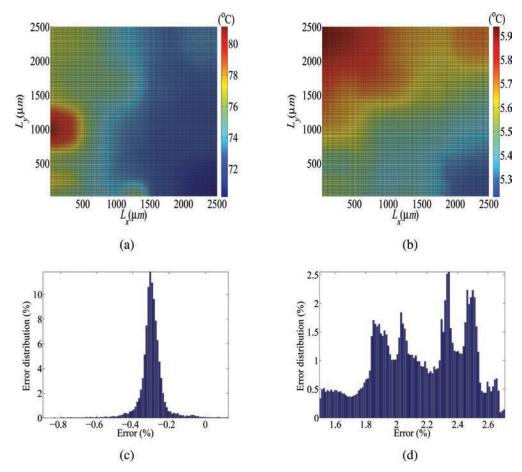

5.2.1. Mean and Standard Deviation Estimation. To demonstrate the accuracy and efficiency of the developed statistical interpolation polynomial generator, the level-1 Smolyak sparse grid formula with the sampling points being the roots of HPs is built. The deterministic electrothermal solver needs to be executed 53 times, since the number of sampling points  $(N_{\mathcal{H}})$  for physical parameters to obtain the level-1 Smolyak sparse grid formula is equal to  $2 \times (N_L + N_{t_{ox}}) + 1$ , and both  $N_L$  and  $N_{t_{ox}}$  are calculated to be 13, as shown in Table IV. The size of each simulation mesh is  $128 \times 128$ .

The maximum absolute errors of mean and standard deviation profiles are presented in Table V. The first two columns indicate the ratio pairs of WID and D2D variations to the total variations. Compared with  $2\times 10^4$  MC simulations, the maximum absolute errors of the estimated mean and standard deviation profiles from the developed statistical interpolation polynomial generator are shown in the fifth and sixth columns, respectively. As shown in Table V, the maximum absolute errors are less than 3.0% for all three different ratio pairs.

To fairly compare the runtime, the MC simulation is performed till achieving the same accuracy of standard deviation as the developed statistical interpolation polynomial generator. The number of MC simulations is shown in the #Samples column, and

$<sup>\</sup>kappa$ : the thermal conductivity of the die.

Fig. 12. Results of the MC method with or without considering the electrothermal effect: (a) and (b) are the mean temperature profiles with and without considering the electrothermal effect, respectively; (c) and (d) are the standard deviation profiles of temperature distribution with and without considering the electrothermal effect, respectively.

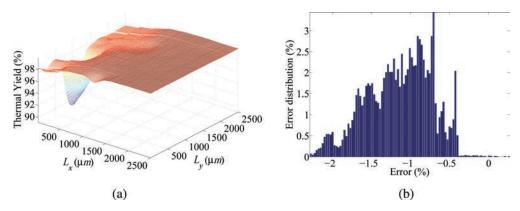

the Runtime column denotes the runtime for both methods. According to the Speedu column, the developed statistical interpolation polynomial generator can be orders of magnitude faster than the MC method. Under the ratio pair (WID, D2D) = (60%, 40%), the developed statistical interpolation polynomial generator takes 2.74 seconds to generate the interpolation polynomial of temperature profile for the  $128\times128$  simulation mesh. It contains 0.47 seconds for executing 53 deterministic electrothermal simulations, and 2.27 seconds to generate the interpolation polynomials after the 53 sampling temperature profiles are obtained.