# Low Operation Voltage InGaZnO Thin Film Transistors with LaAlO<sub>3</sub> Gate Dielectric Incorporation

Z. W. Zheng,<sup>a,z</sup> C. H. Cheng,<sup>b</sup> and Y. C. Chen<sup>c</sup>

<sup>*a*</sup> Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China <sup>*b*</sup> Department of Mechatronic Technology, National Taiwan Normal University, Taipei 106, Taiwan <sup>*c*</sup> Institute of Photonic System, National Chiao Tung University, Hsinchu 300, Taiwan

In this paper, we report low operation voltage indium gallium zinc oxide (IGZO) thin film transistors (TFTs) incorporating a high- $\kappa$  lanthanum aluminum oxide (LaAlO<sub>3</sub>) as gate dielectric. Good TFT characteristics were achieved simultaneously, including a small subthreshold swing (*SS*) of 98 mV/dec, a low threshold voltage (*V*<sub>t</sub>) of 0.29 V, a good on-off-state drive current ratio (*I*<sub>on</sub>/*I*<sub>off</sub>) of 1.1 × 10<sup>5</sup>, and field effect mobility ( $\mu_{FE}$ ) of 5.4 cm<sup>2</sup>/V · sec. These good performances are related to the high gate capacitance density and small equivalent oxide thickness (EOT) provided by the high- $\kappa$  LaAlO<sub>3</sub> dielectric. Moreover, the effects of oxygen partial pressure during IGZO deposition process on the device characteristics were investigated. The small *SS* and low *V*<sub>t</sub> allow the devices to be used at operation voltage as low as 1.5 V, which shows the great potential for future high speed and low power applications. (© 2013 The Electrochemical Society. [DOI: 10.1149/2.020309jss] All rights reserved.

Manuscript submitted May 6, 2013; revised manuscript received June 3, 2013. Published July 6, 2013.

With the rapid development of active-matrix flat panel displays (AMFPDs), thin film transistor (TFT) technologies have been widely used for display applications. However, the traditional Si TFTs using amorphous silicon and poly-crystalline silicon as active channel layer face difficulties due to physical drawback properties.<sup>1–3</sup> Recently, the new TFTs with transparent oxide semiconductors have attracted much attention as potential candidates, due to their unique optical and electrical advantages as compared to conventional Si TFTs, such as high mobility, low cost, excellent uniformity, and good transparency to visible light.<sup>4–25</sup> Particularly, indium gallium zinc oxide (IGZO) TFT<sup>7–25</sup> with superior stability and performance is one of the most promising candidates and has been widely studied. Moreover, the IGZO TFTs can be processed with very low thermal budget and used in emerging flexible display applications.

With the above merits of IGZO film, the IGZO TFT devices are being considered for a variety of applications, such as low-cost largearea displays, RFIDs and wearable electronics.<sup>7,8</sup> For high-speed display circuits, it requires TFTs to operate at low voltages and high drive currents with low threshold voltage  $(V_t)$  and small subthreshold swing (SS), which make low operation voltage TFTs very favorable for efficiency improvement and environment energy conservation. To address these concerns, incorporating high-k gate dielectric into TFT provides an alternative solution to achieve these goals.<sup>26-28</sup> In this paper, we report a low operation voltage IGZO TFT by introducing a high- $\kappa$  lanthanum aluminum oxide (LaAlO<sub>3</sub>)<sup>28–30</sup> as gate dielectric. Due to the higher  $\kappa$ -value (~23) of LaAlO<sub>3</sub> dielectric as compared to that of SiO<sub>2</sub> ( $\sim$ 3.9), the gate capacitance density increases, which lowers the  $V_t$  and improves the gate leakage current. Besides, the LaAlO<sub>3</sub> dielectric has good reliability of low bias temperature instability among high-k devices. The LaAlO3 TFTs showed a small SS of 98 mV/dec, a low Vt of 0.29 V, good on-off-state drive current ratio  $(I_{\rm on}/I_{\rm off})$  of  $1.1 \times 10^5$ , and field effect mobility ( $\mu_{\rm FE}$ ) of  $5.4 \, {\rm cm}^2/{\rm V} \cdot {\rm sec}$ at the operation voltage as low as 1.5 V. Furthermore, the influences of oxygen partial pressure during IGZO film deposition process on the device characteristics were investigated, since IGZO has electrons as majority carriers, which is mainly affected by the oxygen vacancies.<sup>31</sup> The present results demonstrate that IGZO TFTs with high-K LaAlO<sub>3</sub> as gate dielectric has great promise in future high speed and low power applications.

## Experimental

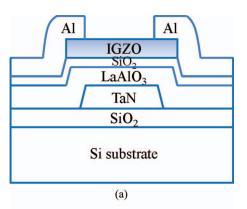

Figure 1a and 1b show the schematic cross-sectional structure and microscopic image of the IGZO TFT device, respectively. The channel width (*W*) and length (*L*) of the TFTs were 500  $\mu$ m and 50  $\mu$ m, respectively. Bottom-gate top-contact IGZO TFTs were fabricated on

<sup>z</sup>E-mail: wei7553@hotmail.com

an insulated SiO<sub>2</sub>/Si substrate through a four-shadow-mask process flow. Firstly, a 50 nm TaN was deposited by physical vapor deposition (PVD) and patterned as gate (G) electrode. Next, a 30 nm LaAlO<sub>3</sub> and a 10 nm SiO<sub>2</sub> were deposited by PVD as gate dielectrics, followed by a 400°C O<sub>2</sub> annealing to improve the gate oxide quality. Sequentially, a 40 nm IGZO was formed as active channel layer by dc reactive sputtering using an IGZO target with a power of 80 W and an oxygen partial pressure of P<sub>O2</sub> = 50% in Ar and O<sub>2</sub> mixed gas ambient under a working pressure of 7.6 mTorr at room temperature. Here, oxygen partial pressure of P<sub>O2</sub> (%) is defined as the mixing ratio of O<sub>2</sub> / (O<sub>2</sub> + Ar). Finally, Al source (S)/drain (D) electrodes of 300 nm

**Figure 1.** (a) Schematic cross-sectional structure and (b) microscopic image of the IGZO TFT device with LaAlO<sub>3</sub> gate dielectric incorporation.

were deposited, followed by sintering at 300°C in N<sub>2</sub> ambient to reduce the contact resistance. The control samples of IGZO/LaAlO<sub>3</sub> TFT without SiO<sub>2</sub> layer insertion were fabricated for comparison. To further evaluate the effects of oxygen partial pressure during IGZO deposition on the device characteristics, the TFT devices with P<sub>O2</sub> of 33% and 0% in IGZO deposition were also fabricated. The metalinsulator-metal (MIM) capacitors were also fabricated to investigate gate dielectric. The TFT devices were characterized by current-voltage (*I-V*) and capacitance-voltage (*C-V*) measurements using HP4156C semiconductor parameter analyzer.

#### **Results and Discussion**

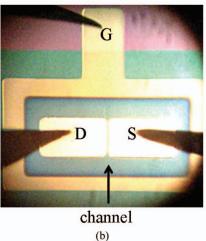

Figure 2a and 2b show the C-V and J-V characteristics of the TaN/LaAlO<sub>3</sub>/Al and TaN/LaAlO<sub>3</sub>/SiO<sub>2</sub>/Al gate capacitors on the same substrate, respectively. The high capacitance density of  $\sim 0.62 \ \mu F/cm^2$  and  $\sim 0.23 \ \mu F/cm^2$  was measured for the TaN/LaAlO<sub>3</sub>/Al and TaN/LaAlO<sub>3</sub>/SiO<sub>2</sub>/Al MIM capacitors, respectively. It indicates an equivalent oxide thickness (EOT) of ~5.5 nm and  $\sim$ 15 nm for single LaAlO<sub>3</sub> and bilayer LaAlO<sub>3</sub>/SiO<sub>2</sub> gate dielectrics, respectively, giving a high  $\kappa$ -value of  $\sim$ 21–23 in the LaAlO<sub>3</sub> dielectric. Such large gate capacitance density can give the advantages of lowering the operation voltage, increasing the transistor drive current, and improving the  $I_{on}/I_{off}$ . Besides, the large gate leakage of  $6.9 \times 10^{-6}$  A/cm<sup>2</sup> at -2 V bias was significantly decreased to  $1.5 \times 10^{-7}$  A/cm<sup>2</sup> after the insertion of SiO<sub>2</sub> layer. This SiO<sub>2</sub> layer evaporated at room temperature without sputtering plasma damage can effectively reduce interface state near the IGZO active channel layer.23,24

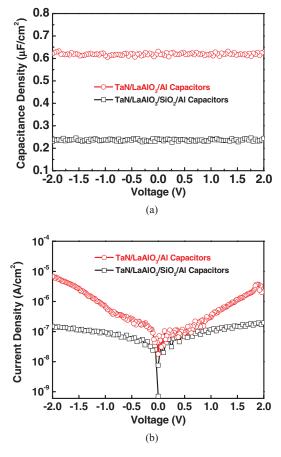

The output  $I_d$ - $V_d$  characteristics of the IGZO/SiO<sub>2</sub>/LaAlO<sub>3</sub> TFT when P<sub>O2</sub> = 50% are shown in Figure 3a. An enhancement-mode

**Figure 2.** (a) *C-V* and (b) *J-V* characteristics of the TaN/LaAlO<sub>3</sub>/Al and TaN/LaAlO<sub>3</sub>/SiO<sub>2</sub>/Al gate capacitors fabricated on the same substrate.

**Figure 3.** (a) Output  $I_d$ - $V_d$  characteristics and (b) transfer  $I_d$ - $V_g$  characteristics of the IGZO/LaAlO<sub>3</sub> and IGZO/SiO<sub>2</sub>/LaAlO<sub>3</sub> TFTs when P<sub>O2</sub> = 50%.

behavior with good saturation characteristics was well observed even under an operation voltage as low as 1.5 V, which could enable energy saving for low power application. Figure 3b displays the transfer  $I_d$ - $V_g$  characteristics of the IGZO/LaAlO<sub>3</sub> and IGZO/SiO<sub>2</sub>/LaAlO<sub>3</sub> TFTs when P<sub>O2</sub> = 50% for a  $V_d$  of 0.4 V, along with the  $I_d^{1/2}$  versus  $V_g$ plot. For the TFT device characteristics,  $V_t$  can be determined from the linear  $I_d^{1/2}$ - $V_g$  curve and  $I_{on}/I_{off}$  can be obtained from the  $I_d$ - $V_g$  curve. Besides,  $\mu_{FE}$  can be extracted from a gradual channel approximation in the linear region using the equation:<sup>32</sup>

$$\mu_{\rm FE} = \partial I_{\rm d} / \partial V_{\rm g} \cdot L / (W \cdot V_{\rm d} \cdot C_{\rm g}), \qquad [1]$$

where  $I_d$ ,  $V_d$ ,  $V_g$ , L, W, and  $C_g$  are the drain current, drain voltage, gate voltage, channel length, channel width, and gate insulator capacitance per unit area, respectively. For the IGZO/LaAlO3 TFT device, it shows a  $V_t$  of 0.41 V and a low operation voltage of 1.5 V, but suffers a low  $I_{\rm on}/I_{\rm off}$  of 1.4  $\times$  10<sup>3</sup>, a small  $\mu_{\rm FE}$  of 1.3 cm<sup>2</sup>/V  $\cdot$  sec and a large SS of 390 mV/dec. In contrast, the IGZO/SiO2/LaAlO3 TFT device exhibits a much larger  $\mu_{FE}$  of 5.4 cm<sup>2</sup>/V · sec and a higher  $I_{on}/I_{off}$  of 1.1 × 10<sup>5</sup> due to small gate leakage current, with a  $V_t$  of 0.29 V. Besides, a much smaller SS of 98 mV/dec is achieved in the IGZO/SiO<sub>2</sub>/LaAlO<sub>3</sub> TFT device and closed to the theoretical minimum value of 60 mV/dec at room temperature, indicating the device can be switched on fast at very low operation voltage. These good performances can be attributed to the insertion of SiO<sub>2</sub> layer, which is necessary for stable operation of TFT devices.<sup>23,24,33</sup> By introducing smooth SiO<sub>2</sub> layer insertion, the high-k surface can be passivated and the interface trap issue can be effectively reduced, thus the performances can be improved, as reported in the literatures.<sup>23,24</sup>

To further investigate the influences of oxygen partial pressure during IGZO deposition process, the IGZO/SiO<sub>2</sub>/LaAlO<sub>3</sub> TFT device characteristics with the IGZO active channel layers deposited at different oxygen partial pressure ( $P_{O2} = 0\%$  and  $P_{O2} = 33\%$ ) were

Downloaded on 2014-04-27 to IP 140.113.38.11 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms\_use) unless CC License in place (see abstract).

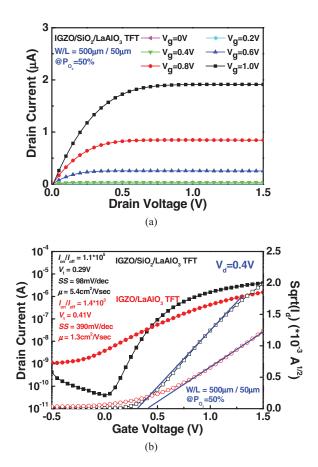

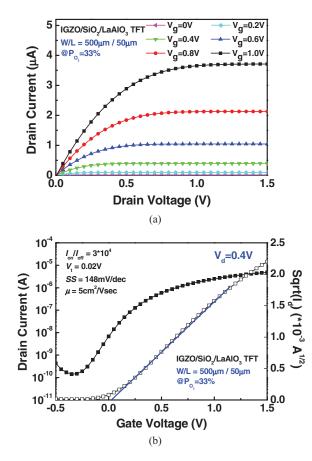

Figure 4. (a) Output  $I_d$ - $V_d$  characteristics and (b) transfer  $I_d$ - $V_g$  characteristics of the IGZO/SiO<sub>2</sub>/LaAlO<sub>3</sub> TFT when  $P_{O2} = 33\%$ .

compared to the characteristics of TFT device when  $P_{O2} = 50\%$ . It is well-known that the carrier concentration and the mobility of sputtered IGZO film can be controlling by the mixing ratio of sputtering gases during deposition process.<sup>25</sup> Defects created by the ion bombardments and incorporation of sputtering ions act as scattering centers or charge traps for the carriers, and thus degrade the electrical device performances.<sup>17</sup> For the  $P_{O2} = 0\%$  TFT device, it behaved with failed transistor characteristics with large leakage current (not shown). For the  $P_{O2} = 33\%$  TFT device, the output  $I_d$ - $V_d$  and transfer  $I_{\rm d}$ - $V_{\rm g}$  characteristics are shown in Figure 4a and 4b, respectively. As compared to the TFT device when  $P_{O2} = 50\%$ , the  $P_{O2} = 33\%$ TFT device exhibits degraded performances, including a much lower  $I_{\rm on}/I_{\rm off}$  of 3  $\times$  10<sup>4</sup> and a smaller  $\mu_{\rm FE}$  of 5 cm<sup>2</sup>/V  $\cdot$  sec, and a much larger SS of 148 mV/dec with a  $V_t$  of 0.02 V. It can be attributed to the oxygen partial pressure when depositing the IGZO film as the active channel layer. Since the IGZO film has electrons as majority carriers, which is mainly affected by the oxygen vacancies during deposition process.<sup>31</sup> When the IGZO film is deposited at low P<sub>02</sub> =0%, the oxygen is not supplied sufficiently, causing the increase of oxygen vacancies, which may act as shallow donors.<sup>34</sup> In this case, the active IGZO film would have a relatively high carrier density and behave with conducting property. This may be one of the reasons why the TFT using IGZO film when  $P_{O2} = 0\%$  exhibited failed transistor characteristics with large leakage current. However, with the increase of P<sub>02</sub> when depositing the IGZO film, the amount of the oxygen vacancies decrease, leading to the decrease of carrier density, and thus the IGZO electrical property may change from conducting to insulating via semiconducting. It agrees with the improved TFT device characteristics when increasing the  $P_{O2}$  from 0% to 50% during the active IGZO channel layer deposition process.

# Conclusions

In conclusion, incorporating a high-κ LaAlO<sub>3</sub> as gate dielectric, the IGZO TFTs show a small SS of 98 mV/dec, a low  $V_t$  of 0.29 V, a good  $I_{\rm on}/I_{\rm off}$  of  $1.1 \times 10^5$ , and an acceptable  $\mu_{\rm FE}$  of 5.4 cm<sup>2</sup>/V · sec at operation voltage as low as 1.5 V. These good performances were related to the high gate capacitance density and small EOT by introducing the high-κ LaAlO<sub>3</sub> dielectric. Furthermore, with relatively high oxygen partial pressure during IGZO deposition process, the TFT device characteristics could be improved due to the low oxygen vacancy formation. The present results show that these low operation voltage IGZO TFTs with high-κ LaAlO<sub>3</sub> as gate dielectric have high potential for future high speed and low power applications.

#### Acknowledgment

The authors thank Professor Albert Chin in National Chiao Tung University, Hsinchu, Taiwan, for his support and technical help on experiments.

### References

- 1. C. W. Chen, T. C. Chang, P. T. Liu, H. Y. Lu, K. C. Wang, C. S. Huang, C. C. Ling, and T. Y. Tseng, *IEEE Electron Device Lett.*, **26**, 731 (2005). K. M. Chang, W. C. Yang, and C. P. Tsai, *IEEE Electron Device Lett.*, **24**, 512 (2003).

- 2.

- 3. C. H. Tseng, T. K. Chang, F. T. Chu, J. M. Shieh, B. T. Dai, H. C. Cheng, and A. Chin, IEEE Electron Device Lett., 23, 333 (2002).

- 4. R. L. Hoffman, B. J. Norris, and J. F. Wager, Appl. Phys. Lett., 82, 733 (2003).

- B. Yaglioglu, H. Y. Yeom, R. Beresford, and D. C. Paine, Appl. Phys. Lett., 89, 5. 062103 (2006).

- N. L. Dehuff, E. S. Kettenring, D. Hong, H. Q. Chiang, J. F. Wager, R. L. Hoffman, C. H. Park, and D. A. Keszler, J. Appl. Phys., 97, 064505 (2005).

- 7. K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature, 432, 488 (2004).

- E. Fortunato, P. Barquinha, and R. Martins, Adv. Mater., 24, 2945 (2012).

- 9. N. C. Su, S. J. Wang, and A. Chin, IEEE Electron Device Lett., 30, 1317 (2009).

- 10. A. Sato, M. Shimada, K. Abe, R. Hayashi, H. Kumomi, K. Nomura, T. Kamiya,

- M. Hirano, and H. Hosono, Thin Solid Films, 518, 1309 (2009). 11. J. S. Park, T. W. Kim, D. Stryakhilev, J. S. Lee, S. G. An, Y. S. Pyo, D. B. Lee,

- Y. G. Mo, D. U. Jin, and H. K. Chung, *Appl. Phys. Lett.*, **95**, 013503 (2009).

I.Y. Kwon, K. S. Son, J. S. Jung, T. S. Kim, M. K. Ryu, K. B. Park, B. W. Yoo,

- J. W. Kim, Y. G. Lee, K. C. Park, S. Y. Lee, and J. M. Kim, IEEE Electron Device Lett., 29, 1309 (2008).

- 13. P. Barquinha, L. Pereira, G. Goncalves, R. Martins, and E. Fortunato, J. Electrochem. Soc., 156, H161 (2009).

- 14. A. Suresh, P. Wellenius, and J. F. Muth, in IEDM Tech. Dig., 587 (2007).

- P. Barquinha, A. M. Vila, G. Goncalves, L. Pereira, R. Martins, J. R. Morante, and 15. E. Fortunato, IEEE Trans. Electron Devices, 55, 954 (2008).

- 16. J. B. Kim, C. Fuentes-Hernandez, and B. Kippelen, Appl. Phys. Lett., 93, 242111 (2008).

- 17. H. Yabuta, M. Sano, K. Abe, T. Aiba, T. Den, H. Kumomi, K. Nomura, T. Kamiya, and H. Hosono, Appl. Phys. Lett., 89, 112123 (2006).

- 18. S. Y. Huang, T. C. Chang, M. C. Chen, S. W. Tsao, S. C. Chen, C. T. Tsai, and H. P. Lo, Solid-State Electronics, 61, 96 (2011).

- 19. H. S. Uhm, S. H. Lee, W. Kim, and J. S. Park, IEEE Electron Device Lett., 33, 543 (2012).

- N. C. Su, S. J. Wang, C. C. Huang, Y. H. Chen, H. Y. Huang, C. K. Chiang, and A. Chin, *IEEE Electron Device Lett.*, 31, 680 (2010).

- 21. W. Lin, J. H. Jang, S. H. Kim, D. P. Norton, V. Craciun, S. J. Pearton, F. Ren, and H. Shen, Appl. Phys. Lett., 93, 082102 (2008).

- J. C. Park and H. N. Lee, IEEE Electron Device Lett., 33, 818 (2012).

- 23. M. Kitamura and Y. Arakawa, Appl. Phys. Lett., 89, 223525 (2006).

- 24. J. H. Na, M. Kitamura, D. Lee, and Y. Arakawa, Appl. Phys. Lett., 90, 163514 (2007).

- 25. J. H. Na, M. Kitamura, and Y. Arakawa, Appl. Phys. Lett., 93, 063501 (2008).

- 26. M. F. Chang, P. T. Lee, S. P. McAlister, and A. Chin, IEEE Electron Device Lett., 29,

- 215 (2008). 27. M. F. Chang, P. T. Lee, S. P. McAlister, and A. Chin, IEEE Electron Device Lett., 30, 133 (2009)

- 28. B. F. Hung, K. C. Chiang, C. C. Huang, A. Chin, and S. P. McAlister, IEEE Electron Device Lett., 26, 384 (2005).

- 29. D. S. Yu, K. C. Chiang, C. F. Cheng, A. Chin, C. Zhu, M. F. Li, and D. L. Kwong, IEEE Electron Device Lett., 25, 559 (2004).

- 30. D. S. Yu, A. Chin, C. C. Laio, C. F. Lee, C. F. Cheng, W. J. Chen, C. Zhu, M. F. Li, W. J. Yoo, S. P. McAlister, and D. L. Kwong, in IEDM Tech. Dig., 181 (2004).

- 31. H. Omura, H. Kumomi, K. Nomura, T. Kamiya, M. Hirano, and H. Hosono, J. Appl. Phys., 105, 093712 (2009).

- 32. S. M. Sze and K. K. Ng, Physics of Semiconductor Devices, 3rd ed., p. 308, John Wiley & Sons, New Jersey (2007)

- 33. G. Wang, D. Moses, A. J. Heeger, H. M. Zhang, M. Narasimhan, and R. E. Demaray, J. Appl. Phys., 95, 316 (2004)

- 34. A. Janotti and C. G. Van de Walle, Phys. Rev. B, 76, 165202 (2007).