Home Search Collections Journals About Contact us My IOPscience

Modulation of Interface and Bulk States in Amorphous InGaZnO Thin-Film Transistors with Double Stacked Channel Layers

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2013 Jpn. J. Appl. Phys. 52 090205

(http://iopscience.iop.org/1347-4065/52/9R/090205)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 24/04/2014 at 14:32

Please note that terms and conditions apply.

## Modulation of Interface and Bulk States in Amorphous InGaZnO Thin-Film Transistors with Double Stacked Channel Layers

Runze Zhan<sup>1</sup>, Chengyuan Dong<sup>1</sup>, Bo-Ru Yang<sup>2</sup>, and Han-Ping D. Shieh<sup>1,3</sup>

Received May 7, 2013; accepted July 4, 2013; published online August 9, 2013

A high-performance amorphous InGaZnO (a-IGZO) thin-film transistor (TFT) was achieved using a double stacked channel layer (DSCL). An oxygen-poor IGZO film was deposited in pure argon ambient as a buffer layer to prevent oxygen plasma bombardment and improve device performance. An oxygen-rich IGZO film was then deposited on top of that buffer layer to modulate device stability. With this structure, an interface with low oxygen-plasma-induced damage and few oxygen vacancies in the bulk was achieved using DSCL, leading to a higher stability of the threshold voltage. © 2013 The Japan Society of Applied Physics

morphous InGaZnO (a-IGZO) is a very promising channel material in thin-film transistors (TFTs) for advanced applications in flat panel display, because of its advantages such as high mobility, room-temperature deposition, and potential flexibility. To date, much effort has been devoted to improve the electrical performance of a-IGZO TFTs. 1-5) However, the stability of a-IGZO TFTs still remains the most crucial issue for their practical applications. For oxide TFTs, their stability has been found to be dominated by interface traps (between the channel layer and gate insulator) and/or bulk traps in the channel layer. Thus, it is important to optimize the interface and bulk states of a-IGZO TFTs to achieve better stability. Generally, interface states could be improved by thermal annealing, plasma treatment, or the use of a high-k dielectric as a gate insulator, 6-8) while better bulk states might be achieved using appropriate conditions for channel layers, such as chamber pressure and reactive gases. 9,100 In particular, frontchannel and back-channel protecting layers were applied to improve the interface and bulk states. 11) Recently, it has been reported by our group and other researchers that a TFT with a double-stacked channel layer (DSCL) might exhibit better performance and stability since its interface and bulk states could be effectively modulated. 12,13) However, those previous reports have not clearly explained the mechanism underlying the improvement. Moreover, design rules for DSCLs, e.g., how to define the thickness in DSCL IGZO-TFTs are still unclear. In this study, the effects of both the thickness of the front-channel layer and the oxygen flow rate (OFR) for the back-channel layer on the performance and stability of DSCL IGZO TFTs are studied. In particular, the impact of oxygen plasma damage to the front channel interface is discussed. Finally, the design rules for DSCL are summarized.

We fabricated a DSCL by firstly depositing an IGZO layer in pure argon ambient, and then depositing a subsequent IGZO layer under controlled oxygen pressure. The rationale of the experimental design is to prevent oxygen plasma from damaging the interface between the gate-insulation and channel layers, as oxygen plasma causes more damages than argon plasma. The second-step deposition under controlled oxygen pressure is to control oxygen vacancies for better device stability. <sup>12,13)</sup>

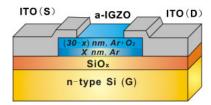

**Fig. 1.** (Color online) Schematic diagram of the a-IGZO TFT with DSCL. An x-nm-thick a-IGZO film was deposited without oxygen, then a (30-x)-nm-thick a-IGZO film was deposited at different OFRs. The total thickness of the channel layer was fixed at 30 nm.

The device was fabricated as follows: As shown in Fig. 1, a piece of heavily doped silicon substrate was used as the gate electrode, and a-IGZO channel layers were grown by RF magnetron sputtering at room temperature on a 100nm-thick thermal SiO<sub>2</sub> as the gate insulator. The a-IGZO channel and source/drain electrodes were defined by a shadow mask. ITO layers as source/drain electrodes were deposited by RF magnetron sputtering. For the channel layer, IGZO films deposited without and with oxygen, called oxygen-poor (pure argon ambient) and oxygen-rich IGZO films, were served as the front- and back-channel layers, respectively. The total thickness of channel layer was fixed at 30 nm, and TFTs with front-channel layers of various thicknesses (x) were fabricated to study the thickness effects on device performance and stability. The channel length (L)and channel width (W) were 200 and 1000  $\mu$ m, respectively. All of the a-IGZO TFTs were annealed at 350 °C for 1 h in a nitrogen furnace to improve their electrical properties. The thickness of the a-IGZO films was determined by atomic force microscopy (Vecco Nanoscope IIIA) and the oxygen content of the a-IGZO films was measured by X-ray photoemission spectroscopy (XPS; Thermal-fisher ESCLAB 250). The electrical characteristics of a-IGZO TFTs were obtained at room temperature using a Keithley 4200 semiconductor characterization system.

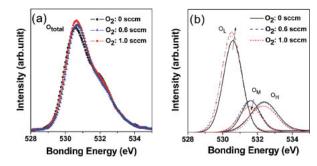

It has been reported that the increase in OFR for deposition may produce IGZO films of higher oxygen contents. Here, we further carried out XPS measurement to verify this point. The XPS spectra of O 1s signals in three types of a-IGZO thin films deposited at different OFRs of 0 (pure argon

<sup>&</sup>lt;sup>1</sup>National Engineering Lab for TFT-LCD Materials and Technologies, Department of Electronic Engineering, Shanghai Jiao Tong University, Shanghai 200240, China

<sup>&</sup>lt;sup>2</sup> State Key Laboratory of Optoelectronic Materials and Technologies, School of Physics and Engineering, Sun Yat-Sen University, Guangzhou 510274. China

<sup>&</sup>lt;sup>3</sup> Department of Photonics and Display Institute, National Chiao Tung University, Hsinchu 30010, Taiwan

**Fig. 2.** (Color online) XPS spectra of IGZO thin films: (a) O 1s at different OFRs. (b) The  $O_H$ ,  $O_M$ , and  $O_L$  fitting spectra extracted from the O 1s of IGZO films deposited at different OFRs of 0, 0.6, and 1.0 sccm, respectively.

ambient), 0.6, and 1.0 sccm are shown in Fig. 2(a). The O 1s peak can be fitted by three nearly Gaussian distributions, approximately centered at 530.5, 531.6, and 532.4 eV, 14) as shown in Fig. 2(b). The low-binding-energy peak (O<sub>L</sub>) at  $530.5 \,\mathrm{eV}$  is related to  $\mathrm{O}^{2-}$  ions that combined with the Zn, Ga, and In atoms in the IGZO compound system. The highbinding-energy peak (O<sub>H</sub>) at 532.4 eV is associated with loosely bonded oxygen on the IGZO film surface, such as -CO<sub>3</sub>, absorbed H<sub>2</sub>O, and O<sub>2</sub>. The binding energy component (O<sub>M</sub>) at 531.6 eV is attributed to O<sup>2-</sup> ions that are in the oxygen-deficient region in the IGZO matrix. In general, O<sub>M</sub>-related oxygen vacancies supply free-electron carriers in the IGZO film, resulting in an increase in electron concentration.<sup>2)</sup> The decrease in area of the O<sub>M</sub> peak with increasing OFR is attributed to the reduction in the number of oxygen vacancies, resulting from the abundant supply of O atoms. The ratios of oxygen vacancies to total oxygen (O<sub>M</sub>/O<sub>tot</sub>) in IGZO films significantly diminishes from 18.65 to 17.74% as the OFRs decrease from 1.0 to 0 sccm. Our results provide quantitative evidence indicating that a-IGZO films of fewer oxygen vacancies can be achieved by reducing the OFR for the deposition of IGZO films.

It was reported by our group that using an oxygenpoor IGZO film as a front-channel layer improved device performance and interface states. 12) In this study, DSCL a-IGZO TFTs with different-thickness front-channel layers were proposed to further investigate the improvement in interface states, which were not well studied previously. The electrical characteristics of DSCL TFTs with differentthickness front-channel layers are shown in Fig. 3(a), where a hysteresis loop was obtained under a sweeping  $V_{gs}$  from -10 to  $30\,\mathrm{V}$  at the same sweep speed. Here, IGZO films deposited at an OFR of 0.6 sccm were used as the backchannel layer. The related performance parameters including field effect mobility ( $\mu_{\rm FE}$ ), subthreshold swing (SS), and  $\Delta V_{\text{th\_hys}}$  are shown in Fig. 3(b).  $\Delta V_{\text{th\_hys}}$  shown in Fig. 3(a) is defined as the threshold voltage  $(V_{th})$  change in hysteresis loops. It is found that, as the thickness (x) of the front-channel layer increases, better electrical properties are achieved, such as higher  $\mu_{FE}$ , lower SS, and lower  $\Delta V_{th\_hys}$ , which were associated with the increase in the carrier density of the channel layer. 12) Positive shifts in the hysteresis loops are observed, which could be ascribed to interface states between the channel layer and the gate insulator.<sup>15)</sup> For forward sweeping, the interface states initially discharge

**Fig. 3.** (Color online) (a)  $I_{\rm ds}-V_{\rm gs}$  multisweep transfer curves at  $V_{\rm ds}=10\,\rm V$ , and (b) SS and  $\mu_{\rm FE}$  for the DSCL TFTs as functions of the thickness (x) of the front channel layer deposited without oxygen. The backchannel layer was deposited at an OFR of 0.6 sccm.

15 x (nm) 30

0.7

trapped carriers and then begin trapping carriers while gate bias sweeps into the subthreshold region. Hence, lower SSs for the samples are obtained. Unfilled interface states could also degrade the effective mobility, as shown in Fig. 3(b). In contrast, for reverse sweeping, interface states are filled with carriers and become noninfluential in the subthreshold region, so that SS decreases. Moreover, carrier trapping/detrapping causes hysteresis. Thus, this result suggests that the improvement in the hysteresis characteristic of DSCL TFTs with thicker front-channel layers contributes to fewer traps at or near the channel layer-gate insulator interface, and an oxygen-poor IGZO film appears to be a buffer layer.

The mechanism for the oxygen-poor IGZO film serving as a front-channel layer could be explained as follows. For a-IGZO with DSCL, when oxygen is applied at a flow rate that produces oxygen-rich IGZO film as a back-channel layer, the effect of oxygen plasma on the channel layer-gate insulator interface should be considered. For the device fabricated with oxygen (x = 0 nm), more traps could be created at or near the interface between the channel layer and the gate insulator owing to the ion bombardment of oxygen plasma, leading to higher SS and  $\Delta V_{\text{th\_hvs}}$ . While the front-channel layer of the IGZOs film deposited in pure argon ambient is applied, the oxygen plasma damage could be alleviated and a decrease in the interface trap density is observed, leading to the improvement in SS. Therefore, when the thickness (x) of the front-channel layers increases to 20 nm or larger, a slight change in SS is observed. This reveals that, as the front-channel layer formed by oxygenpoor a-IGZO film is thick enough, which acts as a buffer

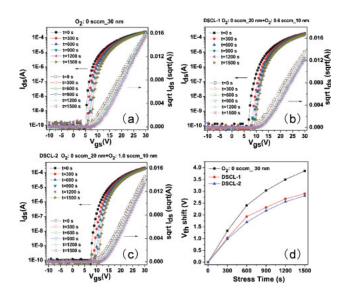

**Fig. 4.** (Color online) Time variations of (a)–(c) transfer curves and (d) threshold voltage shifts for TFTs with single channel layer, and different DSCLs under positive bias stress at room temperature.

layer, the number of defects induced by the following processes for the back-channel layer using oxygen-rich a-IGZO film is effectively reduced.

According to the investigation of the thickness effect of the front-channel layer on device performance, a 20-nmthick oxygen-poor IGZO film was adopted as the frontchannel layer, which was found to be thick enough to achieve a good interface state. On the other hand, it is also important to employ an oxygen-rich IGZO film as a back channel to improve device stability. Therefore, we applied the IGZO film depostied at different OFRs of 0, 0.6, and 1.0 sccm as the back-channel layers, respectively. The hysteresis of those devices reveals that stable interface states could be obtained (data not shown here). A DC-positive bias stress for 1,500 s was applied to TFTs with DSCL and single channel layer at room temperature in the ambience. Figure 4 shows the dependence of stress time on  $V_{th}$  for three types of a-IGZO TFTs under the stress conditions of  $V_{\rm gs} = 20 \, \rm V$  and  $V_{\rm ds} = 0$  V. It can be seen that all the devices exhibit positive shifts in  $V_{th}$  with little changes in SS and  $\mu_{FE}$ . Importantly, the TFTs with DSCL are more stable than those with a single channel layer. Besides, DSCL-2 (OFR of 1.0 sccm for the back-channel layer) shows the highest stability among the three types of IGZO TFTs.

For the a-IGZO TFTs with a DSCL, there are several reasons for the improved device stability. First, back-channel layers influence the bulk state of the entire channel layer. It was reported that the PBS-induced  $V_{\rm th}$  shift was contributed to charge trapping at the channel layer-gate insulator interface and/or in the bulk of the channel layer, when slight changes in SS and  $\mu_{\rm FE}$  were observed. Since similar front-channel layer interface states are obtained for the three types of TFTs, the increase in OFR for the back-channel layer leads to fewer oxygen vacancies in the entire channel layer. Thus, fewer defects in the bulk are achieved, resulting in better device stability. Second, the ambient effect may induce instability for unpassivated TFTs, which was dis-

cussed previously.<sup>12)</sup> Therefore, the variation in the bulk state and the back-channel layer leads to a difference in the PBS for a-IGZO TFTs.

Therefore, we can draw a conclusion on the basic design rules of DSCL IGZO TFTs. With an increase in front-channel-layer thickness, the electrical performance of DSCL IGZO-TFTs is improved owing to better interface states. However, an oxygen-rich IGZO of the back-channel layer is required to enhance electrical stability owing to the decrease in the number of bulk traps and/or ambient effect. According to our experimental results, the device with a front-channel layer of  $x=20\,\mathrm{nm}$  and a back-channel layer deposited at an OFR of 1.0 sccm is the best conditions for achieving both relatively good performance parameters ( $\mu_{\mathrm{FE}}=3.60\,\mathrm{cm^2\,V^{-1}\,s^{-1}}$ , SS = 0.91) and good stability ( $\Delta V_{\mathrm{th}}=2.81\,\mathrm{V}$ ).

In summary, the electrical performance and stability of a-IGZO TFTs with DSCL are investigated. An improved interface is obtained using an oxygen-poor IGZO film of appropriate thickness as the front channel layer, which acts as a buffer layer for reducing the oxygen plasma damage to the channel layer/gate insulator interface induced by the process of the upper oxygen-rich IGZO film. On the other hand, compared with conventional TFTs with single channel layers, TFTs with DSCL may achieve better electrical stability owing to weaker ambient effect and fewer defects in the bulk. The results indicate that not only the interface property but also the device stability of IGZO TFTs could be improved if an appropriate DSCL structure is designed.

**Acknowledgements** This work was supported by the 973 Project (Grant No. 2013CB328803) and the National Natural Science Foundation of China (Grant No. 61136004).

- K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono: Nature 432 (2004) 488.

- T. Kamiya, K. Nomura, and H. Hosono: Sci. Technol. Adv. Mater. 11 (2010) 044305.

- P.-T. Liu, Y.-T. Chou, L.-F. Teng, F.-H. Li, and H.-P. Shieh: Appl. Phys. Lett. 98 (2011) 052102.

- P.-T. Liu, Y.-T. Chou, L.-F. Teng, F.-H. Li, C.-S. Fuh, and H. D. Shieh: IEEE Electron Device Lett. 32 (2011) 1397.

- J. Yao, N. Xu, S. Deng, J. Chen, J. She, H. D. Shieh, P.-T. Liu, and Y.-P. Huang: IEEE Trans. Electron Devices 58 (2011) 1121.

- S. Park, S. Bang, S. Lee, J. Park, Y. Ko, and H. Jeon: J. Nanosci. Nanotechnol. 11 (2011) 6029.

- Y.-K. Moon, S. Lee, W.-S. Kim, B.-W. Kang, C.-O. Jeong, D.-H. Lee, and J.-W. Park: Appl. Phys. Lett. 95 (2009) 013507.

- X. Zou, G. Fang, L. Yuan, X. Tong, and X. Zhao: Semicond. Sci. Technol. 25 (2010) 055006.

- P. Barquinha, L. Pereira, G. Gonçalves, R. Martins, and E. Fortunato: J. Electrochem. Soc. 156 (2009) H161.

- J. H. Jeong, H. W. Yang, J.-S. Park, J. K. Jeong, Y.-G. Mo, H. D. Kim, J. Song, and C. S. Hwang: Electrochem. Solid-State Lett. 11 (2008) H157.

- C.-T. Chen, S.-S. Chen, W.-H. Lin, and P.-H. Chen: SID Symp. Dig. Tech. Pap. 42 (2011) 1208.

- R. Zhan, C. Dong, J. Shi, Y. Chen, J. Wu, B.-R. Yang, and H.-P. D. Shieh: SID Symp. Dig. Tech. Pap. 44 (2013) 1047.

- 13) J. H. Koo, T. S. Kang, and J. P. Hong: J. Korean Phys. Soc. **60** (2012)

- 14) G. H. Kim, W. H. Jeong, and H. J. Kim: Phys. Status Solidi A 207 (2010) 1677.

- C.-T. Tsai, T.-C. Chang, S.-C. Chen, I. Lo, S.-W. Tsao, M.-C. Hung, J.-J. Chang, C.-Y. Wu, and C.-Y. Huang: Appl. Phys. Lett. 96 (2010) 242105.