# Al-SiO<sub>2</sub>-Y<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>-poly-Si Thin-Film Transistor Nonvolatile Memory Incorporating a Y<sub>2</sub>O<sub>3</sub> Charge Trapping Layer

Tung-Ming Pan, a.Z Li-Chen Yen, Somnath Mondal, Chieh-Ting Lo, and Tien-Sheng Chaob

<sup>a</sup>Department of Electronics Engineering, Chang Gung University, Taoyuan 333, Taiwan

In this letter, we investigate the structural properties and electrical characteristics of the Al– $SiO_2$ – $Y_2O_3$ – $SiO_2$ –poly-Si (AOYOP) thin-film transistor (TFT) nonvolatile memory device. The composition of  $Y_2O_3$  charge-trapping layer was analyzed using X-ray photoelectron spectroscopy. The  $Y_2O_3$  AOYOP TFT memory device exhibited a large memory window of 2.5 V, a long charge retention time of ten years with a minimal charge loss of  $\sim$ 15%, and a better endurance performance for P/E cycles up to  $10^5$ . © 2013 The Electrochemical Society. [DOI: 10.1149/2.002310ssl] All rights reserved.

Manuscript submitted May 23, 2013; revised manuscript received July 5, 2013. Published July 13, 2013.

Low-temperature polycrystalline silicon thin-film transistors (LTPS-TFTs) are widely used for active matrix liquid crystal display and active matrix organic light emitting diode. With the rapid advance in the manufacturing technologies, the extent and complexity of circuit integration have been tremendously increased. The realization of integrating an entire system on the top of the panel is then being rigorously pursued by low-temperature process.<sup>2,3</sup> With the increasing demand of system reconfigurability in advanced system-on-chip (SOC), many different memory functions are necessitated. 4-6 Specifically, non-volatile memory (NVM) is crucial and, therefore, careful choice of the best NVM device to be integrated in the system is most important. Silicon-oxide-nitride-oxide-silicon (SONOS)-type flash memory device has received a considerable amount of interest in the electronics industry because of its non-volatility, low power consumption, and fast speed.<sup>7,8</sup> However, the erase saturation phenomenon and vertical stored charge migration<sup>9,10</sup> for conventional SONOS-type memory open critical issues in device performance and reliability.

Various technologies have been developed for improving the performance and reliability of SONOS-type memory. Chen et al. developed a bandgap engineering of SiN<sub>x</sub> film to improve the retention and endurance characteristics. 11 Lin et al. suggested the Hf-silicate film as the charge trapping layer deposited by cosputtering method for achieving long retention time and good endurance.<sup>12</sup> Recently, we have proposed and demonstrated an yttrium oxide (Y2O3) film as a good candidate for charge trapping layer in flash memory technology. 13,14 However, Y<sub>2</sub>O<sub>3</sub> thin film integrated in LTPS-TFT memory device has not been reported. Moreover, Y2O3 film can also be considered as one of the most promising candidate materials for LTPS-TFT memory applications due to its large dielectric constant (13~17) and wide bandgap energy (5.6 eV). 15,16 In this letter, we explore the structural properties and electrical characteristics of the Al-SiO<sub>2</sub>-Y<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>poly-Si (AOYOP) TFT nonvolatile memory device integrated with an Y<sub>2</sub>O<sub>3</sub> charge trapping layer. This memory exhibits good electrical characteristics, including large memory window, good retention time, and high endurance.

## Experimental

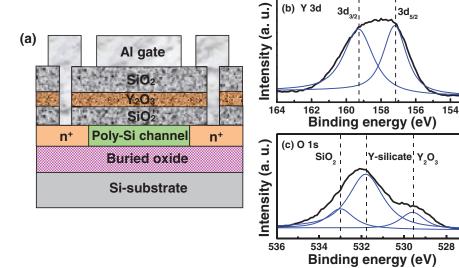

The cross sectional view of the  $Y_2O_3$  AOYOP TFT nonvolatile memory is illustrated in Fig. 1a. First, a 500 nm-thick thermal oxide was grown on the Si wafer by wet oxidation system to substitute the glass substrate. A 50 nm-thick amorphous-Si ( $\alpha$ -Si) film for the channel region was deposited at 550°C by a low-pressure chemical vapor deposition (LPCVD) system. Subsequently, solid-phase crystallization was performed at 600°C for 24 h in  $N_2$  ambient for polycrystalline channel formation. The source and drain (S/D) regions were doped by phosphorous ion implantation with a dose of 5 × 10<sup>15</sup> ions/cm<sup>-2</sup> at 17 keV, then activated by furnace at 600°C for 24 h. A ~10 nm tetraethyloxysilane (TEOS) silicon oxide film as a tunneling layer was deposited through LPCVD system. A ~3 nm-thick  $Y_2O_3$  film

was then deposited on the tunneling oxide by a physical vapor deposition system. Another thin film of  $\sim\!20\,\mathrm{nm}\,\mathrm{SiO_2}$  as a blocking oxide was deposited by plasma-enhanced chemical vapor deposition (PECVD) at 350°C. After creating the contact holes at S/D region, a 500 nm-thick Al was deposited by physical vapor deposition and patterned for gate and S/D contact pads. The length and width of the n-channel AOYOP TFT memory device were 10 and 10  $\mu m$ , respectively. The threshold voltage (V<sub>TH</sub>) values are obtained from the current-voltage (transfer characteristics) curves at a fixed drain current value of 100 nA (100  $\times$  W/L nA).

#### **Results and Discussion**

In order to analyze the physical properties of yttria charge trapping layer, the chemical elements were detected by X-ray photoemission spectroscopy (XPS). Figs. 1b and 1c show the Y 3d and O 1s spectra, respectively, of the  $Y_2O_3$  charge trapping film with their appropriate peak curve-fitting lines. The Y 3d double peaks (157.2 eV and 159.3 eV) shifted to higher binding energy by 0.4 eV relative to the  $Y_2O_3$  reference position (156.8 eV and 158.9 eV). It may be attributed to the formation of a silicate layer at the  $Y_2O_3$ -SiO2 interface. Fig. 1c depicts that the O 1s spectra of  $Y_2O_3$  film can be deconvoluted into three peaks located at 529.5, 531.8, and 533 eV, corresponding to  $Y_2O_3$ , Y-silicate, and SiO2, T respectively. The intensity of O 1s peak corresponding to silicate layer was larger compared to other peaks, indicating the formation of a thicker silicate layer between the  $Y_2O_3$  and SiO2 interface.

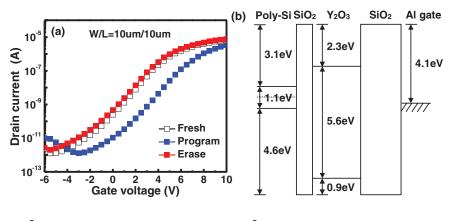

Fig. 2a shows the transfer characteristics of the Y2O3 AOYOP TFT memory device following the P/E operations. The AOYOP TFT memory device exhibited good transistor behavior with a high  $I_{on}/I_{off}$ ratio of 5.3  $\times$  10<sup>6</sup>. The field-effect mobility of 15.32 cm<sup>2</sup>  $\cdot$  V<sup>-1</sup>  $\cdot$  s<sup>-1</sup> and a subthreshold swing of 1.34 V/dec were obtained in the AOYOP TFT memory device. The TFT memory device was programmed by channel hot electron (CHE) injection method, whereas the erasing was carried out by band-to-band hot hole (BTBHH) injection to the device. After programming at the  $V_{GS}$  of 10 V and the  $V_{DS}$  of 10 V for 1 s, the threshold voltage shifted from 3.4 V (fresh device) to 5.6 V (programmed state). This can be attributed to the electron trapping in the charge trapping layer in the TFT memory device. The electron trapping can be explained by considering the band diagram presented in Fig. 2b. The conduction band offset between the tunneling oxide and the Y<sub>2</sub>O<sub>3</sub> charge trapping layer is 2.3 eV. The large electric field in the poly-Si channel of the TFT device creates impact ionized hot-electrons whose energy when exceeds the gate-oxide potential barrier (3.1 eV) can be injected to the gate oxide and Y2O3 charge trapping layer. This electron trapping causes the I<sub>DS</sub>-V<sub>GS</sub> curve in Fig. 2a to move to the right, and thus increasing the V<sub>TH</sub> value after programming. After erase operation of the TFT memory device, we can clearly observe that the I<sub>DS</sub>-V<sub>GS</sub> curve did not fully recover to the initial transfer characteristic. This behavior might be due to the mismatch between the localized spatial distributions for the injected electrons and holes by using CHE programming and BTBHH erasing. The uncompensated

<sup>z</sup>E-mail: tmpan@mail.cgu.edu.tw

<sup>&</sup>lt;sup>b</sup>Department of Electrophysics, National Chiao Tung University, Hsinchu 30010, Taiwan

**Figure 1.** (a) Cross-sectional view of the AOYOP TFT device memory structure using a  $Y_2O_3$  charge trapping layer. XPS spectra of (b) Y 3d and (c) O 1s for  $Y_2O_3$  charge trapping layers.

**Figure 2.** (a) Transfer characteristics of the AOYOP TFT memory device. (b) Band diagram of the AOYOP TFT memory.

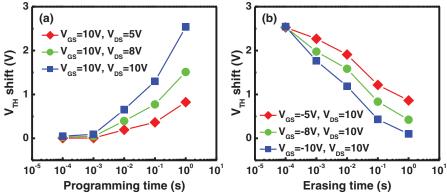

**Figure 3.** (a) Programming and (b) erasing characteristics of AOYOP TFT memory devices.

charge will then cause the  $V_{TH}$  to shift. Moreover, another important parameter for memory read-out operation in the TFT memory device is the difference between the programming current ( $I_{PR}$ ) and the erasing current ( $I_{ER}$ ) at certain reading voltage. The  $I_{PR}/I_{ER}$  current ratio of programmed and erased state in AOYOP TFT device at the read-out voltage of 2 V is more than two-orders-of magnitude, which suffices for nonvolatile memory applications.

Figure 3a demonstrates the program speed of the AOYOP TFT memory device, performed under three different stress conditions at  $V_{DS}$  of 5, 8, and 10 V and  $V_{GS}$  of 10 V for CHE programming. The  $V_{TH}$  shift is defined as the change in the threshold voltage of a TFT memory device between the programmed and the erased states. At the larger programming bias at  $V_{GS} = V_{DS} = 10$  V for 1 s programming, we observed a large  $V_{TH}$  shift of  $\sim$ 2.5 V. It is also observed that the  $V_{TH}$  shift increases with the increase of applied drain voltage. This

is because a large amount of "hot" electrons were generated when a larger drain voltage was applied, and thus more electrons were capable of crossing the barrier height to become trapped in the  $\rm Y_2O_3$  layer. The erase speed behaviors of the AOYOP TFT memory device were also presented in Fig. 3b. We can clearly observe significant increase of programming and erasing speed for higher drain and gate voltage, respectively.

Fig. 4a shows the retention characteristics of the AOYOP TFT memory devices at room temperature and  $85^{\circ}$ C. The retention measurement was performed after the CHE programming. The normalized  $V_{TH}$  shift is defined as the ratio of  $V_{TH}$  shift at the time of interest and at the beginning. The retention times of the AOYOP TFT memory device can be extrapolated more than 10 years operation time for a minimal charge loss of 15% at room temperature. Such good retention behavior can be attributed to the tight embrace of the  $Y_2O_3$  trapping layer with

**Figure 4.** (a) Retention and (b) endurance characteristics of AOYOP TFT memory devices.

sufficiently deep trap energy level. However, at elevated temperature of 85°C, the retention capability of AOYOP TFT memory device degraded significantly and a charge loss of  $\sim$ 35% was observed after 10<sup>8</sup> s. We believed that the AOYOP device with a thick tunnel oxide can be used to improve the charge-keeping capability. Fig. 4b demonstrates the endurance characteristics of the AOYOP TFT memory device. The device was programmed at  $V_{GS} = 10 \text{ V}$  and  $V_{DS} = 10 \text{ V}$ and erased at  $V_{GS} = -10 \text{ V}$  and  $V_{DS} = 10 \text{ V}$  with the same programming and erasing time of 1 s. No significant memory window narrowing is observed in the AOYOP TFT memory device. Though, the V<sub>TH</sub> increases for both memory states after 10<sup>3</sup> P/E cycles. We consider three aspects to explain this behavior. First, the gradual increase of V<sub>TH</sub> may be due to the induced electron trapping to the vicinity of trapping layer during P/E cycling test. Second, the stress induced electron traps generated in the tunnel oxide. The other reason is the presence of uncompensated charge due to mismatch between localized spatial distributions of the injected charges. But, we believe that the third reason is most dominant since it can successfully explain the erase characteristics in Fig. 2a. The Y<sub>2</sub>O<sub>3</sub> film as the charge trapping layer exhibits the potential to be incorporated into the future LTPS-TFT nonvolatile memory fabrication.

### Conclusion

In conclusion, we have fabricated the AOYOP TFT nonvolatile memory device using an  $Y_2O_3$  charge trapping layer. The XPS analysis indicates the formation of a thicker yttrium silicate layer. The AOYOP TFT memory device exhibited better electrical characteristics in terms of large memory window (2.5 V), long charge retention time ( $\sim$ 15% charge loss at ten years), and good endurance (up to  $10^5$  P/E cycles) with no memory window narrowing. The  $Y_2O_3$  thin film is a

promising charge trapping layer material for the fabrication of LTPS-TFT memory devices.

#### Acknowledgment

This work was supported by the National Science Council (NSC) of Taiwan under contract no. NSC-98-2221-E-182-056-MY3.

#### References

- 1. K. Yoneda, R. Yokoyama, and T. Yamada, Proc. Symp. VLSI Circuits, 85 (2001).

- 2. S. Jagar and P. K. Ko, IEEE Electron Device Lett., 21, 439 (2000).

10<sup>5</sup>

- 3. A. K. P. Kumar and J. K. O. Sin, in *IEDM Tech. Dig., Dec.*, 515 (1997)

- 4. F. Hayashi, H. Ohkubo, T. Takahashi, S. Horiba, K. Node, T. Uchida, T. Shimizu, N. Sugawara, and S. Kumashiro, *IEDM Tech. Dig.*, 283 (1996).

- H. J. Cho, F. Nemati, P. B. Griffin, and J. D. Plummer, Proc. VLSI Symp. Tech. Dig., 38 (1998).

- S. C. Chen, T. C. Chang, P. T. Liu, Y. C. Wu, J. Y. Chin, P. H. Yeh, L. W. Feng, S. M. Sze, C. Y. Chang, and C. H. Lien, *Appl. Phys. Lett.*, 91, 193103 (2007).

- 7. J. H. Kim and J. B. Choi, *IEEE Trans. Electron Devices*, **51**, 2048 (2004)

- S. C. Chen, T. C. Chang, P. T. Liu, Y. C. Wu, P. H. Yeh, C. F. Weng, S. M. Sze, C. Y. Chang, and C. H. Lien, *Appl. Phys. Lett.*, 90, 122111 (2007).

- P. Xuan, M. She, B. Harteneck, A. Liddle, J. Bokor, and T. J. King, *IEDM Tech. Dig.*, 609 (2003).

- T. Sugizaki, M. Kobayashi, M. Ishidao, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, T. Nakanishi, and H. Tanaka, Proc. VLSI Symp. Tech. Dig., 27 (2003).

- T. S. Chen, K. H. Wu, H. Chung, and C. H. Kao, *IEEE Electron Device Lett.*, 25, 205 (2002).

- Y. H. Lin, C. H. Chien, T. H. Chou, T. S. Chao, and T. F. Lei, *IEEE Trans. Electron Devices*, 54, 531 (2007).

- 13. T. M. Pan and W. W. Yeh, *Appl. Phys. Lett.*, **92**, 173506 (2008).

- 14. T. M. Pan and W. W. Yeh, Electrochem. Solid-State Lett., 11, G37 (2008).

- M. H. Cho, D. H. Ko, K. Jeong, S. W. Whangbo, C. N. Whang, S. C. Choi, and S. J. Cho, J. Appl. Phys., 85, 2909 (1999).

- 16. T. M. Pan and C. J. Chang, Semiconduct. Sci. Techn., 26, 075004 (2011).

- Y. Uwamino, Y. Ishizuka, and H. Yamatera, J. Electron Spectrosc. Relat. Phenom., 34, 67 (1984).