## Temperature-dependent characteristics of junctionless bulk transistor

Ming-Hung Han, Hung-Bin Chen, Shiang-Shiou Yen, Chi-Shen Shao, and Chun-Yen Chang

Citation: Applied Physics Letters **103**, 133503 (2013); doi: 10.1063/1.4821747

View online: http://dx.doi.org/10.1063/1.4821747

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/103/13?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Experimental confirmation of temperature dependent negative capacitance in ferroelectric field effect transistor Appl. Phys. Lett. **100**, 163504 (2012); 10.1063/1.4704179

Temperature effect on electrical characteristics of negative capacitance ferroelectric field-effect transistors Appl. Phys. Lett. **100**, 083508 (2012); 10.1063/1.3688046

Analysis of hysteresis behavior of pentacene field effect transistor characteristics with capacitance-voltage and optical second harmonic generation measurements

J. Appl. Phys. 101, 094505 (2007); 10.1063/1.2720092

Room-temperature oxide field-effect transistor with buried channel

Appl. Phys. Lett. 76, 3632 (2000); 10.1063/1.126730

Spin-dependent capacitance of silicon field-effect transistors

Appl. Phys. Lett. 76, 1467 (2000); 10.1063/1.126066

## Temperature-dependent characteristics of junctionless bulk transistor

Ming-Hung Han, Hung-Bin Chen, Shiang-Shiou Yen, Chi-Shen Shao, and Chun-Yen Chang<sup>a)</sup>

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

(Received 2 July 2013; accepted 4 September 2013; published online 23 September 2013)

The temperature-dependent performance, including drain current  $(I_d)$  and gate capacitance  $(C_{gg})$  of multi-gate junctionless (JL) bulk transistor for temperature (T) ranging from  $150\,K$  to  $500\,K$ , was investigated using 3D thermodynamic quantum-corrected device simulation. The combination effect of impurity scattering and phonon scattering is observed owing to the different temperature-dependent of mobility at low and high temperature. Since the  $C_{gg}$  of the JL device consists of a series combination of oxide capacitance  $(C_{ox})$  and semiconductor channel capacitance  $(C_S)$  due to bulk conduction of the current, the  $C_{gg}$  at on-state  $(V_g=1\,V)$  shows much sensitive to the temperature than a conventional inversion-mode transistor.

© 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4821747]

Silicon-based devices are being continuously scaled down to increase density and speed. Short channel metaloxide-semiconductor field-effect-transistors (MOSFET) face various challenges, such as leakage currents and the shortchannel effect (SCE) because gate controllability declines over the channel. 1-3 SCE and drain-induced barrier lowering (DIBL), which cause source and drain junctions to be highly confined, are challenges to doping techniques and thermal budget. The ultra-shallow junction is indispensable in the design of devices as they shrink further.<sup>3</sup> Recently, the concept of the junctionless (JL) nanowire transistor, which contains a single doping species at the same level in the source, drain, and channel, has been investigated. 4-14 JL devices provide such advantages as improved SCE control, favorable subthreshold swing, and simpler fabrication processes. Additionally, a multi-gate JL transistor with a bulk substrate, which does not require an SOI wafer, has a lower cost and is fully compatible with the industry standard bulk CMOS process flow, has also been proposed. To ensure the stability of circuit with JL bulk transistor operating at extreme high/low temperature, it is important to evaluate the temperature characteristics of such device. This work studies the n-type multi-gate JL bulk transistor performance, including the oncurrent (I<sub>on</sub>), threshold voltage (V<sub>th</sub>), and the gate capacitance (Cgg) with respect to different temperature by using 3D thermodynamic quantum-corrected device simulation.

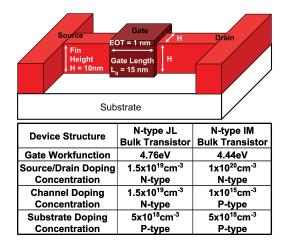

Figure 1 presents the structure of the simulated devices and the relevant parameters. The device has an HfO<sub>2</sub> high-k gate oxide with an equivalent oxide thickness (EOT) of 1 nm, a gate length (L<sub>g</sub>) of 15 nm, and a Fin height (H) of 10 nm. The gate material is TiN with a work-function of  $4.76\,\mathrm{eV},^{15}$  which the linear threshold voltage (V<sub>th</sub>) is adjusted to about 300 mV. The doping concentrations in the source/drain/channel are all set to  $1.5\times10^{19}\mathrm{cm}^{-3}$ . The substrate doping is opposite type with  $5\times10^{18}\mathrm{cm}^{-3}$ , which can be obtained easily by the typical well implantation process. To discuss the difference of physics between JL and

conventional inversion-mode (IM) MOSFET, the multi-gate IM bulk transistor with the same geometry are obtained and compared. The design of multi-gate IM bulk transistor is based on the prediction of International Technology Roadmap for Semiconductors (ITRS) 2011, in which the source/drain doping concentrations are constant with  $1\times10^{20}\,\mathrm{cm}^{-3}$ , the channel doping is opposite type with  $1\times10^{15}\,\mathrm{cm}^{-3}$ , and the well doping with opposite type  $5 \times 10^{18} \,\mathrm{cm}^{-3}$  is used, as listed in Fig. 1. To obtain accurate numerical results for a nanometer-scale device, the device is performed by 3D quantum-corrected simulation using the commercial tool, Synopsys Sentaurus Device. 16 In the quantum-corrected simulation, a density gradient model is used. The bandgap narrowing model, the band-to-band tunneling model, and Shockley-Read-Hall recombination with the doping dependent model are also considered. To analyze the performance in different temperature (T), the thermodynamic model is used. In this model, the relations of Poisson equation and electron/hole continuity equations are generalized to include the temperature gradient as a driving term,

$$\vec{J}_n = -nq\mu_n (\nabla \Phi_n + P_n \nabla T),$$

$$\vec{J}_p = -pq\mu_p (\nabla \Phi_p + P_p \nabla T),$$

(1)

where  $\Phi_n$  and  $\Phi_p$  are quasi-Fermi potentials and  $P_n$  and  $P_p$  are thermoelectric powers, for electron and hole, respectively. The mobility model used in device simulation is according to Mathiessen's rule, expressed as

$$\frac{1}{\mu} = \frac{D}{\mu_{surf\_aps}} + \frac{D}{\mu_{surf\_rs}} + \frac{1}{\mu_{bulk}} + \frac{1}{\mu_{imp}},$$

(2)

where  $D = \exp(x/l\_crit)$ , x is the distance from the interface, and  $l\_crit$  is a fitting parameter. The mobility consists of four parts: surface acoustic phonon scattering ( $\mu_{surf\_aps}$ ), surface roughness scattering ( $\mu_{surf\_rs}$ ), bulk phonon scattering ( $\mu_{bulk}$ ), and impurity scattering ( $\mu_{imp}$ ). The mobility change with impurity scattering is based on continuous doping concentration using Masetti model,

a) Author to whom correspondence should be addressed. Electronic mail: cyc@mail.nctu.edu.tw. Tel.: 886-3-5712121 Ext. 59318.

FIG. 1. The device structure and parameters of simulated n-type multi-gate junctionless (JL) bulk and inversion-mode (IM) bulk transistors.

$$\mu_{imp} = \mu_{\min 1} \exp\left(-\frac{P_c}{N_{A,0} + N_{D,0}}\right) + \frac{\mu_{const} - \mu_{\min 2}}{1 + ((N_{A,0} + N_{D,0})/C_r)^{\alpha}} - \frac{\mu_1}{1 + (C_s/(N_{A,0} + N_{D,0}))^{\beta}},$$

(3)

where  $\mu_{\min 1}$ ,  $\mu_{\min 2}$ ,  $\mu_1$ ,  $P_c$ ,  $C_r$ ,  $C_s$ ,  $\alpha$ , and  $\beta$  are accessible parameters. Additionally, the incomplete ionization is also considered to accurately obtain the device performance at low temperature, the ionized impurity atoms are given by

$$N_D = \frac{N_{D,0}}{1 + g_D \exp(\frac{E_{F,n} - E_D}{kT})}, \quad N_A = \frac{N_{A,0}}{1 + g_A \exp(\frac{E_A - E_{F,p}}{kT})}, \quad (4)$$

where  $N_{D,0}$  and  $N_{A,0}$  are the substitutional donor and acceptor concentrations,  $g_D$  and  $g_A$  are the degeneracy factors for the impurity levels, and  $E_D$  and  $E_A$  are the ionization energies. The details of these models and their parameters are described in Ref. 16.

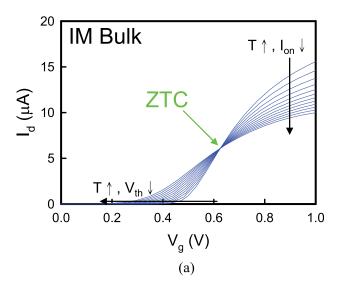

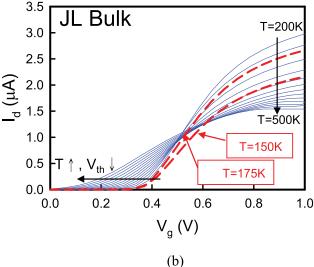

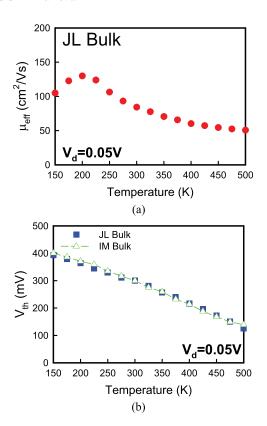

Figure 2 plots the drain current (I<sub>d</sub>) as a function of gate voltage (V<sub>g</sub>) at drain voltage (V<sub>d</sub>) 0.05 V for temperature (T) ranging from 150 K to 500 K in IM and JL bulk transistors. In IM device, the V<sub>th</sub> decreases and the off-current increases as T are increased. The on-current  $(I_{on}, at V_g = 1 V)$ decreases as the T increases due to mobility degradation by severe phonon scattering at high temperature. The decrease of V<sub>th</sub> with temperature tends to increase I<sub>d</sub>, and the reduction of mobility with temperature tends to decrease I<sub>d</sub>, there exists a  $V_g$  which compensate these effects, called the zero-temperature-coefficient (ZTC) point.  $^{11-14,17,18}$  In JL bulk transistor, since the studied device is made on heavily doped bulk substrate, the results are different from the temperature dependency proposed in literature. 11-14 When T is larger than 200 K, as T increases, the I<sub>on</sub> decrease. The ZTC point is observed, which is similar to that in the IM device. However, if we compare the  $I_{d}$ - $V_{g}$  curves of T = 150 K,  $175\,K$ , and  $200\,K$ , the  $I_{on}$  monotonically increases with T, there is no ZTC point in this temperature range. To understand the reason of the results, the effective mobility ( $\mu_{eff}$ ) for different T is extracted, 19 and the extracted mobility is about 90 cm<sup>2</sup>/Vs at T = 300 K, which are confirmed with experimental mobility data, <sup>10</sup> as shown in Fig. 3(a). Usually, the value of mobility is dominated by the phonon scattering,

FIG. 2. The drain current ( $I_d$ ) as a function of gate bias at  $V_d\!=\!0.05\,V$  in (a) IM bulk transistor and (b) JL bulk transistor.

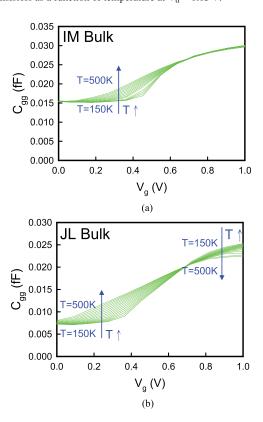

impurity scattering, and surface roughness scattering. 1-3 However, since the current in JL device exhibits bulk conduction, the third term is diminished. 4-9 Mobility varies with  $T^{-3/2}$  if it is limited by phonon scattering and  $T^{3/2}$  if it is limited by impurity scattering. In Fig. 3(a), the combined effect of impurity scattering and phonon scattering is obviously observed owing to the heavily doped channel in the proposed JL bulk transistor, and the peak value of  $\mu_{\rm eff}$  is located at  $T = 200 \,\mathrm{K}$ . Since the sensitivity of  $V_{th}$  (defined as the gate voltage at drain current  $I_d = W/L \times 10^{-7} A = 2 \times 10^{-7} A$ ) with T perform similarly in JL and IM bulk transistors, as displayed in Fig. 3(b), the origin of the absence of ZTC in JL bulk transistor is thus determined by the scattering phenomenon in the device. Figure 4 presents total gate capacitances  $(C_{gg})$  for various gate biases at  $V_d = 0.05 \, V$  in both IM and JL bulk transistors. In JL bulk transistor at low gate bias, the device operates at depletion region, the  $C_{gg}$  is dominated by the depletion capacitance (C<sub>dep</sub>). The increase of T reduces the surface potential ( $\phi_S$ ) and increases  $C_{dep}$ , this trend is similar to that in IM MOSFET.<sup>1,16,17</sup> On the other hand, when the device operate at high  $V_{\rm g}$ , the  $C_{\rm gg}$  of an IM device is usually determined by the gate oxide capacitance  $(C_{ox})$ ,

FIG. 3. (a) The effective mobility ( $\mu_{eff}$ ) of JL bulk transistor for different temperature at  $V_d = 0.05 \, V$ . (b) The threshold voltage ( $V_{th}$ ) of JL and IM bulk transistors as a function of temperature at  $V_d = 0.05 \, V$ .

FIG. 4. The total gate capacitance ( $C_{gg}$ ) as a function of gate bias at  $V_d = 0.05 \, V$  in (a) IM bulk transistor and (b) JL bulk transistor.

which shows less sensitive to the temperature. However, the  $C_{\rm gg}$  of the JL device consists of a series combination of  $C_{\rm ox}$  and semiconductor channel capacitance ( $C_{\rm S}$ ) because of the

bulk conduction of the current. Since the  $\phi_S$  of a JL device operate at on-state is near flat-band condition, in which the  $C_S$  can be described by  $^1$

$$C_S = \sqrt{qN_{ch}\frac{q}{kT}\varepsilon_S},\tag{5}$$

where q is the elementary charge, k is the Boltzmann constant,  $N_{ch}$  is the channel doping concentration, and  $\epsilon_S$  is the dielectric constant of silicon. As T increases, the  $C_S$  is decreased because it is inversely proportional to the square root of T, resulting in the decrease of the  $C_{gg}$ . Therefore, the  $C_{gg}$  at  $V_g \!=\! 1\,V$  shows higher sensitivity to T than an IM device. To reduce such unfavorable property, we have to diminish the  $C_S$  part in  $C_{gg}$ , the increase of  $N_{ch}$  or accumulation-mode operation  $^{10,11}$  are suggested.

This work studies the temperature-dependent performance of JL bulk transistor at the range of temperature from 150 K to 500 K. Owing to the high channel doping concentration is used in the proposed JL bulk transistor, the impurity scattering dominates at low temperature, thus the absence of ZTC point is observed. The  $C_{\rm gg}$  operate at onstate in JL bulk transistor is more sensitive to the temperature than an IM bulk transistor because of the  $C_{\rm S}$  at flat-band condition is a function of temperature.

<sup>1</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices* (Wiley-Interscience, New York, USA, 2007).

<sup>2</sup>C. Hu, Dig. Tech. Pap. - Symp. VLSI Technol. **2004**, 4.

<sup>3</sup>T. Skotnicki, J. A. Hutchby, T.-J. King, H.-S. P. Wong, and F. Boeuf, IEEE Circuits Devices Mag. **21**, 16 (2005).

<sup>4</sup>J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. 5, 225 (2010).

<sup>5</sup>R. Rios, A. Cappellani, M. Armstrong, A. Budrevich, H. Gomez, R. Pai, N. Rahhal-orabi, and K. Kuhn, IEEE Electron Device Lett. **32**, 1170 (2011).

<sup>6</sup>H.-C. Lin, C.-I. Lin, and T.-Y. Huang, IEEE Electron Device Lett. **33**, 53 (2012).

<sup>7</sup>S. Migita, Y. Morita, M. Masahara, and H. Ota, IEDM Symp. Tech. Dig. 2012, 191.

<sup>8</sup>R. Yu, S. Das, I. Ferain, P. Razavi, M. Shayesteh, A. Kranti, R. Duffy, and J. P. Colinge, IEEE Trans. Electron Device **59**, 2308 (2012).

<sup>9</sup>S. Cho, K. R. Kim, B.-G. Park, and I. M. Kang, IEEE Trans. Electron Device 58, 1388 (2011).

<sup>10</sup>K.-I. Goto, T.-H. Yu, J. Wu, C. H. Diaz, and J. P. Colinge, Appl. Phys. Lett. **101**, 073503 (2012).

<sup>11</sup>C.-W. Lee, A. Borne, I. Ferain, A. Afzalian, R. Yan, N. D. Akhavan, P. Razavi, and J.-P. Colinge, IEEE Trans. Electron Device 57, 620 (2010).

<sup>12</sup>M. de Souza, M. A. Pavanello, R. D. Trevisoli, R. T. Doria, and J.-P. Colinge, IEEE Electron Device Lett. 32, 1322 (2011).

<sup>13</sup>R. D. Trevisoli, R. T. Doria, M. de Souza, S. Das, I. Ferain, and M. A. Pavanello, Appl. Phys. Lett. **101**, 062101 (2012).

<sup>14</sup>D.-Y. Jeon, S. J. Park, M. Mouis, S. Barraud, and G.-T. Kim, Solid-State Electron. 80, 135 (2013).

<sup>15</sup>H.-C. Wen, S. C. Song, C. S. Park, C. Burham, G. Bersuker, K. Choi, M. A. Q. Lopez, B. S. Ju, H. N. Alshareef, H. Niimi, H. B. Park, P. S. Lysaght, P. Majhi, B. H. Lee, and R. Jammy, Dig. Tech. Pap. - Symp. VLSI Technol. 2007, 160.

<sup>16</sup>Walker, F. W. Jeffrey, A. Gilbert, and H. Karin, *User's Manual for Synopsys Sentaurus Device*, Ottawa, ON, Canada, 2010.

<sup>17</sup>F. H. Gaensslen, V. L. Rideout, E. J. Walker, and J. J. Walker, IEEE Trans. Electron Device 24, 218 (1977).

<sup>18</sup>S.-H. Hong, G.-B. Choi, R.-H. Baek, H.-S. Kang, S.-W. Jung, and Y.-H. Jeong, IEEE Electron Device Lett. 29, 775 (2008).

<sup>19</sup>J. He, X. Zhang, Y. Wang, and R. Huang, IEEE Electron Device Lett. 22, 597 (2001).