## High voltage characteristics of junctionless poly-silicon thin film transistors

Ya-Chi Cheng, Yung-Chun Wu, Hung-Bin Chen, Ming-Hung Han, Nan-Heng Lu, Jun-Ji Su, and Chun-Yen Chang

Citation: Applied Physics Letters 103, 123510 (2013); doi: 10.1063/1.4821856

View online: http://dx.doi.org/10.1063/1.4821856

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/103/12?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Origin of hysteresis in current-voltage characteristics of polycrystalline silicon thin-film transistors J. Appl. Phys. **105**, 054502 (2009); 10.1063/1.3086271

o. Appl. 1 hys. 100, 004002 (2005), 10.1005/1.30002/1

"Hump" characteristics and edge effects in polysilicon thin film transistors

J. Appl. Phys. 104, 124511 (2008); 10.1063/1.3050323

Effects of high pressure annealing on the characteristics of solid phase crystallization poly-Si thin-film transistors

J. Appl. Phys. 103, 044508 (2008); 10.1063/1.2885345

Electrode interdependence and hole capacitance in capacitance—voltage characteristics of hydrogenated amorphous silicon thin-film transistor

J. Appl. Phys. 83, 8051 (1998); 10.1063/1.367898

Polycrystalline silicon thin film transistor incorporating a semi-insulating field plate for high voltage circuitry on glass

Appl. Phys. Lett. 71, 2002 (1997); 10.1063/1.119768

## High voltage characteristics of junctionless poly-silicon thin film transistors

Ya-Chi Cheng, 1 Yung-Chun Wu, 1,a) Hung-Bin Chen, 2 Ming-Hung Han, 2 Nan-Heng Lu, 1 Jun-Ji Su, <sup>1</sup> and Chun-Yen Chang<sup>2</sup> <sup>1</sup>Department of Engineering and System Science, National Tsing Hua University, 101, Section 2,

Kuang Fu Road, Hsinchu 300, Taiwan

(Received 15 July 2013; accepted 5 September 2013; published online 20 September 2013)

The breakdown voltage (VBD) and breakdown mechanism of junctionless (JL) poly-Si thin film transistor (TFT) were compared to the conventional inversion-mode (IM) TFT using fabricated devices and 3D quantum-corrected hydrodynamic transport device simulation. The simulated results are correspondent with experimental ones. The analyses of electric field distributions in on-state show that the channel of JL devices can equally share the voltage like a resistor, because there are no junctions formed between channel and source/drain. The JL TFT shows excellent breakdown characteristics; the off-state  $V_{BD}$  of 53.4 V is several times larger than  $V_{BD}$  of 9.5 V in IM TFT with same device size. JL devices have large potential for high voltage power metal-oxide-semiconductor devices and circuit applications. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4821856]

The scaling of the channel lengths in conventional metal-oxide-semiconductor (MOS) field-effect-transistors (FET) shrink to the order of nanometers, several critical challenges, such as the need to reduce short-channel effect (SCE), to deliver a higher on-current, to reduce power consumption, and to eliminate intrinsic parameter fluctuations, must be addressed. 1-4 Numerous approaches for addressing these issues have been introduced in the past ten years. These include the use of high-k/metal-gate technology to suppress the direct tunneling current in gate oxides; to enhance mobility using strain, and to develop multi-gate structure such as FinFET and nanowire (NW) structures to reduce SCE.<sup>5,6</sup> Recently, the concept of the junctionless (JL) nanowire transistor, which contains a single doping species at the same level in its source, drain, and channel, has been investigated. 7-12 The junctionless device is basically a gated resistor, in which the advantages of junctionless devices include (1) avoidance of the use of an ultra shallow source/ drain junction, which greatly simplifies the process flow; (2) low thermal budgets owing to implant activation anneal after gate stack formation is eliminated, and (3) the current transport is in the bulk of the semiconductor, which reduces the impact of imperfect semiconductor/insulator interfaces. However, most of studies have focused on the device design and performance estimation of JL transistors at low voltage for digital circuit application, but few have addressed the breakdown mechanism and breakdown voltage (VBD) of such devices for power device and circuit application. In this work, the comparative study on V<sub>BD</sub> between JL thin film transistor (TFT) to conventional inversion-mode (IM) TFT by using experimental measurement and 3D quantumcorrected hydrodynamic transport device simulation is addressed. The physical and electrical properties at high voltage of the JL and IM TFTs are presented.

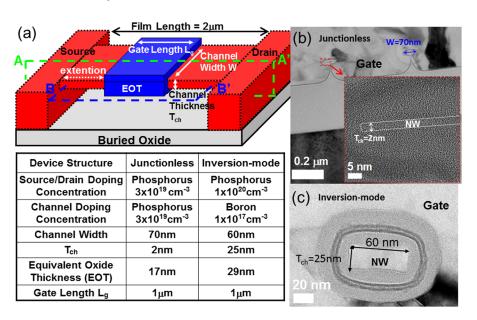

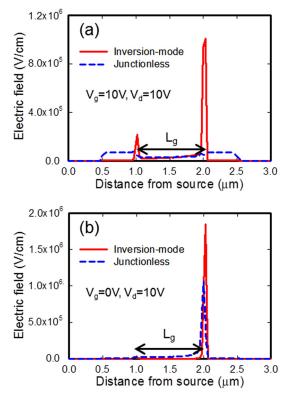

Figure 1(a) presents the schematic of single NW in the simulated device structure and relevant parameters. The parameters setting are fitted as the fabricated devices, in which the film length ( $L_f$ ) and gate length ( $L_g$ ) are  $2\mu m$  and  $1\mu m$ , respectively. The doping concentrations in the source/drain/ channel of JL TFT are set to  $2 \times 10^{19} \, \text{cm}^{-3}$ . In IM TFT, the source/drain doping concentrations are  $1 \times 10^{20} \,\mathrm{cm}^{-3}$ , and the channel doping is opposite type with  $1 \times 10^{17} \, \text{cm}^{-3}$  concentrations. The gate material is poly-silicon with different doping concentration to tune an appropriate device threshold voltage (V<sub>th</sub>) for JL and IM TFTs. The source/drain extension is used to prevent misalignment of e-beam lithography for gate patterning. Figs. 1(b) and 1(c) show the crosssectional transmission electron microscopic (TEM) images of channel region for JL and IM TFTs, respectively. To obtain accurate numerical results for a nanometer-scale device at high voltage bias, the device is simulated by solving 3D quantum-corrected hydrodynamic transport equations using the commercial tool, Synopsys Sentaurus Device. <sup>13</sup> In quantum-corrected equations, a density gradient model is used in the simulation. Additionally, the bandgap narrowing model, the band-to-band tunneling model, and Shockley-Read-Hall recombination with the doping-dependent model are also considered. The detailed process flows in our fabricated devices are investigated in Refs. 14 and 15. Figure 2 shows transfer I<sub>d</sub>-V<sub>g</sub> characteristics of experimental and simulation results in JL and IM TFTs. The experimental subthreshold swing is 61 mV/dec for JL TFTs and is 304 mV/dec for IM TFTs. The experimental V<sub>th</sub>, which is defined as the gate voltage at  $I_d = 1 \times 10^{-10}$  A for JL TFTs and at  $I_d = 1 \times 10^{-8}$  A for IM TFTs, are 0.2 V and 0.3 V, respectively. The simulated data well fit the experimental data. Figure 3 plots electric field distributions along the line of interaction between AA' and BB' plane (indicated in Fig. 1) for JL and IM TFTs at on-state  $(V_g = 10 \text{ V},$  $V_d = 10 \text{ V}$ ) and off-state ( $V_g = 0 \text{ V}$ ,  $V_d = 10 \text{ V}$ ). Because the JL device is a gated resistor, there are no junctions formed at source and drain sides; the potential trends to equally shares

<sup>&</sup>lt;sup>2</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic mail: ycwu@ess.nthu.edu.tw. Tel.: +886-3-5715131 ext. 34287. Fax: +886-3-5720724.

FIG. 1. The simulated device structure and parameters of simulated JL TFT and IM TFT. The experimental cross-sectional TEM images of (b) JL TFT and (c) IM TFT in the gate width direction

in whole film like a resistor. However, the situation only happens at turned-on state or floating-gate voltage state, in which the current flows from source to drain through the whole cross-section of silicon film and the behavior of JL devices indeed acts as a resistor. In Fig. 3(a), the electric field of IM devices concentrates at the two side edges of the gate, where are the depletion region between channel and source/drain p-n junction. In contrast, the electric field in JL devices is averagely distributed like a resistor, thus, the maximum electric field in JL device is significantly smaller than

10<sup>-7</sup> (a) 10-8 Drain Current I<sub>d</sub> (A) Junctionless 10-9 d=0.5V Experiment 10-1 Simulation 10<sup>-1</sup> 10-1 10<sup>-1</sup> вох 10-1 10-1 T<sub>ch</sub>=2nm 10-16 0 2 5 -3 -2 1 3 4 Gate Voltage V<sub>q</sub>(V) 10-4 (b) 10-5 10-6 الا (A) Drain Current Inversion-mode V<sub>d</sub>=0.5V 10-7 Experiment L<sub>α</sub>=1μm 10-8 Simulation 10-9 10-1 10-10-1

FIG. 2. Experimental and simulated  $I_d$ – $V_g$  curves for (a) JL and (b) IM TFTs. The inset shows simulated devices with  $L_g$  = 1  $\mu$ m.

2

Gate Voltage V<sub>q</sub>(V)

0

T<sub>ch</sub>=25nm

5

10<sup>-</sup>

10-1

-3

-2

in IM device. In addition, Fig. 3(a) also indicates that silicon film can be treated as the series of three resistors (source extension, channel, and drain extension regions). The resistance of the channel differs from that of source/drain extension regions because the carriers in the channel are controlled by the gate; therefore, the electric field is different between channel and source/drain extension regions. On the other hand, when the JL device turns off, the channel region is depleted and the increase of the drain voltage produces the larger depletion region than with zero bias, the behavior is the same as in IM devices. However, since the doping concentration gradient between channel and drain in JL devices

FIG. 3. The electric field distribution along the line of interaction between AA' and BB' plane in the middle of channel for JL and IM TFTs at (a) on-state ( $V_g = 10 \, V$ ,  $V_d = 10 \, V$ ) and (b) off-state ( $V_g = 0 \, V$ ,  $V_d = 10 \, V$ ).

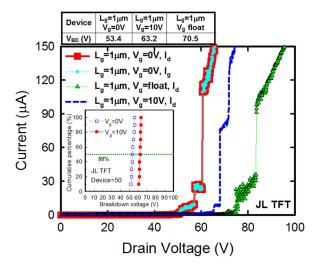

FIG. 4. The  $I_d\text{-}V_d$  curves comparison for JL and IM TFTs at  $V_g=0\,V$ . The  $V_{BD}$  extracted form the curves are listed in the figure. The inset shows cumulative distributions of  $V_{BD}$  for JL and IM TFTs.

is intrinsically smaller than in IM devices, the maximum electric field is still smaller, as displayed in Fig. 3(b). Therefore, a high  $V_{\rm BD}$  in JL device can be expected.

To confirm the simulation results, Fig. 4 compares the breakdown voltages of IM TFT and JL TFT with same size in the off-state ( $V_g = 0 \text{ V}$ ). The  $V_{BD}$ , which is extracted from  $I_d$ - $V_d$  curve at  $I_d = 10\mu A$  of device with  $L_g = 1\mu m$  and  $V_g = 0 \text{ V}$ , is 53.4 V for JL TFT and 9.5 V for IM TFT. The measurement V<sub>BD</sub> of JL devices show much higher than that of IM devices owing to the reduced electric field in JL TFT, as simulated results in Fig. 3(b). The cumulative distributions of  $V_{BD}$  at  $V_g = 0 V$  for 50 devices are shown in the inset of Fig. 4. Fig. 5 plots the measured I<sub>d</sub>-V<sub>d</sub> curves for different gate voltage bias condition (on-state and off-state) of fabricated JL devices. The device breakdowns observed in fabricated devices are oxide breakdown, which is confirmed by the measured gate current equal to drain current when device breakdown. When the drain voltage increases, the potential in the channel also increases, the increased potential enhance the potential difference between channel and gate, resulting in the breakdown of the gate oxide. If the device is turned on  $(V_g = 10 \text{ V})$ , the channel is like a resistor and the electric field is uniformly distributed to alleviate impact-ionization rate. The V<sub>BD</sub> in on-state is thus improved than that in off-state. In addition, If the gate electrode is floated, the vertical (gate to channel direction) electric field is also reduced, resulting in the largest V<sub>BD</sub>. The inset of Fig. 5 shows cumulative distributions of  $V_{BD}$  for  $V_g = 0 V$ and  $V_g = 10 \text{ V}$ . The measurement results prove that the  $V_{BD}$ of the junction avalanche breakdown in JL TFT is very large, which is not seen before the oxide breakdown in our device.

We have studied the high voltage electrical and physical characteristics using the experimental measurement and 3D quantum-corrected hydrodynamic transport device simulations. In the on-state or floating-gate state, the electric field distributions along source to drain indicate that the potential in the film of JL TFT is equally distributed due to resistor-

FIG. 5. The measured currents as a function of drain voltage for different bias conditions in JL TFTs. The  $V_{\rm BD}$  is extracted from the curves, as listed in the figure. The inset shows cumulative distributions of  $V_{\rm BD}$  for different bias conditions.

like structure of JL devices. In the off-state, the doping concentration gradient between channel and drain in JL devices is intrinsically smaller than in IM devices, the maximum electric field is thus still smaller. Therefore, the breakdown voltage in JL TFT is several times larger than IM TFT with same device size. This investigation explores its potential in JL TFTs for high voltage power MOS devices, system-on-panel and 3D stacked applications.

<sup>1</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices* (Wiley-Interscience, New Jersey, 2007).

<sup>2</sup>C. Hu, Dig. Tech. Pap. - Symp. VLSI Technol. 2004, 4.

<sup>3</sup>T. Skotnicki, J. A. Hutchby, T.-J. King, H. -S. P. Wong, and F. Boeuf, IEEE Circuits Devices Mag. **21**, 16 (2005).

<sup>4</sup>G. Roy, A. R. Brown, F. Adamu-Lema, S. Roy, and A. Asenov, IEEE Trans. Electron Devices **53**, 3063 (2006).

M. Wallace, and J. M. Anthony, J. Appl. Phys. 89, 5243 (2001).

D. Hisamoto, W.-C. Lee, J. Kedzierski, H. Takeuchi, K. Asano, C. Kuo, E. Anderson, T.-J. King, J. Bokor, and C. Hu, IEEE Trans. Electron Devices 47, 2320 (2000).

<sup>7</sup>C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J. P. Colinge, Appl. Phys. Lett. **94**, 053511 (2009).

<sup>8</sup>J.-P. Colinge, C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, P. Razavi, B. O'Neill, A. Blake, M. White, A.-M. Kelleher, B. McCarthy, and R. Murphy, Nat. Nanotechnol. 5, 225 (2010).

<sup>9</sup>J. P. Colinge, C.-W. Lee, I. Ferain, N. D. Akhavan, R. Yan, R. Razavi, R. Yu, A. N. Nazarov, and R. T. Doria, Appl. Phys. Lett. **96**, 073510 (2010).

<sup>10</sup>H.-C. Lin, C.-I. Lin, and T.-Y. Huang, IEEE Electron Device Lett. 33, 53 (2012).

<sup>11</sup>C.-J. Su, T.-I. Tsai, Y.-L. Liou, Z.-M. Lin, H.-C. Lin, and T.-S. Chao, IEEE Electron Device Lett. 32, 521 (2011).

<sup>12</sup>R. Rios, A. Cappellani, M. Armstrong, A. Budrevich, H. Gomez, R. Pai, N. Rahhal-orabi, and K. Kuhn, IEEE Electron Device Lett. 32, 1170 (2011).

<sup>13</sup>User's Manual for Synopsys Sentaurus Device.

<sup>14</sup>M.-F. Hung, Y.-C. Wu, and Z.-Y. Tang, Appl. Phys. Lett. **98**, 162108 (2011).

<sup>15</sup>H. B. Chen, Y. C. Wu, C. Y. Chang, M. H. Han, N. H. Lu, and Y. C. Cheng, Dig. Tech. Pap. - Symp. VLSI Technol. 2013, 232, available at <a href="http://orz.tw/GGNS4">http://orz.tw/GGNS4</a>.