# The TEOS CVD Oxide Deposited on Phosphorus *In Situ* Doped Polysilicon with Rapid Thermal Annealing

Chyuan Haur Kao, Chao Sung Lai, and Chung Len Lee, Senior Member, IEEE

Abstract— A TEOS oxide deposited on the phosphorus in situ doped polysilicon annealed with RTA is shown to have good electrical characteristics such as a high breakdown field (>12 MV/cm), especially for the positive bias, and a large Qbd (26 Coul/cm<sup>2</sup>). The improvement is believed to be due to the relatively smooth surface of the in situ doped polysilicon and the reduction of the trapping density by RTA.

### I. INTRODUCTION

POR nonvolatile memories such as EPROM, EEPROM, and Flash, thermal oxides grown on n<sup>+</sup> polysilicon (polyoxides) have been used as the interdielectrics. However, polyoxides have drawbacks of a lower dielectric strength and a higher leakage current than oxides grown on single crystal silicon due to asperities (surface roughness) caused by the enhanced oxidation at grain boundaries. Also, the characteristics of polyoxides are heavily dependent on the structure and morphology of the predeposited-polysilicon film, which in turn are affected by the process parameters [1], [2]. ONO polyoxides are thus used for the inter-polyoxides and show good charactristics [3], [4]. However, due to the intrinsic multiple layer structure, they face a rather difficult scaling down problem [4].

In this letter, we report a TEOS CVD oxide to be a possible candidate for the inter-polyoxide. The oxide is deposited on the phosphorus *in situ* doped polysilicon which has a relatively flat and smooth surface [5], [6], and the CVD deposition makes the grain boundaries of the bottom polysilicon not propagate into the deposited polyoxide film as that which occurs in the thermal polyoxides [6]. The prepared TEOS CVD polyoxide has desirable characteristics such as an asymmetric J-E characteristic and a large charge-to-breakdown (Qbd ~26 Coul/cm<sup>2</sup>).

# II. EXPERIMENTS

P-type wafers were first thermally oxidized to have an oxide of a thickness of 100 nm, then, a 300 nm phosphorus *in situ* doped polysilicon film (poly1) was deposited at 580 °C with

Manuscript received January 27, 1997; revised June 19, 1997. This work was supported by the National Science Council of R.O.C. through Research Contract NSC86-2215-E-009-022 and the National Nano Device Laboratory of R.O.C.

The authors are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(97)08103-2.

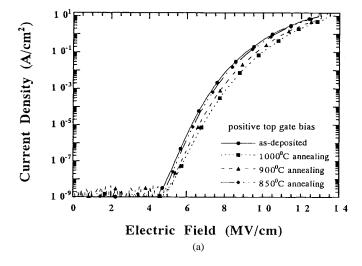

Fig. 1. The J-E characteristics of the deposited TEOS oxides annealed at different temperatures (850, 900, and 1000 °C) for the top gate (a) positive bias and (b) negative bias.

the sheet resistance to be 44  $\Omega$ /cm. A LPCVD TEOS oxide of 13 nm was then deposited at 700 °C and rapidly annealed in N<sub>2</sub> ambient at temperatures of 850, 900, and 1000 °C for 30 s. A second polysilicon film (poly2) of 300 nm, also *in situ* doped with phosphorus, was deposited at 580 °C. After poly2 was patterned, another oxide of 100 nm was grown and contact holes were opened and metallized to form the capacitor

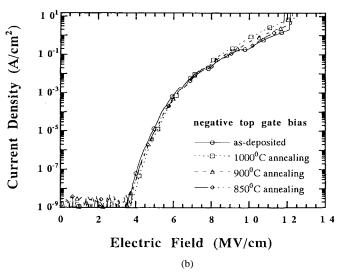

Fig. 2. The AFM (atomic force microscope) images of the surface of the polysilicon films doped with (a) phosphorus in situ (580 °C) and (b) POCl3 (950 °C).

structure. Finally, all devices were sintered at 350  $^{\circ}$ C for 40 min in the  $N_2$  gas.

### III. RESULTS AND DISCUSSION

Fig. 1(a) and (b) shows the positive (gate positive) and the negative J-E characteristics of oxides annealed at temperatures of 850, 900, and 1000 °C, respectively. It can be seen that both J-E characteristics had breakdown fields over 12 MV/cm and the positive J-E characteristics had lower currents and even higher breakdown fields. These high breakdown fields are due to smooth polysilicon1/polyoxide and polyoxide/polysilicon2

interfaces [7], [8]. This can be seen from Fig. 2(a) which shows the AFM (atomic force microscope) image of the surface of the phosphorus *in situ* doped polysilicon, which can be compared with that of the same polysilicon but doped with POCl3 as shown in Fig. 2(b). We can see that Fig. 2(a) has a much smoother surface. In Fig. 1(a), it is also seen that as the annealing temperature was increased, the current and the breakdown field were improved for the positive J-E characteristics.

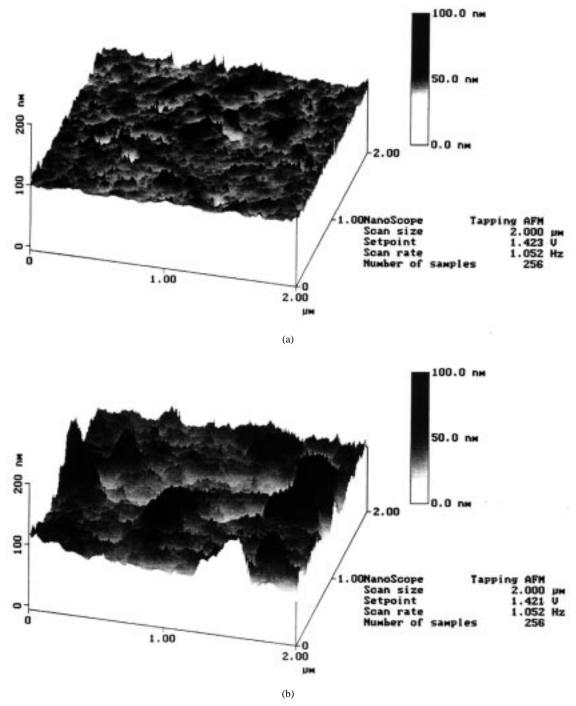

Fig. 3 shows the gate voltage change for samples under a 10  $\mu A/cm^2$  constant current stress. The electron trapping

Fig. 3. The incremental voltage shifts of deposited TEOS oxides annealed at different temperatures under positive and negative constant current stress of  $10~\mu\text{A/cm}^2$ . The gate area was  $5~\times~10^{-4}~\text{cm}^2$ .

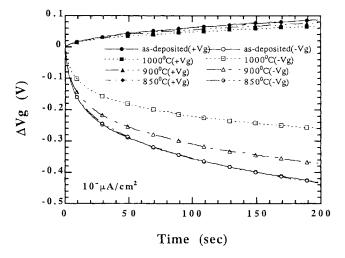

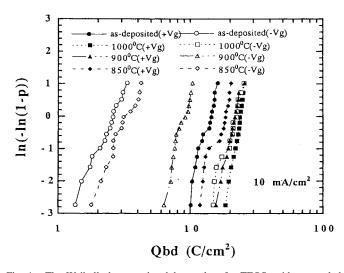

Fig. 4. The Weibull charge-to-breakdown plots for TEOS oxides annealed at different temperatures under positive and negative stress, respectively. The stress condition was 10  $\,$  mA/cm $^2$  and the gate area was 5  $\times$  10  $^{-4}$  cm $^2$ .

rate under the -Vg bias was larger than that under the +Vg bias. The annealing temperature had a remarkable effect on improving the trapping rate for the -Vg bias. Fig. 4 shows the

Weibull charge-to-breakdown (Qbd) plots for the above samples under the  $10~\mathrm{mA/cm^2}$  stress. All the +Vg stressed samples had higher Qbd's than the corresponding -Vg stressed samples, and the higher annealing temperature, the higher Qbd. The improvement was believed to be due to reducing electron trapping sites by RTA's. In addition, the plots also show that as the annealing temperature increased, the polarity asymmetry became smaller. The  $1000~^\circ\mathrm{C}$  annealed sample had the largest Qbd (+Vg:  $26~\mathrm{Coul/cm^2}$ ; -Vg:  $23~\mathrm{Coul/cm^2}$ ) while the smallest polarity asymmetry.

## IV. CONCLUSION

We conclude that the TEOS CVD oxide deposited on the phosphorus *in situ* doped polysilicon annealed with RTA is a very attractive inter-dielectric, which has a high breakdown field, low leakage current for the positive bias, and very large Qbd (26 Coul/cm<sup>2</sup>) than conventional thermally grown or CVD deposited dielectrics.

### REFERENCES

- L. Faraone, R. Vibronek, and J. Mc Ginn, "Characterization of thermally oxidized n<sup>+</sup> polycrystalline silicon," *IEEE Trans. Electron Devices*, vol. ED-32, p. 577, Mar. 1985.

- [2] L. Faraone, "Thermal SiO<sub>2</sub> films on n<sup>+</sup> polycrystalline silicon: Electrical conduction and breakdown," *IEEE Trans. Electron Devices*, vol. ED-33, p. 1785, Nov. 1986.

- [3] D. P. Shum, H. H. Tseng, Q. M. Paulson, K. M. Chang, and P. J. Tobin, "A highly robust process integration with scaled ONO interpoly dielectrics for embedded nonvolatile memory applications," *IEEE Trans. Electron. Devices*, vol. 42, p. 1376, July 1995.

[4] S. Mori, Y. Y. Araki, M. Sato, H. Meguro, H. Tsunoda, E. Kamiya,

- [4] S. Mori, Y. Y. Araki, M. Sato, H. Meguro, H. Tsunoda, E. Kamiya, K. Yoshikawa, N. Arai, and E. Sakagami, "Thickness scaling limitation factors of ONO intrpoly dielectric for nonvolatile memory devices," *IEEE Trans. Electron. Devices*, vol. 43, p. 47, Jan. 1996.

- [5] M. Sterheim, E. Kinsbron, J. Alspector, and P. Heimann, "Properties of thermal oxides grown on phosphorus in situ doped polysilicon," J. Electrochem. Soc., vol. 130, no. 8, p. 1735, Aug. 1983.

- Electrochem. Soc., vol. 130, no. 8, p. 1735, Aug. 1983.

[6] M. Hendriks and C. Mavero, "Phosphorus doped polysilicon for double poly structures," J. Electrochem. Soc., vol. 138, p. 1466, 1991.

- [7] J. H. Klootwijk, M. H. H. Weusthof, H. Van Kranenburg, P. H. Woerlee, and H. Wallinga, "Improvements of deposited interpolysilicon dielectric characteristics with RTP N<sub>2</sub>O-anneal," *IEEE Electron Device Lett.*, vol. 17, p. 358, 1996.

- [8] S. L. Wu, C. Y. Chen, T. Y. Lin, C. L. Lee, T. F. Lei, and M. S. Liang, "Investigation of the polarity asymmetry on the electrical characteristics of thin polyoxides grown on n<sup>+</sup> polysilicon," *IEEE Trans. Electron Devices*, vol. 44, p. 153, Jan. 1997.