Home Search Collections Journals About Contact us My IOPscience

Assessment of Thermal Impact on Performance of Metamorphic High-Electron-Mobility

Transistors on Polymer Substrates Using Flip-Chip-on-Board Technology

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2013 Appl. Phys. Express 6 126701

(http://iopscience.iop.org/1882-0786/6/12/126701)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 23:54

Please note that terms and conditions apply.

## Assessment of Thermal Impact on Performance of Metamorphic High-Electron-Mobility Transistors on Polymer Substrates Using Flip-Chip-on-Board Technology

Chin-Te Wang<sup>1</sup>, Heng-Tung Hsu<sup>2\*</sup>, Che-Yang Chiang<sup>2</sup>, Edward Yi Chang<sup>1</sup>, and Wee-Chin Lim<sup>1</sup>

Received October 10, 2013; accepted October 31, 2013; published online November 18, 2013

In this study, we have fabricated and characterized an In<sub>0.6</sub>Ga<sub>0.4</sub>As metamorphic high-electron-mobility transistor (mHEMT) device packaged using flip-chip-on-board (FCOB) technology. A low-cost polymer substrate was adopted as the carrier for cost-effective purposes. The impact of bonding temperature on the device performance was also experimentally investigated. While the DC performance was not as sensitive, serious degradation in RF performance was observed at high bonding temperature. Such degradation was mainly due to the thermal-mechanical stress resulting from the mismatch in the coefficient of thermal expansion (CTE) between the GaAs chip and the polymer substrate. Quantitative assessment was also performed through equivalent circuit extraction from *S*-parameter measurements.

he rapidly growing demands on the data bandwidth and transmission speed of modern wireless communication systems have pushed the operating frequencies to millimeter-wave range or beyond. <sup>1–3)</sup> Such trend has also accelerated the development of device fabrication as well as packaging technologies to meet the stringent requirements for high-frequency operations. On the device side, metamorphic high-electron-mobility transistor (mHEMT) technology with indium-rich channels has been attractive due to the very high electron mobility and saturation velocity of InGaAs materials. <sup>4–7)</sup>

The development of packaging configuration and interconnect technologies has become critical since both high performance and cost effectiveness are the main focuses of modern applications. Instead of the conventional wire-bonding technology, flip-chip interconnection is considered favorable at high frequencies due to its features of shorter interconnection length, better thermal management, better mechanical stability, and smaller packaging size.<sup>8–16)</sup> Additionally, the flip-chip-on-board (FCOB) technology is a very costeffective solution for high-frequency applications because it bypasses chip-level assembly, which makes it easier for further integration with other components in the system. 17–21) Therefore, such technology not only reduces RF loss but also saves material cost from the elimination of the chip level package. Table I lists the material properties of some conventional substrates for millimeter-wave applications. Clearly, the commercial RO 3210 organic substrate from Rogers Corporation™ is a good candidate due to its very low cost with comparable material properties at high frequencies. Giesler et al. and O'Malley et al. had successfully demonstrated the flip-chip structure on FR4 organic substrate by using 97Pb/ 3Sn solder bump interconnection and the reliability improvement of the flip-chip interconnect with encapsulation. 17,18) Hsu et al. demonstrated the flip-chip structure on the RO 3210 organic substrate with epoxy-based underfill to work up to 50 GHz and pass the 600-cycle thermal-cycling test. <sup>19)</sup> The characteristic of the flip-chip-packaged HEMT device on the RO 3210 organic substrate with epoxy-based underfill injection has been reported up to W band in our previous work.<sup>20)</sup> While previous research effort was devoted mostly to the electrical performance of the FCOB technology, the impact of the bonding temperature on the device performance after packaging has not been investigated.

**Table 1.** Material properties of the substrates commonly used for flip-chip packaging.

| Material  | Dielectric constant<br>(at 10 GHz) | Loss tangent (at 10 GHz) | CTE (ppm/K) | Cost in USD $(2'' \times 2'')$ |

|-----------|------------------------------------|--------------------------|-------------|--------------------------------|

| Si        | 11.9                               | 0.001                    | 2.5         | 2.3                            |

| GaAs      | 12.9                               | 0.0005                   | 5.4         | 88                             |

| $Al_2O_3$ | 9.8                                | 0.0002                   | 6.3         | 25                             |

| RO3210    | 10.2                               | 0.0027                   | 13          | 2.5                            |

In this study, a flip-chip-packaged 150 nm In<sub>0.6</sub>Ga<sub>0.4</sub>As mHEMT on low-cost RO 3210 polymer substrate using FCOB technology is demonstrated. We have characterized the packaged device under different bonding temperatures through the DC and RF measurements up to 110 GHz. Degradations in RF performance were observed due to the stress from the coefficient of thermal expansion (CTE) mismatch between the materials during the bonding process. Further assessment of the thermal effect during the bonding process was performed through equivalent circuit extraction of the solder bumps at different temperatures. Results revealed that minimum degradations in RF performance up to 100 GHz could be achieved with the appropriate bonding temperature.

We adopted the in-house-fabricated 150 nm  $In_{0.6}Ga_{0.4}As$  mHEMT as the primary device in this study. The HEMT structure was grown on a 3" semi-insulating GaAs substrate by molecular beam epitaxy (MBE). The high indium content in the  $In_xGa_{1-x}As$  channel layer will improve the RF performance of the device. A Pt-based buried gate was adopted to minimize the gate-to-channel distance without increasing the access resistance and, in the meantime, to suppress the short-channel effect. The fabrication process of the  $In_{0.6}$ - $Ga_{0.4}As$  mHMET device has been described in a previous publication.  $^{22}$ )

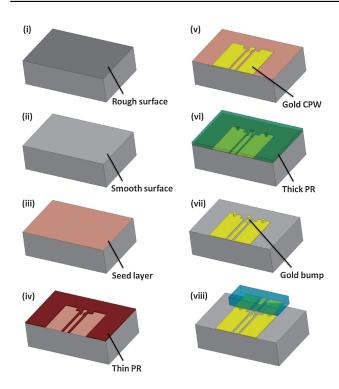

Figure 1 shows the in-house fabrication process of the FCOB structure on the RO 3210 polymer substrate. The commercial RO3210<sup>TM</sup> PCB of 0.635 mm thickness from Rogers Corporation was used as the substrate material. Compared with the conventional  $Al_2O_3$  substrate commonly used for the flip-chip process, the RO3210 substrate exhibits great competitiveness in terms of the very low cost. For both electrical and mechanical performance improvements, chemical mechanical polishing (CMP) was first applied to reduce the

<sup>&</sup>lt;sup>1</sup>Department of Material Science and Engineering, National Chiao-Tung University, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>2</sup> Department of Communications Engineering, Yuan Ze University, Chunli 320, Taiwan E-mail: htbeckhsu@saturn.yzu.edu.tw

Fig. 1. In-house fabrication of FCOB structure on RO 3210 polymer substrate.

Table II. Bonding conditions at high and low substrate bonding temperatures.

| Condition  | Chip temp. (°C) | Substrate temp. (°C) | Bonding force (g) | Duration (s) |

|------------|-----------------|----------------------|-------------------|--------------|

| High temp. | 200             | 200                  | 80                | 200          |

| Low temp.  | 200             | 100                  | 100               | 240          |

surface roughness of the polymer substrate. After the CMP process, the surface roughness of the polymer substrate was improved from 3 to less than 1  $\mu m$  by using a P-10 Surface Profiler. In the beginning of the RO 3210 substrate process, the Ti/Au seed layer was firstly evaporated on the RO 3210 substrate. The CPW transmission line of 3  $\mu m$  thickness was patterned by Au electroplating. To obtain good RF performance of the FCOB structure, the CPW transmission line with compensation design has been considered in Ref. 20. Then, the thick photoresist from TOK Company was patterned for the Au microbump electroplating. The height and diameter of the Au microbumps are 20 and 50  $\mu m$ , respectively. Finally, the mHEMT device was flip-chip packaged onto the RO 3210 polymer substrate by using an M9 flip-chip bonder.

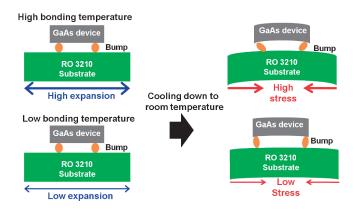

During the bonding process, both the device and substrate were heated before adhesion to establish a solid contact with the interconnection, and then cooled to room temperature. Thus, the existence of the mechanical stress due to the mismatch in CTE between the materials is unavoidable. To investigate the thermal impact on the device during the bonding process, two different flip-chip bonding conditions were applied as summarized in Table II. For the case of high bonding temperature, the optimized bonding force and bonding time were 80 g and 200 s, respectively. A higher bonding force of 100 g and a longer bonding time of 240 s

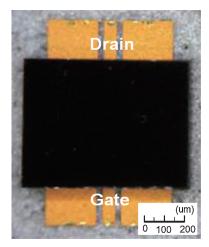

Fig. 2. Photograph of the device flip-chip bonded onto RO3210 substrate.

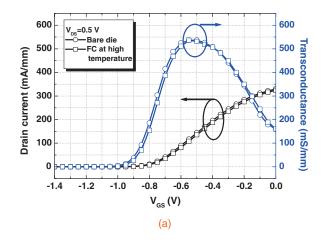

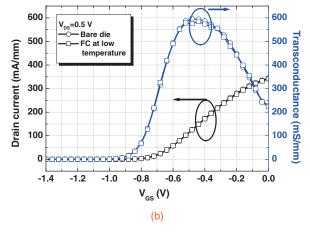

Fig. 3. Measured drain current and DC transconductance as functions of gate bias at  $V_{\rm DS} = 0.5 \, \rm V$  of the flip-chip-packaged device under different bonding conditions, (a) with high bonding temperature and (b) with low bonding temperature, with those of bare dies included for comparison.

were applied to maintain good connection between the Au bumps and Au pads in the case of low bonding temperature. Figure 2 shows the photograph of the device flip-chip bonded onto the RO3210 substrate.

Figures 3(a) and 3(b) show the measured drain current and DC transconductance as functions of gate bias at  $V_{\rm DS} = 0.5\,\rm V$  of the flip-chip-packaged device under different bonding conditions with those of bare dies included for com-

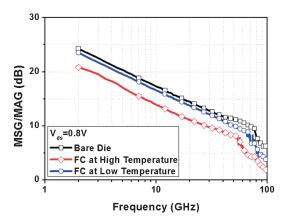

**Fig. 4.** Measured MSG/MAG as a function of frequency for the cases of bare die, flip-chip-packaged device with high bonding temperature, and flip-chip-packaged device with low bonding temperature.

parison. It is clear that the DC characteristics for both cases are identical to those of bare dies without any degradation. The RF performance was characterized from 2 to 110 GHz by using an HP 8510XF network analyzer with E7352 test heads calibrated by using a standard load-reflectionreflection-match method. Figure 4 plots the maximum stable gain/maximum available gain (MSG/MAG) as a function of frequency for the cases of bare die, flip-chip-packaged device with high bonding temperature, and flip-chip-packaged device with low bonding temperature. Note that the input and output terminations were set to  $50\,\Omega$  during the measurement. As is observed, a 5dB drop in the lowfrequency regime occurs for the case with high bonding temperature. In contrast, a very slight degradation of only 0.5 dB at 50 GHz is observed for the case of low bonding temperature. We believe that such degradation should be related to the CTE mismatch between RO 3210 (13 ppm/K) and GaAs (5.4 ppm/K). An intuitive interpretation is shown in Fig. 5. Apparently, the RO3210 substrate undergoes higher expansion during the heating process, leading to higher stress level once cooled to room temperature.

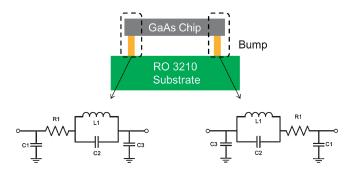

To further assess the mechanism causing the RF degradation, we patterned  $50 \Omega$  transmission lines on GaAs and flip-chip bonded onto the RO3210 substrate using exactly the same conditions listed in Table II. Procedures outlined in Ref. 23 were adopted to extract the equivalent circuit of the bump interconnection through S-parameter measurement. Figure 6 shows the corresponding equivalent circuit model of the bump interconnect. In the equivalent circuit model, C1 and C3 represent the discontinuity capacitances at the RO3210 substrate and the GaAs chip, respectively. R1, L1, and C2 represent the parasitics along the signal path. To determine the S-parameters of the bump interconnect, we first patterned  $50\,\Omega$  CPW transmission lines on GaAs substrate and measured the S-parameters. Then, the transmission line was flip-chip bonded onto RO3210 polymer substrate using the conditions outlined in Table II. Finally, the S-parameters of the complete structure were measured. The S-parameters of the overall structure in Fig. 6 can be obtained by cascading the individual S-matrices as

$$\begin{bmatrix} S^{\text{Total}} \end{bmatrix} = \begin{bmatrix} S_{11}^{\text{b}} & S_{12}^{\text{b}} \\ S_{12}^{\text{b}} & S_{22}^{\text{b}} \end{bmatrix} \begin{bmatrix} S^{\text{CPW}} \end{bmatrix} \begin{bmatrix} S_{22}^{\text{b}} & S_{12}^{\text{b}} \\ S_{12}^{\text{b}} & S_{11}^{\text{b}} \end{bmatrix}, \tag{1}$$

Fig. 5. Illustration of induced mechanical stress during bonding process with different bonding temperatures.

Fig. 6. The corresponding equivalent circuit model of the bump interconnect.

where  $[S^{\text{Total}}]$  and  $[S^{\text{CPW}}]$  are obtained through direct measurement with proper reference plane defined. The remaining unknown matrix elements in the above equation can be solved by the following set of equations:

$$S_{11}^{T} = (S_{11}^{b} S_{22}^{b} + S_{12}^{b} S_{12}^{b}) S_{11}^{C} + (S_{12}^{b} S_{22}^{b} + S_{11}^{b} S_{12}^{b}) S_{12}^{C}, (2)$$

$$S_{12}^{T} = (S_{11}^{b} S_{12}^{b} + S_{11}^{b} S_{12}^{b}) S_{11}^{C} + (S_{12}^{b} S_{12}^{b} + S_{11}^{b} S_{11}^{b}) S_{12}^{C}, (3)$$

$$2S_{11}^{b} S_{12}^{b} S_{11}^{C} + (S_{12}^{b} S_{12}^{b} + S_{11}^{b} S_{11}^{b}) S_{12}^{C}$$

$$= 2S_{12}^{b} S_{22}^{b} S_{11}^{C} + (S_{12}^{b} S_{12}^{b} + S_{22}^{b} S_{22}^{b}) S_{12}^{C}. (4)$$

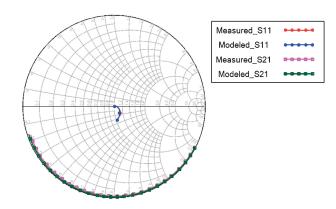

In the above equations, elements with superscript "C" are related to the CPW transmission line on GaAs chip while those with superscript "T" are related to the overall structure. Conversion of the S-parameters of the bump interconnect to the Y-parameters was then performed to extract the component values as outlined in Ref. 23. Figure 7 shows the modeled and measured S-parameters at high bonding temperature. Good agreement over the entire frequency range was achieved. Table III lists the extracted component values corresponding to the two bonding conditions. As observed, the case with higher bonding temperature yields to higher parasitic levels which is related to the larger mechanical stress induced during the bonding process. Such increase in the parasitic levels should be the main reason to result in the degradation in RF performance.

We have investigated the impact of bonding temperature on the performance of a  $150\,\mathrm{nm}$   $\mathrm{In}_{0.6}\mathrm{Ga}_{0.4}\mathrm{As}$  mHEMT device packaged onto RO3210 polymer substrate using FCOB technology. While the DC characteristics remained identical to those of bare dies for both cases, RF degradation was observed for the case of high bonding temperature.

**Fig. 7.** Measured and modeled *S* parameters of the complete structure in Fig. 6 at high bonding temperature.

**Table III.** Extracted parasitic values at high and low bonding temperatures.

| Condition  | R1<br>(Ω) | L1<br>(pH) | C1<br>(fF) | C2<br>(fF) | C3<br>(fF) |

|------------|-----------|------------|------------|------------|------------|

| High temp. | 0.62      | 49         | 12         | 200        | 2.4        |

| Low temp.  | 0.42      | 25         | 7.2        | 95         | 0.2        |

Higher parasitic levels of the bump interconnections have been observed through the extraction of the equivalent circuit for the case of higher bonding temperature. Such increase is related to the higher induced stress level during the bonding process, which leads to the degradation in RF performance.

**Acknowledgment** The authors would like to acknowledge the assistance from National Nano Device Laboratories for high-frequency measurement. The support from the National Science Council, Taiwan, R.O.C., under contracts NSC102-2911-I-009-302 (NCTU-UCB I-RiCE program) and NSC101-2221-E-155-081, is also acknowledged.

- J. N. Mait, D. A. Wikner, M. S. Mirotznik, J. van der Gracht, G. P. Behrmann, B. L. Good, and S. A. Mathews: IEEE Trans. Antennas Propag. 57 (2009) 1713.

- 3) R. Appleby and H. B. Wallace: IEEE Trans. Antennas Propag. 55 (2007) 2944.

- B.-H. Lee, D. An, M.-K. Lee, B.-O. Lim, S.-D. Kim, and J.-K. Rhee: IEEE Electron Device Lett. 25 (2004) 766.

- S. Kim, S. Song, W. Choi, S. Lee, W. Ko, Y. Kwon, and K. Seo: Int. Conf. Indium Phosphide and Related Materials, 2004, p. 20.

- K. Elgaid, H. McLelland, M. Holland, D. A. J. Moran, C. R. Stanley, and I. G. Thayne: IEEE Electron Device Lett. 26 (2005) 784.

- H.-T. Hsu, C.-I. Kuo, E. Y. Chang, and F.-Y. Kuo: Microelectron. Eng. 87 (2010) 2253.

- G. Baumann, H. Richter, A. Baumgartner, D. Ferling, R. Heilig, D. Hollmann, H. Muller, H. Nechansky, and M. Schlechtweg: Proc. IEEE MTT-S Int. Microwave Symp. Dig. 3 (1995) 1639.

- W. Heinrich: IEEE Int. Workshop Radio-Frequency Integration Technology, 2005, p. 124.

- 10) W. Heinrich, A. Jentzsch, and H. Richter: Electron. Lett. 37 (2001) 180.

- K. Boustedt: Proc. IEEE Electronic Components and Technology Conf., 1998, p. 297.

- 12) D. Staiculescu, J. Laskar, and E. M. Tentzeris: IEEE Trans. Microwave Theory Tech. 48 (2000) 1476.

- 13) T. Hirose, K. Makiyama, K. Ono, T. M. Shimura, S. Aoki, Y. Ohashi, S. Yokokawa, and Y. Watanabe: IEEE Trans. Microwave Theory Tech. 46 (1998) 2276.

- 14) T. Krems, W. Haydl, H. Massler, and J. Rudiger: IEEE MTT-S Int. Microwave Symp. Dig. 1 (1996) 247.

- 15) S. Hwang, D. Morgan, A. Kesler, M. Lachab, B. Zhang, A. Heidari, H. Nazir, I. Ahmad, J. Dion, Q. Fareed, V. Adivarahan, M. Islam, and A. Khan: Appl. Phys. Express 4 (2011) 032102.

- 16) A. Jentzsch and W. Heinrich: IEEE MTT-S Int. Microwave Symp. Dig. 2 (1999) 637.

- G. O'Malley, J. Giesler, and S. Machuga: IEEE Trans. Components Packag, Manuf. Technol. 17 (1994) 248.

- 18) J. Giesler, G. O'Malley, M. Williams, and S. Machuga: IEEE Trans. Components Packag. Manuf. Technol. 17 (1994) 256.

- 19) L.-H. Hsu, C.-W. Oh, W.-C. Wu, E. Y. Chang, H. Zirath, C.-T. Wang, S.-P. Tsai, W.-C. Lim, and Y.-C. Lin: IEEE Trans. Components Packag. Manuf. Technol. 2 (2012) 402.

- 20) C.-T. Wang, C.-I. Kuo, H.-T. Hsu, E. Y. Chang, L.-H. Hsu, W.-C. Lim, and Y. Miyamoto: Jpn. J. Appl. Phys. 50 (2011) 096503.

- 21) P. Monfraix, J. Monsarrat, J. L. Muraro, C. Drevon, S. Dareys, M. Billot, and J. L. Cazaux: Proc. IEEE MTT-S Int. Microwave Symp. Dig., 2005, p. 1.

- 22) C.-I. Kuo, H.-T. Hsu, E. Y. Chang, Y. Miyamoto, and W.-C. Tsern: Jpn. J. Appl. Phys. 47 (2008) 7119.

- 23) H. H. M. Ghouz and E.-B. El-Sharawy: IEEE Trans. Microwave Theory Tech. 44 (1996) 2543.

E. Suematsu, Y. Amano, A. Yamada, Y. Zhu, H. Sato, N. Hashizume, F. Kuroki, and T. Yoneyama: IEEE MTT-S Int. Microwave Symp. Dig. 3 (1999) 1047.