## Reduction of defect formation in amorphous indium-gallium-zinc-oxide thin film transistors by N2O plasma treatment

Jhe-Ciou Jhu, Ting-Chang Chang, Geng-Wei Chang, Ya-Hsiang Tai, Wu-Wei Tsai, Wen-Jen Chiang, and Jing-Yi Yan

Citation: Journal of Applied Physics 114, 204501 (2013); doi: 10.1063/1.4832327

View online: http://dx.doi.org/10.1063/1.4832327

View Table of Contents: http://scitation.aip.org/content/aip/journal/jap/114/20?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Low temperature characteristics in amorphous indium-gallium-zinc-oxide thin-film transistors down to 10K Appl. Phys. Lett. **103**, 152103 (2013); 10.1063/1.4824875

Effect of annealing time on bias stress and light-induced instabilities in amorphous indium-gallium-zinc-oxide thin-film transistors

J. Appl. Phys. 110, 114503 (2011); 10.1063/1.3662869

Room-temperature-operated sensitive hybrid gas sensor based on amorphous indium gallium zinc oxide thin-film transistors

Appl. Phys. Lett. 98, 253503 (2011); 10.1063/1.3601488

Environment-dependent thermal instability of sol-gel derived amorphous indium-gallium-zinc-oxide thin film transistors

Appl. Phys. Lett. 98, 152109 (2011); 10.1063/1.3580614

Light induced instabilities in amorphous indium-gallium-zinc-oxide thin-film transistors

Appl. Phys. Lett. 97, 173506 (2010); 10.1063/1.3503971

## Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Reduction of defect formation in amorphous indium-gallium-zinc-oxide thin film transistors by N<sub>2</sub>O plasma treatment

Jhe-Ciou Jhu, <sup>1</sup> Ting-Chang Chang, <sup>1,a)</sup> Geng-Wei Chang, <sup>2</sup> Ya-Hsiang Tai, <sup>2</sup> Wu-Wei Tsai, <sup>3</sup> Wen-Jen Chiang, <sup>3</sup> and Jing-Yi Yan<sup>3</sup>

<sup>1</sup>Department of Physics and Institute of Electro-Optical Engineering, Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung 804, Taiwan

(Received 2 September 2013; accepted 5 November 2013; published online 22 November 2013)

An abnormal sub-threshold leakage current is observed at high temperature in amorphous indium-gallium-zinc-oxide thin film transistors (a-IGZO TFTs). This phenomenon occurs due to a reduced number of defects in the device's a-IGZO active layer after the device has undergone  $N_2O$  plasma treatment. Experimental verification shows that the  $N_2O$  plasma treatment enhances the thin film bonding strength, thereby suppressing the formation of temperature-dependent holes, which are generated above  $400\,\mathrm{K}$  by oxygen atoms leaving their original sites. The  $N_2O$  plasma treatment devices have better stability performance than as-fabricated devices. The results suggest that the density of defects for a-IGZO TFTs with  $N_2O$  plasma treatment is much lower than that in as-fabricated devices. The  $N_2O$  plasma treatment repairs the defects and suppresses temperature-dependent sub-threshold leakage current. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4832327]

#### I. INTRODUCTION

Recently, portable electronic products combined with display, memory, 1-5 and logic devices have been a tendency in modern digital age. As the size and resolution of active matrix displays increase, transparent oxide-based thin-film transistor (TFT) devices with fast response enable the design of peripheral circuits, where deposition of high uniform film at low temperatures such as room temperature (RT)<sup>6,7</sup> and good conducting mobility are required. Also, these characteristics allow for fabrication of flexible displays and computers on inexpensubstrates.<sup>8</sup> In particular, amorphous-InGaZnO<sub>4</sub> (a-IGZO) TFTs have several advantages over other transparent conducting oxides, such as high field-effect mobility, 9-13 small sub-threshold swing, 14 good short-range uniformity, and high electrical reliability. Moreover, amorphous oxide semiconductor-based materials are expected to be adopted as nonvolatile memory devices.<sup>2,15–17</sup> In order to achieve practical application of a-IGZO TFTs in active-matrix backplanes of future generations of large active-matrix liquid-crystal displays (AMLCDs) and organic light-emitting diode panels (OLEDs), some problems still remain to be improved, such as the forming of sub-threshold leakage current at high temperature, instability under light illumination, <sup>18–22</sup> and uncertainty over environmental change.<sup>23–27</sup>

In this study, we investigate the temperature dependence of a-IGZO TFTs using energy band diagrams. Moreover, we fabricate high-performance a-IGZO TFTs with a  $N_2$ O-plasma treatment, and find that the abnormal subthreshold leakage current stretch-out phenomenon can effectively be suppressed

by such treatment. In addition, the hysteresis windows by capacitance-voltage (C-V) measurement can be also significantly suppressed in the N<sub>2</sub>O-plasma treated devices

## **II. EXPERIMENT**

Figure 1 represents the schematic cross-section view of the a-IGZO TFT. Bottom gate coplanar a-IGZO TFTs were produced on glass substrate, and plasma enhanced chemical vapor deposition (PECVD) was applied to grow SiOx (300 nm) film as gate insulator over the patterned Ti/Al/Ti (50/200/50 nm) trilayer gate electrodes at 370 °C. The Ti/Al/Ti (50/200/50 nm) source/drain electrodes were formed by sputtering and then patterned in channel width/length dimensions of (W/L) = 5–30  $\mu$ m/10  $\mu$ m. A 30 nm thick a-IGZO film was deposited by dc magnetron sputtering system at room temperature, using a target of In:Ga:Zn = 1:1:1 atomic ratio, a plasma discharge power of 300 W, and an

FIG. 1. The cross-section view of the bottom gate coplanar a-IGZO TFT device structure.

<sup>&</sup>lt;sup>2</sup>Department of Photonics & Institute of Electro-Optical Engineering, National Chiao Tung University, Hsin-Chu 300, Taiwan

<sup>&</sup>lt;sup>3</sup>Industrial Technology Research Institute, 195, Sec. 4, Chung Hsing Rd., Hsinchu 31040, Taiwan

a) Author to whom correspondence should be addressed. Email: tcchang@mail.phys.nsysu.edu.tw

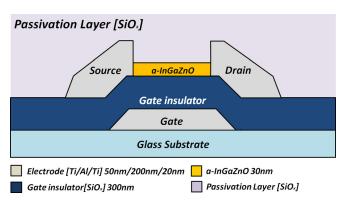

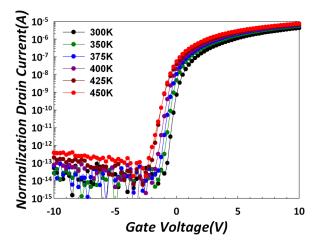

FIG. 2. Characteristics of  $V_G$ -NI $_D$  transfer curves of devices without  $N_2O$  plasma treatment at temperatures between 300 K and 450 K.

ambiance of gas mixture ratio of  $O_2/Ar = 6.7\%$  with a working pressure of 5 mTorr. After defining the active region, one group of TFTs was treated by N2O plasma to passivate the defects in the a-IGZO film. Finally, all devices were capped with a  $200\,\mathrm{nm}~\mathrm{SiO}_X$  layer by PECVD at  $170\,^\circ\mathrm{C}$ , and sequentially annealed in an oven at  $330\,^\circ\mathrm{C}$  for 2 h. The electrical properties of a-IGZO TFTs were analyzed using an Agilent B1500A semiconductor device analyzer in a darkened environment.

#### **III. EXPERIMENT RESULT AND DISCUSSIONS**

Figure 2 shows the transfer characteristics of asfabricated a-IGZO TFTs at different temperatures. As shown in this figure, the curves shift left with the increase of temperature. Also, the drain current in the entire gate voltage  $(V_G)$  region increases with increasing temperature. Below 375 K, the threshold voltage  $(V_T)$  decreases proportionally

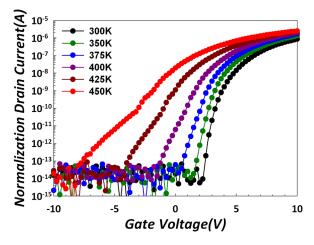

FIG. 3. Energy band diagram of a-IGZO TFTs at high temperature. Thermally induced holes accumulate at the source region and lead to the source side barrier lowering.

with an increase in temperature, with (V<sub>T</sub>) defined as when normalized drain current (NID = ID  $\times$  L/W, where L and W represent channel length and width, respectively) reaches 10<sup>-9</sup> A. It is well known that the free electrons in oxide semiconductor materials are mainly due to the generation of point defects. Thermally excited oxygen atoms leave their original sites with free electrons left behind and vacancies are simultaneously created. The lower V<sub>T</sub> observed at higher temperature can be attributed to more free electrons generated by point defects. Therefore, the threshold voltage substantially shifts towards the negative V<sub>G</sub> direction at 450 K. Moreover, the transfer curve exhibits an apparent subthreshold leakage current stretch-out phenomenon above 400 K. The stretch-out phenomenon becomes serious with the increase in temperature. In addition, it should be noted that the transfer characteristics at room temperature (300 K) are reproducible after measurements at high temperature, implying that the change in transfer characteristics due to increasing temperature is reversible.

Figure 3 shows the energy band diagram of the proposed mechanism. The unique behavior of the subthreshold leakage current for a-IGZO TFTs appears at high temperature. We

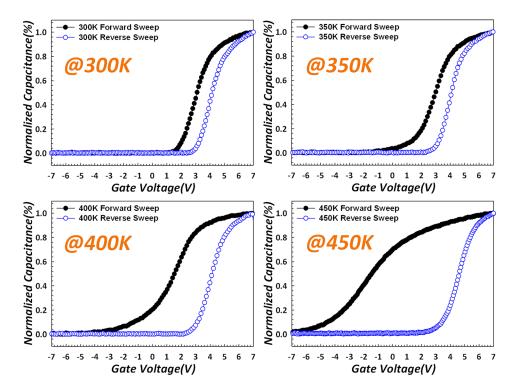

FIG. 4. Normalized capacitance of asfabricated a-IGZO TFTs measured at different temperatures.

FIG. 5. Characteristics of  $V_G$ -NI $_D$  transfer curves of devices with N $_2$ O plasma treatment at temperatures between 300 K and 450 K.

have defined two distinctive regions in the transfer characteristics curve, the stretch-out and above-critical regions. For expediency, we define the critical voltage as when NID reaches  $10^{-10}$  A. When the gate voltage is below critical voltage, thermally induced holes move to the source side due to the transverse electric field. Then, the holes accumulate at the source region and result in source side barrier lowering. The source side barrier lowering enhances electron injection from the source and causes the apparent subthreshold current leakage. Once the gate voltage is above critical voltage, however, the transfer characteristics are dominated by the barrier height between a-IGZO and source, with barrier height becomes much lower with increasing of gate voltage, making hole accumulation at the source region more difficult. Therefore, the transfer curve is separated into two regions with increasing gate voltage.

Figure 4 shows the capacitance-voltage (C-V) curve of as-fabricated a-IGZO TFTs at different temperatures. The device was measured under gate voltage from -7 V to 7 V as the forward sweep, and 7 V to -7 V as reverse sweep. After forward and reverse sweeping, a hysteresis phenomenon appears in as-fabricated a-IGZO TFTs. The shift of the transfer curve in the hysteresis loop can be attributed to the extra trap states generated during the deposition of the SiO<sub>2</sub> passivation layer by PECVD. Furthermore, the interface/oxide defects trap holes at negative gate voltage and electrons at positive gate voltage, respectively. At 300 K, the hysteresis phenomenon is caused by the captured electrons at positive gate voltage rather than hole carriers. Because of the low number of holes in IGZO TFTs at low temperature, it is thus difficult for many to be trapped at interface/oxide defects. However, it is worth noting that the hysteresis window increases with the increase in temperature. With gate voltage changing from -7 V to 7 V, the forward sweep curve shifts to the left with the increase in temperature. This left-moving tendency is caused by the trapped hole carriers at negative gate voltage at high temperature. This implies that the hole is induced by thermal energy. Therefore, the obvious hysteresis phenomenon appears in untreated a-IGZO TFTs at 450 K.

Figure 5 shows the transfer characteristics of a-IGZO TFTs with N<sub>2</sub>O-plasma treatment at different temperatures. Compared with untreated a-IGZO TFTs, the curves shift only slightly to the left with increasing temperature. Also the apparent subthreshold leakage current stretch-out phenomenon is significantly suppressed at high temperature. This implies that the N<sub>2</sub>O-plasma treatment can suppress defect generation at high temperature and enhance the atomic bonding strength. It becomes difficult for oxygen atoms to leave their original sites due to the stronger bonding energy. Moreover, the quantity of thermally induced holes is also reduced as fewer defects are formed. Thus only a few holes

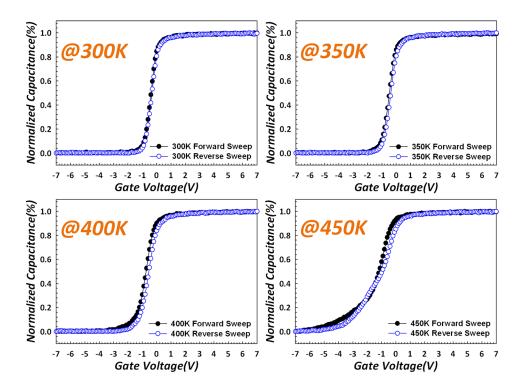

FIG. 6. Normalized capacitance of a-IGZO TFTs with  $N_2O$  plasma treatment measured at different temperatures.

accumulate at the source barrier and the amount is too small to cause source side barrier lowering, which in turn suppresses subthreshold leakage current.

Figure 6 shows the capacitance-voltage (C-V) curve of N<sub>2</sub>O-plasma treatment a-IGZO TFTs at different temperatures. The hysteresis phenomenon can be significantly suppressed in the device with N<sub>2</sub>O-plasma treatment. The N<sub>2</sub>O-plasma treatment can improve SiO<sub>2</sub>/IGZO interface properties as the oxygen-rich region effectively prevents damage during the SiO<sub>2</sub> deposition process. The shift in the transfer curve in the hysteresis loop can be clearly lessened due to the repairing of interface defects. Furthermore, the hysteresis phenomenon also lessened under high temperature. Therefore, N<sub>2</sub>O-plasma treatment for a-IGZO TFTs can significantly enhance the stability of the performance of a-IGZO TFTs at high temperature.

### IV. CONCLUSIONS

In conclusion, we have obtained better performance stability in a-IGZO TFTs with a  $N_2O$  plasma treatment on the a-IGZO channel region. For the as-fabricated device, the passivation layer deposition process can cause extra trap states due to PECVD plasma damage, which results in significant subthreshold current leakage stretch-out phenomenon at high temperatures. The  $N_2O$ -plasma treatment is applied to a-IGZO layer and improves the SiO2/IGZO interface property, as the oxygen-rich region effectively prevents damage during SiO2 deposition process. The  $N_2O$ -plasma treatment therefore significantly enhances the performance stability of a-IGZO TFTs at high temperature. It is expected that  $N_2O$ -plasma will prove to be an effective surface treatment in other oxide semiconductor devices.

### **ACKNOWLEDGMENTS**

This work was performed at National Science Council Core Facilities Laboratory for Nano-Science and Nano-Technology in Kaohsiung-Pingtung area, NSYSU Center for Nanoscience and Nanotechnology, and was supported by the National Science Council of the Republic of China under Contract No. NSC-102-2120-M-110-001.

- <sup>2</sup>M. C. Chen, T. C. Chang, C. T. Tsai, S. Y. Huang, S. C. Chen, C. W. Hu, S. M. Sze, and M. J. Tsai, Appl. Phys. Lett. **96**, 262110 (2010).

- <sup>3</sup>Y. E. Syu, T. C. Chang, T. M. Tsai, Y. C. Hung, K. C. Chang, M. J. Tsai, M. J. Kao, and S. M. Sze, IEEE Electron Device Lett. **32**(4), 545–547 (2011).

- <sup>4</sup>Y. T. Tsai, T. C. Chang, C. C. Lin, S. C. Chen, C. W. Chen, S. M. Sze, F. S. Yeh, and T. Y. Tseng, Electrochem. Solid State Lett. **14**, H135 (2011).

- <sup>5</sup>W. R. Chen, T. C. Chang, J. L. Yeh, S.M Sze, and C. Y. Chang, Appl. Phys. Lett. **92**, 152114 (2008).

- <sup>6</sup>A. Suresh, P. Wellenius, A. Dhawan, and J. Muth, Appl. Phys. Lett. 90, 123512 (2007).

- <sup>7</sup>K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, Nature **432**, 488 (2004).

- <sup>8</sup>W. Lim, E. A. Douglas, S.-H. Kim, D. P. Norton, and S. J. Pearton, Appl. Phys. Lett. **94**, 072103 (2009).

- <sup>9</sup>J. H. Na, M. Kitamura, and Y. Arakawa, Appl. Phys. Lett. **93**, 063501 (2008).

- <sup>10</sup>M. Kim, J. H. Jeong, H. J. Lee, T. K. Ahn, and H. S. Shin, Appl. Phys. Lett. **90**, 212114 (2007).

- <sup>11</sup>S.-Y. Han, D.-H. Lee, G. S. Herman, and C.-H. Chang, J. Display Technol. 5, 520 (2009).

- <sup>12</sup>T. Kamiya, K. Nomura, and H. Hosono, J. Display Technol. 5, 468 (2009).

- <sup>13</sup>A. Suresh, P. Gollakota, P. Wellenius, A. Dhawan, and J. F. Muth, Thin Solid Films **516**, 1326–1329 (2008).

- <sup>14</sup>L.-Y. Su, H.-Y. Lin, H.-K. Lin, S.-L. Wang, L.-H. Peng, and J. J. Huang, IEEE Electron Device Lett. 32, 1245 (2011).

- <sup>15</sup>P. H. Yeh, L. J. Chen, P. T. Liu, D. Y. Wang, and T. C. Chang, Electrochim. Acta **52**, 2920–2926 (2007).

- <sup>16</sup>M. C. Chen, T. C. Chang, S. Y. Huang, K. C. Chang, and H. W. Li, Appl. Phys. Lett. **94**, 162111 (2009).

- <sup>17</sup>M. C. Chen, T. C. Chang, S. Y. Huang, S. C. Chen, C. W. Hu, C. T. Tsai, and S. M. Sze, Electrochem. Solid-State Lett. **13**(6), H191–H193 (2010).

- <sup>18</sup>K. H. Lee, J. S. Jung, K. S. Son, J. S. Park, and T. S. Kim, Appl. Phys. Lett. **95**, 232106 (2009).

- <sup>19</sup>T. C. Chen, T. C. Chang, C. T. Tsai, T. Y. Hsieh, and S. C. Chen, Appl. Phys. Lett. 97, 112104 (2010).

- <sup>20</sup>T. C. Chen, T. C. Chang, T. Y. Hsieh, C. T. Tsai, and S. C. Chen, Appl. Phys. Lett. 97, 192103 (2010).

- <sup>21</sup>Y. J. Chung, J. H. Kim, U. K. Kim, S. H. Rha, and E. Hwang, J. Appl. Phys. 111, 024511 (2012).

- <sup>22</sup>T. C. Chen, T. C. Chang, T. Y. Hsieh, C. T. Tsai, S. C. Chen, C. S. Lin, F. Y. Jian, and M. Y. Tsai, Thin Solid Films 520, 1422–1426 (2011).

- <sup>23</sup>Y. C. Chen, T. C. Chang, H. W. Li, S. C. Chen, W. F. Chung, Y. H. Chen, Y. H. Tai, T. Y. Tseng, and F. S. Yeh(Huang), Thin Solid Films 520, 1432–1436 (2011).

- <sup>24</sup>Y. C. Chen, T. C. Chang, H. W. Li, S. C. Chen, and J. Lu, Appl. Phys. Lett. 96, 262104 (2010).

- <sup>25</sup>J. S. Park, J. K. Jeong, H. J. Chung, Y. G. Mo, and H. D. Kim, Appl. Phys. Lett. **92**, 072104 (2008).

- <sup>26</sup>P. T. Liu, Y. T. Chou, and L. F. Teng, Appl. Phys. Lett. 95, 233504 (2009)

- <sup>27</sup>J. K. Jeong, H. W. Yang, J. H. Jeong, Y. G. Mo, and H. D. Kim, Appl. Phys. Lett. **93**, 123508 (2008).

<sup>&</sup>lt;sup>1</sup>T. C. Chang, F. Y. Jian, S. C. Chen, and Y. T. Tsai, Mater. Today **14**(12), 608 (2011).