## Influences of $\text{SiO}_x$ layer thickness on the characteristics of In–Zn–O/ $\text{SiO}_x/n$ -Si hetero-junction structure solar cells

Hau-Wei Fang <sup>a</sup>, Tsung-Eong Hsieh <sup>a,\*</sup>, Jenh-Yih Juang <sup>b</sup>

<sup>a</sup> Department of Materials and Engineering, National Chiao Tung University, Hsinchu, 30010, Taiwan, ROC

<sup>b</sup> Department of Electrophysics, National Chiao Tung University, Hsinchu, 30010, Taiwan, ROC

### ARTICLE INFO

Available online 1 August 2012

#### Keywords:

Indium zinc oxide

Pulsed laser deposition

Hetero-junction structured solar cells

### ABSTRACT

Indium zinc oxide (IZO) film was directly deposited on an *n*-type Si substrate by pulsed laser deposition (PLD) to form the IZO/ $\text{SiO}_x/n$ -Si hetero-junction solar cell. Analytical results indicated that the thickness and quality of the thermal  $\text{SiO}_x$  layer plays a prominent role in determining the conversion efficiency of the solar cell. The sample containing an about 1.78-nm-thick  $\text{SiO}_x$  layer exhibits an open-circuit voltage of 0.35 V, a short-circuit current density of 28.6 mA/cm<sup>2</sup>, a fill factor of 34.3%, and an overall conversion efficiency of 3.4% under AM1.5 condition. The effects of the  $\text{SiO}_x$  layer thickness and the associated interface states on the carrier transport are discussed.

© 2012 Elsevier B.V. All rights reserved.

### 1. Introduction

Photovoltaic devices based on the semiconductor-insulator-semiconductor (SIS) hetero-junction structures have attracted extensive research interests due to the advantages of a simple manufacturing process, relatively low cost and high efficiency [1–4]. In SIS devices, transparent conductive oxides (TCO) with a wide bandgap ( $E_g > 3$  eV) serve as the transparent window of devices and the solar radiation is mainly absorbed by the Si substrate with  $E_g = 1.1$  eV. There is a native  $\text{SiO}_x$  layer several nanometers in thickness that forms in between the TCO and Si substrate and it has been reported that such a thin insulator layer plays a key role in the performance of SIS devices [3].

Several SIS solar cells with high conversion efficiency ( $\eta$ ) have been reported previously [1–4]. For instance, the devices containing indium tin oxide ( $\text{In}_2\text{O}_3$  doped with 5 to 9 wt.% of  $\text{SnO}_2$ , ITO) [1–3] and tin oxide ( $\text{SnO}_2$ ) [4] exhibited conversion efficiency ( $\eta$ ) = 12% and 8%, respectively. However, the high deposition temperature of  $\text{SnO}_2$  films ( $>400$  °C) and the high cost of ITO films severely hinder the development of these two PV device types. Recently, amorphous In–Zn–O (*a*-IZO) films with various In/Zn ratios have attracted considerable attention due to their low resistivity and high carrier mobility properties [5–9]. In particular, the relatively low In content in comparison with ITO and the low deposition temperature have made IZO a promising TCO alternative for the fabrication of SIS solar cells.

Our previous study employed the pulse laser deposition (PLD) method to fabricate the SIS solar cells by depositing an *a*-IZO film

on *n*-type Si substrate clad with a thin  $\text{SiO}_x$  layer [10]. The  $\text{SiO}_x$  layer was grown by immersing the Si wafer in a hot  $\text{H}_2\text{O}_2$  solution and the IZO film was deposited at the substrate temperature of 150 °C. The *a*-IZO/ $\text{SiO}_x/n$ -Si solar cell exhibited a  $\eta$  value of about 2.2% which is still remote from practical applications. Further, the open-circuit voltage ( $V_{oc}$ ) of the device was about 0.24 V, only half of the reported value of 0.4–0.5 V [1–4]. In addition to the presence of interface states, the thickness and film quality of the  $\text{SiO}_x$  layer are the key factors affecting the performance of the SIS solar cells as suggested by Spitzer et al. [3]. This inspired us to form the  $\text{SiO}_x$  layer by means of a dry process instead of the wet process mentioned above.

In this study, we vary the substrate temperature to modulate the thickness of the  $\text{SiO}_x$  layer formed during PLD deposition which may serve as the tunneling layer of SIS devices. Systematic investigations were carried out to delineate the effects of the structure and properties of the top IZO layers as well as the thickness of the  $\text{SiO}_x$  layer on the characteristics of IZO/ $\text{SiO}_x$ /Si SIS devices. The microstructure, electrical and optical properties of the IZO films prepared at various PLD processing conditions were analyzed in conjunction with the morphology of the  $\text{SiO}_x$  layers grown on the Si substrates under various heating conditions and their correlations to the performance of SIS solar cells are discussed.

### 2. Experimental

The IZO targets for PLD deposition were prepared by using a mixture of  $\text{In}_2\text{O}_3$  and  $\text{ZnO}$  (purity = 99.999% supplied by Gredmann) powders at the atomic ratio of In:Zn = 2:3. The mixed powders were homogenized by attrition milling, pre-calcinated at 600 °C in ambient air for 6 h, and then pressed at a pressure of 10 psi to form

\* Corresponding author. Tel.: +886 3 5712121; fax: +886 3 5724727.

E-mail address: [tehsieh@mail.nctu.edu.tw](mailto:tehsieh@mail.nctu.edu.tw) (T.-E. Hsieh).

the pellets with diameters of one inch. Finally, the pellets were sintered at 1250 °C for 2 h to form the PLD targets.

Corning 1737 glass plates and *n*-type Si (100) wafers (resistivity = 2–5 Ω·cm) were adopted as the substrates for sample preparation. Before transferring to the PLD system, the glass and Si substrates were sequentially cleaned by immersion in deionized water, acetone and ethanol. For Si wafers, they were further immersed in a BOE solution for 3 min to remove the native oxide layer before PLD deposition. The thin-film deposition was carried out in a PLD system equipped with a KrF excimer laser (Compex 201;  $\lambda$  = 248 nm) and background pressure better than  $2.7 \times 10^{-4}$  Pa. The target-to-substrate distance was kept at 45–50 mm. During the deposition, the laser was operated at an energy density of 4.5 J/cm<sup>2</sup> per pulse with a repetition rate of 5 Hz. Prior to IZO deposition, the Si substrates were heated at temperatures of 100, 200, 300 or 400 °C for 5 min, respectively, so as to form the  $\text{SiO}_x$  layers with different thicknesses. Such insulating oxide layers were grown on the Si substrates via the dry thermal oxidization process by utilizing the residual oxygen in the PLD chamber as the reacting gas. Afterward, high purity argon (Ar; purity = 99.999%) was introduced into the vacuum chamber until reaching the working pressure of 0.57 Pa for the IZO deposition. The IZO films with thicknesses in the range of 45 to 55 nm were achieved as determined by the alpha-step profile meter (KOSAKA ET300). Subsequently, a layer of 100-nm thick aluminum (Al) was deposited by using e-beam evaporation to form the bottom electrode on the backside of the Si wafer and the finger electrodes on the top of the IZO layer.

The microstructures of the IZO films were separately analyzed by using an X-ray diffractometer (REGAKU;  $\lambda_{\text{Cu}-K\alpha}$  = 0.15405 nm, scan rate = 2 °/min) and a transmission electron microscope (JEOL JEM-2100 F). The electrical properties, including the resistivity, carrier concentration and Hall mobility, were measured by the van der Pauw method in the four-point probe system (All-real AHE-1000). The transmittance of IZO films was measured in the wavelength range of 200 to 1600 nm by an UV-vis-NIR spectrometer (JASCO, V-650). The density of the interface states ( $D_{it}$ ) was calibrated by the photoresponsive C-V measurement [11] using a 20-W halogen lamp as a light source and a Wayne Kerr 6500B C-V meter at the frequency of 100 kHz. The open-circuit voltage ( $V_{oc}$ ), short-circuit current density ( $J_{sc}$ ) and fill factor (FF) of the  $\alpha$ -IZO/ $\text{SiO}_x$ /Si solar cells were characterized by the  $J$ - $V$  measurements under AM 1.5 illumination in a solar cell efficiency measurement system equipped with a xenon lamp and a Keithley 2400  $I$ - $V$  source meter.

### 3. Results and discussion

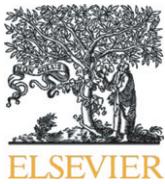

Fig. 1 shows the XRD patterns of IZO films deposited at various substrate temperatures. The IZO film prepared at 100 °C is amorphous

Fig. 1. XRD patterns of IZO films prepared on a glass substrate at various substrate temperatures.

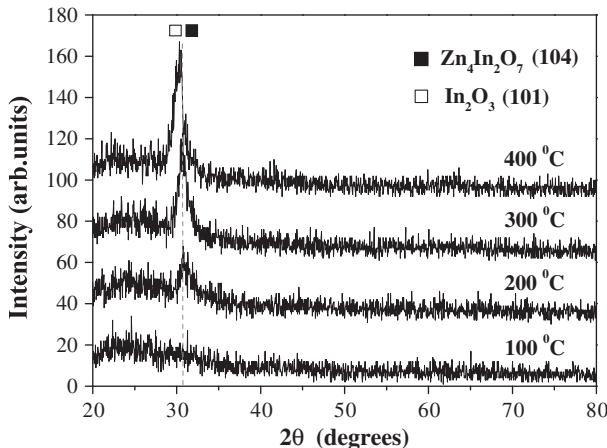

Fig. 2. Resistivity (□), carrier concentration (○), and mobility (△) as functions of the substrate temperature of IZO films deposited on a glass substrate.

whereas a broad peak at  $2\theta = 30.9$  ° emerges for those obtained at substrate temperatures above 200 °C and its intensity increases progressively with the increase of substrate temperature. The diffraction peak possibly originates from the (222) diffraction of the bixbyite structure of  $\text{In}_2\text{O}_3$  ( $2\theta = 30.6$  °) or the (101) diffraction of the spinel structure of  $\text{Zn}_4\text{In}_2\text{O}_7$  ( $2\theta = 31.0$  °). According to the phase diagram of the binary  $\text{In}_2\text{O}_3$ - $\text{ZnO}$  system reported by Moriga et al. [5], both of the  $\text{In}_2\text{O}_3$  and  $\text{Zn}_4\text{In}_2\text{O}_7$  phases might form in the IZO film when the  $\text{Zn}_4\text{In}_2\text{O}_7$  homologous compound or the  $\text{In}_2\text{O}_3$ - $\text{ZnO}$  ceramic target was used. Moreover, the XRD peak shifts toward the small diffraction angle side when the substrate temperature is increased. This is ascribed to the increase of mutual solubility of  $\text{In}_2\text{O}_3$  and  $\text{ZnO}$ , which causes more In atoms to occupy the Zn sites and thus results in the lattice expansion [12].

The electrical characteristics of the IZO films deposited at various substrate temperatures are depicted in Fig. 2. It can be seen that the resistivity decreases with the increase of substrate temperature and reaches a value as low as  $6.0 \times 10^{-4}$  Ω·cm at the substrate temperature of 300 °C. The carrier concentration of IZO films, on the other hand, varies mildly in the range of  $3.6 \times 10^{20}$  to  $4.6 \times 10^{20}$  cm<sup>-3</sup> and is relatively insensitive to the change of substrate temperature. The Hall mobility of IZO films, nevertheless, increases monotonically from 12 to 24 cm<sup>2</sup>/V·s with the increase of temperature. The decrease of resistivity and increase of mobility with the increase of temperature is ascribed to the improvement of IZO crystallinity as indicated by the XRD analysis shown in Fig. 1. Consequently, it is conceived that IZO films with lower resistivity and higher mobility may be obtained when the processing temperature is high. Note that even though the crystallinity was improved by increasing the substrate temperature, the IZO layers prepared in this study should possess a relatively fine grain structure due to the wide full-width-

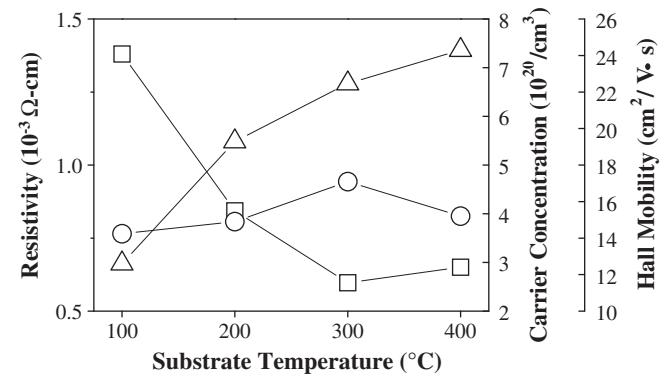

Fig. 3. Transmittance spectra of IZO films prepared at various substrate temperatures. The inset shows the determination of  $E_g$  by extrapolating the plot of  $\sqrt{\alpha h\nu}$  against  $h\nu$ .

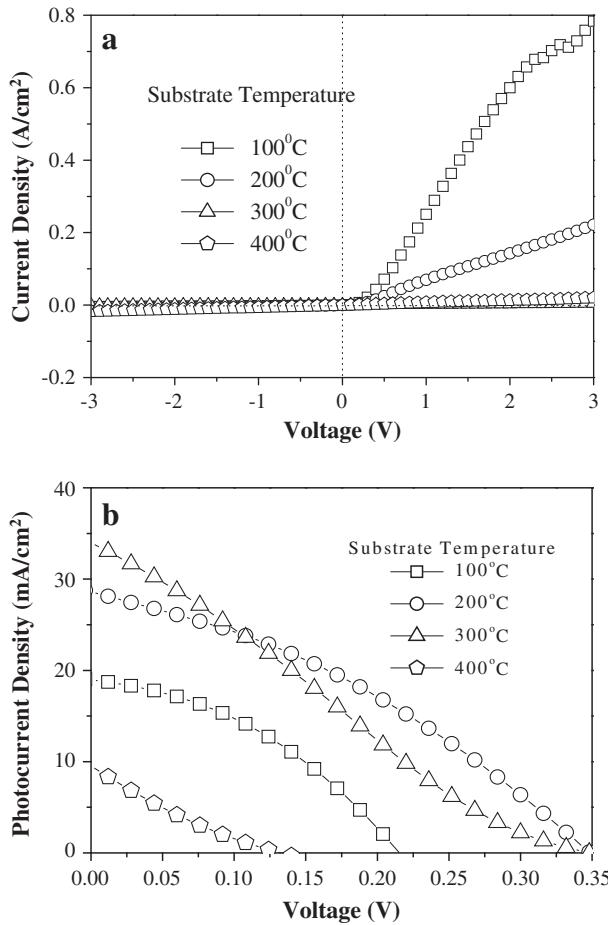

Fig. 4. J-V characteristic of SIS devices measured (a) in the dark and (b) at the AM1.5 illumination condition.

half-maximum of the XRD peak as depicted in Fig. 1. It is believed that the relatively high  $\text{In}_2\text{O}_3$  content implies a mixture of amorphous and nano-scale grain structures in the IZO films, in contrast to the columnar structure observed in IZO films with low  $\text{In}_2\text{O}_3$  contents.

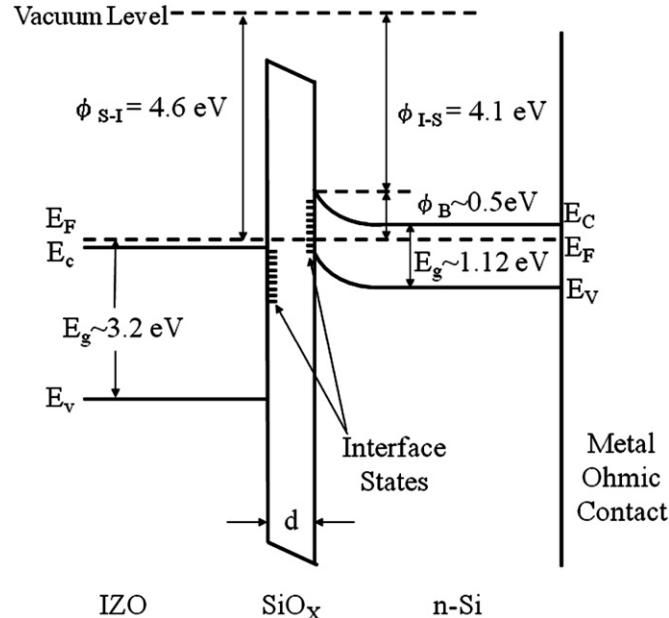

Fig. 5. Schematic energy band diagram of the IZO/SiO<sub>2</sub>/n-Si hetero-junction structure.

Fig. 3 presents the transmittance of IZO films prepared at various substrate temperatures. Except for the IZO films deposited at 100 °C, all films exhibit high transparency (80%) in visible-light wavelength range. Furthermore, it is evident that the increase of substrate temperature, hence improved crystallinity of IZO films, results in a shift of the absorption edge toward the shorter wavelength region. The  $E_g$  values of the samples can be obtained by the Tauc relationship [13]:

$$\alpha = A(h\nu - E_g)^r \quad (1)$$

where  $\alpha$  is the absorption coefficient,  $A$  is a constant,  $h$  is the Plank's constant,  $\nu$  is the frequency of the incident light, and  $r=2$  for an indirect band-gap semiconductor. As revealed by the inset in Fig. 3, the values of  $E_g$  of the IZO films are in the range of 3.20–3.35 eV as determined by extrapolating the plot of  $\sqrt{\alpha h\nu}$  against  $h\nu$ .

Fig. 4(a) shows the current density-voltage (J-V) characteristics of the SIS devices measured in a dark environment. The rectifying behavior of the samples deposited at 100 and 200 °C suggests that these devices are of the SIS type [14]. Based on the  $E_g$  values obtained in Fig. 3 and the J-V characteristics, the devices are believed to consist of the IZO/SiO<sub>x</sub>/n-Si tri-layer structure and the corresponding energy band diagram is depicted schematically in Fig. 5. In the diagram,  $\phi_{S-I}$  and  $\phi_{I-S}$  are the work functions of IZO and Si, respectively. The theoretical upper limit of the barrier height,  $\phi_B$ , i.e., the difference between  $\phi_{S-I}$  and  $\phi_{I-S}$  would be 0.5 eV as indicated in Fig. 5 [15]. Thus, when a forward bias is applied to the device, the current is dominated by the electrons tunneling from n-Si into IZO because of the relatively

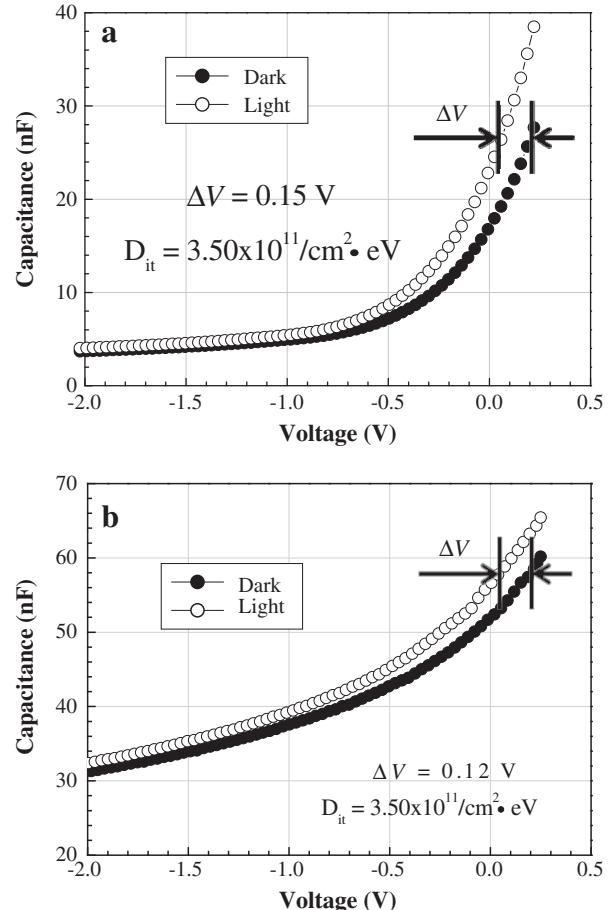

Fig. 6. Photoreponsive C-V characteristics of SIS devices prepared at substrate temperatures of (a) 200 and (b) 400 °C.

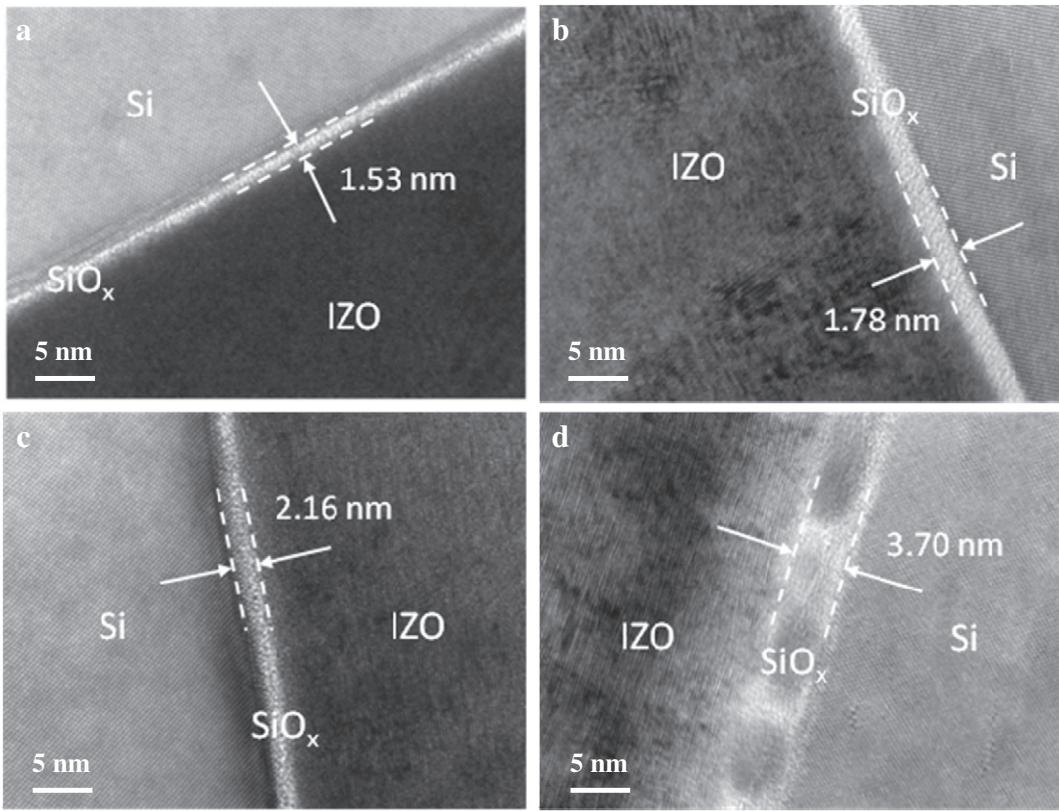

Fig. 7. Cross-sectional TEM micrographs of SIS devices prepared at substrate temperatures of (a) 100, (b) 200, (c) 300 and (d) 400 °C.

higher  $\phi_{S-I}$  in the devices. In principle, the tunneling current would decrease rapidly with increasing  $\text{SiO}_x$  layer thickness. Hence, the results displayed in Fig. 4(a) indicate that the thickness of the  $\text{SiO}_x$  layer might vary markedly with the substrate temperature.

Moreover, the value of  $\phi_B$  is intimately correlated with the  $V_{oc}$  of the devices in accord with the theoretical model proposed by Shewchun et al. [1–3]. The interface traps at the IZO/ $\text{SiO}_x$  interfaces and  $\text{SiO}_x/\text{Si}$  interfaces (denoted as interface states in Fig. 5) may also restrict the carrier tunneling process and result in the suppression of  $V_{oc}$  of the SIS devices. In order to obtain the interface properties of SIS structures, a photoresponsive C-V measurement was carried out. The value of  $D_{it}$  can be estimated by using the equation [11]:

$$D_{it} = \frac{C_i \Delta V}{q E_g} \quad (2)$$

where  $C_i$  is the capacitance of the insulator layer,  $\Delta V$  is the voltage shift caused by the change in charges at the Si surface states,  $q$  is the charge of the electron, and  $E_g$  is the bandgap of the insulator layer. Fig. 6(a) and (b) presents the photoresponsive C-V characteristics of the SIS devices prepared at substrate temperatures of 200 and 400 °C, respectively. According to Eq. (2), the  $D_{it}$  of the SIS solar cell samples prepared at 200 and 400 °C were found to be  $3.50 \times 10^{11}$  and  $1.35 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ , respectively. According to the numerical solution of transport equations reported by Spitzer et al. [3], the  $V_{oc}$ , FF and  $\eta$  of the SIS solar cell can be improved by the decrease of  $D_{it}$  since it would result in a decrease in the interface state recombination current density and a decrease in the charge capture or trapping. As to a  $J_{sc}$  property, their calculation revealed it is insensitive to the change of  $D_{it}$ . Spitzer et al. also reported that the effective fixed insulator charges at  $\text{SiO}_x/\text{Si}$  interface may be dependent on the insulator growth procedure. The fixed insulator charge decreases with the increase of substrate temperature, implying the increase of  $V_{oc}$  and  $J_{sc}$  of SIS device. Our analysis indicated that the SIS sample prepared at

400 °C in fact exhibited the lowest  $\eta$  value although the increase of the substrate temperature suppressed the  $D_{it}$ . The irrelevance of cell performance to the change of  $D_{it}$  might be ascribed to the comparatively low  $D_{it}$  values in our samples which are about two orders of magnitude lower than the results reported previously [16,17]. Since the  $D_{it}$  decrement did not imply the improvement of  $\eta$ , the thickness of the  $\text{SiO}_x$  layer is hence the dominant factor on the performance of SIS solar cells prepared in this study. This is illustrated by the J-V characteristics of SIS devices measured under the AM1.5 illumination condition shown in Fig. 4(b) and the TEM characterization presented in Fig. 7. Table 1 lists the  $V_{oc}$ ,  $J_{sc}$ , FF, and  $\eta$  deduced from the J-V profiles of the devices shown in Fig. 4(b). As shown in Table 1, the  $J_{sc}$  decreases with increasing substrate temperature for IZO film deposition, presumably due to the increasing thickness of  $\text{SiO}_x$  layers deposited at high temperatures.

Fig. 7(a)–(d) shows the cross-sectional TEM images of the SIS devices prepared at various substrate temperatures. According to the lattice fringe emerging in the IZO portion, the crystallinity of the IZO films is progressively improved with the increase of substrate temperature, which is consistent with the XRD results presented in Fig. 1. Furthermore, it is also apparent that an ultra-thin thermal oxide layer presents between the IZO layer and Si substrates in all the samples prepared in this study. The thicknesses of the  $\text{SiO}_x$  layers deposited at 100, 200, 300, and 400 °C are found to be about 1.53, 1.78, 2.16, and 3.70 nm, respectively.

Table 1

PV characteristics of IZO/ $\text{SiO}_x$ /n-Si solar cells prepared at various substrate temperatures.

| Substrate temperature (°C) | $\text{SiO}_x$ thickness (nm) | $V_{oc}$ (V) | $J_{sc}$ (mA/cm <sup>2</sup> ) | FF (%) | $\eta$ (%) |

|----------------------------|-------------------------------|--------------|--------------------------------|--------|------------|

| 100                        | 1.53                          | 0.22         | 18.79                          | 38.66  | 3.16       |

| 200                        | 1.78                          | 0.35         | 28.60                          | 34.28  | 3.42       |

| 300                        | 2.16                          | 0.35         | 34.01                          | 23.73  | 3.01       |

| 400                        | 3.70                          | 0.13         | 9.52                           | 19.75  | 0.25       |

1.78, 2.16, and 3.70 nm, respectively. The influence of the thickness variation of the  $\text{SiO}_x$  layer on the performance of the SIS devices can be understood as follows. For instance, the device fabricated at 400 °C exhibited a low  $J_{sc}$  of 9.5 mA/cm<sup>2</sup> and a relatively low  $\eta$  of 0.25%, which might have resulted from the thick  $\text{SiO}_x$  layer (about 3.70 nm) as seen in Fig. 7(d). It resulted in the increase in the series resistance of the SIS device, leading to the decrease of  $J_{sc}$  and consequently the degradation of carrier tunneling efficiency. On the other hand, the IZO/ $\text{SiO}_x/n$ -Si devices fabricated at 200 °C exhibits the highest  $\eta$  of 3.4% with the corresponding  $V_{oc}$ ,  $J_{sc}$  and FF of 0.35 V, 28.6 mA/cm<sup>2</sup> and 34.3%, respectively. The substantial improvement on  $J_{sc}$  illustrates that an adequate thickness (1.8–2.0 nm) of the interfacial  $\text{SiO}_x$  layer is essential to the performance of SIS solar cells, which is in agreement with the theoretical prediction [18].

Finally, we note that the utilization of dry thermal oxidization in forming the  $\text{SiO}_x$  layer benefits the performance of the SIS sample in comparison with the sample prepared by using the wet process [10]. It is well known that the dry method is able to produce the  $\text{SiO}_x$  layer with a dense structure and less crystalline defects. Hence, the quality of the  $\text{SiO}_x$  layer is also a decisive factor affecting the SIS solar cell performance.

#### 4. Conclusions

This work demonstrates a simple fabrication process of IZO/ $\text{SiO}_x/n$ -Si SIS solar cells by directly depositing IZO films on the  $n$ -type Si substrates. Prior to the IZO deposition, the thin  $\text{SiO}_x$  layers were formed on Si wafers via the dry thermal oxidization method in the temperature range of 100–400 °C to serve as the carrier tunneling layer. Analytical results indicated that an adequate thickness of the interfacial oxide layer is essential to optimize the electrical properties of the SIS devices. The  $\text{SiO}_x$  layer formed at 200–300 °C with a thickness of about 1.8–2.0 nm was found

to imply the best device performance with  $V_{oc}$ ,  $J_{sc}$ , FF and  $\eta$  of 0.35 V, 28.6 mA/cm<sup>2</sup>, 34.3% and 3.4%, respectively.

#### Acknowledgment

This work is supported by the National Science Council, Taiwan, R.O.C., under the contracts NSC98-2221-E-009-037-MY2 and NSC98-3114-E-009-003-CC2. Professor J.Y. Juang is supported in part by NSC98-2112-M009-004-MY3 and the MOE ATU program operated at NCTU.

#### References

- [1] J. Shewchun, J. Dubow, A. Myszkowski, R. Singh, *J. Appl. Phys.* 49 (1978) 855.

- [2] J. Shewchun, D. Burk, R. Singh, M. Spitzer, J. Dubow, *J. Appl. Phys.* 50 (1979) 6524.

- [3] M. Spitzer, J. Shewchun, D. Burk, *J. Appl. Phys.* 51 (1980) 6399.

- [4] A.K. Ghosh, C. Fishman, T. Feng, *J. Appl. Phys.* 49 (1978) 3490.

- [5] T. Moriga, D.D. Edwards, T.O. Mason, G.B. Palmer, K.R. Poeppelmeier, J.I. Schindler, C.R. Kannewurf, I. Nakabayashi, *J. Am. Ceram. Soc.* 81 (1998) 1310.

- [6] N. Naghavi, C. Marcel, L. Dupont, A. Rougier, J.B. Leriche, C. Guery, *J. Mater. Chem.* 10 (2000) 2315.

- [7] Y.S. Jung, J.Y. Seo, D.W. Lee, D.Y. Jeon, *Thin Solid Films* 445 (2003) 63.

- [8] K. Ramamoorthy, M. Jayachandran, K. Sankaranarayanan, P. Misra, L.M. Kukreja, C. Sanjeeviraja, *Sol. Energy* 77 (2004) 193.

- [9] K.C. Aw, Z. Tsakadze, A. Lohani, S. Mhaisalkar, *Scr. Mater.* 60 (2009) 48.

- [10] H.W. Fang, S.J. Liu, T.E. Hsieh, J.Y. Juang, J.H. Hsieh, *Sol. Energy* 85 (2011) 2589.

- [11] J. Tan, M.K. Das, J.A. Cooper Jr., M.R. Melloch, *Appl. Phys. Lett.* 70 (1997) 2280.

- [12] C. Huang, M. Wang, Q. Liu, Y. Cao, Z. Deng, Z. Huang, Y. Liu, Q. Huang, W. Guo, *Semicond. Sci. Technol.* 24 (2009) 095019 (6 pp.).

- [13] J. Tauc, R. Grigorovici, A. Vancu, *Phys. Status Solidi* 15 (1966) 627.

- [14] S.M. Sze, K.K. Ng, *Physics of Semiconductor Devices*, 3rd ed. Wiley & Sons, Inc., 2007.

- [15] J.P. Ponpon, P. Siffert, *J. Appl. Phys.* 47 (1976) 3248.

- [16] D. Bauza, *IEEE Electron Device Lett.* 23 (2002) 658.

- [17] P.K. Hurley, B.J. O'Sullivan, F.N. Cubaynes, P.A. Stolk, F.P. Widdershoven, J.H. Das, *J. Electrochem. Soc.* 149 (2002) G194.

- [18] W.W. Wenas, S. Riyadi, *Sol. Energy Mater. Sol. Cells* 90 (2006) 3261.