Home Search Collections Journals About Contact us My IOPscience

Novel gate-all-around polycrystalline silicon nanowire memory device with HfAlO charge-trapping layer

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2014 Jpn. J. Appl. Phys. 53 014001

(http://iopscience.iop.org/1347-4065/53/1/014001)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 23:35

Please note that terms and conditions apply.

# Novel gate-all-around polycrystalline silicon nanowire memory device with HfAlO charge-trapping layer

Ko-Hui Lee<sup>1</sup>, Horng-Chih Lin<sup>1,2\*</sup>, and Tiao-Yuan Huang<sup>1</sup>

<sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan

<sup>2</sup>National Nano Device Laboratories, Hsinchu 300, Taiwan

E-mail: hclin@faculty.nctu.edu.tw

Received August 6, 2013; accepted October 9, 2013; published online December 16, 2013

Gate-all-around (GAA) nanowire (NW) memory devices with a SiN- or Hf-based charge-trapping (CT) layer of the same thickness were studied in this work. The GAA NW devices were fabricated with planar thin-film transistors (TFTs) on the same substrate using a novel scheme without resorting to the use of advanced lithographic tools. Owing to their higher dielectric constant, the GAA NW devices with a HfO<sub>2</sub> or HfAlO CT layer show greatly enhanced programming/erasing (P/E) efficiency as compared with those with a SiN CT layer. Furthermore, the incorporation of Al into the Hf-based dielectric increases the thermal stability of the CT layer, improving retention and endurance characteristics.

#### 1. Introduction

Recently, polycrystalline silicon (poly-Si)-based devices have received much attention for the integration of nonvolatile memory cells in ultrahigh-density arrays. 1-3) Moreover, the low-temperature fabrication and high flexibility of poly-Si field-effect transistors (FETs) make such FETs feasible for integration with other circuit components, such as drivers, converters, processors, and memories, on the same chip or panel. 4-6) Among a number of flash memories, the gate-allaround (GAA) nanowire (NW) charge-trapping (CT)-type memory is considered to be one of the most promising structures for future NAND flash technologies.<sup>7,8)</sup> Due to its enhanced gate controllability, the GAA NW device shows excellent electrical characteristics, such as a steep subthreshold swing (~200 mV/dec or smaller), a high ON/OFF current ratio (>107), and a high immunity against shortchannel effects.<sup>9,10)</sup> Furthermore, owing to the tiny NW channel, a small numbers of discrete trapped charges in the trapping layer can result in a large sensing window. The NW memory devices also show a lower programming/erasing (P/E) operation voltage and a much higher speed than the planar memory devices. 11,12)

Recently, high- $\kappa$  dielectrics, such as HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, have been explored as materials to replace nitride in the SONOS CT-type memory. 13,14) Compared with nitride, the high- $\kappa$ trapping layer can improve the P/E efficiency and enlarge the programming window owing to its reduced equivalent oxide thickness (EOT) and higher charge-trapping density. 15) Furthermore, the reduced electric field across the blocking oxide also resolves the overerasing issue. From previous studies, 16,17) the HfO<sub>2</sub> CT layer shows a high P/E efficiency but a low retention level because of its liability to recrystallize. On the other hand, the Al<sub>2</sub>O<sub>3</sub> CT layer shows a low P/E efficiency but a high retention level owing to its deep trap states. 18) It has also been reported that HfAlO is a promising material with a high crystallization temperature and can preserve the specific advantages associated with  $HfO_2$  and  $Al_2O_3$ . 17,19)

In this work, we study memory devices with a GAA NW channel and a Hf-based CT layer. In order to realize low-cost, high-performance, and low-power portable electronic products, the integration of logic circuits and memory compo-

nents on the same panel or chip is necessary. However, the fabrication of NW devices typically requires advanced lithographic tools. This is an issue in the manufacturing of flat-panel products where the device feature size is generally 5 to  $10\,\mu m$ . To address this concern, we propose a simple approach that is capable of fabricating planar and NW poly-Si devices simultaneously without resorting to the use of advanced lithographic tools. Greatly enhanced P/E efficiency and retention characteristics of the GAA NW structure with respect to the planar counterpart of the poly-Si devices are clearly evidenced by the measured results.

#### 2. Device fabrication

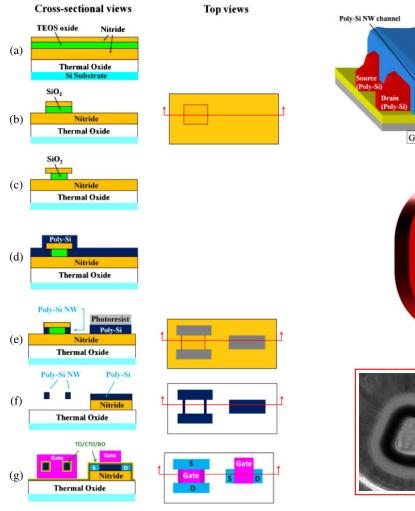

Figure 1 shows the process sequence for fabricating planar poly-Si thin-film transistors (TFTs) together with the GAA NW CT-type memory device simultaneously. In addition, the cross-sectional view of the device structure and the top view of the device layout at key steps are also shown to help elucidate the process features. The fabrication began on a Si wafer capped with a thick thermal oxide layer to simulate a glass substrate. First, 80-nm-thick silicon nitride, 30nm-thick tetraethoxysilane (TEOS) oxide, and 30-nm-thick silicon nitride layers were deposited on the wafer surface sequentially by low-pressure chemical vapor deposition (LPCVD), as shown in Fig. 1(a). After a conventional lithographic process, anisotropic dry etching was performed to etch the nitride and TEOS oxide layers to form a dummy pattern on the surface, as shown in Fig. 1(b). Then, HF-based wet etching was performed to selectively remove the oxide layer from the sidewall of the stack and form cavities underneath the top nitride layer at the sidewall of the dummy structure, as shown in Fig. 1(c). This was followed by the deposition of a 100 nm amorphous silicon (a-Si) layer by LPCVD, and the cavities were fully refilled with the a-Si layer that was subsequently transformed into a polycrystalline phase by solid-phase crystallization (SPC) at 600 °C in N<sub>2</sub> ambient for 24 h, as shown in Fig. 1(d). Afterwards, photoresist (PR) patterns were generated to cover the source/ drain (S/D) regions of the NW memory device and the active region of the planar device [see Fig. 1(e)], followed by an anisotropic dry etching process to define these regions. The Si film contained in the cavities remained after the etching process and subsequently formed the NW channels. When

**Fig. 1.** (Color online) Schematic diagrams of the fabrication process of planar TFTs and GAA NW HfAlO CT memory devices. The left figures show cross-sectional views of the devices at key steps, and the right figures are the corresponding top views.

**Table I.** Sample and material/thickness for the dielectric stack and electrode layer. The atomic ratio of HfAlO is Hf 14%: Al 30%: O 56%.

| Sample split | Tunnel oxide (3 nm) | CT layer (10 nm) | Blocking oxide (11 nm) | Gate electrode (150 nm) |

|--------------|---------------------|------------------|------------------------|-------------------------|

| SiN          | $SiO_2$             | SiN              | SiO <sub>2</sub>       | n <sup>+</sup> poly-Si  |

| $HfO_2$      | $SiO_2$             | $HfO_2$          | $Al_2O_3$              | TiN                     |

| HfAlO        | $SiO_2$             | HfAlO            | $Al_2O_3$              | TiN                     |

the top nitride, side TEOS oxide, and bottom nitride layers were selectively removed, the Si NWs hung between the source and drain regions, as shown in Fig. 1(f). Then, a stack consisting of tunnel oxide/CT layer/blocking oxide (3 nm/10 nm/11 nm) and gate layers was sequentially deposited. Three types of memory devices with various dielectric stacks and gate electrodes were fabricated in this work. Details of their structural conditions are shown in Table I. The TEOS oxide layer deposited by LPCVD was used as the tunnel oxide layer. The CT layers for the three types of memory devices are SiN, HfO<sub>2</sub>, and HfAlO (the atomic ratio of Hf/Al/O is 0.14/0.30/0.56). SiN was prepared by LPCVD, while both HfO<sub>2</sub> and HfAlO were prepared by atomic layer deposition (ALD). For the HfO<sub>2</sub> and HfAlO splits, an Al<sub>2</sub>O<sub>3</sub> blocking oxide layer was also deposited by ALD.

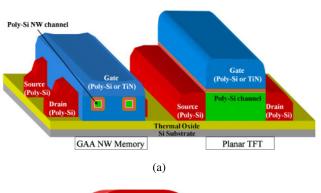

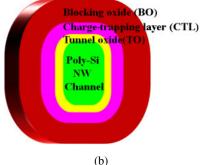

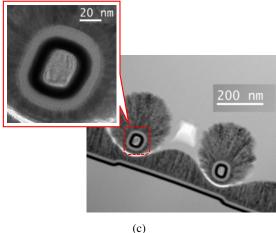

**Fig. 2.** (Color online) (a) Stereoscopic view of the completed GAA NW and planar devices. (b) Channel cross sections of the GAA NW CT-type device under various TO/CTL/BO and gate conditions. (c) Cross-sectional TEM image of a NW device with HfAlO as the CT layer.

The gate electrode was subsequently defined by dry etching, and then self-aligned phosphorus ion implantation ( $25\,\mathrm{keV}$ ,  $2\times10^{15}\,\mathrm{cm^{-2}}$ ) was carried out to dope the S/D regions of the devices, as shown in Fig. 1(g). Finally, a passivation oxide layer was deposited to cover the fabricated devices, followed by normal metallization steps to form Al–Si–Cu metal contacts. Finally, after the deposition of gate dielectrics and electrodes, all devices were treated by postmetallization annealing (PMA) at  $600\,^{\circ}\mathrm{C}$  for  $30\,\mathrm{s}$ .

A stereoscopic view of the completed GAA NW and planar devices is shown in Fig. 2(a). Figure 2(b) shows the channel cross section of the GAA NW CT-type device. Various tunnel oxide/charge trapping layer/blocking oxide (TO/CTL/BO) and gate conditions are shown in Table I. A transmission electron microscopy (TEM) image of a NW device with HfAlO as the CT layer is shown in Fig. 2(c).

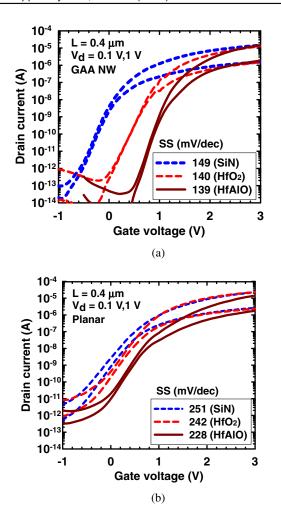

Fig. 3. (Color online) Transfer characteristics of (a) GAA and (b) planar devices with HfAlO,  $HfO_2$ , and SiN CT layers.

#### 3. Results and discussion

#### 3.1 Basic electrical characteristics

With the proposed scheme, conventional planar and GAA NW devices are fabricated and integrated easily on the same substrate. According to the process conditions mentioned in the previous section, the major split condition of the fabrication is the CT dielectric material; thus, in the following analysis and discussion, we simply use the CT dielectric to denote each split. Figures 3(a) and 3(b) show the transfer characteristics of all splits of the devices with GAA NW and planar structures, respectively. The channel lengths of these devices are 0.4 µm. Good device characteristics are demonstrated in both types of structures. The shift in threshold voltage  $(V_{th})$  is attributed to the differences in the gate workfunction and fixed charge density in the CT dielectric. However, among the devices with the same CT dielectric, the GAA NW device always shows better short-channel characteristics than its planar counterpart, such as a smaller subthreshold swing (SS <150 mV/dec), negligible draininduced barrier lowering (DIBL) values (55.6, 12.8, and 61.1 mV/V for SiN, HfO<sub>2</sub>, and HfAlO devices, respectively), and a lower off-state leakage. This is attributed to the GAA configuration, which enhances the gate controllability over the channel potential, and the tiny NW channels, which tend to reduce the off-state leakage. 20-22) Furthermore, the

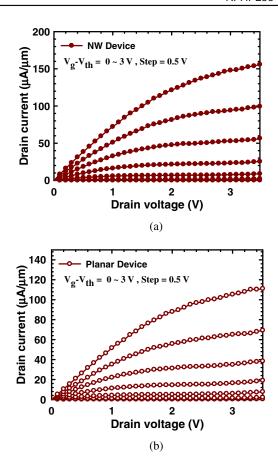

**Fig. 4.** (Color online) Output characteristics of (a) GAA device and (b) planar TFT with HfAlO CT layer.

standard deviations of the ON currents ( $I_{\rm on}$  at  $V_{\rm g}-V_{\rm th}=1.5\,\rm V$ ,  $V_{\rm d}=0.1\,\rm V$ ) of all the GAA NW devices are very small, i.e., 96.7, 103.6, and 128.3 nA for the SiN, HfO<sub>2</sub>, and HfAlO devices, respectively.

The output characteristics of the HfAlO GAA NW and planar TFTs are shown in Figs. 4(a) and 4(b), respectively. Good performance is obtained for the two devices. However, the normalized ON current is much higher for the NW TFT. This is again attributed to its tiny channel, which contains much fewer grain boundary defects than the 100-nm-thick channel of its planar counterpart.<sup>23)</sup> It is well known that the transport of carriers in a poly-Si channel is greatly impeded by the potential barrier at the grain boundaries.<sup>24,25)</sup> It was pointed out previously<sup>26)</sup> that the modulation of the barrier height at the grain boundaries by the gate bias is more efficient in a multigate NW device than in planar devices. This explains why the drain current of the GAA NW device outperforms that of the planar device, as shown in Figs. 4(a) and 4(b).

### 3.2 P/E characteristics

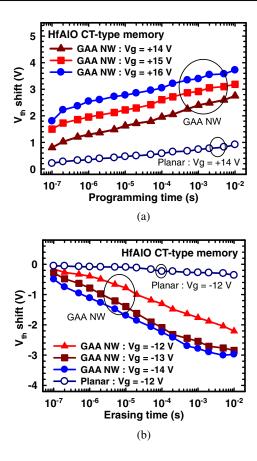

For P/E operations, a high gate voltage is applied while grounding both the source and the drain. For simplicity,  $V_{\rm th}$  is obtained from the transfer curves with the drain current of  $10^{-9}$  A at  $V_{\rm d}$  of 0.1 V. Figure 5(a) shows the  $V_{\rm th}$  shift versus the programming time for NW devices with a HfAlO CT layer programmed at 14, 15, and 16 V. To illustrate the improvement of the GAA NW configuration, the characteristics of the planar counterpart programmed at 14 V are also

Fig. 5. (Color online)  $V_{\rm th}$  shift as a function of (a) programming time and (b) erasing time for GAA NW devices with HfAlO CT layer at different voltages. The results for the planar device stressed at 14 and -12 V are also shown in (a) and (b), respectively.

included in the figure. Owing to the higher electric field across the tunnel oxide layer that resulted from the use of the NW channel,<sup>27)</sup> the GAA NW devices exhibit an enhanced operation efficiency as compared with the planar one and achieve a 3 V shift in 50 µs at the gate bias of 16 V. The erasing characteristics of the programmed HfAlO GAA NW devices are also studied. Figure 5(b) shows the results of the  $V_{\rm th}$  shift of HfAlO GAA NW devices as a function of erasing time at the gate biases of -12, -13, and -14 V. The erasing characteristic of a planar counterpart is also shown in Fig. 5(b). Still, the HfAlO GAA NW devices show a higher erasing speed than the planar ones and achieve a shift of >2 V in 100  $\mu$ s at the gate bias of -13 V. It can be seen that the rate of the  $V_{\rm th}$  shift decreases when the erasing time is longer than 0.5 ms, which is presumably related to the injection of electrons from the gate.<sup>17)</sup>

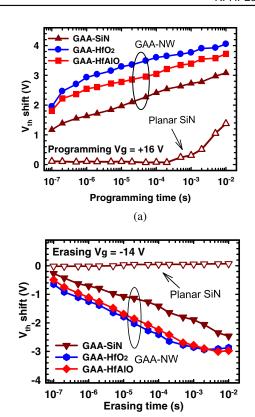

To further illustrate the merits of the high- $\kappa$  CT layer and GAA configuration, typical P/E characteristics of the NW devices with various CT layers and planar SONOS devices are shown and compared in Figs. 6(a) and 6(b). The P/E performance of the conventional planar SiN device clearly lags far behind that of the GAA NW ones. Furthermore, among the three splits of GAA NW devices, the HfO<sub>2</sub> split shows the highest efficiency, while the HfAlO split exhibits comparable performance, indicating that the P/E speed of the HfAlO split is similar to that of HfO<sub>2</sub> split. This is attributed to the higher electric field across the tunnel oxide layer that resulted from the use of thinner EOTs; thus, the HfO<sub>2</sub> and HfAlO devices

**Fig. 6.** (Color online)  $V_{\rm th}$  shift as a function of programming time for the three splits of GAA NW devices stressed at (a) 16 and (b) -14 V. The results for a planar SONOS device are also shown.

(b)

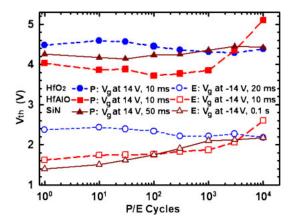

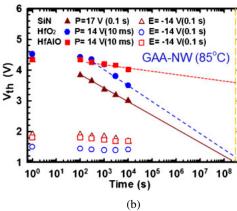

**Fig. 7.** (Color online) Endurance characteristics for the three splits of the fabricated devices at room temperature. The solid and open symbols stand for the threshold voltages in the programmed and erased states, respectively.

exhibit a greatly enhanced operation efficiency as compared with the SiN GAA device.

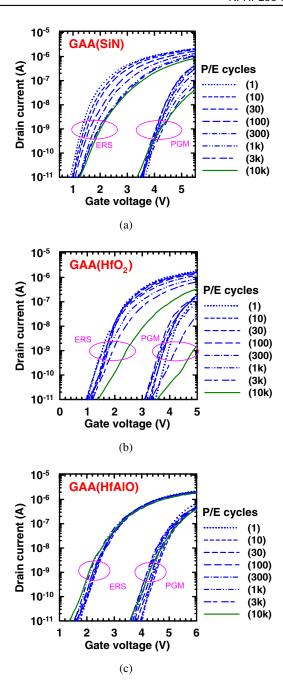

The endurance characteristics of the three splits of the GAA NW devices are shown in Fig. 7. The P/E conditions used in each split to create comparable windows are also given in the figure. It is seen that all the devices maintain acceptable memory windows after  $10^4$  P/E cycles. Nevertheless, the memory window of the SiN memory device shrinks slightly, primarily owing to the increase in  $V_{\rm th}$  for the erased state. The  $V_{\rm th}$  of the two logic states of the HfO<sub>2</sub> device clearly increases after  $10^3$  P/E cycles. To gain insights into the origins of the increase in  $V_{\rm th}$  for the HfO<sub>2</sub> device after

10<sup>3</sup> P/E cycles, we inspected the evolution of transfer characteristics after various numbers of P/E cycles. Figure 8 shows transfer characteristics of the three GAA NW devices after various numbers of P/E cycles (1 to  $10^4$ ). It is clear that the SS values of the SiN and HfO2 devices degrade markedly after 10<sup>3</sup> P/E cycles, while the HfAlO GAA NW device exhibits only minor changes even after 10<sup>4</sup> P/E cycles. In the SiN GAA memory device, the lowest P/E efficiency is obtained [as shown in Figs. 6(a) and 6(b)]. In order to obtain a memory window comparable to those of the Hf-based splits, a much longer P/E stress time on the SiN device is needed. This is believed to be responsible for the degradation of SS in Fig. 8(a). The increase in  $V_{\rm th}$  for the SiN device in the erased state after 100 P/E cycles is attributed to the largest SS value and the accumulation of residual charges in the SiN device during the P/E operations.<sup>28)</sup>

In the HfO<sub>2</sub> GAA device, the most severe degradation of SS and the largest drift in  $V_{\rm th}$  after  $10^4$  P/E cycles are observed among all the splits, as shown in Fig. 8(b). The severe degradation of SS should be related to the generation of extra interface state traps as well as nonuniform charge trapping. The situation is significantly improved when HfAlO is used instead of HfO<sub>2</sub> as the CT layer, as shown in Fig. 8(c). The different outcomes of the two splits are attributed to the different crystallinities of the CT layers. It was reported that a HfO2 film starts to crystallize at 300 °C, <sup>29,30)</sup> while a HfAlO film remains amorphous even after annealing at 800 °C for a considerable period. 17,31) Therefore, the PMA treatment (600 °C) in the fabrication process should make the HfO<sub>2</sub> trapping layer polycrystalline and generate grain boundaries (GBs) in the thin film. Since the defect density is high at or near the GBs, the use of the polycrystalline CT layer may result in a nonuniform distribution of the charges stored inside the layer. The excessive charges stored in or near the GBs should leak out easily owing to the increase in local electric potential. As a result, after a sufficient number of P/E cycles, the nearby tunnel oxide layer should experience far more carrier tunneling events than elsewhere and thus more damage. This leads to the degradation observed in the *I–V* curves. By incorporating Al into the dielectric, the thermal stability is promoted by increasing the recrystallization temperature to 800 °C. Therefore, in contrast to the HfO<sub>2</sub> device, the HfAlO one shows the best endurance characteristics and exhibits minor changes in transfer characteristics even after 10<sup>4</sup> P/E cycles.

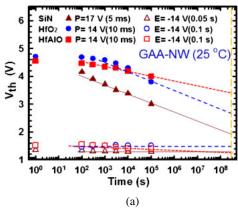

Figures 9(a) and 9(b) show the retention characteristics of the three splits of the GAA NW devices at 25 and 85 °C, respectively. The HfAlO device clearly outperforms the SiN and HfO<sub>2</sub> ones according to the figure. The extrapolated window after ten years for the HfAlO device is about 2.1 V, which is much larger than those of the HfO<sub>2</sub> ( $\sim$ 1 V) and SiN ( $\sim$ 0.6 V) devices. As compared with the SiN split, the Hf-based ones show better retention performance because of the deeper traps in the trapping layers. <sup>16)</sup> Furthermore, as compared with the HfO<sub>2</sub> split, the HfAlO split shows outstanding retention performance. Such an improvement is also a result of the higher crystallization temperature.

# 4. Conclusions

GAA NW CT-type memory devices with various CT materials were characterized. These devices were fabricated

**Fig. 8.** (Color online) Subthreshold characteristics of (a) SiN, (b) HfO<sub>2</sub>, and (c) HfAlO CT-type GAA devices measured after various numbers of P/E cycles. Among them, the HfAlO device shows the best endurance characteristics, such as the smallest shift in SS and drift in  $V_{\rm th}$  even after  $10^4$  P/E cycles.

on the same substrate with planar TFT devices using a process that can easily be implemented in a modern manufacturing process. Equipped with a GAA configuration and a poly-Si NW channel, the devices with a HfO<sub>2</sub> CT medium show a high P/E speed but low retention and endurance characteristics. Nonuniform charge trapping in the polycrystalline HfO<sub>2</sub> trapping layer is believed to be responsible for the above reliability issues. In contrast, the memory device with the HfAlO CT layer shows comparable P/E efficiency but superior retention and endurance characteristics as compared with the HfO<sub>2</sub> device. The improvements are attributed to the retardation of recrystallization with the incorporation of Al into the Hf-based dielectric.

**Fig. 9.** (Color online) Retention characteristics for the three splits of the fabricated devices at (a) 25 and (b) 85 °C. The HfAlO split shows superior data retention characteristics.

## Acknowledgments

This work was supported in part by the National Science Council, Taiwan (No. NSC-102-2221-E-009-097-MY3), the NCTU-UCB I-RiCE Program (No. NSC-102-2911-I-009-302), and the Ministry of Education in Taiwan under the ATU Program.

- R. Katsumata, M. Kito, Y. Fukuzumi, M. Kido, H. Tanaka, Y. Komori, M. Ishiduki, J. Matsunami, T. Fujiwara, Y. Nagata, L. Zhang, Y. Iwata, R. Kirisawa, H. Aochi, and A. Nitayama, Symp. VLSI Tech. Dig., 2009, p. 136.

- J. Jang, H. S. Kim, W. Cho, H. Cho, J. Kim, S. I. Shim, Y. Jang, J. H. Jeong, B. K. Son, D. W. Kim, K. Kim, J. J. Shim, J. S. Lim, K. H. Kim, S. Y. Yi, J. Y. Lim, D. Chung, H. C. Moon, S. Hwang, J. W. Lee, Y. H. Son, U. I. Chung, and W. S. Lee, Symp. VLSI Tech. Dig., 2009, p. 192.

- 3) S. Imanaga and H. Aozasa, Jpn. J. Appl. Phys. 43, 5186 (2004).

- C. A. Choi, C. S. Lee, W. I. Jang, Y. S. Hong, J. H. Lee, and B. K. Sohn, Jpn. J. Appl. Phys. 38, 3693 (1999).

- J.-K. Lin, C.-Y. Chang, H.-S. Huang, K.-L. Chen, and D.-C. Kuo, Jpn. J. Appl. Phys. 33, 2513 (1994).

- E.-K. Lai, H.-T. Lue, Y.-H. Hsiao, J.-Y. Hsieh, S.-C. Lee, C.-P. Lu, S.-Y. Wang, L.-W. Yang, K.-C. Chen, J. Gong, K.-Y. Hsieh, J. Ku, R. Liu, and C.-Y. Lu, Symp. VLSI Tech. Dig., 2006, p. 46.

- 7) H. Tanaka, M. Kido, K. Yahashi, M. Oomura, R. Katsumata, M. Kito, Y. Fukuzumi, M. Sato, Y. Nagata, Y. Matsuoka, Y. Iwata, H. Aochi, and A. Nitayama, Symp. VLSI Tech. Dig., 2007, p. 14.

- 8) H. Aochi, Proc. IEEE Int. Memory Workshop (IMW), 2009, p. 1.

- J. Fu, K. D. Buddharaju, S. H. G. Teo, C. Zhu, M. B. Yu, N. Singh, G. Q. Lo, N. Balasubramanian, and D. L. Kwong, IEDM Tech. Dig., 2007, p. 79.

- W. C. Chen, H. C. Lin, and T. Y. Huang, Jpn. J. Appl. Phys. 50, 085002 (2011).

- 11) K. H. Yeo, K. H. Cho, M. Li, S. D. Suk, Y.-Y. Yeoh, M.-S. Kim, H. Bae, J.-M. Lee, S.-K. Sung, J. Seo, B. Park, D.-W. Kim, D. Park, and W. S. Lee, Symp. VLSI Tech. Dig., 2008, p. 138.

- H. H. Hsu, T. W. Liu, C. D. Lin, C. Kuo-Jung, T. Y. Huang, and H. C. Lin, Proc. Int. Symp. VLSI Technology, Systems and Applications (VLSI-TSA), 2009, p. 148.

- S. Maikap, P.-J. Tzeng, T.-Y. Wang, H.-Y. Lee, C.-H. Lin, C.-C. Wang, L.-S. Lee, J.-R. Yang, and M.-J. Tsai, Jpn. J. Appl. Phys. 46, 1803 (2007).

- L. Larcher, A. Padovani, V. della Marca, P. Pavan, and A. Bertacchini, Proc. Int. Symp. VLSI Technology, Systems and Applications (VLSI-TSA), 2010, p. 53.

- G. Zhang and W. J. Yoo, Proc. 8th Int. Conf. Solid-State and Integrated-Circuit Technology (ICSICT), 2007, p. 781.

- 16) T. Sugizaki, M. Kobayashi, M. Ishidao, H. Minakata, M. Yamaguchi, Y. Tamura, Y. Sugiyama, T. Nakanishi, and H. Tanaka, Symp. VLSI Tech. Dig., 2003, p. 27.

- 17) Y. N. Tan, W. K. Chim, W. K. Choi, M. S. Joo, and B. J. Cho, IEEE Trans. Electron Devices 53, 654 (2006).

- 18) Y. N. Tan, W. K. Chim, W. K. Choi, M. S. Joo, T. H. Ng, and B. J. Cho, IEDM Tech. Dig., 2004, p. 889.

- 19) M. Cho, H. B. Park, J. Park, C. S. Hwang, J.-C. Lee, S.-J. Oh, J. Jeong, K. S. Hyun, H.-S. Kang, Y.-W. Kim, and J.-H. Lee, J. Appl. Phys. 94, 2563 (2003).

- H. H. Hsu, H. C. Lin, K. H. Lee, J. F. Huang, and T. Y. Huang, Proc. Int. Symp. VLSI Technology, Systems and Applications (VLSI-TSA), 2008, p. 101.

- H. C. Lin, K. L. Yeh, M. H. Lee, W. Lee, W. J. Lin, and T. Y. Huang, Tech. Dig. 2003 Int. Workshop Active-Matrix Liquid Crystal Displays (AMLCD), 2003, p. 247.

- 22) Y. B. Kim, Trans. Electr. Electron. Mater. 10, 23 (2009).

- H.-C. Lin, M.-H. Lee, C.-J. Su, and S.-W. Shen, IEEE Trans. Electron Devices 53, 2471 (2006).

- 24) J. Y. W. Seto, J. Appl. Phys. 46, 5247 (1975).

- K. Y. Choi, J. S. Yoo, M. K. Han, and Y. S. Kim, Jpn. J. Appl. Phys. 35, 915 (1996).

- Z. M. Lin, H. C. Lin, W. C. Chen, and T. Y. Huang, Appl. Phys. Lett. 96, 072108 (2010).

- P.-C. Huang, L.-A. Chen, and J.-T. Sheu, IEEE Electron Device Lett. 31, 216 (2010).

- M. She, H. Takeuchi, and T. J. King, IEEE Electron Device Lett. 24, 309 (2003).

- 29) W. J. Zhu, T. Tamagawa, M. Gibson, T. Furukawa, and T. P. Ma, IEEE Electron Device Lett. 32, 461 (2011).

- S. Stemmer, Y. Li, B. Foran, P. S. Lysaght, S. K. Streiffer, P. Fuoss, and S. Seifert, Appl. Phys. Lett. 83, 3141 (2003).

- R. J. Potter, P. A. Marshall, P. R. Chalker, S. Taylor, A. C. Jones, T. C. Q. Noakes, and P. Bailey, Appl. Phys. Lett. 84, 4119 (2004).