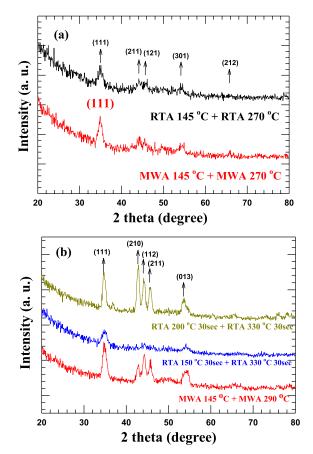

# Low-Temperature Microwave Annealing Processes for Future IC Fabrication—A Review

Yao-Jen Lee, Ta-Chun Cho, Shang-Shiun Chuang, Fu-Kuo Hsueh, Yu-Lun Lu, Po-Jung Sung, Hsiu-Chih Chen, Michael I. Current, Tseung-Yuen Tseng, Fellow, IEEE, Tien-Sheng Chao, Chenming Hu, Fellow, IEEE, and Fu-Liang Yang

Abstract-Microwave annealing (MWA) and rapid thermal annealing (RTA) of dopants in implanted Si are compared in their abilities to produce very shallow and highly activated junctions. First, arsenic (As), phosphorus (P), and BF2 implants in Si substrate were annealed by MWA at temperatures below 550 °C. Next, enhancing the substitutional carbon concentration ([C]<sub>sub</sub>) by cluster carbon implantation in (100) Si substrates with MWA or RTA techniques was investigated. Annealing temperatures and time effects were studied. Different formation mechanisms of  $SiC_x$  layer were observed. In addition, substrate temperature is an important factor for dopant activation during MWA and in situ doped a-Si on oxide/Si substrate or glass were compared to elucidate the substrate temperature effect. After the discussion of dopant activation in Si substrates, low temperature formation of ultrathin NiGe layer is presented. Ultrathin NiGe films with low sheet resistance have been demonstrated with a novel twostep MWA process. In the two-step MWA process, the first step anneals the sample with low power MWA, and the second step applies higher power MWA for reducing sheet resistance. During fixed-frequency microwave heating, standing wave patterns may be present in the MWA chamber resulting in nodes and antinodes and thermal variations over the process wafer. Therefore, the effects of Si or quartz susceptor wafers on dopant activation and sheet resistance uniformity during fixed-frequency MWA were investigated.

Index Terms—Dopant activation, low temperature, microwave, microwave annealing (MWA), NiGe, solid phase epitaxial growth (SPEG), temperature effect, uniformity.

### I. INTRODUCTION

T IS expected that metal—oxide—semiconductor field-effect transistors (MOSFETs) will scale to under 14 nm by

Manuscript received October 2, 2013; revised December 8, 2013; accepted January 12, 2014. Date of current version February 20, 2014. This work was supported by the National Science Council (NSC), Taiwan, under Grant NSC-101-2221-E-492-020. The review of this paper was arranged by Editor H. Shang.

Y.-J. Lee is with the National Nano Device Laboratories, Hsinchu 30010, Taiwan, and also with the Department of Physics, National Chung Hsing University, Taichung 402, Taiwan (e-mail: yjlee@narlabs.org.tw).

- T.-C. Cho, Y.-L. Lu, and T.-S. Chao are with the Department of Electrophysics, National Chiao-Tung University, Hsinchu 300, Taiwan.

- S.-S. Chuang and T.-Y. Tseng are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan.

- F.-K. Hsueh and P.-J. Sung are with the National Nano Device Laboratories, Hsinchu 30010, Taiwan, and also with the Department of Electrophysics, National Chiao-Tung University, Hsinchu 300, Taiwan.

- H.-C. Chen is with the National Nano Device Laboratories, Hsinchu 30010,

- M. I. Current is with Current Scientific, San Jose, CA 95124 USA.

- C. Hu is with the Graduate School, University of California, Berkeley, CA 94720 USA.

- F.-L. Yang is with Academia Sinica, Taipei 11529, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2014.2300898

2017 to meet the International Technology Roadmap for Semiconductors 2011 (ITRS 2011) [1]. A key technical challenge is to form highly activated doped junctions with depths of <10 nm. However, the suppression of dopant diffusion is challenging, especially in the source/drain (S/D) extension junctions with very shallow junction depths. Shallow junction depths and high resistivity would increase parasitic resistance and lower circuits drive currents and speeds [2]. To keep the junction and contact resistances low, high temperature anneals have been used to electrically activate implanted dopants and repair lattice damages created during ion implantation process to reduce junction leakage currents. However, any high temperature process after implantation causes the diffusion and redistribution of dopants, and the high diffusion rate makes a shallow junction depth hard to achieve.

Therefore, in order to avoid dopant diffusion effect, that is dominant at high anneal temperatures, low-temperature annealing with microwave excitation appears to offer promises microwave annealing (MWA) process may be an alternative to other rapid thermal processing methods in silicon processing [3]–[9]. Microwaves could repair the damages caused by high-dose implantation. Furthermore, the dopant could be also activated in semiconductor by MWA process.

Microwaves generate rapidly changing electric fields and will generally heat any material containing mobile electric charges, such as polar molecules in a solvent or conducting ions in a solid. Polar solvents are heated as their component molecules are forced to rotate with the field and lose energy in collisions. Semiconducting and conducting samples heat when ions or electrons within them form an electric current in response to the electric field and energy is lost through resistive heating of the material [10], [11]. The mechanisms of microwave power absorption in semiconductors include ohmic heating and dielectric relaxation [12]–[14]. In particular, at lower frequencies (<10 GHz), ohmic heating dominates.

MWA process has been shown to provide a lower temperature process that restrains diffusion and results in good activation [9]; this cannot be explained with simple heating by the microwaves.

Compared with conventional heating, microwave heating has different and special effects, including specific microwave effects and nonthermal microwave effects [15]–[19]. Specific microwave effects involve selective heating of specific materials, rapid heating rates and temperature gradients, the elimination of wall effects, and the superheating of solvents.

About the nonthermal microwave effects, it is generally considered to result from interaction of the electric field

with specific reaction molecules, and a numerical model based on continuum equation was applied to investigate the unusual observations in microwave chemistry [20]. As the term suggests, these effects are the result of the transfer of microwave energy into the annealed material in addition to thermal heating, associated with the amplitude of randomly oriented atomic vibrations in the solid. These other forms of energy transfer include changes to the chemical energy stored in molecular structure and bonding orbitals of the solid as well as coherently directed atom motion, such as atomic rearrangements at the growing crystal material interface at the boundary of an amorphous layer. Because the time for energy redistribution between molecules in a liquid is much less than the period of a microwave oscillation nonthermal effects are considered to be nonexistent in liquids [16], [17]. Therefore, it is considered that a mechanism is analogous to enhanced ionic transport. But the transport motion is in short range motion just within a lattice constant. If the impurity ion or surrounding defect Si atoms (they would be partially ionized due to the defect state) move around a lattice spacing, they have moved far enough to recrystallize [21]–[23]. However, the nonthermal effects of microwaves are the considerable issue and still controversial. Therefore, extensive research about microwave effects will be necessary to truly understand these related phenomena [16].

Therefore, this paper includes the in-depth studies of several silicon MWA processes. First of all, As, P, BF<sub>2</sub>, and cluster carbon activation in implanted Si substrate by low temperature MWA or rapid thermal annealing (RTA) are compared in this paper [9]. Next, substrate temperature effects on MWA process are studied. Absorption of microwave energy by glass substrates is negligible due to its low loss factor, and the glass substrate will be in a lower temperature state. Activation of *in situ* doped amorphous Si films deposited on SiO<sub>2</sub>/Si substrate and on glass by MWA is compared for the elucidation of the effects of substrate temperature.

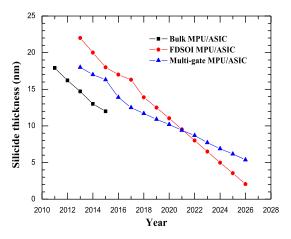

The resistances of source, drain, and gate are becoming more detrimentally limiting of IC performance with the downscaled device dimensions. The self-aligned silicide technique must be improved to reduce the series resistance of a device. ITRS 2011 stated that Ni silicide had encountered the barriers of both lowering the thickness and phase issue. Thicker silicide thickness would consume the doped region of the S/D junction and contact the Si substrate causing junction leakage. Therefore, reducing the silicide thickness is a critical issue to solve, as shown in Fig. 1. NiSi currently faces difficult tradeoffs between thickness and sheet resistance. In addition, germanium substrate is a potential material to replace silicon because of its higher mobility for electrons and holes than Si. NiGe still faces difficult tradeoffs between thickness and sheet resistance. In this paper, for similar temperature profiles with MWA and RTA, a lower sheet resistance (Rs) was obtained by MWA due to a higher crystallization level of NiGe without sacrificing thickness and quality. In addition, lower Rs could be obtained by increasing the input MWA power and shortening the process time. This technique is promising for achieving 12-nm node CMOS and beyond.

Fig. 1. Silicide thickness requirement by ITRS 2011.

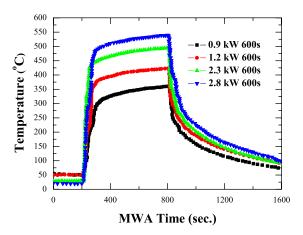

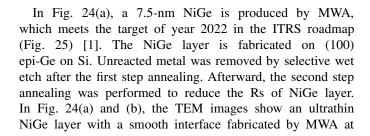

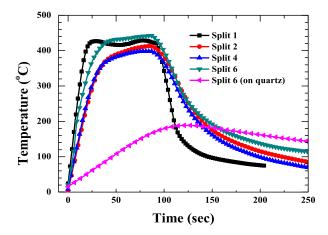

Fig. 2. Comparisons of temperature profiles versus MWA time at different MWA power. The MWA time was defined as the period when the microwave power was turned on.

Finally, microwave heating is able to heat the target compounds without heating the entire furnace or chamber, which saves time and energy. It is also able to heat sufficiently thin objects volumetrically producing more uniform heating. However, due to the design of most microwave ovens and to uneven absorption by the object being heated, the microwave field is usually nonuniform and localized superheating occurs. Variable frequency microwave methods to improve thermal uniformity have been proposed and studied [24]. In this paper [25], the coupling effects of Si and quartz susceptor wafers to improve the uniformity and dopant activation efficiency for fixed-frequency MWA process are presented.

# II. SOLID PHASE EPITAXIAL REGROWTH WITH DOPANT ACTIVATION BY MWA AND RTA IN IMPLANTED Si

MWA is a volumetric heating process. The EM wave penetrates the wafer, resulting in a lower thermal gradient in the wafer during MWA. The temperature profiles versus annealing time are shown in Fig. 2. The MWA processing time is defined as the period when the microwave power was turned on. It is noted for the first 50 s of the MWA period, the temperature increased rapidly, which may be attributed to

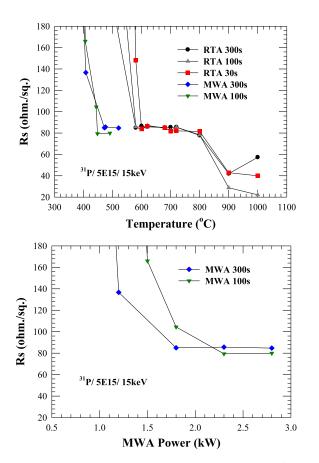

Fig. 3. (a) Rs of P implant splits at 15 keV with a dose of  $5 \times 10^{15}$  ion/cm<sup>2</sup> versus different annealing temperatures. (b) Rs of P implant splits at 15 keV with a dose of  $5 \times 10^{15}$  ion/cm<sup>2</sup> versus different MWA power.

the power dissipation by the process wafer and transfer into heat. The equation of power dissipation is

$$P = \omega \varepsilon_0 \varepsilon_{\text{eff}}^{"} E_{\text{rms}}^2 \tag{1}$$

where  $\omega$  is the microwave frequency,  $\varepsilon_0$  is the dielectric constant of free space,  $\varepsilon''_{\rm eff}$  is the effective loss factor, and  $E_{\rm rms}$  is the root mean square of the electric field. In addition, the power required to raise the temperature of a mass  $\rho$  kg/m³ with the heat capacitance  $c_p$  of material from  $T_0$  °C to T °C in t seconds is

$$P = \rho c_p (T - T_0)/t. \tag{2}$$

Substituting P using (1), (2) yields

$$(T - T_0)/t = \frac{\omega \varepsilon_0 \varepsilon_{\text{eff}}'' E_{\text{rms}}^2}{\rho c_p}.$$

(3)

From Fig. 2, after the first 50 s of the MWA periods, though microwave power was still being projected into the processing chamber, the maximum temperature was close to saturation. Different implanted species, such as P, As, BF<sub>2</sub>, and cluster carbon (C<sub>7</sub>H<sub>7</sub>), are prepared for MWA. In order to evaluate the dopant characteristics in implanted silicon substrate splits, samples implanted by P (15 keV,  $1 \times 10^{14}$ – $5 \times 10^{15}$  ions/cm<sup>2</sup>), As (20 keV,  $1 \times 10^{14}$ – $5 \times 10^{15}$  ions/cm<sup>2</sup>) were prepared.

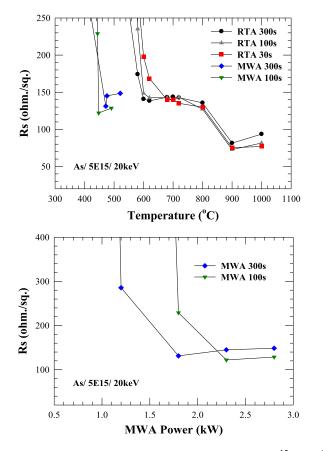

Fig. 3(a) shows Rs of P implant splits at 15 keV with a dose of  $5 \times 10^{15}$  ion/cm<sup>2</sup> for different annealing temperatures and times. The trends of Rs at different RTA temperatures suggest the presence of several possible mechanisms during the RTA process, including solid phase epitaxial growth (SPEG), deactivation, diffusion, and out-diffusion. In range of 580 °C–800 °C, stable Rs should be due to the equilibrium between activation and deactivation. The Rs begins to decrease when the temperature exceeds 800 °C due to dopant diffusion and dopant out-diffusion is seen in all splits at 1000 °C for 300 s.

Therefore, the annealing temperatures of Fig. 3(a) fall into three regions by mechanism when only the splits by RTA for 100 or 300 s are considered. The first such region lies below 580 °C and is dominated by SPEG with dopant activation. The second region is between 580 °C and 800 °C and is dominated by the equilibrium between activation and deactivation. The third region, above 800 °C, is dominated by dopant diffusion and out-diffusion. As RTA decreases to 30 s, the temperature must rise to 600 °C to reach equilibrium.

The results by MWA given in Fig. 3(a) and (b) show that a lower Rs value may be reached in just 100 s as MWA power exceeds 1.8 kW, even lower than by RTA in the SPEG and equilibrium regions. In addition, under MWA for 300 s [Fig. 3(b)], Rs magnitude is stable in the microwave power range of 1.8-2.8 kW, which indicates that the window of MWA power magnitude for stable Rs is large. As microwave power declines to 0.9 and 1.2 kW, Rs will increase dramatically. The results of Rs by MWA versus maximum substrate temperatures in Fig. 3(a), thus show that SPEG with dopant activation and equilibrium regions may be achieved without diffusion and out-diffusion regions. Therefore, based on Fig. 3(a), it is possible that there is a temperature offset between MWA and RTA due to the nonthermal microwave effect, in which the microwave energy itself directly couples to the energy modes within the lattices, assisting the SPEG and increasing dopant activation efficiency.

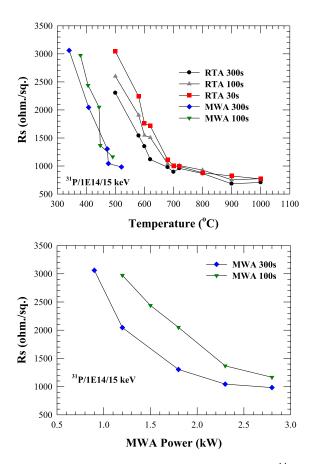

Fig. 4(a) shows the Rs of P implanted splits at 15 keV with a dose of  $1 \times 10^{14}$  ion/cm<sup>2</sup> with different annealing temperatures and time after decreasing the implanted dose to reduce the SPEG effects. Lower Rs values are obtained as the annealing temperature rises. In addition, the results by MWA given in Fig. 4(a) and (b) show that lower Rs values may be obtained by increasing the microwave power and process time. The longer MWA time of 300 s causes a reduction in Rs. Therefore, without the assistance of SPEG, activating the implanted dopant requires greater power and time. SPEG appears to shorten the MWA time and power, if the dose exceeds  $1 \times 10^{15}$  ion/cm<sup>2</sup>, indicating an amorphous layer formed by the higher dose can simultaneously enhance the SPEG with dopant activation efficiency, for 100 s only.

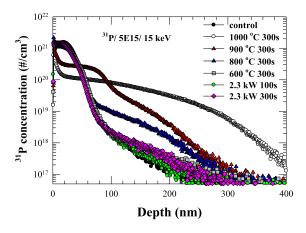

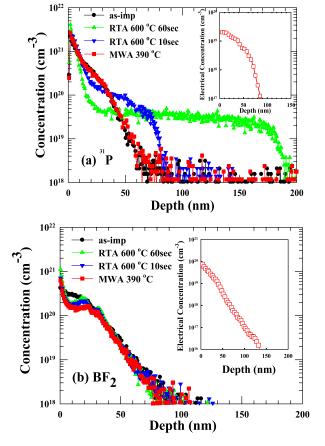

Fig. 5 shows the SIMS profiles for P (15 keV,  $5 \times 10^{15}$  ions/cm<sup>2</sup>) implants. After RTA at 800 °C for 300 s, the P profile showed diffusion in the tail region, with substantial diffusion in the tail and peak regions after RTA at 900 °C. The dopant profiles after the low temperature MWA are indistinguishable from the profile of the as-implanted split, indicating no dopant diffusion motion for these <550 °C

Fig. 4. (a) Rs of P implant splits at 15 keV with a dose of  $1 \times 10^{14}$  ion/cm<sup>2</sup> versus different annealing temperatures. (b) Rs of P implant splits at 15 keV with a dose of  $1 \times 10^{14}$  ion/cm<sup>2</sup> versus different MWA power.

Fig. 5. SIMS profiles of P concentration at a dose of  $5 \times 10^{15}$  ions/cm<sup>2</sup>. The P distribution after the RTA over 800 °C shows deeper dopant diffusion, while the MWA resulted in no significantly dopant diffusion.

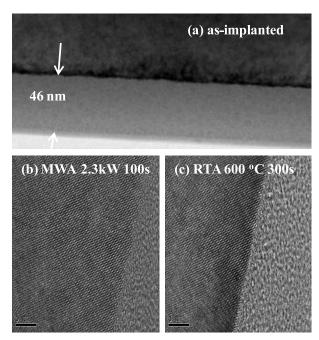

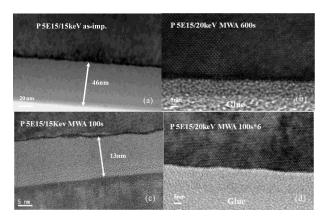

anneals. Cross-sectional transmission electron microscopy (TEM) images of P implanted samples are shown in Fig. 6. Fig. 6(a)—(c) show that the amorphous-layer thickness for P implanted layers is 46 nm, with excellent crystallinity after MWA for 100 s and RTA at 600 °C for 300 s. The kinetics and mechanisms of the crystallinity regrowth during MWA are driven by SPEG, nucleating at the a/c interface, and proceeding toward the sample surface. During the crystallization of the amorphous layer, the dopant can be activated by SPEG. In that

Fig. 6. Cross-sectional TEM pictures, P at 15 keV with  $1\times10^{15}$  ion/cm<sup>2</sup>, of (a) as-implanted, (b) MWA at 2.3 kW for 100 s, and (c) RTA at 600 °C for 300 s.

case, the dopant deactivation characteristics are not apparent, if microwave power is maintained.

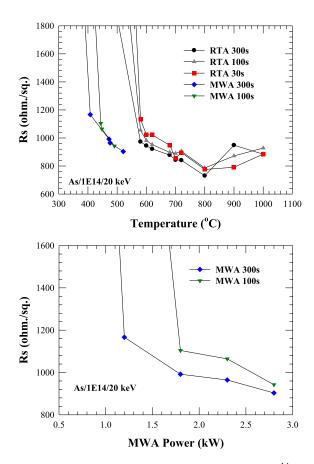

Fig. 7(a) shows the Rs of As implanted splits at 20 keV with a dose of  $5 \times 10^{15}$  ion/cm<sup>2</sup> for different annealing temperatures and times. From the trends of Rs at different annealing temperatures, the possible annealing mechanisms during the annealing process appear to be the same as those of P implants. But, this will increase the temperature necessary to obtain small and stable Rs with only a marginal dopant deactivation impact. The Rs of all splits begins to decrease at over 800 °C due to dopant diffusion. Dopant out-diffusion dominates the Rs for the split at 1000 °C for 300 s. Shorter annealing times, <300 s, suppress As out-diffusion. Therefore, the annealing temperature variations in Fig. 7(a) again show three different mechanisms by temperature, similar to the P implanted splits. However, among the RTA splits, there is a temperature offset for the splits by RTA for 30 s, indicating that the RTA processing time for the As implanted splits is a more important parameter for SPEG with As activation. Further, the MWA results given in Fig. 7(a) and (b) show that a lower Rs value may be obtained after just 100 s when MWA power exceeds 1.8 kW, even lower than by RTA in the SPEG and equilibrium regions. In addition, after MWA for 300 s [Fig. 7(b)], Rs magnitude is the lowest at 1.8 kW, and then increases due to dopant deactivation. Then, as microwave power is reduced to <1.8 kW, Rs will increase dramatically. Therefore, the results of Rs by MWA versus maximum substrate temperatures in Fig. 7(a) show that SPEG with dopant activation and equilibrium regions, but without diffusion and out-diffusion regions are possible. In addition, the magnitude of As deactivation by MWA is more apparent than by RTA.

Fig. 8(a) shows the Rs of As implanted splits at 20 keV with a dose of  $1 \times 10^{14}$  ion/cm<sup>2</sup> for different annealing

Fig. 7. (a) Rs of As implant splits at 20 keV with a dose of  $5 \times 10^{15}$  ion/cm<sup>2</sup> versus different annealing temperatures. (b) Rs of As implant splits at 20 keV with a dose  $5 \times 10^{15}$  ion/cm<sup>2</sup> versus different MWA power.

temperatures and times as the implanted dose is decreased to reduce the SPEG effects. At temperatures under 800 °C, the Rs falls as the annealing temperature rises. However, dopant deactivation and diffusion dominate Rs once the annealing temperature exceeds 800 °C. The results of MWA [Fig. 8(a) and (b)] show that increasing the microwave power and process time yields lower Rs values. Greater MWA power for longer times causes a reduction in Rs. Therefore, without the assistance of SPEG, greater power and time are necessary to activate the implanted dopant, and SPEG could shorten the MWA time and power, if the dose exceeds 1 × 10<sup>15</sup> ion/cm<sup>2</sup>. This also indicates that the amorphous layer formed by the higher dose simultaneously enhances dopant activation efficiency of the SPEG, for 100 s only.

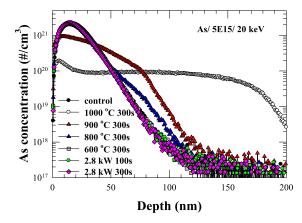

Fig. 9 shows the SIMS profiles of the As (20 keV,  $5 \times 10^{15} \, \mathrm{ions/cm^2}$ ). After RTA at 800 °C for 300 s, the As profile shows diffusion in the tail region, with substantial diffusion in the tail and peak regions after RTA over 900 °C. The dopant profiles after the low temperature MWA are indistinguishable from the profile of the as-implanted split, indicating no dopant diffusion motion for these < 550 °C anneals. The kinetics and mechanisms of the crystallinity regrowth during MWA are driven by SPEG, nucleating at the a/c interface and proceeding toward the sample surface. During the crystallization of the amorphous layer, the dopant may be activated by SPEG. The dopant will then leave the lattice sites due to its dopant

Fig. 8. (a) Rs of As implant splits at 20 keV with a dose of  $1 \times 10^{14}$  ion/cm<sup>2</sup> versus different annealing temperatures. (b) Rs of As implant splits at 20 keV with a dose of  $1 \times 10^{14}$  ion/cm<sup>2</sup> versus different MWA power.

Fig. 9. SIMS profiles of As concentration at a dose of  $5 \times 10^{15}$  ions/cm<sup>2</sup>. The As distribution after the RTA over 800 °C showed a deeper dopant diffusion, while the MWA resulted in no dopant diffusion.

deactivation characteristics, if the microwave processing time prolonged.

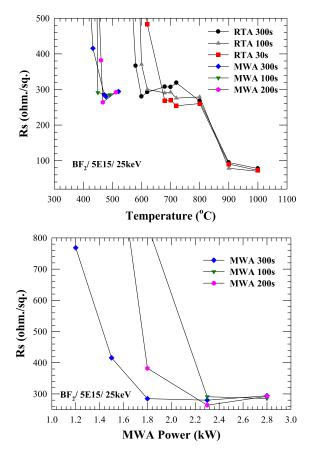

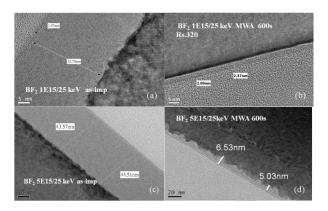

Fig. 10(a) shows the Rs of BF<sub>2</sub> implanted splits at 25 keV with a dose of  $5 \times 10^{15}$  ion/cm<sup>2</sup> for different annealing temperatures and times. By RTA, one requires higher annealing temperatures to complete the SPEG and obtain lower Rs as the annealing time declines, which indicates that the processing time of RTA for the BF<sub>2</sub> implanted splits is an important parameter for SPEG with boron activation. The crossover

Fig. 10. (a) Rs of BF<sub>2</sub> implant splits at 25 keV with a dose of  $5 \times 10^{15}$  ions/cm<sup>2</sup> versus different annealing temperatures. (b) Rs of BF<sub>2</sub> implant splits at 25 keV with a dose of  $5 \times 10^{15}$  ions/cm<sup>2</sup> versus different MWA power.

behavior of Rs may then be determined. Longer processing times result in stronger dopant deactivation impact, and Rs values are reduced due to the suppression of BF<sub>2</sub> deactivation as RTA time is reduced. The Rs begins to decrease at temperatures over 800 °C due to dopant diffusion. Therefore, as with the other dopants, As and P, the annealing temperature in Fig. 10(a) falls into three regions. In the first two regions, process time dominates Rs characteristics, including dopant action and deaction. The region over 800 °C is dominated by dopant diffusion. The MWA results [Fig. 10(a) and (b)] show a clear MWA power offset across different times, while 200 s with MWA power at 2.3 kW yields lower Rs values for all splits. As microwave power is reduced to 0.9 and 1.2 kW, Rs will increase dramatically. Therefore, the results for Rs by MWA versus maximum substrate temperatures show that it is possible to obtain SPEG with dopant activation and equilibrium regions but without diffusion and out-diffusion regions.

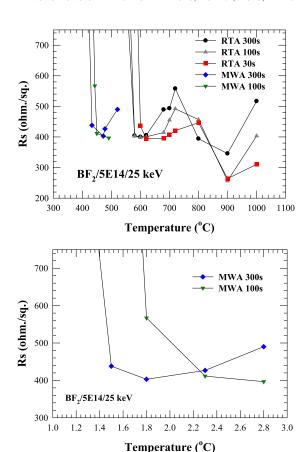

Fig. 11(a) shows the Rs of BF<sub>2</sub> implanted splits at 25 keV with a dose of  $5\times10^{14}$  ion/cm<sup>2</sup> for different annealing temperatures and times. Crossover behavior of the Rs is also depicted. Dopant deactivation is more apparent as the annealing time lengthens from 30 to 300 s, compared with the split with a dose of  $5\times10^{15}$  ion/cm<sup>2</sup>. Furthermore, the results of MWA for 300 s [Fig. 11(a) and (b)] show that Rs will increase due to dopant deactivation when the MWA power exceeds 1.8 kW. When the microwave power falls below 1.8 kW, Rs will

Fig. 11. (a) Rs of BF<sub>2</sub> implant splits at 25 keV with a dose of  $4 \times 10^{15}$  ions/cm<sup>2</sup> versus different annealing temperatures. (b) Rs of BF<sub>2</sub> implant splits at 25 keV with a dose of  $4 \times 10^{15}$  ions/cm<sup>2</sup> versus different MWA power.

increase dramatically. In addition, the magnitudes of  $BF_2$  deactivation by MWA for 300 s and RTA are very clear.

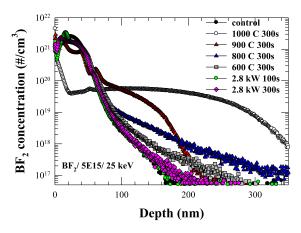

Fig. 12 shows the SIMS profiles of the BF $_2$  (25 keV,  $5 \times 10^{15}$  ions/cm $^2$ ). After RTA at 600 °C for 300 s, the BF $_2$  profile showed diffusion in the tail region, with substantial diffusion in the tail and peak regions after RTA exceeding 900 °C. The dopant profiles after the low temperature MWA are indistinguishable from the profile of the as-implanted split, indicating no dopant diffusion motion for these <550 °C anneals. During the crystallization of the amorphous layer, the dopant can be activated by SPEG. The dopant will then leave the lattice sites due to its dopant deactivation characteristics, if microwave processing time is prolonged.

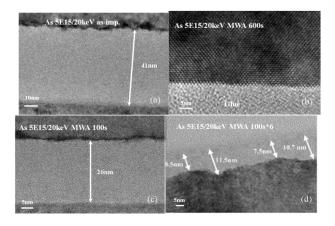

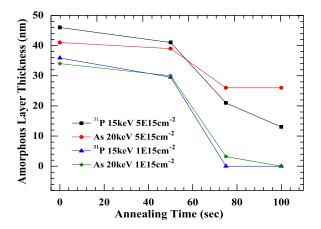

To evaluate the rate of SPEG in ion implanted silicon samples by low temperature MWA, cross-sectional TEM images were made of P (15 keV,  $5 \times 10^{15}$  ions/cm<sup>2</sup>), As (20 keV,  $5 \times 10^{15}$  ions/cm<sup>2</sup>), and BF<sub>2</sub> (25 keV,  $1-5 \times 10^{15}$  ions/cm<sup>2</sup>) implanted samples (Figs. 13–15). The amorphous region is the lightly shaded area.

After MWA for 600 s ( $T_{\rm max} \sim 480$  °C), the P, As, and BF<sub>2</sub> (25 keV,  $1 \times 10^{15}$  ions/cm<sup>2</sup>) implanted splits show the excellent crystallinity of the regrown Si layer. The kinetics and mechanisms of the crystallinity regrowth during MWA are driven by SPEG, nucleating at the a/c interface and proceeding toward the sample surface.

For the P and As implanted samples, the a/c interface remains smooth for < 50 s of MWA processing for all splits,

Fig. 12. SIMS profiles of BF $_2$  concentration at a dose of  $5 \times 10^{15}$  ions/cm $^2$ . The As distribution after the RTA over 600 °C showed a deeper dopant diffusion, while the MWA resulted in no dopant diffusion.

Fig. 13. Cross-sectional TEM pictures for P at 15 keV with  $5\times10^{15}$  ions/cm<sup>2</sup> of (a) as implanted, (b) 600 s, (c) 100 s, and (d) 100 s  $\times$  6.

Fig. 14. Cross-sectional TEM pictures for As at 20 keV with  $5\times10^{15}$  ions/cm<sup>2</sup> of (a) as implanted, (b) 600 s, (c) 100 s, and (d) 100 s  $\times$  6.

which indicates that MWA can nucleate and initialize SPEG at the a/c interface, but with relatively little a/c interface motion, due to the lower wafer temperature during the early stages of the annealing process (Fig. 2). For the second period, between 50 and 75 s, the SPEG rate and dopant activation level increase. That is, most of the dopants are effectively activated during this period. In the third period, between 75 and 100 s, rate of the SPEG of the P and As implanted samples was

Fig. 15. Cross-sectional TEM pictures for BF<sub>2</sub> (a) as implanted at 25 keV with  $1 \times 10^{15}$  ions/cm<sup>2</sup>, (b) after MWA 600 s, (c) as implanted at 25 keV with  $5 \times 10^{15}$  ions/cm<sup>-2</sup>, and (d) after MWA 600 s.

retarded. For longer annealing time, from 100 to 600 s, the remaining amorphous Si layer could regain its crystallinity due to the longer dwell times and higher processing temperatures. For BF<sub>2</sub> implanted samples, the rate of the SPEG was much slower, than other two kinds of dopants. As shown in Fig. 15, the sample of BF<sub>2</sub> (25 keV,  $1 \times 10^{15}$  ions/cm<sup>2</sup>) requires 600 s for the crystallization of the regrown Si layer, and that of BF<sub>2</sub> (25 keV,  $5 \times 10^{15}$  ions/cm<sup>2</sup>) requires over 600 s for crystallization. In the BF<sub>2</sub> implants, the high F content,  $1 \times 10^{16}$  ions/cm<sup>2</sup>, seems to be inhibiting the crystal regrowth and damage annealing process.

To investigate low (< 450 °C) temperature processing with longer anneal times, six MWA cycles of 100 s each, totaling 600 s, were also carried out. Cross-sectional TEM images of P [Fig. 13(d)] show excellent crystallinity. The crystallinity of the implanted Si layer also appears to depend on the MWA time and implanted damage if limiting the maximum temperature. However, the cross-sectional TEM images of As [Fig. 14(d)], show that the roughness of the regrowing a/c interfaces increases markedly, to a max-min thickness range of 4 nm [Fig. 14(d)], as the number of 100-s MWA cycles increases. This breakdown of planar front regrowth behavior is another indication that the regrowth kinetics for As annealing with microwaves is more difficult than lighter ions, such as P.

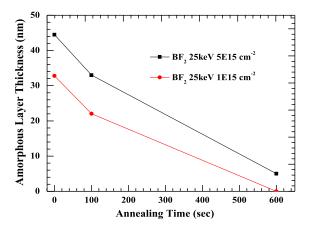

Figs. 16 and 17 summarize the amorphous layer thickness, measured by TEM, versus annealing time. Fig. 16 shows the As and P implanted layers for MWA times <100 s, while Fig. 17 shows the BF<sub>2</sub> implanted layer for MWA times <600 s.

As shown in Fig. 16, the SPEG rate is very slow for the first 50 s, where the temperature increases very rapid. After that the temperature tends to be stable and increases slowly. The SPEG rate increases dramatically after 50 s. However, when the a/c interface was close to the Si surface, the SPEG rate slows.

These results appear to show that the MWA can accelerate the SPEG rate. According to [26], the SPEG rate could be expressed by

$$rate = \frac{vf N_i}{\rho} \exp\left(\frac{-\Delta G}{kT}\right)$$

where  $\nu$  is an attempt frequency, f is a geometry-determined form factor between 0 and 1,  $N_i$  is the number of atoms at

Fig. 16. Amorphous-layer thickness, measured by TEM, for As and P implanted layers for microwave anneal times of <100 s.

Fig. 17. Amorphous-layer thickness, measured by TEM, for  $BF_2$  implanted layers for microwave anneal times of <600 s.

the interface in atoms per area,  $\rho$  is the atomic density of the crystal in atoms per volume, and  $\Delta G$  is the activation energy. The RTA process may heat up the silicon lattice to accelerate the SPEG rate. Then, we suggest that MWA can couple energy from microwaves into cooperative atom motion at the regrowth interface to overcome the activation energy without increasing the substrate temperatures, resulting in an acceleration of the SPEG rate at lower temperatures. In Fig. 14, the amorphous region vanishes after 10 min of MWA treatment, but remains after 6 cycles of 100s MWA treatment. This phenomenon shows that the microwave power transferred to repair the lattice between these two processes is different. A portion of the microwave power in the 6 cycles at 100s is transferred to heat the wafer, and the process wafer could not couple sufficient microwave energy to repair the entire amorphous region.

## III. CARBON-INDUCED STRAIN IN Si BY C7H7 IMPLANTS

This paper then investigates uniaxial tensile strain in the Si channel, introduced through the integration of a S/D material with a smaller lattice constant than Si to enhance the electron mobility of n-MOSFETs. Formation of  $Si_{1-x}C_x$  or SiC films in the S/D regions results in a substantial reduction in the

lattice constant, inducing tensile stress in the device channel regions [27]–[30]. Many methods may be used to form the  $Si_{1-x}C_x$  films, such as epitaxial growth of the  $Si_{1-x}C_x$  [28], [29], or implanting carbon as a dopant followed by subsequent activation [24]. However, the selective epitaxy process is more expensive and complicated, while activating the carbon implanted in the Si layer results in a difficult tradeoff between the high carbon concentration and low thermal budget.

Conventionally, the crystallization of  $Si_{1-x}C_x$  films is carried out by such processes as rapid thermal annealing (RTA) [31] and high-temperature pulsed laser annealing [31]–[34]. These techniques use high temperature to crystallize  $Si_{1-x}C_x$  films, with a high thermal budget for the unannealed region, inducing film disintegration. Therefore, in this paper, an alternative approach to efficient  $Si_{1-x}C_x$  film crystallization at a low temperature using MWA is also explored. The samples investigated were p-type boron-doped 50-60  $\Omega$ -cm (100) orientated Si wafers. All wafers were implanted using a Nissin CLARIS cluster ion implanter. The multiple C<sub>7</sub>H<sub>7</sub><sup>+</sup> implantation conditions used in this paper were as follows:  $10 \text{ keV}/3 \times 10^{15} \text{ cm}^{-2} + 6 \text{ keV}/8 \times 10^{14} \text{ cm}^{-2} + 3 \text{ keV}/6 \times 10^{14} \text{ cm}^{-2}$ 10<sup>14</sup> cm<sup>-2</sup>. Carbon distribution (carbon peak concentration  $1 \times 10^{21}$  cm<sup>-3</sup>) displayed an approximately box-like profile, which is necessary to realize a thicker  $Si_{1-x}C_x$  film with uniform strain. Selected wafers were then implanted by P at a dose of 15 keV with  $4 \times 10^{15}$  cm<sup>-2</sup>. Recrystallization annealing was achieved using: 1) RTA in the range of 500 °C-1000 °C and 2) MWA at 2.8 kW. The quality of the  $Si_{1-x}C_x$  film layer was investigated using several techniques. Strain and [C]<sub>sub</sub> were derived from X-ray diffraction (XRD) rocking curves. Structural analysis was performed by crosssectional TEM.

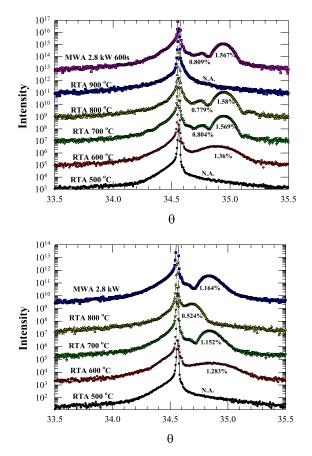

In Fig. 18, the reflection of the XRD spectra, the  $Si_{1-x}C_x$ related peak enables extraction of the substitutional carbon concentration [C]<sub>sub</sub>. Fig. 18(a), MWA at 2.8 kW for 600 s, shows a high [C]<sub>sub</sub> (1.567%), where the maximum temperature is around only 520 °C. In addition, after RTA for 600 s, if the RTA temperature increases above 500 °C, the content of [C]<sub>sub</sub> will increase from 0% to 1.58% at 800 °C, and then decrease to 0% at 900 °C. Temperature is an important factor in the incorporation of the carbon in the Si lattices, and the results by MWA are similar to those of RTA at 700 °C and 800 °C. However, as P in the implanted Si film is increased by cluster carbon, and then annealed by MWA or RTA, the content of [C]<sub>sub</sub> decreases, compared with splits without P implants. Further, the content of the [C]<sub>sub</sub> between 700 °C and 800 °C varies, with higher temperature reducing the content of [C]<sub>sub</sub>. For MWA for P activation in implanted Si film by carbon cluster, the content of [C]<sub>sub</sub> is close to that of RTA at 700 °C.

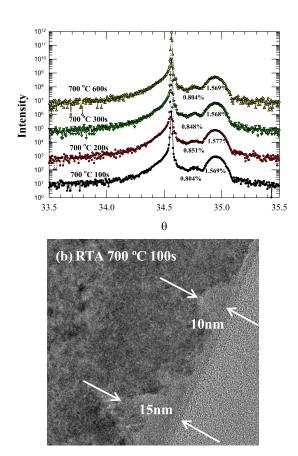

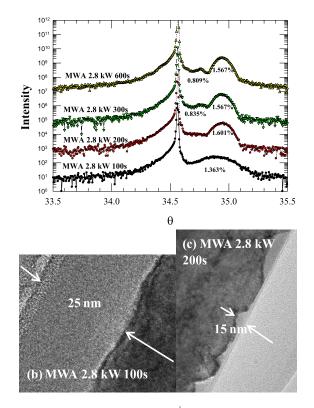

Fig. 19(a) shows RTA at 700 °C for different processing times. The content of [C]<sub>sub</sub> reaches a higher value after only 100 s, including the minor peaks, and TEM images indicate that the amorphous layer has almost been recovered [Fig. 19(b)]. Some twins remain, and a roughly 3-nm amorphous layer still exists in the split by RTA at 700 °C for 100 s. However, it is interesting that the regrowth characteristics of splits by MWA for different processing times are different, as shown in Fig. 20. For MWA for only 100 s, the strength

Fig. 18. (a) In-plane XRD curves for  $C_7H_7^+$  implanted samples with  $[C]_{sub}$  after different annealing conditions in (100) Si substrates. (b) In-plane XRD curves for  $C_7H_7^+$  implanted and P samples with  $[C]_{sub}$  after different annealing conditions.

of the  $Si_{1-x}C_x$  is inferior, and lower  $[C]_{sub}$  (1.363%) is obtained from XRD. If the MWA processing time increases, minor peak would appear, which indicate that it has better crystallization. Therefore, the annealing mechanisms of RTA and MWA appear to be quite different. The initial regrowth rate by MWA is slow, while RTA is faster. With RTA, temperature is an important factor in the incorporation of the carbon into Si lattices, but the MWA results indicate that the annealing time and power are two important annealing parameters.

## IV. EFFECTS OF SUBSTRATE TEMPERATURE DURING MWA PROCESS

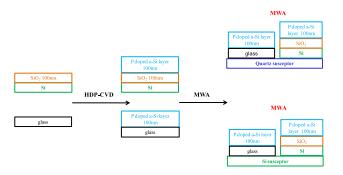

The above results suggest that MWA can assist annealing and SPEG at relatively low temperatures due to the microwave energy itself directly coupling to energy modes within the molecule or lattice. In this section, HDP-CVD *in situ* amorphous Si on oxide/Si or glass is used to investigate the effects of substrate temperatures. Two different substrates, glass and 100-nm oxide/Si, are adopted due to their different microwave power absorption efficiencies, the Si substrate being high and glass low. A 100-nm Si amorphous layer with P *in situ* doped by HDP-CVD was then deposited on the glass and oxide/Si substrates.

Different MWA power levels 1.8, 2.3, or 2.8 kW are used for the comparisons. A schematic diagram of the experimental

Fig. 19. In-plane XRD curves for  $C_7H_7^+$  implanted samples with  $[C]_{sub}$  (a) after RTA at 700 °C for different annealing times in (100) Si substrates and (b) TEM images after RTA at 700 °C for 100 s.

setups is shown in Fig. 21. The Rs after MWA processing are summarized in Table I. Since the original amorphous Si layer has no Si seeds to assist crystallization, dopant activation, and film crystallization require longer processing times and higher MWA power. For the samples on Si susceptors, the Rs of the amorphous films decreased dramatically, to below 1 k  $\Omega$ /sq. This is because the temperature of the Si susceptors increases due to the high-microwave absorption efficiency of Si materials.

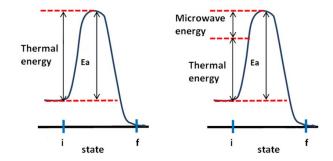

However, if one replaces the Si susceptors with glass suceptors, the results will be different. As summarized in Table I, Rs was very high, reaching 191 M  $\Omega$ /sq. after MWA at 3P for 600 s. Then, even after increases in the MWA power, the Rs remains high for the splits on glass substrate due to its low-microwave absorption efficiency. Therefore, it appears that substrate temperature is an important parameter in dopant activation and film crystallization during the MWA process. Without the assistance of substrate temperature, the efficiency of the MWA process will be low. Fig. 22 shows a schematic of the different annealing mechanisms of RTA and MWA. Using RTA, the substrate temperature can be raised and the activation energy Ea could be overcome by thermal energy. Using MWA, one could overcome the Ea by the combination of substrate temperature and direct coupling of microwave energy into the lattice.

Fig. 20. In-plane XRD curves for  $C_7H_7^+$  implanted samples with  $[C]_{sub}$  (a) after MWA at 2.8 kW for different annealing times in (100) Si substrates and (b) TEM images after MWA at 2.8 kW (a) for 100 s and (b) for 200 s.

Fig. 21. Schematic diagram of the experimental setups.

TABLE I SUMMARY OF Rs AFTER MWA PROCESS

| Susceptor | Substrate                    | MWA Conditions/ Rs |        |       |  |  |

|-----------|------------------------------|--------------------|--------|-------|--|--|

|           | Materials                    | 1.8kW              | 2.3kW  | 2.8kW |  |  |

|           |                              | 600s               | 600s   | 600s  |  |  |

| Si        | a-Si on SiO <sub>2</sub> /Si | 292k               | 793    | 802   |  |  |

| susceptor | a-Si on glass                | 298k               | 906    | 424   |  |  |

| Quartz    | a-Si on SiO <sub>2</sub> /Si | 345k               | 219k   | 636   |  |  |

| susceptor | a-Si on glass                | 191M               | 111.4M | 116M  |  |  |

#### V. FORMATION OF THIN NICKEL GERMANIDE LAYER

Germanium has been considered a potential material for replacement of silicon because of its higher mobility for electrons and holes than Si. For dopant activation in Ge MOS, RTA process (>600 °C) has been widely adopted [35], [36]. Such high temperature process causes the degradation of

Fig. 22. Schematic diagram of different annealing mechanisms between RTA and MWA. By RTA, substrate temperature can be heated and the activation energy Ea could be overcome by thermal energy. By MWA, one could overcome the Ea by the combination of substrate temperature and coupling of microwave energy into lattice.

gate dielectric/Ge channel interface, and also results in severe dopant diffusion in S/D region and Ge out-diffusion into the gate dielectric from the substrate surface. However, when the lower RTA temperature is used, lower activation causes higher contact resistance reducing the drain current. For lowering the contact resistance to germanium, NiGe is the most promising candidate due to its low resistivity [37], [38]. To reduce the thickness of NiGe for continuous scaling down, the process temperature needs to be reduced. However, a lower process temperature results in a higher NiGe resistance due to the small crystallite size of NiGe layer. These are the major challenges of scaling Ge CMOS into nanoscale devices. Accordingly, MWA may be an alternative to other rapid thermal processing methods in silicon processing [3]. MWA has been used to activate implanted dopants through solid phase epitaxial regrowth at low temperature [8]. It is promising for achieving advanced Ge CMOS because of its unique volumetric heating and low temperature due to apparent nonthermal energy transfer that is not yet fully understood [11]. Diffusion-less junctions are observed from the SIMS profiles. Cox and interface improvement could be achieved. By using two-step MWA, an ultrathin Ni monogermanide layer could be formed with a low Rs at low temperature.

After implantation, a MWA with a frequency of 5.8 GHz was used for annealing. Susceptor and quartz wafers were used to improve the uniformity and dopant activation efficiency [25]. A N<sub>2</sub> purge from the top of chamber was performed before the MWA process was started and the N2 flow was maintained until the process was completed. The MWA processing time of microwave process was counted when the power was turned on without regard to temperature. The process temperature ramped up to about 350 °C linearly and tended to saturate after 50 s. The peak temperature of dopant activation by MWA was 390 °C. Fig. 23(a) shows a significant diffusion of P after RTA at 600 °C, and the longer process time leads to a more severe diffusion. Because of the low activation temperature, diffusion-less junction of P after MWA was observed from the SIMS profile. For boron dopants, comparable diffusion-less concentration profiles after MWA and RTA are observed and shown in Fig. 23(b). The electrical activated levels of P and B after MWA are  $2 \times 10^{19}$  cm<sup>-3</sup> and  $7.5 \times 10^{19} \text{ cm}^{-3}$ , respectively.

Fig. 23. SIMS and SRP profiles of (a) P and (b) BF<sub>2</sub> at  $1 \times 10^{15}$  cm<sup>-2</sup> in (100) Ge. The P distribution after MWA is identical to as-implanted, but not after RTA. All boron distribution profiles are close to as-implanted. Insets: activated levels of P and B by SRP are  $2 \times 10^{19}$  cm<sup>-3</sup> and  $7.5 \times 10^{19}$  cm<sup>-3</sup>.

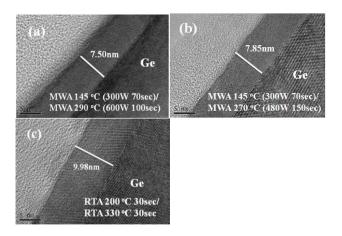

Fig. 24. (a) and (b) HR-TEM images of NiGe by two-step MWA process using lower power in the second step than (a) and by two-step RTA (c).

Fig. 25. ITRS silicide thickness roadmap. A 7.5-nm NiGe is formed by MWA in this paper meeting the 2022 target.

Fig. 26. Temperature profiles of MWA for NiGe formation.

Fig. 27. Rs of NiGe after first step annealing (open symbol) and after second step annealing (solid symbol).

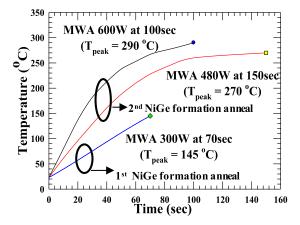

two different microwave power levels during the second step annealing. By increasing the MWA power with shortened process time, a thinner NiGe layer could be formed. Fig. 24(c) shows the result of RTA NiGe annealing. The NiGe thickness by RTA is ~2-nm thicker than by MWA. The temperature ramp up curves of MWA for NiGe formation are shown in Fig. 26. The temperature ramped at 2 °C/s-6 °C/s during MWA depending on the microwave power. In Fig. 27,

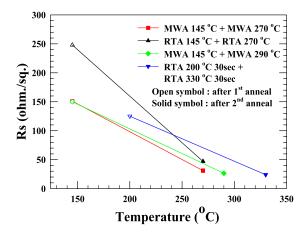

Fig. 28. XRD  $2\theta$ -scan of NiGe formed by MWA or RTA. MWA 145 °C + MWA 270 °C produces the relatively strong (111) preferred crystal orientation with low anneal temperature.

the Rs of NiGe by two-step MWA or RTA are summarized for comparison. The temperature profile of the annealing condition of RTA 145 °C + RTA 270 °C was designed to be the same as MWA to examine the additional microwave effect. We found the microwave could reduce the Rs at the same thermal budget. Lower Rs could be obtained by increasing the MWA power with shortened process time, which lowers the peak temperature by 40 °C compared with RTA. XRD spectra of NiGe formed by MWA or RTA are shown in Fig. 28. Only Ni monogermanide crystal structure was found in both MWA and RTA conditions after two-step annealing. In Fig. 28(a), the scan spectrum for the annealing condition of MWA 145 °C + MWA 270 °C shows relatively strong (111) preferred crystal orientation with low annealing temperature. By comparing with RTA, the higher intensity of MWA leads to a lower resistivity because of the larger grain size of NiGe compared with the RTA process. In Fig. 28(b), an increasing power with shortened process time of second step annealing leads to a larger crystallite size. In addition, by lowering the first step annealing temperature of RTA for reducing the thickness of NiGe a low intensity of RTA 150 °C + RTA 330 °C shows that it is hard to achieve both the well-defined crystalline structure and the scaling of the NiGe layer. However, the MWA results show that a thinner and lower Rs of NiGe layer was obtained because of the increased crystallinity at low temperature.

#### TABLE II

DIFFERENT CHAMBER CONFIGURATIONS FOR THE COMPARISONS OF COUPLING EFFECT. THE DIAGRAM SHOWS THE SETUP IN THE MICROWAVE CHAMBER. THE DISTANCE BETWEEN ADJACENT SLOTS WAS 1 CM ONLY. P.W. IS PROCESS WAFER, S.W. IS SUSCEPTOR, AND Q.W. IS QUARTZ

| configuration | Split 1 | Split 2 | Split 3 | Split 4 | Split 5 | Split 6 | Split 7 | Microwave Head 5.8 GHz |

|---------------|---------|---------|---------|---------|---------|---------|---------|------------------------|

| Slot 1        |         |         |         |         | s.w.    |         |         |                        |

| Slot 2        |         |         |         |         |         |         |         |                        |

| Slot 3        |         |         | s.w.    | s.w.    |         |         | Q.W.    | <000>                  |

| Slot 4        |         | s.w.    | s.w.    |         |         | Q.W.    | Q.W.    | Quartz                 |

| Slot 5        | P.W.    | Susceptor              |

| Slot 6        |         | s.w.    | s.w.    |         |         | Q.W.    | Q.W.    |                        |

| Slot 7        |         |         | s.w.    | s.w.    |         |         | Q.W.    | Process<br>Wafer       |

| Slot 8        |         |         |         |         |         |         |         |                        |

| Slot 9        |         |         |         |         | s.w.    |         |         |                        |

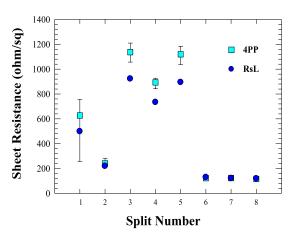

Fig. 29. Sheet resistance values, measured by 4PP and a JPV carrier spreading technique, RsL, for the wafer splits in this paper. The position and composition of the susceptors around the Si test wafer (shown as a filled rectangle) are shown above the Rs values. In addition, split 8 is for 1000 °C spike RTA.

# VI. SUSCEPTOR COUPLING FOR THE UNIFORMITY AND DOPANT ACTIVATION EFFICIENCY

The final section of this paper discusses improvement in the uniformity and dopant activation efficiency of the microwave chamber using the susceptors-coupling effect. All the splits and a schematic are given in Table II, where the distance between adjacent slots was only 1 cm. The Rs of all splits within wafer uniformities (error bars) are shown in Fig. 29. Carrier recombination and trap-assisted tunneling leakage currents measured with the RsL tool are quite modest [39], with a range from 1 to 10  $\mu$ A/cm<sup>2</sup> for all wafer splits in this paper. From the results of splits 1 and 2, it appears that although the Si susceptor wafer can soak up the microwave power inside the chamber, its coupling effect with process wafers is an important factor in increasing the dopant activation efficiency. When adding additional Si susceptors (split 3), the Rs increases to  $\sim$ 1120  $\Omega$ /sq. with a standard deviation of 44.5  $\Omega$ /sq., which indicates that the sharing of microwave power by

Fig. 30. Comparison of temperature profiles versus annealing time at MWA 300% power. The MWA time was defined as the period when the microwave power was turned on.

the four Si susceptors dominates the dopant activation efficiency.

The distance between the process wafer and Si susceptors is also an important factor in the coupling effect. When the distance between the pair of Si susceptors and the process wafer is increased from one to two units (split 4) and to three units (split 5), the Rs remains high, near 1000  $\Omega$ /sq. with a standard deviation of roughly 30  $\Omega$ /sq. The temperature profile versus annealing time by MWA is shown in Fig. 30. For split 1, with only one process wafer inside the chamber, the temperate increase rate was the fastest among all splits. However, as the temperature saturated, the temperature became unstable. This indicates that standing wave patterns were established in the microwave processing chamber, resulting in nodes and antinodes over the process wafer, causing an unstable temperature profile. When adding two Si wafers as the susceptors (split 2), the slope of the temperature increase is not as steep as that of split 1 because the Si susceptors soak up the microwave power inside the chamber. In addition, as the distance between the Si susceptors and process wafer increases to two units (split 4), the rate of temperature increase remains the same as in split 2, but the maximum temperature decreases roughly 20 °C.

Microwave power absorption of solid materials is due to their magnetic, dielectric, and conductivity properties. The loss factor  $\varepsilon''$  determines the absorption of the propagating electric field. In addition,  $\varepsilon''$  is the material parameter that conveys the effects of conduction and polarization loss mechanisms during microwave heating of doped silicon [3]. Thus, while both the quartz and Si susceptors absorb the microwave power inside the chamber, quartz susceptors absorb far less.

When setting the quartz susceptors (split 6), the peak process wafer temperature was 445 °C and low sheet resistances were obtained. The maximum temperature of the quartz wafers of split 6 was only 180 °C and the lower rate of temperate increase and decrease compared with the silicon susceptor splits is due to the low loss factor. After the microwave power is turned off, the rate of temperature decrease also depends on the number of Si and quartz susceptors. The

greater the number of susceptors, the slower the rate of cooling.

In conclusion, it appears that quartz wafers could prevent power dissipation among process wafers during the MWA process with the highest peak temperature among all splits. Susceptors could stabilize the process wafer temperature by slowing the temperature decrease after the microwave power is terminated.

Finally, in this section, the effects of susceptor coupling on the dopant activation levels and uniformity of implant-doped Si for fixed-frequency MWA are investigated. The number and placement of various combinations of Si and quartz susceptor wafers changed the temperature profiles for 100-s microwave heating cycles as well as the sheet resistance level and uniformity. The addition of susceptor wafers in the near vicinity of the process wafer improved the sheet resistance uniformity and caused higher dopant activation level. The use of low-susceptibility quartz wafers resulted in remarkably low sheet resistance and low leakage current values.

## VII. CONCLUSION

This paper explores several potential applications of MWA. First, activation and deactivation of P, As, and BF<sub>2</sub> implants by low-temperature (<550 °C) MWA on implanted Si samples have been demonstrated. In the implanted Si region, the dopant activation was driven by SPEG during MWA. Beyond the amorphous/crystalline interface, the dopant can also be activated due to the energy of the microwaves coupling to the crystalline lattice. The coupling of the microwave power aids transport of the ionized impurities to the substitutional sites over very short range through a nonthermal microwave effect, but does not produce the longer range transport that is junction diffusion. In addition, for  $Si_{1-x}C_x$ , the annealing mechanisms of RTA and MWA appear to be quite different. The initial regrowth rate by MWA is slow, while it is faster by RTA. With RTA, temperature is an important factor in the incorporation of the carbon into Si lattices, but the MWA results indicate that the annealing power, not just the temperature itself, is an important parameter.

This paper also presents a novel NiGe process that achieves an NiGe thickness of 7.5 nm with two-step low temperature MWA. Finally, the placement of various combinations of Si and quartz susceptor wafers changes the temperature profiles during MWA as well as the sheet resistance level and uniformity. The addition of susceptor wafers in the near vicinity of the process wafer improved the sheet resistance uniformity and caused a higher dopant activation level. The use of low-susceptibility quartz wafers resulted in remarkably low sheet resistance and low leakage current values.

MWA for low temperature IC processing is promising, but we are just beginning to understand how these mechanisms are assisted by microwave thermal and nonthermal effects. The experimental data reviewed here offer a conceptual and quantitative basis for understanding the microwave effect. The process of innovating applications for MWA, still in its infancy, shows much potential.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. J. H. Booske, University of Wisconsin-Madison, USA, for the useful input and discussions.

#### REFERENCES

- (2011). International Technology Roadmap for Semiconductor [Online]. Available: http://www.itrs.net/

- [2] D. K. Schroder, Semiconductor Material and Device Characterization. Hoboken, NJ, USA: Wiley, 2006.

- [3] T. L. Alford, D. C. Thompson, J. W. Mayer, and N. D. Theodore, "Dopant activation in ion implanted silicon by MWA," *J. Appl. Phys.*, vol. 106, no. 11, pp. 114902-1–114902-8, 2009.

- [4] H. Zohm, E. Kasper, P. Mehringer, and G. A. Muller, "Thermal processing of silicon wafers with microwave co-heating," *Microelectron. Eng.*, vol. 54, no. 3, pp. 247–253, 2000.

- [5] Y. J. Lee, Y. L. Lu, F. K. Hsueh, K. C. Huang, C. C. Wan, T. Y. Cheng, et al., "3D 65 nm CMOS with 320 °C microwave dopant activation," in Proc. IEEE IEDM, Dec. 2009, pp. 31–34.

- [6] Y. J. Lee, F. K. Hsueh, S. C. Huang, J. M. Kowalski, J. E. Kowalski, A. T. Y. Cheng, et al., "A low-temperature microwave anneal process for boron-doped ultrathin Ge epilayer on Si substrate," *IEEE Electron Device Lett.*, vol. 30, no. 2, pp. 123–125, Feb. 2009.

- [7] Y. L. Lu, F. K. Hsueh, K. C. Huang, T. Y. Cheng, J. M. Kowalski, J. E. Kowalski, et al., "Nanoscale p-MOS thin-film transistor with TiN gate electrode fabricated by low-temperature microwave dopant activation," *IEEE Electron Device Lett.*, vol. 31, no. 5, pp. 417–439, May 2010.

- [8] F. K. Hsueh, Y. J. Lee, K. L. Lin, M. I. Current, C. Y. Wu, and T. S. Chao, "Amorphous-layer regrowth and activation of P and as implanted Si by low-temperature microwave annealing," *IEEE Trans. Electron Devices*, vol. 58, no. 7, pp. 2088–2093, Jul. 2011.

- [9] Y.-J. Lee, S.-S. Chuang, F.-K. Hsueh, H.-M. Lin, S.-C. Wu, C.-Y. Wu, et al., "Dopant activation in single-crystalline germanium by low-temperature microwave annealing," *IEEE Electron Device Lett.*, vol. 32, no. 2, pp. 194–196, Feb. 2011.

- [10] J. H. Booske, R. F. Cooper, and I. Dobson, "Mechanisms for nonthermal effects on ionic mobility during microwave processing of crystalline solids," *J. Mater. Res.*, vol. 7, no. 2, pp. 495–501, 1992.

- [11] A. G. Whittaker, "Diffusion in microwave-heated ceramics," Chem. Mater., vol. 17, no. 13, pp. 3426–3432, 2005.

- [12] K. Thompson, Y. B. Gianchandani, J. Booske, and R. F. Cooper, "Direct Si-Si bonding by electromagnetic induction heating," *J. Microelectro*mech. Syst., vol. 11, no. 4, pp. 285–292, 2002.

- [13] K. Thompson, J. H. Booske, Y. B. Gianchandani, and R. F. Cooper, "Electromagnetic annealing for the 100 nm technology node," *IEEE Electron Device Lett.*, vol. 23, no. 3, pp. 127–129, Mar. 2002.

- [14] K. Thompson, J. H. Booske, R. F. Cooper, and Y. B. Gianchandani, "Electromagnetic fast-firing for ultra-shallow junction formation," *IEEE Trans Semicond. Manuf.*, vol. 16, no. 3, pp. 460–468, Aug. 2003.

- [15] D. Stuerga and P. Gaillard, "Microwave athermal effects in chemistry: A Myth's Autopsy. Part II: Orienting effects and thermodynamic consequences of electric field," *J. Microw. Power Electromagn. Energy*, vol. 31, no. 2, pp. 101–113, 1996.

- [16] C. O. Kappe, "Controlled microwave heating in modern organic synthesis," *Angew. Chem. Int. Ed.*, vol. 43, no. 46, pp. 6250–6285, 2004.

- [17] A. De la Hoz, A. Diaz-Ortiz, and A. Moreno, "Microwaves in organic synthesis. Thermal and non thermal microwave effects," *Chem. Soc. Rev.*, vol. 34, no. 2, pp. 164–178, 2005.

- [18] J. H. Booske, R. F. Cooper, and S. A. Freeman, "Microwave enhanced reaction kinetics in ceramics," *Mater. Res. Innov.*, vol. 1, no. 2, pp. 77–84, 1997.

- [19] G. Robb, A. Harrison, and A. G. Whittaker, "Temperature-resolved, in-situ powder X-ray diffraction of silver iodide under microwave irradiation," *Phys. Chem. Commun.*, vol. 5, no. 19, pp. 135–137, 2002.

- [20] S. A. Freeman, J. H. Booske, and R. F. Cooper, "Modeling and numerical simulations of microwave-induced ionic transport," *J. Appl. Phys.*, vol. 83, no. 11, pp. 5761–5772, 1998.

- [21] J. H. Booske, Private Communication. Madison, WI, USA: Univ. Wisconsin-Madison, 2010.

- [22] J. H. Booske, R. F. Cooper, S. A. Freeman, K. Rybakov, and V. Semenov, "Microwave ponderomotive forces in solid state ionic plasmas," *Phys. Plasmas*, vol. 5, no. 5, pp. 1664–1670, 1998.

- [23] K. Thompson, J. H. Booske, R. L. Ives, J. Lohr, Y. Gorelov, and K. Kajiwara, "Millisecond microwave annealing: Driving microelectronics nano," J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct., vol. 23, no. 3, pp. 970–978, 2005.

- [24] T. L. Alford, I. Ahmad, and R. Hubbard, "Variable frequency microwave induced low temperature dopant activation in ion implanted silicon," in *Proc. 17th Int. Conf. Adv. Thermal Process. Semicond.*, Oct. 2009, pp. 1–5.

- [25] Y. J. Lee, F. K. Hsueh, M. I. Current, C. Y. Wu, and T. S. Chao, "Susceptor coupling for the uniformity and dopant activation efficiency in implanted Si under fixed-frequency microwave anneal," *IEEE Electron Device Lett.*, vol. 33, no. 2, pp. 248–250, Feb. 2012.

- [26] O. Hellman, "Topics in solid phase epitaxy: Strain, structure and geometry," Mater. Sci. Eng., R, Rep., vol. 16, no. 1, pp. 1–42, Jan. 1996.

- [27] Y. Liu, O. Gluschenkov, J. Li, A. Madan, A. Oszan, B. Kim, et al., "Strained Si channel MOSFETs with embedded silicon carbon formed by solid phase epitaxy," in *Proc. IEEE Symp. VLSI Technol.*, Jun. 2007, pp. 44–45.

- [28] B. Yang, R. Takalkar, Z. Ren, L. Black, A. Dube, J. W. Wejtmans, et al., "High-performance nMOSFET with in-situ phosphorus-doped embedded Si:C (ISPD eSi:C) source-drain stressor," in *Proc. IEEE IEDM*, Dec. 2008, pp. 1–4.

- [29] K. W. Ang, K. J. Chui, V. Bliznetsov, Y. Wang, L.-Y. Wong, C.-H. Tung, et al., "Thin body silicon-on-insulator N-MOSFET with silicon-carbon source/drain regions for performance enhancement," in *Proc. IEEE IEDM*, Dec. 2005, pp. 497–500.

- [30] K.-W. Ang, K.-J. Chui, H.-C. Chin, Y.-L. Foo, A. Du, W. Deng, et al., "50nm silicon-on-insulator N-MOSFET featuring multiple stressors: Silicon-carbon source/drain regions and tensile stress silicon nitride liner," in Proc. Symp. VLSI Technol., 2006, pp. 66–67.

- [31] H. Itokawa, K. Miyano, Y. Oshima, I. Mizushima, and K. Suguro, "Carbon incorporation into substitutional silicon site by molecular carbon ion implantation and recrystallization annealing as stress technique in n-metal-oxide-semiconductor field-effect transistor," *Jpn. J. Appl. Phys.*, vol. 49, no. 4, p. 04DA05, 2010.

- [32] A. T.-Y. Koh, R. T.-P. Lee, F.-Y. Liu, T.-Y. Liow, K. M. Tan, X. Wang, et al., "Pulsed laser annealing of silicon-carbon source/drain in MuGFETs for enhanced dopant activation and high substitutional carbon concentration," *IEEE Electron Device Lett.*, vol. 29, no. 5, pp. 464–467, May 2008.

- [33] Y.-C. Yeo, "Enhancing CMOS transistor performance using lattice-mismatched materials in source/drain regions," *Semicond. Sci. Technol.*, vol. 22, no. 1, pp. S177—S182, 2007.

- [34] S.-M. Koh, K. Sekar, D. Lee, W. Krull, X. Wang, G. S. Samudra, et al., "N-channel MOSFETs with embedded silicon–carbon source/drain stressors formed using cluster-carbon implant and excimer-laser-induced solid phase epitaxy," *IEEE Electron Device Lett.*, vol. 29, no. 12, pp. 1315–1318, Dec. 2008.

- [35] G.-L. Luo, S.-C. Huang, C.-T. Chung, D. Heh, C.-H. Chien, C.-C. Cheng, et al., "A comprehensive study of Ge<sub>1-x</sub>Si<sub>x</sub> on Ge for the Ge nMOSFETs with tensile stress, shallow junctions and reduced leakage," in *Proc. IEEE IEDM*, Dec. 2009, pp. 689–692.

- [36] J.-H. Park, M. Tada, D. Kuzum, P. Kapur, H.-Y. Yu, H.-S. P. Wong, et al., "Low temperature (≤380 °C) and high performance Ge CMOS technology with novel source/drain by metal-induced dopants activation and high-k/Metal gate-stack for monolithic 3D integration," in Proc. IEEE IEDM, Dec. 2008, pp. 389–392.

- [37] P. S. Y. Lim, D. Z. Chi, P. C. Lim, X. C. Wang, T. K. Chan, T. Osipowicz, et al., "Formation of epitaxial metastable NiGe<sub>2</sub> thin film on Ge(100) by pulsed excimer laser anneal," Appl. Phys. Lett., vol. 97, no. 18, pp. 182104-1–182104-3, 2010.

- [38] K. Martens, A. Firrincieli, R. Rooyackers, B. Vincent, R. Loo, S. Locorotondo, et al., "Record low contact resistivity to n-type Ge for CMOS and memory applications," in Proc. IEEE IEDM, Dec. 2010, pp. 428–431.

- [39] V. A. Faifer, M. I. Current, T. M. H. Wong, and V. Souchkov, "Non-contact sheet resistance and leakage current mapping for ultra-shallow junctions," *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct.*, vol. 24, no. 1, pp. 414–420, 2006.

**Yao-Jen Lee** was born in Kaohsiung, Taiwan, in 1976. He received the Ph.D. degrees from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 2004.

He is currently a Research Fellow with the National Nano Device Laboratories, Hsinchu, Taiwan, and partly with the Department of Physics, National Chung Hsing University.

Hsiu-Chih Chen received the A.S. degree in electronic engineering from the Minghsin University of Science and Technology, Hsinchu, Taiwan, in 1993. She joined the National Nano Device Laboratories,

She joined the National Nano Device Laboratorie Hsinchu, as an Assistant Technician.

**Ta-Chun Cho** received the M.S. degree in physics from National Chung-Hsing University, Taichung, Taiwan, in 2011. He is currently pursuing the Ph.D. degree with the Department of Electrophysics, National Chiao-Tung University, Hsinchu, Taiwan.

**Michael I. Current** received the B.S., M.S., and Ph.D. degrees in solid-state physics from the Rensselaer Polytechnic Institute, Troy, NY, USA, in 1967, 1973, and 1974, respectively.

He was a Visiting Professor with Kyoto University, Kyoto, Japan.

Shang-Shiun Chuang received the M.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2010, where he is currently pursuing the Ph.D. degree with the Department of Electronics Engineering and the Institute of Electronics.

**Tseung-Yuen Tseng** (F'02) received the Ph.D. degree in electroceramics from the School of Materials Engineering, Purdue University, West Lafayette, IN, USA, in 1982.

He is currently a University Chair Professor with the Department of Electronics Engineering and the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan.

**Fu-Kuo Hsueh** received the M.S. degree in semiconductor materials and process equipment from National Chiao-Tung University, Hsinchu, Taiwan, in 2010, where he is currently pursuing the Ph.D. degree with the Department of Electrophysics.

He has been with the National Nano Device Laboratories, Hsinchu, as an Engineer, since 2006.

**Tien-Sheng Chao** received the Ph.D. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1992.

He is currently a Professor with National Chiao-Tung University.

**Yu-Lun Lu** received the B.S. and M.S. degrees in physics from National Chung Hsing University, Taichung, Taiwan, in 2005 and 2007, respectively, and the Ph.D. degree from the Department of Electrophysics, National Chiao-Tung University, Hsinchu, Taiwan, in 2012.

He has been with the Taiwan Semiconductor Manufacturing Company, Ltd., Tainan, Taiwan, as a Nano Diffusion Engineering Principal Engineer, since 2012.

Chenming Hu is the TSMC Distinguished Professor of UC Berkeley and a Board Director of SanDisk, Inc. and Friends of Children with Special Needs. He was formerly the Chief Technology Officer of TSMC. He is known for developing the 3D transistor, FinFET, that can be scaled to sub-10nm; and BSIM, the industry-standard SPICE model used in designing most ICs.

**Po-Jung Sung** received the M.S. degree in chemical and materials engineering from National Central University, Zhongli, Taiwan, in 2008. He is currently pursuing the Ph.D. degree with the Department of Electrophysics, National Chiao-Tung University, Hsinchu, Taiwan.

He has been with the National Nano Device Laboratories, Hsinchu, since 2010, as an Associate Engineer.

**Fu-Liang Yang** received the Ph.D. degree in materials science and metallurgy from the University of Cambridge, U.K., in 1994.

He was elected as an TSMC Academician, TSMC Academy, in 2004. Now, he is a director and distinguished research fellow of Academia Sinica, Taiwan. He has authored more than 30 IEDM and VLSI Symposium papers, and several invited talks. He has also invented or co-invented more than 240 patents in advanced CMOS devices and dynamic/static/nonvolatile memory technologies.