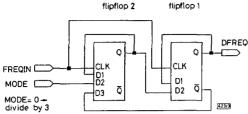

Fig. 3 Dual-modulus divider 2/3

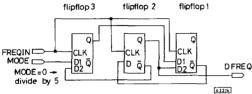

Fig. 4 Dual-modulus divider 4/3

Conclusions: The realisation of dual-modulus frequency dividers with minimum gate count has been addressed in a general way. An expression for the maximum number of different (k/k+1) dividers was derived. This number is equal to the number of different state-mapping sets of Boolean equations. A computer search for a mapping-set containing one type of Boolean operator only was performed. Equation sets for divide-by-2/3 and divide-by-4/5 have been presented. A D-flipflop with multiple inputs was used as a building block in the realisation of these dividers. Detailed schematic diagrams for divide-by-2/3 and divide-by-4/5 frequency dividers using NOR-gates have been presented. Speed increase and power savings in dual-modulus frequency dividers have been achieved by reducing the gate count.

© IEE 1994 6 June 1994

Electronics Letters Online No: 19940829

P. Wennekers (Motorola Inc., Semiconductor Product Sector, 2100 East Elliott Road, Tempe, Arizona 85284, USA)

## References

- 1 OHATA, M., TAKADA, T., INO, M., KATO, N., and IDA, M.: 'A 4.5-Ghz GaAs dual-modulus prescaler IC', IEEE Trans., 1988, MTT-36, pp. 158-160

- 2 KASAHARA, J., WADA, M., KAWASAKI, H., HIDA, Y., and OKUBORA, A.: '10 GHz GaAs JFET dual-modulus prescaler IC', Electron. Lett., 1989, 25, pp. 889–890

- 3 MIZUNO, M., SUZUKI, H., OGAWA, M., SATO, K., and ICHIKAWA, H.: 'A 3-mW 1.0-GHz silicon-ECL dual-modulus prescaler IC', IEEE J. Solid-State Circuits, 1992, SSC-27, pp. 1794-1798

- 4 SENEFF, T., MCKAY, L., SAKAMOTO, K., and TRACHT, N.: 'A sub-1mA 1.5GHz silicon bipolar dual modulus prescaler'. IEEE, BCTM-Proc. Minneapolis, 1993, pp. 240-243

- 5 KADO, Y., SUZUKI, M., KOIKE, K., OMURA, Y., and IZUMI, K.: 'A 1-GHZ/0.9mW CMOS/SIMOX divide-by-128/129 dual-modulus prescaler using a divide-by-2/3 synchronous counter', IEEE J. Solid-State Circuits, 1993, SSC-28, pp. 513-517

## Genetic algorithms for the module orientation problem

R.-I. Chang and P.-Yung Hsiao

Indexing terms: Circuit layout CAD, Genetic algorithms

To solve the module orientation problem the optimal number of flips of modules needs to be determined so as to minimise total wire length. A genetic-based module orientation method is proposed. Experiments show that the proposed method performs better than the best method known for this problem.

Introduction: The placement of modules to minimise total wire length is a major consideration in the physical design of VLSI circuits. Assume that the modules have already been placed by some placement algorithms and the pin positions on each module are fixed on the module boundary. An improvement can be made to further minimise total wire length by flipping these modules with respect to their vertical and/or horizontal axes of symmetry. The problem of finding the optimal flips for a given set of modules with minimium total wire length is called the module orientation problem. It has been proved to be NP-complete [1] for macro-cell layout, and some methods were presented in [1-4]. In 1992, a neural-based module orientation method was presented by Lee and Takefuji [2] using a generalised maximum neural network. To our knowledge, it is the best algorithm known for this problem. In this Letter, a new approach based on a natural processing concept is proposed to minimise total wire length for the module orientation problem. The presented method, which mimics the mechanics of natural selection and genetics, is called a genetic algorithm [5]. The algorithm starts with an initial set of random configurations and uses a process similar to biological evolution to improve on them. Because of its robustness and effectiveness, this method has been successfully applied in various optimisation problems. In this Letter, a genetic-based module orientation method is proposed. Experiments show that it performs better than the best algorithm [2] known for this problem. Moreover, the proposed approach which uses the concept of evolution is capable of handling different wire-length metrics and more complicated problem constraints.

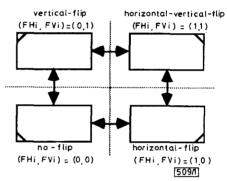

Fig. 1 No-flip, horizontal flip, vertical flip and horizontal-vertical flip states of circuit module

Formulations for module orientation problem: Assume that each circuit module i has an orientation state  $(FH_i, FV_j)$  where  $FV_i$  and  $FH_i \in \{0, 1\}$  represent the states of vertical flip and horizontal flip, respectively. Thus, the orientation states  $(FH_i, FV_j) = (0, 0)$ , (1, 0), (0, 1) and (1, 1), as shown in Fig. 1, denote no-flip, horizontal-flip, vertical-flip and horizontal-vertical-flip of the circuit module, respectively. Assume that there are n circuit modules and each circuit module i has already been placed with centre  $(x_i, y_i)$ . Let pin j located on a macro-cell i be fixed on the module boundary with position  $(x_{ij}, y_{ij})$ . The offset  $(dx_{ij}, dy_{ij})$  can be defined as  $(x_{ij} - x_{ii}, y_{ij} - y_i)$ . It is clear that the co-ordinates  $(x_i + dx_{ij}, y_i + dy_{ij})$ ,  $(x_i - dx_{ij}, y_i + dy_{ij})$ ,  $(x_i - dx_{ij}, y_i - dy_{ij})$  and  $(x_i - dx_{ij}, y_i - dy_{ij})$  are the positions of the pin j by norizontal-flip, vertical-flip and horizontal-vertical-flip of module i, respectively. In this Letter, we simply rewrite the pin position as  $(X_{ij}, Y_{ij}) = (x_i + (1 - 2FH_i) \times dx_{ij}, y_i + (1 - 2FV_i) \times dy_{ij})$ . Assume that there are m wire nets in the problem, and each wire net k is connected from pin  $P0_k$  of module  $M0_k$  to pin  $P1_k$  of module  $M1_k$ ; then, the total wire length can be defined as follows:

$$\sum_{k=1}^{m} \sqrt{(X_{M0_k P0_k} - X_{M1_k P1_k})^2 + (Y_{M0_k P0_k} - Y_{M1_k P1_k})^2}$$

(1)

The module orientation problem is defined to minimise the total wire length by flipping circuit modules.

Module flipping using genetic algorithms: A genetic algorithm is presented to minimise the objective function as eqn. 1. Typically, the set of configurations on which the genetic algorithm operates

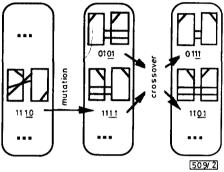

is called the population. Each individual in the population is a binary bit string (called chromosome) representing a solution to the problem. During each iteration, called a generation, the individuals in the current population are evaluated, using some measure of fitness called a fitness function. Based on this fitness value, individuals are selected from the population as parents. A number of genetic operators (i.e. crossover and mutation) are applied to the parents for generating new individuals, called offspring. The offspring are next evaluated, and a new generation is formed by selecting some of the parents and offspring, and rejecting others so as to keep the population size constant. Thus, the evolution results of an optimal individual will lead to an optimal solution for the problem. The flip of circuit module i is represented by the orientation state (FH<sub>i</sub>, FV<sub>i</sub>). In this Letter, the solution configuration of the proposed problem can be binary encoded into the chromosome  $(FH_1FV_1FH_2FV_2 \dots FH_nFV_n)$ . We define the fitness function to evaluate the individuals as  $-1 \times eqn$ . 1. Thus, the evolution results of an optimal chromosome will lead to the optimal orientation assignments for macro-cell placement. The module orientation problem can be solved by a genetic-based algorithm. A simple example to demostrate this idea is shown in Fig. 2.

Fig. 2 Simple example to demonstrate proposed genetic-based method

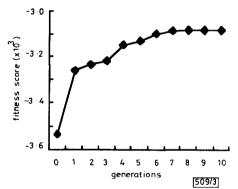

Fig. 3 Fitness of best chromosomes in population for evolution process of ex4

Experimental results: A genetic algorithm with the size of population set 100 and the number of generation 10 is applied. To benchmark the performance of the proposed algorithm, the test examples are all taken from [2]. All our experiments were carried out on a Sun SPARC IPC workstation and the best solutions chosen. Consider a test example ex4 with 10 circuit modules, the total number of configurations examined by the proposed algorithm is more than 100 times less than that for the exhaustive search, and the run time was marginally better. Fig. 3 shows the fitness of the best chromosomes in the population at each generation for the evolution process of ex4. The comparisons of the proposed genetic algorithm (GA) method with the generalised maximum neural network (GMNN) are shown in Table 1. To our knowledge, it is the best algorithm known for this problem. Experimental results indicate that the proposed genetic-based approach finds the global optimal solutions for all these test examples. It is

generally better than GMNN which cannot find the global optimal solutions for the test example ex7.

Table 1: Comparisons of proposed GA method with GMNN

| Example | Initial | GMNN [2] | GA    |

|---------|---------|----------|-------|

| exl     | 994     | 755*     | 755*  |

| ex2     | 2487    | 2093*    | 2093* |

| ex3     | 2255    | 1785*    | 1785* |

| ex4     | 3537    | 3085*    | 3085* |

| ex5     | 1971    | 1584*    | 1584* |

| ex6     | 2526    | 2349*    | 2349* |

| ex7     | 1930    | 1684     | 1678* |

<sup>\*</sup>Global optimal solutions

Conclusion: A genetic-based module orientation method has been proposed. We have shown that the proposed method is very efficient at minimising total wire length by flipping circuit modules. Experiments show that the genetic algorithm yields results better than the previous module orientation methods, both in the final result quality and computation time required.

© IEE 1994

Electronics Letters Online No: 19940837

R.-I. Chang and P.-Y. Hsiao (Department of Computer and Information Science, National Chiao Tung University, Hsinchu, Taiwan 30050, Republic of China)

## References

- HADAS, R.L., and LIU, C.L.: 'Solution to the module orientation and rotation problem by neural computation networks'. Proc. 26th Design Automation Conf., 1989, pp. 400-405

- 2 LEE, K.C., and TAKEFUJI, Y.: 'A generalized maximum neural network for the module orientation problem', *Int. J. Electron.*, 1992, 72, (3), pp. 331-355

- 3 YAMADA, M., and LIU, C.L.: 'An analytical method for optimal module orientation'. Proc. Int. Symp. on Circuits and Systems, 1988, pp. 1679-1682

- 4 CHENG, C.K., HU, T.C., and YAO, S.Z.: 'The modular orientation of VLSI layout'. Int. Symp. on Circuits and Systems, 1990, pp. 1600– 1603

- 5 GOLDBERG, D.E.: 'Genetic algorithms in search, optimization and machine learning' (MA: Addison-Wesley, 1989)

## Bandwidth efficient modulation with wavelets

F. Daneshgaran and M. Mondin

Indexing terms: Modulation, Wavelet transforms

The authors demonstrate that the use of scaling functions and wavelets as envelope functions for modulation is natural in view of the first Nyquist criterion for ISI removal. Using wavelet packets, the number of dimensions available to the modulator per unit time is increased.

Introduction: Consider Fig. 1 depicting the complex baseband equivalent model of a narrowband communication system. At each time slot the source emits a symbol drawn from the complex plane that linearly modulates the possibly complex shaping pulse whose Fourier transform is S(f). Simply put, we propose the use of scaling functions and wavelets as this shaping pulse and investigate the possibility of approaching the dimensionality limit in the process. The focus of this Letter will be on the Daubechies compactly supported wavelets [1] (the concept presented generalises to other orthonormal wavelets).