Home Search Collections Journals About Contact us My IOPscience

Effects of  $N_2$  O-Plasma Treatment of a- $SiO_XN_y/a$ - $SiN_X$  Gate Insulators on Electrical Stability of a-Si:H Thin-Film Transistors

This content has been downloaded from IOPscience. Please scroll down to see the full text.

1994 Jpn. J. Appl. Phys. 33 L977

(http://iopscience.iop.org/1347-4065/33/7B/L977)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 28/04/2014 at 16:29

Please note that terms and conditions apply.

# Effects of $N_2O$ -Plasma Treatment of a-SiO $_xN_y/a$ -SiN $_x$ Gate Insulators on Electrical Stability of a-Si:H Thin-Film Transistors

Tean-Sen Jen, Shyue-Ter Leu, Tsung-Chih Chou, Jyh-Wong Hong and Chun-Yen Chang<sup>1</sup> Department of Electrical Engineering, National Central University, Chungli, 32054, Taiwan, Republic of China <sup>1</sup>Institute of Electronics, National Chiao Tung University, Hsinchu, 30050, Taiwan, Republic of China (Received April 30, 1994; accepted for publication June 1, 1994)

$N_2O$ -plasma was used to treat the as-deposited a-SiO<sub>x</sub>N<sub>y</sub>/a-SiN<sub>x</sub> gate insulators of inverted-staggered a-Si:H thin-film transistors (TFTs), and its effects on electrical properties of TFTs were investigated. The TFTs with N<sub>2</sub>O-plasma-treated gate insulators tended to have a smaller threshold voltage ( $V_{th}$ ),  $V_{th}$  shift and hysteresis width ( $W_{FB}$ ) of the forward and backward transfer characteristics. In addition, the results of a bias-temperature stress (BTS) experiment showed that the N<sub>2</sub>O-plasma-treated devices had a smaller decay of drain current with time. These phenomena demonstrated that the N<sub>2</sub>O-plasma treatment could be used to improve the electrical stability of a-Si:H TFTs.

KEYWORDS: thin-film transistor, electrical stability, N2O-plasma treatment

#### 1. Introduction

Exposure to light or gate-bias stress can cause a reduction of on-conductance and a  $V_{\rm th}$  shift to a conventional a-Si:H thin-film transistor (TFT) with an a-SiN $_x$  gate insulator. Alternately, an a-SiO $_x$ N $_y$  gate insulator, which possesses a lower mechanical stress and a larger optical gap than those of the a-SiN $_x$  film, is more water-resistant than the a-SiO $_x$  film. Also, a thin a-SiN $_x$  layer inserted between the a-Si:H channel and a-SiO $_x$ N $_y$  gate insulator can be used to reduce the density of trapped charges in the a-SiO $_x$ N $_y$  gate insulator without degrading the switching characteristics of an a-Si:H TFT. Therefore, the structure of a-SiO $_x$ N $_y$ /a-SiN $_x$  gate insulators may result in good performance of a-Si:H TFT.

Exposing the gate nitride to an O<sub>2</sub> plasma prior to the a-Si:H deposition results in a reduction of defects in the interface region and especially an improvement of the p-channel a-Si:H TFT characteristics.<sup>5)</sup> Also, the surface oxidation of a-Si:H caused by the N<sub>2</sub>O-plasma treatment of a fabricated a-Si:H TFT increases its drain current under negative gate bias. 6) On the other hand, although the NH<sub>3</sub>-plasma treatment of the gate nitride causes a general increase in the subthreshold slope, S, and  $V_{th}$  of the a-Si:H TFT, the TFT stability can be improved, since the NH<sub>3</sub>-plasma-treated TFT has a smaller  $W_{\rm FB}$  and a higher resistance against the prolonged positive gate bias. 7) In addition, an H<sub>2</sub>-plasma treatment of thermally grown SiO2 gate insulator of a-Si:H TFT results in degradation of its electrical stability, and this phenomenon is ascribed to the increased defect density in SiO<sub>2</sub> caused by H<sub>2</sub>-plasma treatment.<sup>8)</sup>

We previously reported a  $N_2O$ -plasma treatment of a-SiO<sub>x</sub>N<sub>y</sub>/a-SiN<sub>x</sub> gate insulators which showed an electrical stability improvement of the a-Si:H TFT. <sup>9)</sup> Unfortunately, it also caused degradation of device field-effect mobility  $\mu_{eff}$ . The Si source gas previously used during depositions of the gate insulators and channel was 4% SiH<sub>4</sub> in H<sub>2</sub>. <sup>9)</sup> Since a N-rich a-SiN<sub>x</sub> layer can be used to improve the TFT performance, <sup>4)</sup> in this study, the Si source gases employed were 4% SiH<sub>4</sub> in N<sub>2</sub> for gate insulators and 4% SiH<sub>4</sub> in H<sub>2</sub> for i- and n<sup>+</sup>-a-Si:H

layers, respectively. Then, a  $N_2O$ -plasma treatment of the as-deposited a-SiO<sub>x</sub>N<sub>y</sub>/a-SiN<sub>x</sub> gate insulators was performed again to improve the electrical stability of an inverted-staggered a-Si:H TFT.

#### 2. Experiments

The inset in Fig. 1 depicts the schematic cross section of the fabricated a-Si:H TFT. After patterning of the sputter-deposited 1500 Å Cr gates on the Corning 7059 glass substrate, the a-SiO<sub>x</sub>N<sub>y</sub> (1400 Å)/a-SiN<sub>x</sub> (400 Å), i-a-Si:H (1450 Å) and n<sup>+</sup>-a-Si:H (500 Å) films were deposited consecutively in a plasma-enhanced chemical vapor deposition (PECVD, ULVAC CPD-1108D) system. During the deposition process, the RF power densities and chamber pressures for the  $a-SiO_xN_y$ ,  $a-SiN_x$ , i-a-Si:H, and  $n^+$ -a-Si:H films were kept at 50, 50, 28,  $21 \text{ mW/cm}^2$  and 0.3, 0.45, 0.3, 0.4 Torr, respectively. The substrate temperatures were kept at 180°C for n<sup>+</sup>-a-Si:H layer and 250°C for the others. The Al source/drain metal was thermally evaporated and then patterned with the conventional photolithographic technique. CF<sub>4</sub>-O<sub>2</sub> plasma etching was used to expose the gate electrode of TFT and also to remove the n<sup>+</sup>-a-Si:H layer between Al source/drain electrodes. For device passivation, a 2000 Å of SiO<sub>2</sub> was sputtered onto the a-Si:H TFT.

The  $N_2O$ -plasma treatment was performed immediately following the deposition of the a-SiN<sub>x</sub> layer. The treatment conditions were RF power density of 28 mW/cm², chamber pressure of 0.25 Torr, substrate temperature of 250°C,  $N_2O$  flow rate of 100 sccm and treatment time of 12 min. Also, a NH<sub>3</sub>-plasma treatment with the same process conditions was also employed for the purpose of comparison. The other fabrication conditions for the devices with/without treatment were kept the same.

The electrical characteristics of the a-Si:H TFTs were measured with an HP 4145B semiconductor parameter analyzer.  $V_{\rm th}s$  and  $\mu_{\rm eff}s$  were determined from the x-axis intercept and the slope of the TFT square-law model. In calculation of the  $\mu_{\rm eff}$ , the capacitance in the TFT square-law model was measured using the metal/gate insulators/metal capacitor.

#### 3. Results and Discussion

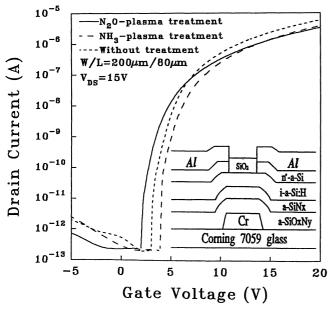

Figure 1 shows the transfer curves for three kinds of a-Si:H TFTs: (a) with N<sub>2</sub>O-plasma treatment, (b) with NH<sub>3</sub>-plasma treatment, and (c) without treatment. All of the on/off current ratios for these three devices exceeded 10<sup>7</sup> as estimated from the ratios of drain currents,  $I_{DS}$ , at  $V_{DS}=0$  and 15 V. Their calculated  $V_{thS}$ were (a) 5.22, (b) 6.41, and (c) 5.73 V and the  $\mu_{\text{eff}}$ s were (a) 1.013, (b) 1.305, and (c)  $1.773 \text{ cm}^2/\text{V} \cdot \text{s}$ . The capacitance measured using an ITO/a-SiO<sub>x</sub>N<sub>y</sub>/a-SiN<sub>x</sub>/ Al capacitor were (a) 20.15, (b) 19.96 and (c) 19.93 nF/ cm<sup>2</sup>. When the subthreshold slope S, defined as  $dV_{GS}$ d (log  $I_D$ ), was calculated for  $I_D$  ranging from 10 pA to 1 nA, the corresponding S values for these three kinds of a-Si:H TFTs were (a) 0.508, (b) 0.470 and (c) 0.352 V/decade, which showed a slight increase after plasma treatment. This phenomenon was similar to that presented in ref. 7.

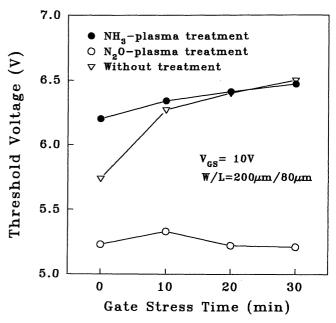

Figure 2 shows the variations of  $V_{\rm th}$  for these three kinds of a-Si:H TFTs after applying a gate bias of 10 V. As can be seen, the TFT with a N<sub>2</sub>O-plasma treatment had the smallest  $V_{\rm th}$  and  $V_{\rm th}$  shift.

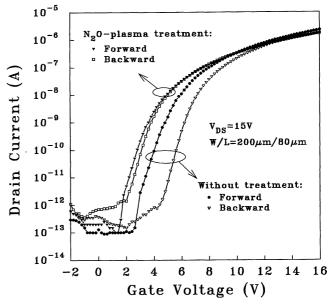

Figure 3 shows the forward and backward transfer characteristics of the a-Si:H TFTs with and without  $N_2O$ -plasma treatment. During the measurement of forward and backward transfer curves for the a-Si:H TFTs, a delay time of 5 s was used after each  $V_{\rm GS}$  voltage step. It took about 25 min to complete the entire transfer curves for  $V_{\rm GS}$  sweeping from -10 to 20 and then back to -10 V. This long measurement time allows the electron to be trapped deep in the gate insulator, kinetically causes the generation of a metastable state in a-Si:H, and forms the hysteresis curve in the forward and backward sweepings of transfer characteristics. The experimental data for voltages below -2

Fig. 1. The transfer characteristics of the three obtained a-Si:H TFTs (a) with  $N_2O$  plasma, (b) with  $NH_3$  plasma, and (c) without treatment of gate insulators. The inset shows a schematic cross section of the inverted-staggered a-Si:H TFT.

Fig. 2. The variations of  $V_{\rm th}$  after applying a gate bias of 10 V for these three a-Si:H TFTs (a) with N<sub>2</sub>O plasma, (b) with NH<sub>3</sub> plasma and (c) without treatment of gate insulators.

Fig. 3. The forward and backward transfer characteristics for the a-Si:H TFTs with and without  $\rm N_2O$ -plasma treatment of gate insulators.

V and above 16 V were omitted to emphasize the hysteresis phenomenon. The  $W_{\rm FBS}$ , taken from the maximum separations between the forward and backward transfer curves of a-Si:H TFTs, were 0.345 and 1.701 V for the devices with and without N<sub>2</sub>O-plasma treatment, respectively. On the other band, the  $W_{\rm FB}$  of the NH<sub>3</sub>-plasma-treated device was 0.776 V. Hence, the N<sub>2</sub>O-plasma-treated a-Si:H TFT had the smallest  $W_{\rm FB}$ .

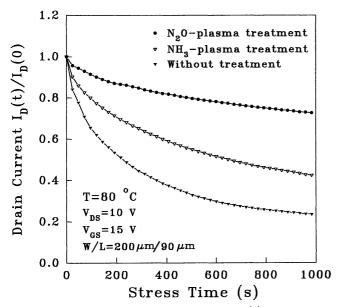

Figure 4 shows the time dependence of drain current  $I_{\rm D}(t)$  normalized by its initial value  $I_{\rm D}(0)$  for these three devices at a temperature of 80°C. The decay of  $I_{\rm D}(t)/I_{\rm D}(0)$  with time for the N<sub>2</sub>O-plasma-treated device was

Fig. 4. The time dependence of drain current  $I_{\rm D}(t)$  normalized by its initial value  $I_{\rm D}(0)$  for these three a-Si:H TFTs at a temperature of 80 °C.

found to be the smallest.

Table I lists the refractive indices (at a wavelength  $\lambda$  of 632.9 nm) and thicknesses before and after the different plasma treatments for the a-SiN<sub>x</sub> layers grown on the Si wafers. These data were measured using a Woollam 12-wavelength spectroscopic ellipsometry. The thicknesses and refractive indices were nearly unchanged after plasma treatments.

Table II summarizes some electrical parameters of these three devices with  $W/L=200/90~(\mu m/\mu m)$ . The data presented are the ranges of at least 5 sets of

Table I. The refractive indices and thicknesses before and after different plasma treatments for the  $\text{a-SiN}_x$  layers grown on Si wafers.

| Treatment               | Thickness (nm) |       | Refractive Index $(\lambda = 632.9 \text{ nm})$ |        |

|-------------------------|----------------|-------|-------------------------------------------------|--------|

|                         | Before         | After | Before                                          | After  |

| N <sub>2</sub> O-plasma | 105.2          | 105.0 | 1.8441                                          | 1.8448 |

| NH <sub>3</sub> -plasma | 102.8          | 102.5 | 1.8445                                          | 1.8433 |

Table II. A summary of some electrical parameters for these three kinds of a-Si:H TFTs.

| Treatment                          | $V_{ m th} \ ({ m V})$               | $\mu_{ m eff} \ ({ m cm^2/V \cdot s})$ | S (V/decade)                             |

|------------------------------------|--------------------------------------|----------------------------------------|------------------------------------------|

| Without<br>NH <sub>3</sub> -plasma | $5.46 \sim 5.80$<br>$5.96 \sim 6.40$ | $1.53 \sim 1.58$ $1.22 \sim 1.24$      | $0.348 \sim 0.357$<br>$0.467 \sim 0.491$ |

| $N_2O$ -plasma                     | $4.98 \sim 5.55$                     | $0.96 \sim 1.01$                       | $0.495 \sim 0.528$                       |

results taken from the corresponding devices on the substrates. It was clear the  $N_2$ O-plasma-treated device had the smaller  $V_{\rm th}$  and  $W_{\rm FB}$ . However,  $\mu_{\rm eff}$  of the  $N_2$ O-plasma-treated a-Si:H TFT obviously decreased and that of the NH<sub>3</sub>-plasma-treated device decreased only moderately.

Furthermore, secondary ion mass spectroscopy (SIMS) analysis of the N<sub>2</sub>O-plasma-treated TFT showed a lower H concentration in the surface region of a-SiN<sub>x</sub> layer and a higher O concentration at the interface of a-SiN<sub>x</sub>/a-Si:H, as compared to those of a TFT without plasma treatment. This incorporation of O atoms after N<sub>2</sub>O-plasma treatment might degrade the N-rich condition of a-SiN<sub>x</sub> film, resulting in a decrease of  $\mu_{\rm eff}$ . Also, the reduction of the H concentration could lead to higher electrical stability of the N<sub>2</sub>O-plasma-treated device, since the hydrogen-induced defects might be the trapping centers which induced the  $V_{\rm th}$  shift. 8)

## 4. Conclusions

In conclusion, the obtained inverted-staggered a-Si:H TFTs with the N<sub>2</sub>O-plasma-treated a-SiO<sub>x</sub>N<sub>y</sub>/a-SiN<sub>x</sub> gate insulators had lower  $V_{\rm th}$ ,  $V_{\rm th}$  shift and  $W_{\rm FB}$ , as compared to those of the devices with NH<sub>3</sub>-plasma treatment and without treatment. The BTS experiments also showed that the N<sub>2</sub>O-plasma-treated device had a higher resistance against a prolonged positive gate bias. However,  $\mu_{\rm eff}$  of the N<sub>2</sub>O-plasma-treated a-Si:H TFT obviously decreased. From the above results, we concluded that N<sub>2</sub>O-plasma treatment of the as-deposited a-SiO<sub>x</sub>N<sub>y</sub>/a-SiN<sub>x</sub> gate insulators could be used to improve the electrical stability of a-Si:H TFTs.

### Acknowledgement

This work was supported by the National Science Council of the Republic of China, under contract NSC 80-0417-E008-05.

- M. J. Powell, B. C. Easton and D. H. Nicholls: J. Appl. Phys. 53 (1982) 5068.

- M. J. Powell, C. V. Berkel, I. D. French and D. H. Nicholls: Appl. Phys. Lett. 51 (1987) 1242.

- 3) K. Hiranaka and T. Yamaguchi: J. Appl. Phys. 67 (1990) 1088.

- K. Hiranaka and T. Yamaguchi: Jpn. J. Appl. Phys. 29 (1990) 229.

- N. H. Nickel, W. Fuhs, H. Mell and W. Beyer: Proc. Mater. Res. Soc. Symp. 284 (1993) 395.

- J. Jang, M. Y. Jung, S. S. Yoo, H. K. Song and J. M. Jun: Proc. Mater. Res. Soc. Symp. 258 (1992) 973.

- 7) S. Luan and G. W. Neudeck: J. Appl. Phys. 68 (1990) 3445.

- R. Carluccio, G. Fortunato and W. I. Milne: J. Non-Cryst. Solids 164-166 (1993) 751.

- T. S. Jen, T. C. Chou, S. T. Leu, N. F. Shin, W. C. Tsay and J. W. Hong: Proc. Electron. Devices & Mater. Symp., Taiwan, R.O.C., 1993 (Chung Yuan Christian University, Chungli, 1993) p. 64.