Home Search Collections Journals About Contact us My IOPscience

Material growth and device characterization of AlGaN/GaN single-heterostructure and AlGaN/GaN/AlGaN double-heterostructure field effect transistors on Si substrates

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2014 Appl. Phys. Express 7 055501

(http://iopscience.iop.org/1882-0786/7/5/055501)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/12/2014 at 02:50

Please note that terms and conditions apply.

http://dx.doi.org/10.7567/APEX.7.055501

## Material growth and device characterization of AlGaN/GaN single-heterostructure and AlGaN/GaN/AlGaN double-heterostructure field effect transistors on Si substrates

Yu-Lin Hsiao<sup>1</sup>, Chia-Ao Chang<sup>1</sup>, Edward Yi Chang<sup>1\*</sup>, Jer-Shen Maa<sup>3</sup>, Chia-Ta Chang<sup>1</sup>, Yi-Jie Wang<sup>2</sup>, and You-Chen Weng<sup>3</sup>

Received February 14, 2014; accepted March 31, 2014; published online April 16, 2014

An  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  double-heterostructure field effect transistor (DH-FET) structure was grown on a 150-mm-diameter Si substrate and the crystalline quality of the epitaxial material was found to be comparable to that of an  $Al_{0.2}Ga_{0.8}N/GaN$  single-heterostructure field effect transistor (SH-FET) structure. The fabricated DH-FET shows a lower buffer leakage current of  $9.2 \times 10^{-5}$  mA/mm and an improved off-state breakdown voltage of higher than 200 V, whereas the SH-FET shows a much higher buffer leakage current of  $6.0 \times 10^{-3}$  mA/mm and a lower breakdown voltage of 130 V. These significant improvements show that the  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  DH-FET is an effective structure for high-power electronic applications. © 2014 The Japan Society of Applied Physics

wing to the superior material properties of GaN, including high breakdown field, wide band gap, high saturated electron velocity, and high operation temperature, GaN-based devices have attracted much attention for high-power switching applications.<sup>1)</sup> Conventional AlGaN/ GaN single-heterostructure field effect transistors (SH-FETs) fabricated on SiC, sapphire and Si substrates all exhibit high breakdown voltage and low specific on-resistance characteristics.<sup>2–4)</sup> The difficulties of the large lattice mismatch and the large thermal mismatch between GaN and Si substrates have been overcome in recent years. The extraordinary development has made GaN-on-Si technology for high-power and high-frequency devices on Si substrates with diameters larger than 150 mm realizable.5-7) The production of GaN devices on large-diameter Si substrates at a low fabrication cost is considered the key factor for leading GaN-based devices into the next-generation power electronic market.

In order to further improve the breakdown voltage of the GaN-on-Si devices, several methods have been proposed over the last few years, such as the use of a thicker epitaxial layer, the inclusion of a carbon-doped GaN buffer, the implementation of a field plate structure, ion-implantation isolation, and local Si substrate removal. (8-13) Additionally, AlGaN/GaN/AlGaN double-heterostructure field effect transistors (DH-FETs) for high-breakdown-voltage devices were also investigated because of the better electron confinement and higher breakdown field when using the AlGaN back barrier. (14,15) However, even with these advances, studies focusing on the comparison of the device performances of SH-FETs and DH-FETs fabricated on larger diameter Si substrates are still lacking. (16)

In this work, an  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  DH-FET structure with an  $Al_{0.1}Ga_{0.9}N$  back barrier and a conventional  $Al_{0.2}Ga_{0.8}N/GaN$  SH-FET structure with a GaN buffer were grown on 150-mm-diameter Si substrates. Both wafers show good crystalline quality. The epitaxial layer growth process and the crystal quality of the DH-FET and SH-FET structures on Si substrates are discussed and the device performances are compared in this study. It is found that the breakdown voltage of the DH-FET is greatly improved with the  $Al_{0.1}Ga_{0.9}N$  back barrier layer.

The epitaxial growth of the DH-FET and SH-FET structures on 150-mm-diameter Si(111) substrates were carried out

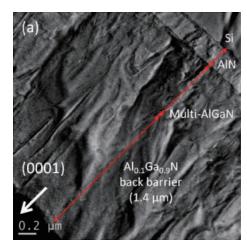

using a Thomas Swan metal organic chemical vapor deposition (MOCVD) system. Trimethylgallium (TMGa), trimethylaluminum (TMAl), and ammonia were used as the precursors for Ga, Al, and N elements, respectively. H<sub>2</sub> was used as the carrier gas. Firstly, an AlN nucleation layer (200 nm) and multi- $Al_xGa_{1-x}N$  transition layers (600 nm) were grown on the Si substrate. Following the transition layer growth, the  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  (27 nm/ 55 nm/1.4 µm) epitaxial layers were grown for the DH-FET. The cross-sectional transmission electron microscopy (TEM) images of the whole DH-FET epitaxial structure and the Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN/Al<sub>0.1</sub>Ga<sub>0.9</sub>N heterostructure layers are shown in Figs. 1(a) and 1(b), respectively. The sample of the  $Al_{0.2}Ga_{0.8}N/GaN$  SH-FET (27 nm/2.6  $\mu$ m) structure was grown on the same AlN and multi-Al<sub>x</sub>Ga<sub>1-x</sub>N buffer layers as the control sample for device performance comparison.

A Laytec EpiCurve<sup>®</sup> TT system was used for in-situ measurement of the wafer temperature, reflectance, and wafer curvature during epitaxial layer growth. The crystalline qualities of these two structures were examined using the high-resolution X-ray diffraction (HRXRD) Bede D1 system. From room-temperature Hall measurements, the mobility of  $1110~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$  and the sheet carrier concentration of  $8.5~\times~10^{12}/\text{cm}^2$  were obtained on the DH-FET structure. The SH-FET structure exhibited the mobility of  $1270~\text{cm}^2~\text{V}^{-1}~\text{s}^{-1}$  and the sheet carrier concentration of  $8.7~\times~10^{12}/\text{cm}^2$ .

The DH-FET and SH-FET devices were fabricated after the epitaxial growth. The device mesa regions were defined using an inductively coupled plasma (ICP) etcher. The Ti/Al/Ni/Au (20/120/25/100 nm) multilayer metal was deposited as the source and drain ohmic contact metal using an electron beam evaporator, and was subsequently annealed at 800 °C for 60 s in N2 atmosphere. According to the transmission line model method, the ohmic contact resistances of 0.5 and 0.6 Ω·mm were obtained for the DH-FET and SH-FET structures, respectively. Finally, the Ni/Au (20/300 nm) metal was deposited as a Schottky gate metal using the electron beam evaporator. The gate width  $(W_g)$ , gate length  $(L_g)$ , gate-to-drain spacing  $(L_{gd})$ , and gate-to-source spacing  $(\tilde{L}_{gs})$  were 100, 1, 4.5, and 1.5  $\mu m$ , respectively. The electrical characteristics of the devices were measured using Agilent E5270B.

<sup>&</sup>lt;sup>1</sup>Department of Materials Science and Engineering, National Chiao-Tung University, Hsinchu, Taiwan

<sup>&</sup>lt;sup>2</sup>Institute of Photonic System, College of Photonics, National Chiao-Tung University, Tainan, Taiwan

<sup>&</sup>lt;sup>3</sup>Institute of Lighting and Energy Photonics, College of Photonics, National Chiao-Tung University, Tainan, Taiwan E-mail: edc@mail.nctu.edu.tw

Fig. 1. Cross-sectional TEM images of (a) DH-FET structure with AlN and multi-AlGaN buffer layers on the Si substrate, and (b)  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  double heterostructure.

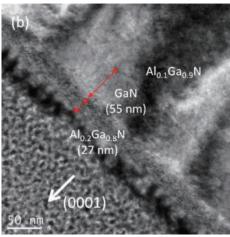

Figure 2 shows the transients of temperature and reflectance (upper figure) and the wafer curvature (lower figure) obtained with a Laytec EpiCurve® TT system during the growth of the  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  DH-FET structure. The growth rate was  $1.4\,\mu\text{m}/h$  and the layer thickness was  $1.4\,\mu\text{m}$  for the  $Al_{0.1}Ga_{0.9}N$  back barrier, as determined from the Fabry–Perot oscillations using the reflectance at 950 nm. The reflectance intensity maxima and minima occurred at constant values during the growth of the  $Al_{0.1}Ga_{0.9}N$  back barrier. This indicates that the epitaxial layers were quite smooth. Meanwhile, a SH-FET with a 2.6- $\mu$ m-thick GaN buffer was grown on a Si substrate for comparison.

The in-situ wafer curvature measurement is essential for optimizing growth recipes and controlling the stress in order to maintain crack-free wafers. By emitting two parallel laser beams from the Laytec EpiCurve® TT curve head, the curvature can be calculated from the difference between the initial separation distance of the parallel beams and the distance between reflected laser beams. A convex wafer means a negative curvature due to compressive stress. For the DH-FET, a negative curvature trace was observed during the growth of the multi-Al $_x$ Ga $_{1-x}$ N transition layers and the Al $_{0.1}$ Ga $_{0.9}$ N back barrier, indicating that an effective compressive stress was introduced. Owing to the significant

Fig. 2. Data of in situ measurements of temperature, reflectance, and wafer curvature during the growth of DH-FET.

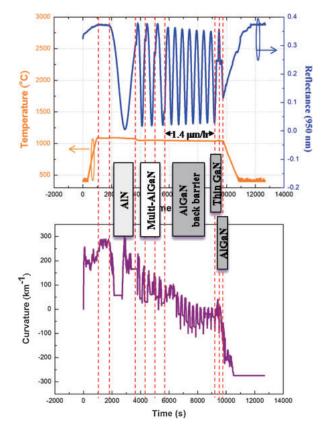

Fig. 3. XRD  $\omega$ =2 $\theta$  scan of DH-FET epitaxial structure. The inset shows the rocking curve of the Al<sub>0.1</sub>Ga<sub>0.9</sub>N(002) peak.

difference between thermal expansion coefficients of GaN and the Si substrate, this compressive stress induced in the epitaxial layer is necessary to compensate for the tensile stress during the cooling process.

Figure 3 shows HRXRD  $\omega$ – $2\theta$  scanning and rocking curve results for the DH-FET. The Al composition of 10.3% in the AlGaN(002) peak shows the highest intensity in the  $\omega$ – $2\theta$  scan. A higher Al composition in AlGaN is required to provide a higher conduction band discontinuity. However, when the Al composition is above 10%, the thermal conductivity of AlGaN becomes quite low because of alloy scattering. Therefore, the Al composition should be kept below 10% for the growth of the Al<sub>x</sub>Ga<sub>1-x</sub>N back barrier.

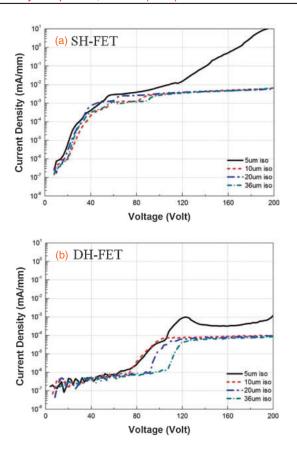

Fig. 4. Buffer leakage currents of (a) SH-FET and (b) DH-FET with various metal contact spacings.

Compared with the GaN buffer used for SH-FET, the DH-FET buffer has better electron confinement in the GaN channel owing to a higher conduction band discontinuity, which helps to prevent the leakage current at the  $Al_{0.1}Ga_{0.9}N$  back barrier. The full-widths at half-maximum (FWHMs) of X-ray rocking curves for the  $Al_{0.1}Ga_{0.9}N(002)$   $\omega$ -scan and  $Al_{0.1}Ga_{0.9}N(102)$   $\omega$ -scan were 578.8 and 1110 arcsec, respectively. On the other hand, the SH-FET exhibited the FWHMs of 473.8 and 653.8 arcsec for the GaN(002)  $\omega$ -scan and GaN(102)  $\omega$ -scan, respectively. The SH-FET has narrower FWHMs owing to the presence of the 2.6- $\mu$ m-thick GaN buffer. However, the crystalline quality of the  $Al_{0.1}Ga_{0.9}N$  back barrier is comparable to those in other studies of AlGaN with 10% Al composition in the literature. <sup>18,19</sup>

The buffer leakage current characteristics of the SH-FET and DH-FET measured using different ohmic contact spacings are plotted in Figs. 4(a) and 4(b), respectively. When measured with isolation patterns with a 5  $\mu m$  gap, the breakdown voltage of the SH-FET is 170 V, as defined by the leakage current of 1 mA/mm. However, the breakdown voltage of the DH-FET is more than 200 V. The buffer leakage current of the DH-FET is 9.2  $\times$  10 $^{-5}$  mA/mm when measured at 200 V with an isolation pattern having a 20  $\mu m$  gap, which is much lower than that of the SH-FET measured under the same conditions (6.0  $\times$  10 $^{-3}$  mA/mm). The reduced buffer leakage current of the DH-FET indicates that the higher conduction band discontinuity and higher breakdown field of the Al $_{0.1}$ Ga $_{0.9}$ N back barrier can effectively reduce the leakage of the electrons from the channel to the buffer.

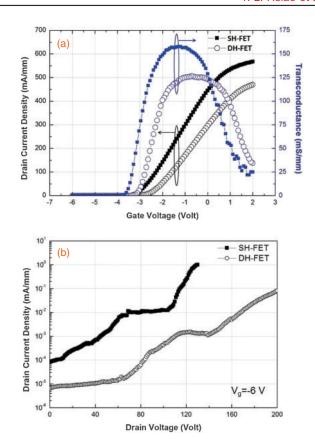

Fig. 5. Device characteristics of SH-FET and DH-FET  $(W_{\rm g}/L_{\rm g}/L_{\rm gd}/L_{\rm gs}=100/1/4.5/1.5~\mu m)$ . (a)  $I_{\rm D}$ – $V_{\rm G}$  transfer characteristics and (b) breakdown voltage characteristics.

The transfer characteristics and leakage currents of the SH-FET and DH-FET are plotted in Figs. 5(a) and 5(b), respectively. The fabricated devices have a gate-to-drain spacing  $(L_{\rm gd})$  of 4.5 µm. The maximum drain current density of  $475 \,\mathrm{mA/mm}$  under  $V_{\mathrm{g}} = 2 \,\mathrm{V}$  for the DH-FET is lower than the current density of the SH-FET. The reduction in drain current density may result from the lower sheet carrier concentration of the DH-FET. Additionally, the lower sheet carrier concentration results in the threshold voltage shift. The threshold voltage shifted positively from  $-3.2\,\mathrm{V}$ for the SH-FET to  $-2.3 \,\mathrm{V}$  for the DH-FET. Moreover, a lower leakage current for the DH-FET was observed. A higher breakdown voltage of greater than 200 V for the DH-FET was achieved compared with the 130 V observed for the SH-FET. The improvement of buffer isolation by using an Al<sub>0.1</sub>Ga<sub>0.9</sub>N back barrier also reduces the punchthrough effects and thus markedly improve the breakdown voltage of the device.20) Although the total thickness of the Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN/Al<sub>0.1</sub>Ga<sub>0.9</sub>N DH-FET is much smaller than that of the Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN SH-FET, the device still demonstrates improved breakdown voltage characteristics. Overall, the study reveals that the Al<sub>0.1</sub>Ga<sub>0.9</sub>N back barrier can substantially improve the breakdown voltage of the device even with thinner buffer layers.

In conclusion, high-crystalline-quality  $Al_{0.2}Ga_{0.8}N/GaN$  SH-FET and  $Al_{0.2}Ga_{0.8}N/GaN/Al_{0.1}Ga_{0.9}N$  DH-FET structures were grown on 150-mm-diameter Si substrates, and the SH-FET and DH-FET devices were fabricated. For the DH-FET, a lower buffer leakage current of  $9.2 \times 10^{-5} \, \text{mA/mm}$  and an improved off-state breakdown voltage of higher than

200 V were realized, compared with the SH-FET. Because of the higher conduction band discontinuity and the better electron confinement in the channel, the Al<sub>0.1</sub>Ga<sub>0.9</sub>N back barrier of the DH-FET can effectively prevent punch-through effects, resulting in a lower leakage current than that of the GaN buffer SH-FET, and thus greatly reduces the buffer thickness needed for the GaN power devices. Overall, it was demonstrated that the Al<sub>0.2</sub>Ga<sub>0.8</sub>N/GaN/Al<sub>0.1</sub>Ga<sub>0.9</sub>N DH-FET approach with improved device characteristics resulting from the use of a thinner buffer layer is a promising technology for future high-power electronic applications.

**Acknowledgments** This work was sponsored by the NCTU-UCB I-RiCE program, National Science Council, Taiwan, under Grant No. NSC 103-2911-I-009-302 and the Ministry of Economic Affairs, Taiwan, under Grant No. 101-EC-17-A-05-S1-154.

- N. Ikeda, Y. Niiyama, H. Kambayashi, Y. Sato, T. Nomura, S. Kato, and S. Yoshida, Proc. IEEE 98, 1151 (2010).

- F. Brunner, E. Bahat-Treidel, M. Cho, C. Netzel, O. Hilt, J. Wuerfl, and M. Weyers, Phys. Status Solidi C 8, 2427 (2011).

- Y. Uemoto, D. Shibata, M. Yanagihara, H. Ishida, H. Matsuo, S. Nagai, N. Batta, M. Li, T. Ueda, T. Tanaka, and D. Ueda, Proc. Int. Electron Devices Meeting, 2007, p. 861.

- I. B. Rowena, S. L. Selvaraj, and T. Egawa, IEEE Electron Device Lett. 32, 1534 (2011).

- D. Christy, T. Egawa, Y. Yano, H. Tokunaga, H. Shimamura, Y. Yamaoka, A. Ubukata, T. Tabuchi, and K. Matsumoto, Appl. Phys. Express 6, 026501 (2013).

- 6) K. Cheng, H. Liang, M. Van Hove, K. Geens, B. De Jaeger, P. Srivastava, X. Kang, P. Favia, H. Bender, S. Decoutere, J. Dekoster, J. del Agua Borniquel, S. W. Jun, and H. Chung, Appl. Phys. Express 5, 011002 (2012).

- S. Arulkumaran, G. I. Ng, S. Vicknesh, H. Wang, K. S. Ang, J. P. Y. Tan, V. K. Lin, S. Todd, G.-Q. Lo, and S. Tripathy, Jpn. J. Appl. Phys. 51, 111001 (2012).

- A. Dadgar, T. Hempel, J. Bläsing, O. Schulz, S. Fritze, J. Christen, and A. Krost, Phys. Status Solidi C 8, 1503 (2011).

- S. L. Selvaraj, A. Watanabe, A. Wakejima, and T. Egawa, IEEE Electron Device Lett. 33, 1375 (2012).

- 10) S. Kato, Y. Satoh, H. Sasaki, I. Masayuki, and S. Yoshida, J. Cryst. Growth 298, 831 (2007).

- 11) J. Lee, B. Park, H. Lee, M. Lee, K. Seo, and H. Cha, Appl. Phys. Express 5, 066502 (2012).

- 12) M. Sun, H. Lee, B. Lu, D. Piedra, and T. Palacios, Appl. Phys. Express 5, 074202 (2012).

- 13) P. Srivastava, J. Das, D. Visalli, M. Van Hove, P. E. Malinowski, D. Marcon, S. Lenci, K. Geens, K. Cheng, M. Leys, S. Decoutere, R. P. Mertens, and G. Borghs, IEEE Electron Device Lett. 32, 30 (2011).

- 14) Z. Chen, Y. Pei, S. Newman, D. Brown, R. Chung, S. Keller, S. P. DenBaars, S. Nakamura, and U. K. Mishra, Appl. Phys. Lett. 94, 171117 (2009)

- 15) A. Zanandrea, E. Bahat-Treidel, F. Rampzaao, A. Stocco, M. Meneghini, E. Zanoni, O. Hilt, P. Ivo, J. Wuerfl, and G. Meneghesso, Microelectron. Reliab. 52, 2426 (2012).

- 16) D. Visalli, M. Van Hove, J. Derluyn, S. Degroote, M. Leys, K. Cheng, M. Germain, and G. Borghs, Jpn. J. Appl. Phys. 48, 04C101 (2009).

- 17) W. Liu and A. A. Balandin, Appl. Phys. Lett. 85, 5230 (2004).

- 18) K. Cheng, M. Leys, J. Derluyn, K. Balachander, S. Degroote, M. Germain, and G. Borghs, Phys. Status Solidi C 5, 1600 (2008).

- 19) P. Saengkaew, A. Dadgar, J. Blaesing, T. Hempel, P. Veit, J. Christen, and A. Krost, J. Cryst. Growth 311, 3742 (2009).

- E. Bahat-Treidel, O. Hilt, F. Brunner, J. Wuerfl, and G. Tränkle, Phys. Status Solidi C 6, 1373 (2009).