## Investigation of LaAlO<sub>3</sub>/ZrO<sub>2</sub>/a-InGaZnO thin-film transistors using atmospheric pressure plasma jet

Chien-Hung Wu, Hau-Yuan Huang, Shui-Jinn Wang, Kow-Ming Chang and Hsin-Yu Hsu

Amorphous indium–gallium–zinc-oxide thin-film transistors (*a*-IGZO-TFTs) with the LaAlO<sub>3</sub>/ZrO<sub>2</sub> gate dielectric stack employing a novel atmospheric pressure plasma jet process that results in small subthreshold swing and low threshold voltage are proposed and fabricated. The influence of post-deposition annealing (PDA) temperature on LaAlO<sub>3</sub>/ZrO<sub>2</sub> gate dielectric stack and device performance was investigated. The equivalent oxide thickness of the LaAlO<sub>3</sub>/ZrO<sub>2</sub> dielectric stack decreases from 11.5 nm without annealing to 7 nm after a 500°C annealing was applied. The LaAlO<sub>3</sub>/ZrO<sub>2</sub>/*a*-InGaZnO TFT with a 500°C annealing exhibits a small subthreshold swing of 77 mV·dec<sup>-1</sup>, a high field-effect mobility of 9 cm²·V<sup>-1</sup>·s<sup>-1</sup> and an excellent current ratio of 1.8 × 10<sup>7</sup>, which could be attributed to the improved gate dielectric quality by the PDA. The LaAlO<sub>3</sub>/ZrO<sub>2</sub>/*a*-InGaZnO TFTs with excellent gate control ability allow the device to operate at a low operating voltage with low power consumption.

Introduction: Of the abundant AOS compound materials, amorphous indium-gallium-zinc-oxide thin-film transistors (a-InGaZnO TFTs) attract considerable interest for backplanes of the next-generation flatpanel displays as active matrix liquid crystal displays and active matrix organic light-emitting diode displays. Owing to their better field-effect mobility >10 cm<sup>2</sup>/V·s and better stability against electrical stress [1, 2]. The non-vacuum techniques such as solution-processed InGaZnO films [3, 4] and atmospheric pressure plasma jet (APPJ) InGaZnO films were proposed recently [5, 6]. The APPJ technique has lower apparatus cost since it does not need a vacuum chamber and associated pumping systems; it also has better suitability for large-scale applications among the other deposition technologies. To further improve the device performance, high-κ materials of ZrO<sub>2</sub> and HfO2 have been investigated for their superior properties for advanced TFT devices, such as high breakdown field intensity (10~15 MV/cm), high dielectric constant (20~25) and the capability of room-temperature processing [7, 8]. In this Letter, the fabrication of bottom-gate IGZO-TFTs with an LaAlO<sub>3</sub>/ZrO<sub>2</sub> gate dielectric stack (40 nm/10 nm) is reported. The equivalent oxide thickness (EOT) of the LaAlO<sub>3</sub>/ ZrO<sub>2</sub> dielectric stack shrinks from 11.5 nm before post-deposition annealing (PDA) to 7 nm after a 500°C PDA. Excellent gate control ability with a small subthreshold swing (SS) of 77 mV·dec<sup>-1</sup>, high field-effect mobility ( $\mu_{\text{fet}}$ ) of 9 cm<sup>2</sup> V<sup>-1</sup>·s<sup>-1</sup>, high current ratio ( $I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{on}}/I_{\text{$  $I_{\rm min}$ ) of 1.8 × 10<sup>7</sup> and low operation voltage of 3.0 V are attributed to the improved gate dielectric quality by the PDA.

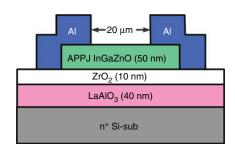

Experiments: Fig. 1 shows the schematic of the fabricated LaAlO<sub>3</sub> (40 nm)/ZrO<sub>2</sub> (10 nm)/IGZO (50 nm) TFT. The staggered bottom-gate a-IGZO-TFTs were fabricated on heavily doped n-type silicon substrates. High-k gate dielectrics of LaAlO3 and ZrO2 were deposited by an e-beam evaporation with thicknesses of 40 and 10 nm, respectively, on the silicon substrate which served as the gate electrode. PDA was then carried out at various temperatures (T) between 300 and 500°C in N2 for 10 min. Subsequently, a 50 nm-thick a-IGZO layer was deposited by APPJ. The substrate temperature was kept at 200°C during deposition of InGaZnO. Trimethylaluminium (Al<sub>2</sub>(CH<sub>3</sub>)<sub>6</sub>, TMA) and oxygen plasma reactants were used as precursors and oxidants, respectively. Indium nitrate (In(NO<sub>3</sub>)<sub>2</sub>), gallium nitrate (Ga(NO<sub>3</sub>)<sub>2</sub>) and zinc nitrate (Zn(NO<sub>3</sub>)<sub>2</sub>) were used as the precursor materials. The concentration of the InGaZnO solution was kept at 0.2 M and was ultrasonically atomised at 2.45 MHz into mist and then conveyed by the carrier gas (N2) to the plasma region connected to a pulsed DC power supply at a repetition rate of 25 kHz and voltage pulse of 15 kV with a pulse width of 8 µs to generate the downstream plasma. The InGaZnO film was deposited and patterned through photolithography and wet etching. Finally, 300 nm-thick Al source/ drain contacts were thermally deposited and formed by the lift-off. The channel width (W) and length (L) were 200 and 20  $\mu$ m, respectively. Al/LaAlO<sub>3</sub>/ZrO<sub>2</sub>/p-Si (MIS structure) capacitors were fabricated simultaneously for C–V performance characterisation. The devices were characterised under an open air condition at room temperature using a semiconductor parameter analyser (2636A, Keithley, USA).

Fig. 1 Schematic diagram of bottom-gate ZrO<sub>2</sub>/LaAlO<sub>3</sub>/IGZO-TFT

Results and discussion: The optical transmittance spectra of the a-IGZO films deposited on a glass substrate are shown in Fig. 2. The average transmittance of a-IGZO films on a glass substrate are more than 80% in the visible range. The transmittance spectrum of the glass substrate is also indicated. In a direct-transition semiconductor, the absorption coefficient,  $\alpha$ , and optical band gap  $(E_{\rm g})$  are related by Tang et al. [9] as follows:  $\alpha^2 = B(hv - E_{\rm g})$  and  $\alpha = 2.303[\log(1/T)]/d$ , where B is a constant, hv is the energy of the incident photon and T and d are the transmittance and thickness of the thin films. The band gap of a-IGZO films is about 3.35 eV.

Fig. 2 Optical transmission spectra of 50 nm-thick a-IGZO film on glass substrates by APPJ

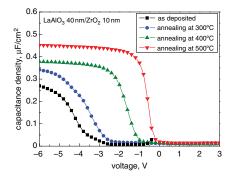

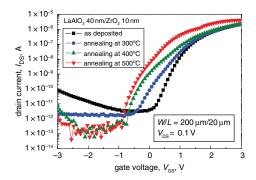

The *C–V* characteristics of the Al/LaAlO<sub>3</sub>/ZrO<sub>2</sub>/*p*-Si (MIS structure) are shown in Fig. 3. The capacitance of the Al/LaAlO<sub>3</sub>/ZrO<sub>2</sub>/p-Si capacitor increases with an increasing PDA temperature. The calculated EOTs of the LaAlO<sub>3</sub>/ZrO<sub>2</sub> dielectric stacks are 11.5, 10, 9 and 7 nm for the case without PDA and at annealing temperatures of 300, 400 and 500°C, respectively. The decrease in the flat-band voltage and increase in the slope with increasing T indicates that both the interface and the bulk traps of the dielectric stack are recovered by the high annealing temperature. With a sharper slope and a considerable shift towards positive  $V_{G}$ -axis for the  $V_{fb}$ , an improved LaAlO<sub>3</sub>/ZrO<sub>2</sub> gate dielectric quality could be obtained. The transfer curves of the IGZO-TFTs without and with the annealing temperatures of 300, 400 and 500°C are shown in Fig. 4. It is noted that the current maximum  $(I_{\text{max}})$  increases with increasing T, while the current minimum ( $I_{min}$ ) reduces to about  $10^{-13}$  A. The current ratio  $(I_{\rm max}/I_{\rm min})$  and the threshold voltage  $(V_{\rm t})$ are  $4.7 \times 10^5$  and 1.0 V,  $1.2 \times 10^6$  and 0.8 V,  $5.2 \times 10^6$  and 0.5 V, and  $1.8 \times 10^7$  and 0.1 V for the case without PDA and T = 300, 400 and 500°C. The  $\mu_{\text{fet}}$  and SS were extracted through the dependences of  $Lg_m/C_iWV_{DS}$  and  $\delta V_{GS}/\delta(\log I_{DS})$ , which are 8.3 cm<sup>2</sup>/V·s and 219 mV/ dec, 7.8 cm<sup>2</sup>/V·s and 335 mV/dec, 8 cm<sup>2</sup>/V·s and 109 mV/dec, and  $9 \text{ cm}^2/\text{V} \cdot \text{s}$  and 77 mV/dec for the case without PDA and T = 300, 400and 500°C. The improved SS at high T could be attributed to the increased gate oxide capacitance ( $C_{\rm ox}$ ) and therefore the higher  $\kappa$ value of the LaAlO<sub>3</sub>/ZrO<sub>2</sub> dielectric stack by the PDA; however, the deviation of SS and  $\mu_{\rm fet}$  at 300 and 400°C could be induced by the increment of interface traps since the annealing was applied before channel deposition, and a constant channel capacitance can be assumed [10]. The best device performances of  $I_{\rm max}/I_{\rm min}$ , SS,  $V_{\rm t}$  and  $\mu_{\rm fet}$  are 1.8 × 10<sup>7</sup>, 77 mV/dec, 0.1 V and 9 cm<sup>2</sup>/V·s, respectively, which were obtained for the case with T = 500°C. The comparisons of the ZrO<sub>2</sub>/ LaAlO<sub>3</sub>/IGZO-TFT with variant gate dielectric stacks are shown in Table 1.

Fig. 3 C-V characteristics of Al/LaAlO<sub>3</sub>/ZrO<sub>2</sub>/p-Si (MIS structure) gate capacitor annealed at different PDA temperatures

Fig. 4  $I_{DS}$ – $V_{GS}$  transfer characteristics of IGZO-TFT with LaAlO $_3$  (40 nm)/ $ZrO_2$  (10 nm) dielectric stack at different PDA temperatures

**Table 1:** Comparisons of LaAlO<sub>3</sub>/ZrO<sub>2</sub>/a-IGZO-TFT with variant gate dielectric stacks

| Dielectric materials                                 | Mobility<br>(cm <sup>2</sup> /V·s) | <i>V</i> <sub>t</sub> (V) | SS (mV/dec) | $I_{ m max}/I_{ m min}$ |

|------------------------------------------------------|------------------------------------|---------------------------|-------------|-------------------------|

| PVD LaAlO <sub>3</sub> /ZrO <sub>2</sub> , this work | 9                                  | 0.1                       | 77          | $1.8 \times 10^{7}$     |

| PE-ALD Al <sub>2</sub> O <sub>3</sub> [5]            | 8.4                                | 0.7                       | 280         | $1.0 \times 10^{8}$     |

| AP-CVD AlO <sub>x</sub> [6]                          | 4.2                                | 3.6                       | 550         | ~108                    |

| RF sputter ZrO <sub>2</sub> [7]                      | 28                                 | 3.2                       | 560         | $4.8 \times 10^{7}$     |

| RF sputter HfON/HfO <sub>2</sub> /HfON [8]           | 10.2                               | -0.92                     | 130         | $2.2 \times 10^{6}$     |

Conclusion: LaAlO<sub>3</sub>/ZrO<sub>2</sub>/a-IGZO-TFTs with a silicon gate have been fabricated successfully using the APPJ process. The devices feature a small SS of 77 mV·dec<sup>-1</sup>, a high  $\mu_{\rm FET}$  of 9 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> and a good  $I_{\rm max}/I_{\rm min}$  of  $1.8\times10^7$  with 500°C annealing of the LaAlO<sub>3</sub>/ZrO<sub>2</sub> dielectric stack. The integration of high- $\kappa$  LaAlO<sub>3</sub>/ZrO<sub>2</sub> dielectrics into IGZO-TFTs attains the aim of enhancing the gate control ability. It is expected that LaAlO<sub>3</sub>/ZrO<sub>2</sub>/a-IGZO-TFTs might have great potential for applications in low power-consuming and high-end displays.

Acknowledgments: This work was supported by the National Science Council of Taiwan, Republic of China, under grants NSC 100-2221-E-006-156-MY2, NSC 100-2221-E-006-045-MY2 and NSC

102-2221-E-006-217-MY2. The authors thank the Center for Micro/Nano Science and Technology, National Cheng Kung University, Taiwan, for equipment access and technical support.

© The Institution of Engineering and Technology 2014 7 March 2014

doi: 10.1049/el.2014.0816

One or more of the Figures in this Letter are available in colour online.

Chien-Hung Wu (Department of Electronics Engineering, Chung Hua University, Hsinchu, Taiwan)

E-mail: rossiwu@chu.edu.tw

Hau-Yuan Huang and Shui-Jinn Wang (Department of Electrical Engineering, Institute of Microelectronics, National Cheng Kung University, Tainan, Taiwan)

Kow-Ming Chang and Hsin-Yu Hsu (Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan)

## References

- 1 Bak, J.Y., Yoon, S.M., Yang, S., Kim, G.H., Park, S.H.K., and Hwang, C.S.: 'Effect of In-Ga-Zn-O active layer channel composition on process temperature for flexible oxide thin-film transistors', *J. Vac. Sci. Technol. B*, 2012, 30, (4), pp. 041208-1-6

- 2 Lee, Y.S., Chen, W.J., Huang, J.S., and Wu, S.C.: 'Effects of composition on optical and electrical properties of amorphous in-Ga-Zn-O films deposited using radio-frequency sputtering with varying O<sub>2</sub> gas flows', *Thin Solid Film*, 2012, **520**, pp. 6942–6946

- 3 Kim, C.E., Cho, E.N., Moon, P., Kim, G.H., Kim, D.L., Kim, H.J., and Yun, I.: 'Density-of-states modeling of solution-processed InGaZnO thin-film transistors', *IEEE Electron Device Lett.*, 2010, 31, (10), pp. 1131–1133

- 4 Yang, Y.H., Yang, S.S., and Chou, K.S.: 'Characteristic enhancement of solution-processed In–Ga–Zn oxide thin-film transistors by laser annealing', *IEEE Electron Device Lett.*, 2010, 31, (9), pp. 969–971

- 5 Wu, C.H., Chang, K.M., Huang, S.H., Deng, I.C., Wu, C.J., Chiang, W. H., and Chang, C.C.: 'Characteristics of IGZO TFT prepared by atmospheric pressure plasma jet using PE-ALD Al2O3 gate dielectric', *IEEE Electron Device Lett.*, 2012, 33, (4), pp. 552–554

- Electron Device Lett., 2012, 33, (4), pp. 552–554

Furuta, M., Kawaharamura, T., Wang, D., Toda, T., and Hirao, T.: 'Electrical properties of the thin-film transistor with an indium-gallium-zinc oxide channel and an aluminium oxide gate dielectric stack formed by solution-based atmospheric pressure deposition', IEEE Electron Device Lett., 2012, 33, (6), pp. 851–853

- Lee, J.S., Chang, S., Koo, S.-M., and Lee, S.Y.: 'High-performance a-IGZO TFT with ZrO<sub>2</sub> gate dielectric fabricated at room temperature', *IEEE Electron Device Lett.*, 2010, 31, (3), pp. 225–227

Yuan, L., Zou, X., Fang, G., Wan, J., Zhou, H., and Zhao, X.:

- 8 Yuan, L., Zou, X., Fang, G., Wan, J., Zhou, H., and Zhao, X.: 'High-performance amorphous indium gallium zinc oxide thin-film transistors with HfO<sub>x</sub>N<sub>y</sub>/HfO<sub>2</sub>/HfO<sub>x</sub>N<sub>y</sub>, tristack gate dielectrics', *IEEE Electron Device Lett.*, 2011, 32, (1), pp. 42–44

- 9 Tang, Z.K., Wong, G.K.L., Yu, P., Kawasaki, M., Ohtomo, A., Koinuma, H., and Segawa, Y.: 'Room temperature ultraviolet laser emission from self-assembled ZnO microcrystallite thin films', *Appl. Phys. Lett.*, 1998, 3270, (72), pp. 3270–3272

- 10 Su, N.C., Wang, S.J., and Chin, A.: 'High performance InGaZnO thin film transistors using HfLaO gate dielectric', *IEEE Electron Device Lett.*, 2009, 30, (12), pp. 1317–1319