# Nanoscale

## COMMUNICATION

CROYAL SOCIETY OF CHEMISTRY

View Article Online

View Journal | View Issue

Open Access Article. Published on 26 March 2014. Downloaded on 25/12/2014 03:25:24. This article is licensed under a Creative Commons Attribution-NonCommercial 3.0 Unported Licence.

## Multi-level control of conductive nano-filament evolution in HfO<sub>2</sub> ReRAM by pulse-train operations†

Cite this: Nanoscale, 2014, 6, 5698

Received 24th January 2014 Accepted 16th March 2014

DOI: 10.1039/c4nr00500g

www.rsc.org/nanoscale

L. Zhao,<sup>a</sup> H.-Y. Chen,<sup>a</sup> S.-C. Wu,<sup>b</sup> Z. Jiang,<sup>a</sup> S. Yu,<sup>c</sup> T.-H. Hou,<sup>b</sup> H.-S. Philip Wong<sup>a</sup> and Y. Nishi<sup>\*a</sup>

Precise electrical manipulation of nanoscale defects such as vacancy nano-filaments is highly desired for the multi-level control of ReRAM. In this paper we present a systematic investigation on the pulse-train operation scheme for reliable multi-level control of conductive filament evolution. By applying the pulse-train scheme to a 3 bit per cell HfO<sub>2</sub> ReRAM, the relative standard deviations of resistance levels are improved up to 80% compared to the single-pulse scheme. The observed exponential relationship between the saturated resistance and the pulse amplitude provides evidence for the gap-formation model of the filament-rupture process.

Transition-metal-oxide (TMO) based resistance-switching memory (ReRAM) devices have attracted intense research interest as a promising candidate for next generation non-volatile memory devices.<sup>1-3</sup> Among various switching materials, HfO<sub>2</sub> has exhibited reliable memory performances including fast switching speed, superior scalability and low power consumption.<sup>4-6</sup> For HfO<sub>2</sub> and various other binary oxides, the filamentary switching mechanism is widely accepted, which attributes the resistance change to the formation/rupture of nanoscale filaments consisting of oxygen vacancies.<sup>7-16</sup> Much effort has been made to either confirm the existence of these filaments,<sup>10-13</sup> or simulate their evolution by solving physical equations.<sup>14-16</sup> However, the ability to precisely control the size/ resistance of these nanoscale defects remains a critical challenge for ReRAM technology.<sup>1-3,17-19</sup>

Especially, precise control of the nano-filament makes it possible to store more information in each device, which leads to multi-level cells (MLCs) and better synaptic devices for neuromorphic computing applications.<sup>20–27</sup> However, the resistance-state variations caused by the stochastic nature of filament evolution lead to reduced margins between resistance levels and limit the storage capacity. For ReRAM devices with large ON–OFF ratios (>10<sup>3</sup>), this stochasticity is especially severe which leads to the so-called 'over-RESET' problem.<sup>28</sup>

Various program-and-verify schemes have been proposed to control the filament-rupture process and reduce the resistance variations.<sup>23,29,30</sup> However, an accurate resistance measurement over a large dynamic range may significantly increase the operation time and complexity of the control circuitry. In this study, we present a pulse-train operation scheme to achieve reliable and uniform multi-level control of the conductive-filament state, without the need for read-verification operations. By applying pulse-train signals to operate a 3 bit per cell HfO<sub>2</sub>-based ReRAM, the variations between neighbouring resistance states are substantially improved. Moreover, the observed relationship between the saturated resistance and the pulse amplitude supports the gap-formation model for the filament-rupture process.

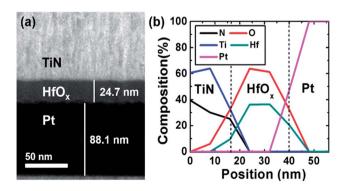

In this study,  $TiN/HfO_2/Pt$  devices are fabricated to investigate the multi-level switching capability of ReRAM. The crosssectional TEM image (Fig. 1(a)) confirms the  $HfO_2$  thickness to

Fig. 1 (a) Cross-sectional TEM image of the fabricated  $TiN/HfO_x/Pt$  ReRAM device. (b) Elemental compositions throughout the device obtained by energy-dispersive X-ray spectroscopy (EDX).

<sup>&</sup>lt;sup>a</sup>Department of Electrical Engineering, Stanford University, 420 Via Palou, Stanford, CA 94305-4070, USA. E-mail: nishiy@stanford.edu

<sup>&</sup>lt;sup>b</sup>Department of Electronics Engineering, National Chiao Tung University, ED-309C, 1001 University Road, Hsinchu 300, Taiwan

<sup>&</sup>lt;sup>c</sup>Department of Computer Engineering, Arizona State University, P.O. Box 878809, Tempe, AZ 85287-8809, USA

<sup>†</sup> Electronic supplementary information (ESI) available. See DOI: 10.1039/c4nr00500g

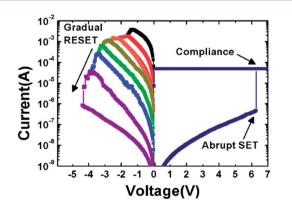

be around 25 nm. According to electron dispersive X-ray (EDX) analysis (Fig. 1(b)), an interfacial  $\text{TiO}_x N_y$  layer is formed to get oxygen and create substoichiometric  $\text{HfO}_x$  which serves as the switching layer.<sup>5</sup> As shown in Fig. 2, the DC sweep characteristics of the device exhibit a very large ON/OFF ratio of 10<sup>6</sup>. By varying the RESET stop voltage from -2.0 V to -4.3 V, a gradual increment of resistivity is observed. 8 discrete resistance levels are achieved with an average separation by a factor of 7.2, implying the potential capability to store 3 bits in each ReRAM cell.

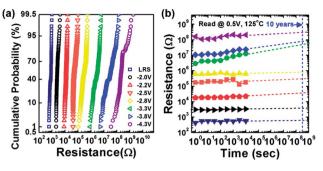

Fig. 3(a) shows the resistance distributions obtained in 100 consecutive DC sweep cycles at different RESET voltages. At smaller voltages, the uniformity of the high resistance state (HRS) is well-controlled, with resistance levels clearly separated from each other. However, when higher RESET voltages are applied to reach deep HRSs, the variations are noticeably increased. Fig. 3(b) shows the retention data collected from 8 resistance states measured at 125 °C, which can be extrapolated to 10 years. These results confirm the 3 bit per cell capability of the fabricated devices.

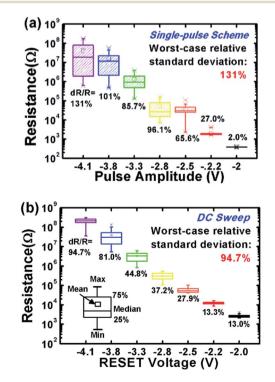

Compared to the DC sweep, pulse programming is a more desirable approach for practical applications due to high operation speed and energy efficiency. Multiple resistance levels can be achieved by varying either the widths or amplitudes of RESET pulses.<sup>22</sup> However, these single-pulse schemes often result in cycle-to-cycle variations that are worse than the DC sweep, which reduces the margins between resistance levels and lowers the storage capacity. In the case of our 3 bit per cell ReRAM, controlling multiple levels by a single-pulse scheme becomes extremely challenging. Fig. 4(a) shows the relative standard deviations of 7 HRSs achieved by applying single pulses with various amplitudes. Compared to the DC sweep (Fig. 4(b)), most of the resistance states exhibit larger variations which cause severe overlapping between the adjacent levels. The only exception is the lowest HRS, which has very small variation due to reset failures. Varying pulse widths are not studied in this work because the required pulse width increases exponentially (which is six orders of magnitude), and the uniformity is unlikely to be improved compared to a varying pulse amplitude.22 The large variations of the single-pulse

Fig. 2 DC sweep characteristics of the fabricated ReRAM device. 8 resistance levels are achieved with a maximum ON/OFF ratio of  $\sim 10^6$ .

Fig. 3 (a) Resistance distributions obtained from 100 consecutive DC sweep cycles at different RESET voltages. (b) Retention characteristics of 8 different resistance levels, measured up to  $10^4$  seconds at 125 °C. Retention can be extrapolated to 10 years.

scheme can be partially attributed to the presence of only one rising edge, which causes the random atomic drift/diffusion to be 'quenched' in the device after the pulse. According to the recent studies on pulse rise-time of ReRAM,<sup>31</sup> the switching voltages can be substantially affected by the rising edge of the pulses. Thus, applying a pulse-train operation scheme should not be viewed as an equivalent single pulse with the longer width of the pulse-train's cumulative time. Overall, the singlepulse operation scheme is not a favorable approach to control the filament evolution of this 3 bit per cell ReRAM due to the uncontrollable variation among the adjacent levels.

On the other hand, pulse-train operation has been suggested to minimize the reset failures of ReRAM.<sup>32,33</sup> It also emerges as a

**Fig. 4** (a) Distributions of HRS resistances in 30 switching cycles obtained by the single-pulse scheme. (b) Distributions of HRS resistances in 100 DC sweep cycles. 7 different HRSs are studied to evaluate the MLC capability.

#### Nanoscale

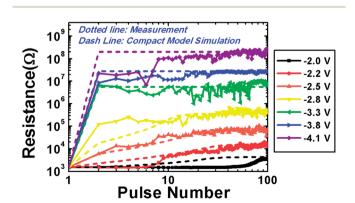

natural method to control analog synaptic devices for neuromorphic applications.<sup>24–27</sup> In this study, the possibility of using a train of identical pulses to achieve multi-level switching with better uniformity is investigated. In this way, we hope to improve the control of the filament evolution by suppressing the stochasticity arising from sharp rising edges. Fig. 5 shows the variation of the resistances during the sequential applications of 100 identical pulses with various amplitudes. Three distinct regimes are observed in these characteristic curves: initially, the resistance changes slowly, then begins to rapidly increase at a certain point, and finally becomes saturated with some fluctuations around a certain value. Following the conventions of MOSFET, the three regimes can be denoted as the subthreshold region, linear region and saturation region. The subthreshold region could be responsible for RESET failures at low voltages,<sup>34</sup> and it is generally eliminated at higher voltages. The linear region is where the majority of atomic migrations occurs, which in this case is controlled in a continuous manner. After entering the saturation region, the range of resistance fluctuation is comparable or even smaller than the cycle-to-cycle variations during the DC sweep. These pulse-trained characteristics, except for the initial random fluctuations, can be well reproduced by ReRAM compact modelling.35 The observations suggest that if the device reaches its saturation regime, the resistances should become more uniform and insusceptible to further identical stimuli.

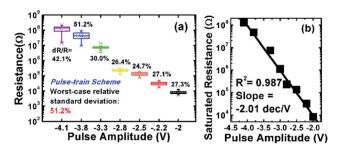

According to this observation, the pulse-train scheme using 100 identical pulses of 200 ns width is applied to program the fabricated  $HfO_2$  device to 7 different HRSs. Each of the resistance state is programmed for 30 switching cycles. As shown in Fig. 6(a), the new scheme significantly improves the variations compared to the single-pulse scheme. The relative standard deviation in the worst case is improved to 51%, which contributes to better separation of the resistance levels. Moreover, the mean saturated resistances are comparable to the corresponding HRS resistances from the DC sweep, and increase exponentially with the pulse amplitude (Fig. 6(b)).

During the RESET process, it is widely accepted that the conductive filament(s) is (are) ruptured to form a tunnelling gap

**Fig. 5** Double log plot of the resistance changes upon the applications of 100 identical pulses with different amplitudes. Both measurement data and compact-model simulation results are demonstrated.

**Fig. 6** (a) Distributions of HRS resistances in 30 switching cycles obtained by the pulse-train scheme. (b) Relationship between the pulse amplitudes and the mean values of the HRS resistance by the pulse-train scheme.

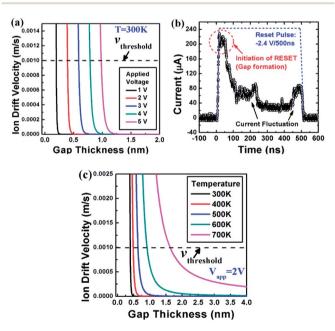

between the filament(s) and the electrode. According to the Wentzel-Kramers-Brillouin (WKB) approximation, the tunneling current across the gap is exponentially dependent on the gap thickness  $(t_{gap})$ .<sup>36</sup> The abovementioned results thus suggest the existence of a maximum gap thickness  $(t_{gap,max})$ , which is linearly dependent on the RESET pulse amplitude. Fig. 7(a) further explains the formation of such a maximized gap by plotting the oxygen drift velocity as a function of the gap thickness. The vacancy migration probability is exponentially dependent on the applied electric field, which is reflected in the drift velocity of the oxygen atom:<sup>14,16</sup>

$$v = fa \exp(-E_{\rm m}/kT)\sinh(qFa/2kT)$$

(1)

where *f* is the frequency of atomic vibration ( $\sim 1 \times 10^{13}$  Hz), *a* is the hopping distance between adjacent potential wells ( $\sim 2.5$  Å),

Fig. 7 (a) Ion drift velocity in  $HfO_2$  ReRAM as a function of gap thickness, at a fixed temperature and various applied voltages. (b) Measured transient current of the  $HfO_2$  ReRAM device during a RESET pulse. (c) Ion drift velocity in  $HfO_2$  ReRAM as a function of the gap thickness, at a fixed applied voltage and various different temperatures.

#### Communication

$E_{\rm m}$  is the migration barrier of the oxygen ion in HfO<sub>2</sub>, which is assumed to be 1.0 eV and *F* is the electric field, which equals the voltage divided by the gap thickness here. In order for a migration event to occur, the velocity should be large enough to move the ion by one atomic distance. As a reference, this threshold velocity is ~0.001 m s<sup>-1</sup> for 200 ns pulses. As shown in Fig. 7(a), the drift velocity exhibits a significant drop across the threshold as the gap thickness increases. Beyond this threshold, the migration probability becomes so small that the movement of oxygen vacancies can barely be observed within the pulse duration. Moreover, the corresponding gap thickness at the threshold is linearly dependent on the applied voltage, consistent with experimental results. To sum up, the saturation region is a manifestation of the maximized gap thickness, which is a consequence of the exponential drift velocity of ions.

Next, the difference between a pulse train and a single pulse with the same equivalent duration is further discussed. Fig. 7(b)shows the transient current of a HfO<sub>2</sub> ReRAM device during the RESET pulse. Beginning at the rising edge, the RESET process is not initiated until the current reaches the highest level. Then, the current drops quickly for about 100 ns before reaching the steady state with fluctuations. Before and after initiation, the progress of RESET is totally different even if the current levels are the same. This suggests that the initiation of RESET is a thermal-assisted event which can be connected with gap formation, and the first RESET pulse can be divided into two regimes. Before initiation, the filament is connected and the voltage drop is rather uniform across the entire film thickness. A significant amount of heat is needed to rupture the filament by ion diffusion at its weakest spot. This argument is supported by numerical simulations of transient thermal responses in the ON state,<sup>37</sup> which confirms the rapid rise of the temperature as a complementary driving force during RESET. After initiation, the tunneling gap is formed and the voltage drop is concentrated to the gap. Now the reset process is field-driven and dominated by an ionic drift, without the need for a high temperature or current level.

The characteristics of pulse-train operation can be well explained within this picture. The subthreshold region corresponds to the condition before initiation of RESET. In the linear region, the gap thickness is gradually expanded until the maximum/saturation is reached. Now according to previous simulations,<sup>37,38</sup> only the pulses before gap formation can create high temperatures in the filament. The rapid temperature rise suggests slow heat dissipation in the filament, which causes elevated temperatures in the first RESET pulse. According to eqn (1), this results in large variations of the ion migration speed (Fig. 7(c)) and hence larger resistance variations. After the first pulse, the stochasticity induced by the elevated temperatures is quenched in the device. On the other hand, the pulsetrain scheme allows correction of this stochasticity with subsequent pulses which result in low temperatures. Since the process is now field-driven, the resistance monotonically increases and is strictly limited by the maximum gap thickness, thereby providing better uniformity.

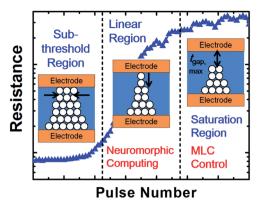

Fig. 8 summarizes the proposed filament evolution during the course of pulse-train programming. The different natures of

**Fig. 8** Schematic of the pulse-train characteristics of ReRAM, divided into three regions. The corresponding physical processes and applications are outlined and discussed in the framework of filamentary resistive switching.

the pulse-trained characteristics happen to satisfy the requirements of different applications: the saturation region is desired for precise MLC control, while the linear region can be utilized in both MLC switching and neuromorphic computing. From Fig. 5, 10 identical pulses are sufficient to bring the device into saturation for most resistance levels, which suggests that the pulse amplitude is an efficient knob for exponential resistance modulation. On the other hand, linear resistance modulation is often desired for multi-level digital memory, which demands a lower dynamic range of the sense amplifiers. In this case, a proper combination of the varying pulse number and amplitude can help to optimize the device performance. Finally, we wish to point out that the idea of pulse-train operation discussed here is not limited to ReRAM, but also applicable to the fine control of other nanostructures such as metal-ion-based atomic switches and magnetic domain wall motion.39,40

### Conclusions

In summary, we systematically investigated the pulse-train operation scheme for reliable and uniform multi-level control of conductive-filament evolution in ReRAM. By applying electrical pulse-train to a 3 bit per cell  $HfO_2$  device, the relative standard deviation of resistance levels is improved up to 80% compared to the single-pulse scheme. Furthermore, the observed exponential relationship between the saturated resistance and the pulse amplitude is consistent with the gap-formation model of the filament rupture process.

### Experimental

The bottom electrode of Pt (~90 nm) is first deposited by e-beam evaporation on Si wafer with a 2 nm Ti adhesion layer. Then, HfO<sub>x</sub> and TiN (~200 nm) were deposited by reactive sputtering at room temperature, followed by a lift-off process to form ReRAM cells of  $100 \times 100 \ \mu\text{m}^2$  area. The device characteristics are measured using a Keithley 4200-SCS semiconductor analyzer with the pulsed *I*-*V* module. The length of the applied pulses is 200 ns, with a rise/fall time of 20 ns.

## Acknowledgements

This work was supported in part by the member companies of the Stanford Non-Volatile Memory Technology Research Initiative (NMTRI). H.-Y. Chen is additionally supported by the Intel Fellowship and the Taiwanese Government Scholarship to Study Aboard (GSSA). S.-C. Wu is additionally supported by the Taiwanese Government Graduate Student Study Abroad Program (GSSAP). Z. Jiang is additionally supported by the M. Stanley Rundel Fellowship Fund at Stanford University. S. Yu is additionally supported by the Stanford Graduate Fellowship.

### Notes and references

- 1 H.-S. P. Wong, H.-Y. Lee, S. Yu, Y.-S. Chen, Y. Wu, P.-S. Chen, B. Lee, F. T. Chen and M.-J. Tsai, *Proc. IEEE*, 2012, **100**, 1951.

- 2 R. Waser, R. Dittmann, G. Staikov and K. Szot, *Adv. Mater.*, 2009, **21**, 2632.

- 3 H. Akinaga and H. Shima, Proc. IEEE, 2010, 98, 2237.

- 4 Y. M. Kim and J. S. Lee, J. Appl. Phys., 2008, 104, 114115.

- 5 H. Y. Lee, P. S. Chen, T. Y. Wu, Y. S. Chen, C. C. Wang, P. J. Tzeng, C. H. Lin, F. Chen, C. H. Lien and M.-J. Tsai, *IEEE Int. Electron Devices Meet., Tech. Dig., 54th*, 2008, 297.

- 6 B. Govoreanu, G. S. Kar, Y. Chen, V. Paraschiv, S. Kubicek,

A. Fantini, I. P. Radu, L. Goux, S. Clima, R. Degraeve,

N. Jossart, O. Richard, T. Vandeweyer, K. Seo,

P. Hendrickx, G. Pourtois, H. Bender, L. Altimime,

D. J. Wouters, J. A. Kittl and M. Jurczak, *IEEE Int. Electron Devices Meet., Tech. Dig., 57th*, 2011, 31.6.

- 7 J. F. Gibbons and W. E. Beadle, Solid-State Electron., 1964, 7, 785.

- 8 U. Russo, D. Ielmini, C. Cagli and A. L. Lacaita, *IEEE Trans. Electron Devices*, 2009, **56**, 186.

- 9 K. M. Kim, D. S. Jeong and C. S. Hwang, *Nanotechnology*, 2011, 22, 254002.

- 10 J. Y. Son and Y.-H. Shin, Appl. Phys. Lett., 2008, 92, 222106.

- 11 D.-H. Kwon, K. M. Kim, J. H. Jang, J. M. Jeon, M. H. Lee, G. H. Kim, X.-S. Li, G.-S. Park, B. Lee, S. Han, M. Kim and C. S. Hwang, *Nat. Nanotechnol.*, 2010, 5, 148.

- G. Bersuker, D. C. Gilmer, D. Veksler, P. Kirsch, L. Vandelli, A. Padovani, L. Larcher, K. McKenna, A. Shluger, V. Iglesias, M. Porti and M. Nafría, *J. Appl. Phys.*, 2011, **110**, 124518.

- P. Calka, E. Martinez, V. Delaye, D. Lafond, G. Audoit, D. Mariolle, N. Chevalier, H. Grampeix, C. Cagli, V. Jousseaume and C. Guedj, *Nanotechnology*, 2013, 24, 085706.

- 14 X. Guan, S. Yu and H.-S. P. Wong, *IEEE Trans. Electron Devices*, 2012, **59**, 1172.

- 15 L. Vandelli, A. Padovani, L. Larcher, G. Broglia, G. Ori, M. Montorsi, G. Bersuker and P. Pavan, *IEEE Int. Electron Devices Meet.*, *Tech. Dig.*, 57th, 2011, 17.5.

- 16 D. Ielmini, IEEE Trans. Electron Devices, 2011, 58, 4309.

- 17 X. Guan, S. Yu and H.-S. P. Wong, *IEEE Trans. Electron Devices*, 2012, **59**, 1183.

- 18 B. Chen, B. Gao, S. W. Sheng, L. F. Liu, X. Y. Liu, Y. S. Chen, Y. Wang, R. Q. Han, B. Yu and J. F. Kang, *IEEE Electron Device Lett.*, 2011, 32, 282.

- 19 M.-J. Lee, S. Han, S. H. Jeon, B. H. Park, B. S. Kang, S.-E. Ahn, K. H. Kim, C. B. Lee, C. J. Kim, I.-K. Yoo, D. H. Seo, X.-S. Li, J.-B. Park, J.-H. Lee and Y. Park, *Nano Lett.*, 2009, 9, 1476.

- 20 W. C. Chien, Y. C. Chen, K. P. Chang, E. K. Lai, Y. D. Yao, P. Lin, J. Gong, S. C. Cai, S. H. Hsieh, C. F. Chen, K. Y. Hsieh, R. Liu, and C.-Y. Lu, *IEEE International Memory Workshop (IMW)*, 2009.

- 21 M. Terai, Y. Sakotsubo, S. Kotsuji and H. Hada, *IEEE Electron Device Lett.*, 2010, **31**, 204.

- 22 S. Yu, Y. Wu and H.-S. P. Wong, Appl. Phys. Lett., 2011, 98, 103514.

- 23 S. R. Lee, Y.-B. Kim, M. Chang, K. M. Kim, C. B. Lee, J. H. Hur, G.-S. Park, D. Lee, M.-J. Lee, C. J. Kim, U.-I. Chung, I.-K. Yoo and K. Kim, *IEEE Symp. VLSI Tech. Dig.*, 2012, p. 71.

- 24 S. Yu, B. Gao, Z. Fang, H. Y. Yu, J. F. Kang and H.-S. P. Wong, *Adv. Mater.*, 2013, **25**, 1774.

- 25 D. Kuzum, S. Yu and H.-S. P. Wong, *Nanotechnology*, 2013, 24, 382001.

- 26 S. H. Jo, T. Chang, I. Ebong, B. Bhavitavya, P. Mazumder and W. Lu, *Nano Lett.*, 2010, **10**, 1297.

- 27 S. Park, J. Noh, M.-I. Choo, A. M. Sheri, M. Chang, Y.-B. Kim, C. J. Kim, M. Jeon, B.-G. Lee, B. H. Lee and H. Hwang, *Nanotechnology*, 2013, 24, 384009.

- 28 H. Y. Lee, Y. S. Chen, P. S. Chen, P. Y. Gu, Y. Y. Hsu, S. M. Wang, W. H. Liu, C. H. Tsai, S. S. Sheu, P. C. Chiang, W. P. Lin, C. H. Lin, W. S. Chen, F. T. Chen, C. H. Lien and M.-J. Tsai, *IEEE Int. Electron Devices Meet., Tech. Dig.*, 57th, 2011, 19.7.

- 29 F. Alibart, L. Gao, B. D. Hoskins and D. B. Strukov, Nanotechnology, 2012, 23, 075201.

- 30 C. Xu, D. Niu, N. Muralimanohar, N. P. Jouppi and Y. Xie, Proceedings of the 50th Annual Design Automation Conference. ACM, 2013.

- 31 R. Liu, H.-Y. Chen, H. Li, P. Huang, L. Zhao, Z. Chen, F. Zhang, B. Chen, L. Liu, X. Liu, B. Gao, S. Yu, Y. Nishi, H.-S. P. Wong and J. Kang, *International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA)*, 2014.

- 32 K. Higuchi, T. O. Iwasaki and K. Takeuchil, *IEEE* International Memory Workshop (IMW), 2012.

- 33 K. Yoo, B. S. Kang, Y. D. Park, M. J. Lee and Y. Park, *Appl. Phys. Lett.*, 2008, **92**, 202112.

- 34 Y. Y. Chen, R. Degraeve, S. Clima, B. Govoreanu, L. Goux,

A. Fantini, G. S. Kar, G. Pourtois, G. Groeseneken,

D. J. Wouters and M. Jurczak, *IEEE Int. Electron Devices Meet., Tech. Dig., 58th*, 2012, 20.3.

- 35 X. Guan, S. Yu and H.-S. P. Wong, *IEEE Electron Device Lett.*, 2012, **33**, 1405.

- 36 S. Yu, X. Guan and H.-S. P. Wong, *Appl. Phys. Lett.*, 2011, **99**, 063507.

- 37 B. Govoreanu, S. Clima, I. P. Radu, Y.-Y. Chen, D. J. Wouters and M. Jurczak, *IEEE Trans. Electron Devices*, 2013, **60**, 2471.

- 38 U. Russo, D. Ielmini, C. Cagli and A. L. Lacaita, *IEEE Trans. Electron Devices*, 2009, **56**, 193.

- 39 K. Terabe, T. Hasegawa, T. Nakayama and M. Aono, *Nature*, 2005, **433**, 47.

- 40 L. Thomas, M. Hayashi, X. Jiang, R. Moriya, C. Rettner and S. Parkin, *Science*, 2007, **315**, 1553.

Nanoscale