# Ambipolar MoTe<sub>2</sub> Transistors and Their Applications in Logic Circuits

Yen-Fu Lin,\* Yong Xu, Sheng-Tsung Wang, Song-Lin Li, Mahito Yamamoto, Alex Aparecido-Ferreira, Wenwu Li, Huabin Sun, Shu Nakaharai, Wen-Bin Jian, Keiji Ueno, and Kazuhito Tsukagoshi\*

The advent of graphene, a two-dimensional (2D) material, extracted from graphite using scotch tape-based mechanical cleavage, has triggered much attention because of its peculiar electrical, optical, and mechanical properties in nature, opening up a new area for both fundamental science and technological communities.[1] However, the absence of an intrinsic bandgap in graphene has hindered its development for use in logic circuits in the modern semiconductor industry, stimulating scientific and engineering progress on its derivatives and other 2D layered nanomaterials. [2–7] Transition-metal dichalcogenides (TMDs) with the common formula MX2, where M stands for a transition metal from group IV-VII (M = Mo, W, Nb, Re, and so on) and X is a chalcogen element (S, Se, Te), form a well-known class of layered composite materials. In these layered materials, a hexagonally packed layer of M atoms is sandwiched between two layers of X atoms, and the triple layers stack together via weak van der Waals forces, which facilitate cleavage of the bulk crystals to form individual 2D flakes along each triplet of layered structures. The lack of covalent bonds between adjacent triple layers renders these 2D TMD flakes free of dangling bonds, thus creating chemical stability and low carrier scattering on their surfaces. These layered TMD structures lead to high anisotropy in their electrical properties.<sup>[8]</sup> The earliest

where bulk WSe2 crystals exhibited ambipolar behavior with mobilities as high as 500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and a current modulation of up to 10<sup>4</sup>.<sup>[9]</sup> The electrical properties of several TMDs with ultra-thin layers have been studied including those of MoS<sub>2</sub>, MoSe<sub>2</sub>, WS<sub>2</sub>, and WSe<sub>2</sub> flakes, revealing superior transistor performance in comparison to those made of graphene. [10-14] As a result, 2D TMDs are regarded as promising materials for the development of non-graphene optoelectronics. 2H-type molybdenum ditelluride (MoTe<sub>2</sub>) is a TMD layered

use of TMDs in field-effect transistors was reported in 2004,

compound. In its bulk form, MoTe2 is a semiconductor with an indirect bandgap of 1.0 eV[3] and has been exploited as an electrode material in photovoltaic cells because of its strong absorption properties throughout the solar spectrum.<sup>[15]</sup> Other distinctive properties have also been addressed in bulk MoTe<sub>2</sub>. Its mobility at room temperature (RT), for example, can theoretically reach up to 200 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.[16] Both p- and n-type materials were synthesized through controlling the growth conditions in MoTe2 crystals, leading to their use in light-emitting transistors (p-n junctions).[17] In addition, a phase transition was observed between the semiconducting  $\alpha$ -MoTe<sub>2</sub> and the metallic  $\beta$ -MoTe<sub>2</sub> because of distortion of the octahedral coordinates.<sup>[18]</sup> Moreover, calculations have shown that MoTe<sub>2</sub> exhibits a direct bandgap of 1.07 eV because of the induced quantum confinement when the layer is thinned to a monolayer.[19] Recently, semiconducting MoTe<sub>2</sub> nanorods were fabricated by annealing MoTe<sub>2</sub> particles in solution.<sup>[20]</sup> The mechanical properties of the single-walled MoTe<sub>2</sub> nanotubes were found to strongly depend on the diameter and chirality of the tubes.<sup>[21]</sup> Although the electrical properties of bulk MoTe<sub>2</sub> have been studied, [8,16,22-25] layered MoTe<sub>2</sub> flake structures have not been investigated thus far and are still puzzling.

In order for digital and analog applications to be realized, silicon-based complementary metal-oxide-semiconductor (CMOS) electronics, where unipolar n- and p-type transistors are predetermined through deliberate stoichiometric variations during the fabrication process and are integrated together to build logic circuits, have been part of the most efficient strategy until now. However, as the number of transistors per circuit increases, the transistor channels have to be spatially separated to prevent leakage currents. Thus, the fabrication of circuits becomes more complex and the cost of mass production is more expensive as a result. In contrast, the use of ambipolar-based transistors, characterized by a superposition of electrons and holes, might be used as an alternative scenario in simplifying circuit

Dr. Y. F. Lin, Dr. Y. Xu, Dr. S. L. Li, Dr. M. Yamamoto, Dr. A. A. Ferreira, Dr. W. Li, H. Sun, Dr. S. Nakaharai, Dr. K. Tsukagoshi WPI Center for Materials Nanoarchitechtonics

(WPI-MANA)

National Institute for Materials Science (NIMS) Tsukuba, Ibaraki 305-0044, Japan

E-mail: yenfulin@nchu.edu.tw; Tsukagoshi.kazuhito@nims.go.jp

Dr. Y. F. Lin

Department of Physics National Chung-Hsing University Taichung 40227, Taiwan S. T. Wang, Prof. W. B. Jian Department of Electrophysics National Chiao Tung University Hsinchu 30010, Taiwan Prof. K. Ueno

Department of Chemistry Graduate School of Science and Engineering Saitama University

Saitama 338-8570, Japan

DOI: 10.1002/adma.201305845

- Matrices

www.MaterialsViews.com

design. Transistors that display charge-carrier ambipolarity can easily be switched because of the simultaneous or selective transport of electrons and holes in the conducting channel by applying an electric field.<sup>[26]</sup> Very recently, with the use of an electrolyte gate, ambipolar charge transport has been shown in 2D TMD flakes, providing an opportunity for future applicability in both the digital and analog domains.<sup>[12,27–29]</sup>

In this communication, we determine, for the first time, the electrical characteristics in layered flakes (2-4 layers) of α-MoTe<sub>2</sub> that were mechanically exfoliated onto Si/SiO<sub>2</sub> substrates. The MoTe<sub>2</sub> transistors unambiguously displayed ambipolar charge-transport behavior. The performance of the ambipolar-transistor operation under a drain-source voltage  $(V_{\rm ds})$  of 10 V at RT was characterized with a current on/off ratio of  $5 \times 10^2$  and  $2 \times 10^3$  for the electron and hole accumulation regimes, respectively. Through extensive analysis of the temperature dependence of the current-voltage ( $I_{ds}$ - $V_{ds}$ ) curves in the layered MoTe2 transistors, the ambipolar charge transport can be exactly described on the basis of charge transport across a Schottky barrier at the metal-MoTe<sub>2</sub> contact. The existence of a Schottky barrier at the contact can be modulated by the addition of an electrostatic field from the back-gate voltage  $(V_{bg})$  and the drain-source voltage (V<sub>ds</sub>), allowing the MoTe<sub>2</sub> flakes to exhibit ambipolar charge transport with a low contact resistance for both n- and p-type conduction. Comprehensive mapping of the effective Schottky barrier heights as a function of  $V_{bg}$  and  $V_{ds}$ is further unveiled and offers insight into understanding the

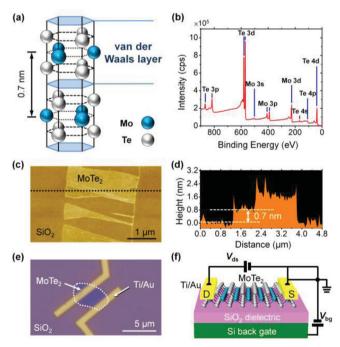

**Figure 1.** a) The crystal structure of 2H-type  $\alpha$ -MoTe<sub>2</sub>. Each layer has a thickness of 0.7 nm. b) XPS spectrum of as-synthesized MoTe<sub>2</sub> crystals. c) AFM image of a MoTe<sub>2</sub> flake deposited on top of a silicon substrate with a 285-nm thick SiO<sub>2</sub> layer. d) The cross-sectional profile along the dotted line of the AFM image shown in (c). e) Optical image of a pair of Ti/Au electrodes deposited on a layered MoTe<sub>2</sub> flake. f) Scheme of a MoTe<sub>2</sub> transistor used for this study, with the circuit diagram overlaid. The heavily doped Si substrate was used as the back gate. The electrode on one side served as the drain (D), whereas the other was the source (S).

carrier-injection mechanism, as well as the controlling current on/off ratio in MoTe<sub>2</sub> flakes. More excitingly, these ambipolar layered MoTe<sub>2</sub> transistors enabled us to achieve complementary inverters and output polarity controllable (OPC) amplifiers based on a single active material.

The crystal structure of the 2H-type  $\alpha$ -MoTe<sub>2</sub> layer compound is shown in Figure 1a, where the stacking layers follow the sequence of Te-Mo-Te, Te-Mo-Te. Each layer has a thickness of 0.7 nm, in which the Mo atom is covalently bound to six neighboring Te atoms in a trigonal prismatic coordination.<sup>[30]</sup> The XPS spectrum for the as-synthesized bulk crystals used in the study is displayed in Figure 1b. Only Mo and Te core electron peaks are observed, indicating that the growth of MoTe<sub>2</sub> crystals was successful. Figure 1c shows an AFM image of a MoTe<sub>2</sub> flake transferred onto a Si/SiO<sub>2</sub> substrate. From the line profile of the AFM image the thickness of the flake could be estimated to be about 0.7 nm, which is in conformity with the height of a monolayer of MoTe2 (see Figure 1d). This result is the first experimental evidence proving that a monolayer of MoTe<sub>2</sub> can be stable at RT in air. The flakes that we obtained were triangular, with most of them showing irregularities (Figure S3, Supporting Information). In this study, we used MoTe<sub>2</sub> flakes with thicknesses ranging from 2 to 4 layers rather than monolayer MoTe2 flakes, because we were unable to cleave the MoTe2 crystals down to atomic flakes with a large enough lateral size for device fabrication. It should be noted that within the investigated thickness range of the MoTe2 flakes, the transistor characteristics were not found to be remarkably thickness dependent. An optical image of a typical MoTe2 transistor (bilayer) is displayed in Figure 1e. For all of the layered MoTe<sub>2</sub> transistors, the channel length-to-width ratio was purposely kept constant at around 1 to reduce device-device variations. Figure 1f illustrates a sketch of the MoTe2 transistor configuration along with the circuit measurements used.

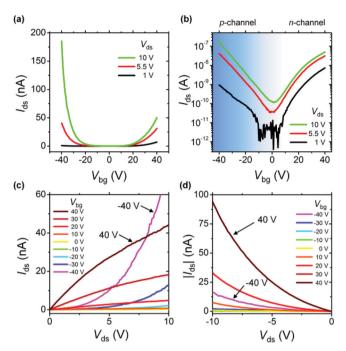

The room-temperature (RT) transfer characteristics of a trilayered MoTe2 transistor under different Vds values are shown on the linear scale in Figure 2a and on the logarithmic scale in Figure 2b. An abrupt increase in Ids is clearly observed with increasing  $V_{\rm bg}$  for both positive (n-channel) and negative (p-channel) polarities, which demonstrates the ambipolar operation in the MoTe<sub>2</sub> flake transistors. Moreover, no significant hysteresis is observed in the transfer characteristics of the MoTe<sub>2</sub> flake transistors when the back-gate voltage is scanned at the fixed speed of 4 V s<sup>-1</sup> used in our study (Figure S4, Supporting Information), implying that defect and trap contributions can be ignored. Under modulation of  $V_{\rm bg}$  the current on/off ratio at  $V_{\rm ds} = 10$  V reaches  $5 \times 10^2$  and  $2 \times 10^3$  for the n- and p-type regimes, respectively, fulfilling the requirements for use as a switch.[31] For simplicity, the contribution of the contact resistance was ignored when estimating the mobilities. According to the conventional equation  $\mu = (L/W)(d/\varepsilon_0\varepsilon_r V_{ds})(\Delta I_{ds}/\Delta V_{bg})$ , where  $\mu$  is the field-effect mobility, L/W is the channel length-to-width ratio and is 1 for this study,  $\varepsilon_0$  is the permittivity in vacuum,  $\varepsilon_{\rm r}$  is 3.9 for SiO<sub>2</sub>, and d is the thickness of the dielectric layer (285 nm),  $^{[32]}$  we obtained mobilities of 0.03 and 0.30 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, extracted at  $V_{\rm ds}$  = 10 V in the high  $V_{\rm bg}$  region, for electrons and holes, respectively. Both mobilities were much lower than the theoretical prediction in the literature, [16] implying the existence of a large contact resistance in the layered MoTe<sub>2</sub> transistors.

ADVANCED MATERIALS

www.dovmar.c

**Figure 2.** RT transfer characteristics of a tri-layered MoTe<sub>2</sub> transistor under different  $V_{ds}$  values on a linear scale (a) and on a logarithmic scale (b). RT output characteristics of the MoTe<sub>2</sub> transistor under different  $V_{bg}$  values in the positive  $V_{ds}$  regime (c) and in the negative  $V_{ds}$  regime (d).

Figure 2c and d reveal the RT output characteristics of the  $MoTe_2$  transistor at different  $V_{bg}$  values in the positive and negative  $V_{\rm ds}$  regimes, respectively. When sweeping  $V_{\rm ds}$  from 0 to 10 V, a saturation of the current is detected at  $V_{\rm bg}$  = 40 V, as shown in Figure 2c. This is caused by the occurrence of pinch-off in the channel. With a decreasing  $V_{\rm bg}$  from 40 to 0 V at a given  $V_{ds}$ , the magnitude of  $I_{ds}$  decreases. This demonstrates that electrons are the majority of the charge carriers in the positive  $V_{\mathrm{bg}}$  regime. However, when varying  $V_{\mathrm{bg}}$  from 0 to -40 V, the  $I_{\rm ds}$  shows typical behavior, namely it increases at a given  $V_{ds}$ . Such a unique increase, which is not present in unipolar transistors, can be attributed to the accumulation of holes in the conducting channel and is a typical ambipolar feature. When  $V_{\rm ds}$  is scanned from 0 to -10 V, we observe a nonlinear increase in  $|I_{ds}|$  (Figure 2d), suggesting that there is a significant contact resistance suppressing the carrier injection as well as the transistor appearance in the channel. With a decrease in the negative  $V_{\rm bg}$  the  $|I_{\rm ds}|$  value gradually decreases, which means that holes are dominant in the negative  $V_{\mathrm{bg}}$  regime. The electron current (ca. 95 nA at  $V_{\rm bg} = 40$  V and  $V_{\rm ds} = -10$  V) was twice as large as the hole current (ca. 45 nA at  $V_{\rm bg}$  = -40 V and  $V_{\rm ds} = -10$  V), confirming that the type of carrier that formed the majority in the inversion layer was not as obvious as seen in Figure 2c. Unlike graphene transistors, evidence of both a high current on/off ratio and current saturation over a wide V<sub>ds</sub> window points to the presence of a bandgap in the MoTe<sub>2</sub> flakes, showing that these flakes can contribute to broadening the scope of logic design.

To verify our conjecture on the existence of contact barriers and to elucidate the charge-transport mechanism for the ambipolar operation in  $MoTe_2$  transistors, temperature-dependent

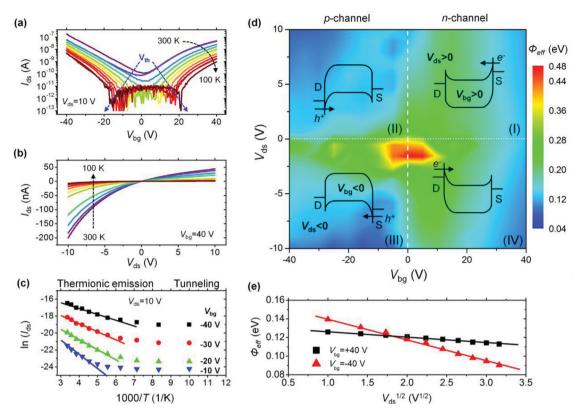

measurements were carried out. Figure 3a and b unveil the temperature dependence of the transfer and output characteristics, respectively, for the MoTe<sub>2</sub> transistor shown in Figure 2. In Figure 3a, it can be seen that the minimum voltage required to achieve the on-current state (threshold voltage,  $V_{th}$ ) shifts toward the more positive or negative  $V_{\rm bg}$  region, when the temperature decreases from 300 down to 100 K. The blue dashed lines in Figure 3a are a guide to the eye for the shift in  $V_{th}$ . This behavior is can be explained by the decreasing number of charge carriers in the conducting channel. The current on/off ratio was derived as  $5 \times 10^2$  (2 × 10<sup>3</sup>) at 300 K, approaching a saturation value of  $10^4$  ( $10^5$ ) at 220 K at  $V_{\rm ds} = 10$  V for the n- (p-) channel region (Figure S5, Supporting Information). In Figure 3b, the  $I_{ds}$  increases for a fixed temperature with increasing  $V_{ds}$ , revealing a downward (upward) bending characteristic in the positive (negative)  $V_{ds}$  region. Such asymmetric  $I_{ds}$ – $V_{ds}$  behavior is strongly associated with the contact resistance, which arises from contact barriers with different potential heights, taking place at the source/MoTe<sub>2</sub> and drain/MoTe<sub>2</sub> interfaces. With decreasing temperature, the value of  $I_{ds}$  gradually drops for a given  $V_{\rm ds}$ .

If we consider the semiconducting nature of MoTe<sub>2</sub>, the circuit configuration of the MoTe2 transistors can be treated as a metal-semiconductor-metal (M-S-M) structure, where the Schottky barriers are constructed at both metal/semiconductor contacts. To verify the relationship between the experimental data and the model of thermionic emission for the Schottky contacts,[33] an Arrhenius plot of the MoTe2 transistor as a function of V<sub>bg</sub> (p-channel) is shown in Figure 3c. From this figure, the contribution of both the thermionic emission and tunneling components can be clearly differentiated. Similar results are obtained for an n-channel as well. This manifests that Schottky barriers are formed at both the source/MoTe2 and drain/MoTe<sub>2</sub> interfaces, giving rise to the contact resistance. Through analysis of the slopes of the linear fits in the  $ln(I_{ds})$ -1/T plot at high temperatures, the effective Schottky barrier,  $\phi_{eff}$ , could be obtained (see Section V of the Supporting Information for more details). The extracted  $\phi_{e\!f\!f}$  at  $V_{ds}=10~V$  shows a strong dependence on  $V_{\rm bg}$ , as it shrinks from 0.13 to 0.08 eV as  $V_{\rm bg}$  is increased from -10 to -40 V.

To gain further insight into the underlying mechanism of the ambipolar behavior in the layered MoTe2 transistors, the magnitudes of the effective Schottky barrier heights were mapped as a function of  $V_{\rm ds}$  and  $V_{\rm bg}$  and are presented in Figure 3d. The dotted and dashed white lines refer to the positions of  $V_{ds} = 0 \text{ V}$ and  $V_{\rm bg} = 0$  V, respectively, which equally divide Figure 3d into four quadrants so as to highlight the energy-band bending in the MoTe<sub>2</sub> transistors under different electrostatic fields. Taking into account the M-S-M structure, the band model of two backto-back Schottky barriers was adopted, [34] as shown in Figure 3d. As  $V_{\rm bg}$  is swept between -40 to 40 V, the transistor undergoes a transition from the p- to the n-type regime. With a positive  $V_{\rm bg}$ , the conduction and valence bands are bent downward, making it easier to inject electrons from the source (drain) to the drain (source) at a given positive (negative) V<sub>ds</sub>, thus establishing n-type conduction. Parts (I) and (IV) in Figure 3d show a concept of the energy-band diagram. With a negative V<sub>bg</sub>, the conduction and valence bands are bent upward driving holes from the drain (source) to the source (drain) at a given

www.MaterialsViews.com

**Figure 3.** a) Transfer characteristics of the MoTe<sub>2</sub> transistor at  $V_{ds} = 10$  V as a function of temperature. b) Output characteristics of the MoTe<sub>2</sub> transistor at  $V_{bg} = 40$  V as a function of temperature. c) Arrhenius plot at  $V_{ds} = 10$  V with  $V_{bg}$  varying from -40 to -10 V (p-channel). d) Maps of effective Schottky barrier heights,  $\phi_{eff}$ , as a function of  $V_{ds}$  and  $V_{bg}$  for the MoTe<sub>2</sub> transistors. The dotted and dashed white lines denote the positions of  $V_{ds} = 0$  V and  $V_{bg} = 0$  V, respectively. Energy-band bending diagrams for the MoTe<sub>2</sub> transistor operated under  $V_{ds} > 0$  and  $V_{bg} > 0$  (I),  $V_{ds} > 0$  and  $V_{bg} < 0$  (III), and  $V_{ds} < 0$  and  $V_{bg} > 0$  (IV) are drawn to illustrate the electron and hole injections and the ambipolar charge-transport behavior. d)  $\phi_{eff}$  as a function of the square root of  $V_{ds}$  at  $V_{bg} = 40$  V (n-channel) and -40 V (p-channel).

positive (negative)  $V_{ds}$ . This idea is shown in parts (II) and (III) in the p-channel regime. Close inspection of the effective barrier heights shows that a small  $\phi_{\it eff}$  can be gained at a high  $V_{

m ds}$  or  $V_{\rm bg}$ . In other words, when both  $V_{\rm ds}$  and  $V_{\rm bg}$  gradually approach 0 V, a maximum  $\phi_{eff}$  of 0.48 eV occurs, as depicted in Figure 3d. As the variations in  $I_{ds}$  are roughly symmetric with respect to  $V_{\rm bg}$  (see Figure 2b), the maximum effective barrier height is expected to be half that of the MoTe<sub>2</sub> bandgap  $(\phi_{\text{max}} \sim E_g / 2)$ . [35] Hence an experimental value for  $E_g$  of 0.96 eV can be obtained, which is in excellent agreement with the previously published value of 1.0 eV.[3] In addition, the fact that the deduced mobility for electrons is lower than that for holes can also be explained by the existence of a higher  $\phi_{eff}$  in the n-type regime. Interestingly, the  $\phi_{eff}$  obeys a linear dependence on the square root of  $V_{\rm ds}$  (see Figure 3e), which signifies a large electrostatic field from the  $V_{ds}$  at the contacts, leading to an image force lowering of the Schottky barrier.[33]

From these above-mentioned results, we can summarize that the thermionic emission of the Schottky contacts dominates the charge transport in the layered MoTe<sub>2</sub> transistors and the ambipolar characteristics are responsible for the tunability of the Schottky barrier heights and the contact resistance, rather than the channel conductance. We speculate that the formation of two back-to-back Schottky barriers possibly stems from the energy difference between the metal work function and the

MoTe<sub>2</sub> electron affinity energy.<sup>[36]</sup> For transistors with Ti contacts (Ti work function is ca. 4.33 eV), relatively equal barrier heights for electrons and holes are established, allowing ambipolar charge transport. The conjecture suggests that using a metal with a lower (or higher) work function for the contacts may *engineer* MoTe<sub>2</sub> transistors to behave in a unipolar n- (p-) type manner. This type of unipolar transistor has been preliminarily realized and is shown in Figure S6 in the Supporting Information. Further discussion about charge injection via different contact metals is still needed in the near future. An unusual two-Schottky-barrier-type transistor has been demonstrated in the layered MoTe<sub>2</sub> flakes. Complete mapping of the effective barrier heights will pave a way to develop new electronic functions in 2D TMD electronics.

Despite the fact that transistors with two back-to-back Schottky barriers arising from the contacts are considered to be undesirable because they cause additional energy to dissipate, leading to poor device performance and low mobilities, in the following discussion we demonstrate that the ambipolarity caused by these Schottky barriers in the MoTe<sub>2</sub> transistors should not be seen as a drawback but can be beneficial in realizing logic applications.

As proof of concept, we fabricated a complementary inverter, which is the basic building block in logic architectures, by assembling two layered MoTe<sub>2</sub> transistors (bilayer) with a

ADVANCED MATERIALS

www.advmat.de

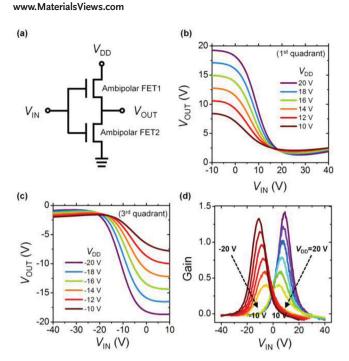

**Figure 4.** a) Scheme of a complementary inverter circuit comprising two ambipolar transistors, one of which operated as an n-type channel transistor whereas the other was conducted as a p-type channel transistor. b) Inverter characteristics where  $V_{\rm IN}$  and  $V_{\rm DD}$  were both positively biased (1st quadrant). c) Inverter characteristics where  $V_{\rm IN}$  and  $V_{\rm DD}$  were both negatively biased (3rd quadrant). d) The corresponding voltage gain of the complementary inverter ( $-\Delta V_{\rm OUT}/\Delta V_{\rm IN}$ ).

common gate as the input voltage,  $V_{\rm IN}$ . The circuit diagram for the inverter is depicted in Figure 4a, where the supply voltage and output voltage are labeled as  $V_{\rm DD}$  and  $V_{\rm OUT}$ , respectively. When a positive  $V_{DD}$  and  $V_{IN}$  are applied, the inverter works in the positive V<sub>OUT</sub> regime (1st quadrant), as shown in Figure 4b. Under these circumstances, the ambipolar transistor, FET1 in Figure 4a, operates as a p-type channel, whereas the FET2 conducts as an n-type channel. As  $V_{\rm DD}$  and  $V_{\rm IN}$  are applied negatively without any alternation of the circuit formation, the inverter works in the negative  $V_{OUT}$  regime (3<sup>rd</sup> quadrant), as shown in Figure 4c. Here, the ambipolar transistors, FET1 and FET2, are functioned to the n- and p-type regimes, respectively. Depending on the polarities of  $V_{\rm DD}$  and  $V_{\rm IN}$ , the inverter can work in either the 1st or 3rd quadrant, which is a unique characteristic of ambipolar-based inverters. The corresponding voltage gains, defined as  $-\Delta V_{OUT}/\Delta V_{IN}$ , at various  $V_{DD}$  are displayed in Figure 4d as a function of  $V_{IN}$ . With decreasing  $|V_{DD}|$  the voltage gain is reduced. It is worth noting that the peak position of the gain (inverting voltage) is close to  $V_{\rm DD}/2$ , which reflects that there is no significant difference between the electron and hole contributions in the two ambipolar transistors used in the inverter demonstration.

Transistors displaying ambipolar behavior have flexibilities for use in communication applications over conventional routines. Ambipolar transistors could much simplify circuit designs and improve signal processing performance. Here we use another layered MoTe<sub>2</sub> transistor (bilayer) with balanced electron and hole characteristics to demonstrate the two basic

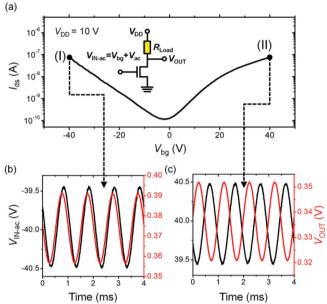

**Figure 5.** a) RT transfer characteristics of a layered  $MoTe_2$  transistor. The inset depicts the scheme of an OPC amplifier circuit equipped with an off-chip resistor  $R_{Load}$ . The two dots represent the difference in the operation modes. From the left side to the right side, the OPC amplifier is manipulated in the common-drain mode (I) and the common-source mode (II). b) In the common-drain mode, the output signal shows the same phase as the input signal. c) In the common-source mode, the output signal displays a  $180^{\circ}$  phase shift when compared to the input signal.

functions of analog circuits. The RT transfer curve for this MoTe<sub>2</sub> transistor is displayed in Figure 5a. The inset shows the scheme of an OPC amplifier circuit equipped with an off-chip resistor  $R_{\text{Load}}$ . The  $V_{\text{DD}}$  and  $R_{\text{Load}}$  were set to 10 V and 25 M $\Omega$ , respectively. A small sinusoidal signal  $V_{ac}$  was superimposed at a given constant  $V_{\rm bg}$  and then applied to the back gate as a dynamic input signal ( $V_{\text{IN-ac}} = V_{\text{bg}} + V_{\text{ac}}$ ). When a negative  $V_{\text{bg}}$ is applied to the OPC amplifier, in the positive phase of  $V_{ac}$ ,  $I_{

m ds}$  increases/decreases as  $V_{

m IN-ac}$  decreases/increases; and, as a consequence, the corresponding  $V_{\rm OUT}$  also increases/decreases in an oscillatory manner. This situation is called the commondrain mode and is illustrated in Figure 5b. In this mode,  $V_{OUT}$ shows the same phase as  $V_{IN-ac}$ . Similarly, when  $V_{bg}$  is applied in the n-type regime, the corresponding  $V_{\mathrm{OUT}}$  oscillates synchronously with a phase difference of 180° with respect to  $V_{\text{IN-ac}}$ , as shown in Figure 5c (the common-source mode). This demonstration of two fundamental modes in a single-layered MoTe<sub>2</sub> transistor has encouraged us to develop other complicated analog circuits such as phase-shift keying, frequency-shift keying, and RF mixers.

In conclusion, a layered compound structure of a semiconducting α-MoTe<sub>2</sub> crystal has been thinned down to atomic flakes and placed on Si/SiO<sub>2</sub> substrates by means of mechanical exfoliation before fabricating them into ambipolar transistors. Through deliberate analysis of the temperature dependence of the electrical properties, the ambipolarity of the charge transport in the layered MoTe<sub>2</sub> flakes was seen to occur because of the formation of two back-to-back Schottky barriers rather than through the channel conductance. An *in-depth* understanding www.advmat.de

www.MaterialsViews.com

Makrials Views

of the underlying mechanism of the carrier injection was uncovered by mapping the effective Schottky barrier heights as a function of  $V_{\rm bg}$  and  $V_{\rm ds}$ . By precisely controlling the electrostatic fields of  $V_{\rm bg}$  and  $V_{\rm ds}$ , the effective barrier height dramatically varied, and the current on/off ratio reached  $5\times 10^2$  and  $2\times 10^3$  for the electron and hole accumulation regimes, respectively. In addition, through extrapolation of the effective barrier height (at  $V_{\rm bg}=0$  V and  $V_{\rm ds}=0$  V), the bandgap of MoTe<sub>2</sub> was found to be 0.96 eV, which is consistent with the literature value, confirming the validity of this study. The tunability of these MoTe<sub>2</sub>-based ambipolar transistors is suitable for use in logic and analog applications. Our findings provide an important avenue toward future fundamental studies as well as for the production of new atomic electronics with simpler and higher integration densities.

## **Experimental Section**

Flakes made of a few layers of MoTe<sub>2</sub> were obtained by mechanical exfoliation of a semiconducting  $\alpha$ -MoTe<sub>2</sub> bulk crystal grown by chemical vapor transport and then deposited on a heavily doped Si substrate covered with a 285-nm-thick SiO<sub>2</sub> dielectric layer. As-synthesized MoTe<sub>2</sub> bulk crystals were examined by X-ray photoelectron spectroscopy (XPS) and X-ray diffraction (see Section I and Figure S2 of the Supporting Information for more details). Here the specific thickness of the SiO<sub>2</sub> layer was chosen to be able to optically visualize the contrast between the layers in the MoTe<sub>2</sub>.<sup>[37]</sup> Flakes suitable for electrical characterization were identified by an optical microscope and the corresponding thicknesses were accurately inspected by atomic force microscopy (AFM). After characterization, a pair of electrical contacts was patterned on top of the selected flakes using standard electron-beam lithography, followed by thermal evaporation of a Ti/Au film (5/50 nm thick). To acquire the temperature-dependent evolution, the as-fabricated MoTe<sub>2</sub> transistors were mounted into an insert cryostat. The temperature was set using a temperature controller (Cryogenic Control Systems model 32) in the range of 300 to 100 K. The quasi-static measurements of the layered MoTe2 transistors were carried out using an Agilent 4156C semiconductor parameter analyzer, whereas the dynamic characterizations were performed by combining a Hewlett-Packard 3245A signal generator and a Keithley 2400 power supply. The radiofrequency (RF) response was monitored using an Agilent 54830B digital oscilloscope.

### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

The authors acknowledge K. Komatsu for useful discussions. This research was supported by a Grant-in-Aid (Kakenhi No. 25107004) from the Japan Society for the Promotion of Science (JSPS) through the Funding Program for World-Leading Innovative R&D on Science and Technology (FIRST), initiated by the Council for Science and Technology Policy (CSTP) of Japan, and Experiment-Theory Fusion trial project by MANA.

Received: November 26, 2013 Revised: January 17, 2014 Published online: April 1, 2014

- [1] A. K. Geim, K. S. Novoselov, Nat. Mater. 2007, 6, 183-191.

- [2] K. P. Loh, Q. Bao, G. Eda, M. Chhowalla, Nat. Chem. 2010, 2, 1015–1024.

- [3] Q. H. Wang, K. Kalantar-zadeh, A. Kis, J. N. Coleman, M. S. Strano, Nat. Nanotechnol. 2012, 7, 699-712.

- [4] M. Xu, T. Liang, M. Shi, H. Chen, Chem. Rev. 2013, 113, 3766–3798.

- [5] K. J. Koski, Y. Cui, ACS Nano 2013, 5, 3739-3743.

- [6] M. Chhowalla, H. K. Shin, G. Eda, L. J. Li, K. P. Loh, H. Zhang, Nat. Chem. 2013, 5, 263–275.

- [7] M. S. Choi, G. H. Lee, Y. J. Yu, D. Y. Lee, S. H. Lee, P. Kim, J. Hone, W. J. Yoo, Nat. Commun. 2013, 4, 1624.

- [8] K. Balakrishnan, P. Ramasamy, J. Cryst. Growth 1994, 137, 309–311.

- [9] V. Podzorov, M. E. Gershenson, C. Kloc, R. Zeis, E. Bucher, Appl. Phys. Lett. 2004, 84, 3301–3303.

- [10] B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, A. Kis, Nat. Nanotechnol. 2011, 6, 147–150.

- [11] S. Larentis, B. Fallahazad, E. Tutuc, Appl. Phys. Lett. 2012, 101, 22 3104

- [12] D. Braga, I. G. Lezama, H. Berger, A. F. Morpurgo, Nano Lett. 2012, 12, 5218–5223.

- [13] H. Fang, S. Chuang, T. C. Chang, K. Takei, T. Takahashi, A. Javey, Nano Lett. 2012, 12, 3788–3792.

- [14] S. L. Li, K. Wakabayashi, Y. Xu, S. Nakaharai, K. Komatsu, W. Li, Y. F. Lin, A. Aparecido-Ferreira, K. Tsukagoshi, *Nano Lett.* 2013, 13, 3546–3552.

- [15] H. D. Abruna, G. A. Hope, A. J. Bard, J. Electrochem. Soc. 1982, 129, 2224–2228.

- [16] A. Conan, A. Bonnet, M. Zoaeter, D. Ramoul, Phys. Status Solidi B 1984, 124, 403–410.

- [17] J. C. Bernede, M. Kettaf, A. Khelil, M. Spiesser, *Phys. Status Solidi A* 1996, 157, 205–209.

- [18] M. B. Vellinga, R. D. Jonge, C. Haas, J. Solid State Chem. 1970, 2, 299–302.

- [19] Y. Ma, Y. Dai, M. Guo, C. Niu, J. Lu, B. Huang, Phys. Chem. Chem. Phys. 2011, 13, 15 546–15 553.

- [20] L. Qiu, Y. Wei, V. G. Pol, A. Gedanken, *Inorg. Chem.* 2004, 43, 6061–6066

- [21] X. Wu, Z. Xu, X. C. Zeng, Nano Lett. 2007, 7, 2987-2992.

- [22] A. J. Grant, T. M. Griffiths, G. D. Pitt, A. D. Yoffe, J. Phys. C: Solid State Phys. 1975, 8, L17-L23.

- [23] S. H. Eİ-Mahalawy, B. L. Evans, Phys. Status Solidi B 1977, 79, 713–722.

- [24] A. Conan, D. Delaunay, A. Bonnet, A. G. Moustafa, M. Spiesser, Phys. Status Solidi B 1979, 94, 279–286.

- [25] M. Kettaf, A. Conan, A. Bonnet, J. C. Bernede, J. Phys. Chem. Solids 1990, 51, 333–341.

- [26] E. J. Meijer, D. M. D. Leeuw, S. Setayesh, E. V. Veenendaal, B. H. Huisman, P. W. M. Blom, J. C. Hummelen, U. Scherf, T. M. Klapwijk, Nat. Mater. 2003, 2, 678–682.

- [27] Y. Zhang, J. Ye, Y. Matsuhashi, Y. Iwasa, Nano Lett. 2012, 12, 1136–1140.

- [28] Y. Zhang, J. Ye, Y. Yomogida, T. Takenobu, Y. Iwasa, Nano Lett. 2013, 13, 3023–3028.

- [29] M. M. Perera, M. W. Lin, H. J. Chuang, B. P. Chamlagain, C. Wang, X. Tan, M. M. C. Cheng, D. Tomanek, Z. Zhou, ACS Nano 2013, 7, 4449–4458.

- [30] T. Boker, R. Severin, A. Muller, C. Janowitz, R. Manzke, D. Vob, P. Kruger, A. Mazur, J. Pollmann, Phys. Rev. B 2001, 64, 235 305.

- [31] F. Schwierz, Nat. Nanotechnol. 2010, 5, 487-496.

- [32] K. Lee, H. Y. Kim, M. Lotya, J. N. Coleman, G. T. Kim, G. S. Duesberg, Adv. Mater. 2011, 23, 4178–4182.

ADVANCED MATERIALS

#### www.MaterialsViews.com

- [33] R. Martel, V. Derycke, C. Lavoie, J. Appenzeller, K. K. Chan, J. Tersoff, P. Avouris, Phys. Rev. Lett. 2001, 87, 256 805.

- [34] Y. F. Lin, W. B. Jian, Nano Lett. 2008, 8, 3146-3150.

- [35] S. Heinze, J. Tersoff, R. Martel, V. Derycke, J. Appenzeller, P. Avouris, *Phys. Rev. Lett.* **2002**, *89*, 106 801.

- [36] S. Walia, S. Balendhran, Y. Wang, R. A. Kadir, A. S. Zoolfakar, P. Atkin, J. Z. Ou, S. Sriram, K. Kalantar-zadeh, M. Bhaskaran, Appl. Phys. Lett. 2013, 103, 232 105.

- [37] M. M. Benameur, B. Radisavljevic, J. S. Heron, S. Sahoo, H. Berger, A. Kis, Nanotechnology 2011, 22, 125 706.