Home Search Collections Journals About Contact us My IOPscience

Schottky barrier height modification of metal/4H-SiC contact using ultrathin  ${\rm TiO}_2$  insertion method

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2014 Jpn. J. Appl. Phys. 53 04EP10

(http://iopscience.iop.org/1347-4065/53/4S/04EP10)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/12/2014 at 03:17

Please note that terms and conditions apply.

# Schottky barrier height modification of metal/4H-SiC contact using ultrathin TiO<sub>2</sub> insertion method

Bing-Yue Tsui<sup>1\*</sup>, Jung-Chien Cheng<sup>1</sup>, Lurng-Shehng Lee<sup>2</sup>, Chwan-Ying Lee<sup>2</sup>, and Ming-Jinn Tsai<sup>2</sup>

Received September 22, 2013; accepted December 24, 2013; published online March 6, 2014

The fabrication processes, electrical characteristics, and reliability of the Schottky barrier diodes (SBDs) on an n-type 4H-silicon carbide (SiC) substrate are investigated. To modulate the Schottky barrier height (SBH), titanium dioxide ( $TiO_2$ ) is inserted at the interface between the metal and the SiC substrate. Ni, Mo, Ti, and Al are chosen to form SBDs. The maximum SBH modulation of  $0.3 \, \text{eV}$  is obtained with a 5-nm-thick  $TiO_2$  layer. The SBH pinning factors of the SBDs without  $TiO_2$  insertion and with 2-nm-thick  $TiO_2$  insertion are similar. Therefore, the mechanism of the SBH modulation is attributed to the interface dipole-induced potential drop. Finally, the reliability of the SBD with  $TiO_2$  insertion is evaluated. The SBH, ideality factor, and reverse leakage current are stable after high forward current stress at  $300 \, \text{A/cm}^2$  for  $15000 \, \text{s}$ . This work provides a simple method to modulate the SBH on SiC and is feasible for SBD application. ©  $2014 \, \text{The}$  Japan Society of Applied Physics

#### 1. Introduction

Schottky barrier diodes (SBDs) have been utilized as rectifying devices because of their high switching speed and low minority carrier storage effect compared with pn diodes. However, the reverse breakdown voltage of Si-based SBDs is usually lower than 200 V because the narrow band gap of Si is only about 1.12 eV.<sup>1)</sup> Simultaneously, Si-based SBDs suffer from a high thermal generation rate of minority carriers, which leads to vital leakage current when operating at temperatures higher than 150 °C.

Among more than 170 crystalline polytypes in the silicon carbide (SiC) system, 4H-SiC has been regarded as a candidate for high-power and high-frequency electronic devices owing to its wide band gap ( $\sim$ 3.26 eV), high thermal conductivity ( $\sim$ 5.0 W cm<sup>-1</sup> K<sup>-1</sup>), and high electron mobility  $(\sim 1000 \,\mathrm{cm^2 \, V^{-1} \, s^{-1}}).^{2-4)}$  Besides, SiC is chemically inert and has strong mechanical hardness. These properties are beneficial to operate the SiC power devices in harsh environments, e.g., motor control systems or automobile electronics. SiC-based SBDs have many advantages, such as high breakdown voltage (>600 V) and low switching loss.<sup>5–9)</sup> To avoid unnecessary power consumption due to parasitic resistance, all semiconductor devices require a low Schottky barrier height (SBH) and a low contact resistivity at the metal/semiconductor contacts, which result in bi-directional current flowing through the contacts and low on-resistance  $(R_{\rm on})$ .

Considering the Fermi-level pinning effect, the SBH can be expressed as

$$\Phi_{\rm bn} = S(\Phi_{\rm m} - \Phi_{\rm CNL}) + (\Phi_{\rm CNL} - \chi), \tag{1}$$

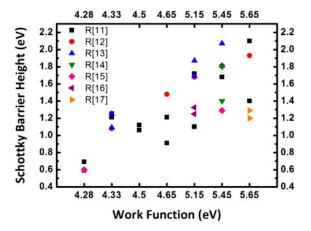

where S is the pinning factor,  $\chi$  is the electron affinity of the semiconductor,  $\Phi_m$  is the metal work function, and  $\Phi_{CNL}$  is the semiconductor charge neutrality level. The published SBHs are drawn as a function of the metal work function  $(\Phi_m)$  in Fig. 1.  $^{11-17}$  The S factor is approximately 0.6–0.7. Although we can achieve a lower SBH and contact resistance by applying lower  $\Phi_m$  metals, lower  $\Phi_m$  metals are active and may not be stable during the remaining semiconductor processes. To reduce the SBH and the contact resistivity, most studies have figured out that an ohmic contact can be formed by a high-temperature (>900 °C) annealing process

**Fig. 1.** (Color online) Distribution of Schottky barrier height as a function of metal work function reported in the literature. The pinning factor is approximately 0.6–0.7.

between a heavily doped SiC substrate ( $>5 \times 10^{18}\,\mathrm{cm}^{-3}$ ) and various metals, such as Ni and Ti. <sup>18–24</sup>) In general, the specific contact resistance can be lower than  $1\times 10^{-4}\,\Omega\,\mathrm{cm}^2$  but higher than  $1\times 10^{-6}\,\Omega\,\mathrm{cm}^2$ .

Except for the ohmic contact, introducing a high dielectric constant (high-k) thin film in Si-, Ge-, and GaAs-based SBDs has been proposed to modulate SBH and contact resistivity in recent experiments.  $^{25-27)}$  Different kinds of dielectrics, e.g.,  $\mathrm{Si_3N_4},^{28,29)}$  MgO,  $^{30)}$  Al<sub>2</sub>O<sub>3</sub>,  $^{31,32)}$  GeO<sub>x</sub>,  $^{33)}$  and TiO<sub>2</sub>,  $^{27)}$  have been employed. Several models have been proposed to explain the SBH modulation mechanism. (1) The inserted dielectric layer could block the work function penetration and reduce the metal-induced gap states (MIGS) to relax the Fermi-level pinning. 30,33,34) (2) The formation of dipoles at the dielectric/semiconductor interface would provide a potential drop in the carrier transport path to modulate the SBH.<sup>25,35,36)</sup> Recently, Hu et al. have proposed that (3) the fixed oxide charge would exist in a non-ideal, amorphous, and non-stoichiometric dielectric layer and also provide an extra potential drop.<sup>26)</sup> Furthermore, Fermi-level pinning at the metal/dielectric interface is also observed.<sup>37–39)</sup> These explanations are verified in this work.

<sup>&</sup>lt;sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan 30010, R.O.C.

<sup>&</sup>lt;sup>2</sup>Electronics and Optoelectronics Research Laboratory, Industrial Technology Research Institute, Hsinchu, Taiwan 31040, R.O.C. E-mail: bytsui@mail.nctu.edu.tw

Compared with the ohmic contact formation by high-temperature annealing, the dielectric insertion method avoids the silicidation process and reduces the thermal budget substantially. Nevertheless, studies have seldom used this method on SiC-based SBDs to modulate SBH so far. In addition, some basic properties have not been studied yet, for example, the SBH control and the contact resistance of the metal/dielectric/SiC contacts.

In this work, we fabricate and characterize the 4H-SiC SBDs with a  $TiO_2$  interfacial layer. It is demonstrated that the  $TiO_2$  layer is able to reduce the SBH on SiC-based SBDs effectively as on Si- and Ge-based SBDs. The stability of the metal/ $TiO_2$ /SiC contact is also evaluated by applying current stress at room temperature.

### 2. Experimental methods

The SBDs were fabricated on an n-type nitrogen-doped (0001)-oriented 4H-SiC substrate with a doping concentration of  $1 \times 10^{18} \,\mathrm{cm}^{-3}$ , with a 5-µm-thick epitaxial layer with a doping concentration of  $3 \times 10^{15} \,\mathrm{cm}^{-3}$ , which was purchased from CREE. First of all, the substrate was cleaned by the standard RCA cleaning process followed by a 200-nmthick oxide deposition using a plasma-enhanced chemicalvapor-deposition (PECVD) system. This oxide layer was used to protect the front-surface of samples. Native oxide was removed by dipping samples in diluted HF (DHF) solution and then a Ni/TiN stack (100 nm/30 nm) was deposited at the backside of samples using a sputtering system. Samples were then annealed at 1000 °C in N2 ambient for 30 s to form good ohmic contacts. After the annealing process, the  $H_2SO_4: H_2O_2 = 3:1$  solution was used to remove the unreacted metal. The front-side protection layer was removed by buffer oxide etchant (BOE) solution.

For the sake of creating a uniform and hydrophilic surface before  $\rm TiO_2$  deposition using an atomic layer deposition (ALD) system, the samples were soaked in the  $\rm H_2SO_4$ :  $\rm H_2O_2=3:1$  solution for 10 min. Soon afterwards, blanket  $\rm TiO_2$  films with various thicknesses were deposited at 250 °C in thermal mode using tetrakis(dimethylamino)titanium (TDMAT) and  $\rm H_2O$  as precursors. In contrast, the reference samples bypassed the soaking in sulfuric acid and the  $\rm TiO_2$  deposition to maintain pure metal/SiC interfaces.

The front-side contacts were patterned by photolithography and cleaned by DHF immersion. The radii of contacts were 400, 200, 100, and 50 µm. Different metals were deposited by sputtering or a thermal evaporation system, followed by deposition of a 300-nm-thick Al layer for probing. Then, metals beyond the contacts were lifted-off by ultrasonic oscillation in acetone. Finally, samples were alloyed at 500 °C for 5 min in vacuum. The key process conditions are listed in Table I.

Electrical measurements were performed at room temperature using a semiconductor parameter analyzer (Agilent 4156C). The cross-sectional structure of SBD was inspected by transmission electron microscopy (TEM; JEM-2100F).

## 3. Results and discussion

## 3.1 Effect of TiO<sub>2</sub> thickness

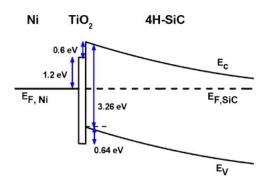

Figure 2 shows sketches of the Ni/TiO<sub>2</sub>/SiC band diagram. TiO<sub>2</sub> is selected as the insertion dielectric because of the negative electron barrier between SiC and TiO<sub>2</sub>, so that no

**Table I.** Key process conditions.

|                                 | Contact metal                  |               |            |               |

|---------------------------------|--------------------------------|---------------|------------|---------------|

|                                 | Al                             | Ti            | Mo         | Ni            |

| Metal thickness (nm)            | 300                            | 100           | 30         | 100           |

| Deposition method               | Thermal evaporation            | Sputtering    | Sputtering | Sputtering    |

| TiO <sub>2</sub> thickness (nm) | 0, 2                           | 0, 1, 2, 5, 8 | 0, 2       | 0, 1, 2, 5, 8 |

| Annealing                       | 500 °C/5 min/in vacuum furnace |               |            |               |

**Fig. 2.** (Color online) Band diagram of a metal/ $TiO_2/4H$ -SiC Schottky barrier diode. The conduction band of  $TiO_2$  is lower than that of SiC, which is preferred to avoid extra electron tunneling resistance.

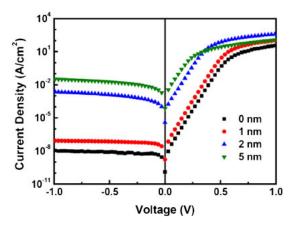

**Fig. 3.** (Color online) I–V characteristics of the Ti SBDs with various  $TiO_2$  thicknesses. Thicker  $TiO_2$  brings about a lower SBH and a higher reverse current.

extra resistance exists and a sufficiently high carrier tunneling probability or thermionic emission rate to obtain a high forward conduction current can be expected.

Firstly, we alter the thickness of the  $TiO_2$  layer to determine the most effective modulation. Figure 3 shows the current–voltage (I–V) characteristics of the Ti SBDs with various  $TiO_2$  thicknesses. According to the basic thermionic emission model, the I–V characteristic can be expressed as

$$I = AA^*T^2 \times \exp\left(-\frac{q\Phi_{\rm bn}}{kT}\right) \times \left[\exp\left(\frac{qV}{\eta kT}\right) - 1\right], \quad (2)$$

where A is the SBD area,  $A^*$  is the effective Richardson constant (146 A cm<sup>-2</sup> K<sup>-2</sup>),<sup>40)</sup> k is the Boltzmann constant, and T is the absolute temperature. The ideality factor ( $\eta$ ) can be extracted as a qualitative benchmark of SBDs. The SBD without a TiO<sub>2</sub> layer exhibits the highest average SBH and

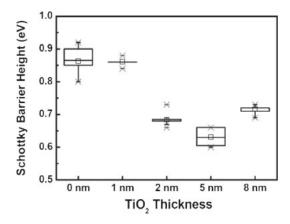

**Fig. 4.** Distribution of Schottky barrier height as a function of  $\text{TiO}_2$  thickness. A  $0.2\,\text{eV}$  SBH reduction is approached with a 2-nm-thick  $\text{TiO}_2$  insertion. The boxes are defined by the 25th and 75th percentiles. The whiskers are defined by the 5th and 95th percentiles. The median, mean, and maximum/minimum values are represented by the line in the box, the square in the box, and the asterisks, respectively.

the lowest leakage current. On the other hand, as shown in Fig. 4, the SBDs with  $TiO_2$  insertion show modulated characteristics and the average SBH decreases from 0.9 to 0.63 eV as the  $TiO_2$  thickness increases from 0 to 5 nm. As the thickness of the  $TiO_2$  layer exceeds 5 nm, the carrier tunneling probability or thermionic emission rate decreases dramatically. Therefore, the SBDs turn out to have a higher average SBH ( $\sim$ 0.75 eV). This trend of SBH modulation is similar to that observed on a Ge substrate.<sup>27)</sup> It is known that the SBH would be affected by the surface defects.<sup>41–43)</sup> Figure 4 shows that the SBH variation of the SBDs with  $TiO_2$  insertion is lower than that without  $TiO_2$  insertion. This result implies that the  $TiO_2$  layer can passivate the surface defects to improve the device uniformity.

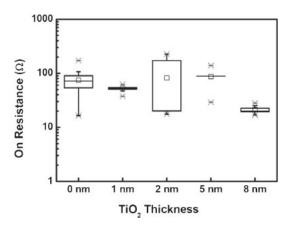

Figure 5 shows the  $R_{\rm on}$  distribution versus TiO<sub>2</sub> thickness. On purpose, we extracted  $R_{\rm on}$  at  $V=\Phi_{\rm bn}$  to unify the turn-on situation of different SBDs.  $R_{\rm on}$  is not degraded by the TiO<sub>2</sub> layer as expected because of the negative conduction band off-set between TiO<sub>2</sub> and SiC. Since the SBDs are fabricated on the substrate with a lightly doped epitaxial layer,  $R_{\rm on}$  is dominated by the resistance of the epitaxial layer. To reduce the extracted specific contact resistance, the doping concentration near the interface of the metal/SiC contact should be raised and suitable test structures such as the transmission-line method (TLM) structure or the cross-bridge Kelvin resistor (CBKR) structure should be employed.

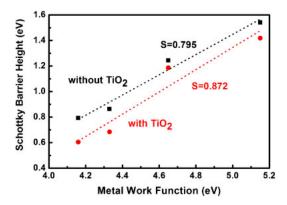

#### 3.2 SBH modulation mechanism

In Fig. 6, compared with pure metal/SiC SBDs, we use a 2-nm-thick  ${\rm TiO_2}$  layer as a standard condition to study the SBH modulation with various metals. The pinning factors S can be extracted from the slope of the linear regression of the SBH versus metal work function plot. The metals we used are Ni, Mo, Ti, and Al with work functions of 5.15, 4.65, 4.33, and 4.16 eV, respectively. The pinning factor of pure metal/SiC SBDs is about 0.8, which is slightly higher but still comparable to the pinning factor obtained from Fig. 1. In contrast, the pinning factor of the metal/TiO<sub>2</sub> (2 nm)/SiC SBDs is about 0.87, which is similar to the pinning factor of the pure metal/SiC SBDs.

Fig. 5. Distribution of on-resistance as a function of  $TiO_2$  thickness at  $V = \Phi_{bn}$ . The compact range indicates that the on-resistance is not degraded by the  $TiO_2$  layer. The boxes are defined by the 25th and 75th percentiles. The whiskers are defined by the 5th and 95th percentiles. The median, mean, and maximum/minimum values are represented by the line in the box, the square in the box, and the asterisks, respectively.

**Fig. 6.** (Color online) Distribution of Schottky barrier height as a function of metal work function. The pinning factor does not change significantly, but the SBHs of Ni, Ti, and Al SBDs reduce by about  $0.2 \, \text{eV}$  uniformly when  $\text{TiO}_2$  is inserted.

As mentioned in the introduction, one of the SBH modulation mechanisms is MIGS. If this is the main mechanism, the Fermi level pinning effect should be eliminated and the pinning factor should be much closer to 1 after  ${\rm TiO_2}$  insertion. However, there is only a slight difference between both conditions, which indicates that the inserted  ${\rm TiO_2}$  layer does not depin the Fermi level effectively. MIGS may be not the main mechanism for barrier lowering. The high pinning factor also implies that MIGS are not severe on the SiC SBDs. Meanwhile, various metals exhibit a similar level in the SBH modulation. The average SBH values of Ni-, Ti-, and Al-contacted diodes decrease uniformly by  $\sim 0.2 \, {\rm eV}$  when a 2-nm-thick  ${\rm TiO_2}$  layer is inserted. Therefore, the effect of the  ${\rm TiO_2}$  layer is to shift the SBH but not to relax the Fermi level pinning.

It has been suggested that the fixed oxide charges in the inserted dielectric or the dipole at the dielectric/SiC interface would induce an extra potential drop. <sup>25,26,35,36)</sup> This potential drop reduces the SBH. Besides, owing to the 500 °C alloying process on all samples, a new interfacial layer may be formed to modulate the SBH. The cross-sectional structure of the Ni

**Fig. 7.** TEM image of Ni SBDs with a 2-nm-thick TiO<sub>2</sub> insertion. Three clear layers, Ni, TiO<sub>2</sub>, and SiC, are separate and no new interfacial layer was formed. The TiO<sub>2</sub> layer has become polycrystalline after the alloying process.

SBD with a 2-nm-thick TiO<sub>2</sub> layer was inspected by TEM. As shown in Fig. 7, three layers, Ni, TiO<sub>2</sub>, and SiC, are clearly distinct and no new interfacial layer was formed during the alloying process. It is concluded that the SBH modulation is not induced by the formation of a new interfacial layer. At the same time, the image of the TiO<sub>2</sub> layer shows an ordered arrangement, which indicates that, the TiO<sub>2</sub> layer becomes crystallized during the alloying process. We assume that the relative dielectric constant of the TiO<sub>2</sub> layer is 80.44) If the main mechanism of the SBH reduction is due to the fixed oxide charge, to approach a 0.2 eV reduction in the band diagram, the estimated amount of fixed oxide charge would be as high as  $4 \times 10^{13} \,\mathrm{cm}^{-2}$ . However, the amount of fixed oxide charge should be decreased substantially as the dielectric layer crystallizes. Consequently, we postulate that the interface dipoles induced by the inserted TiO<sub>2</sub> layer affect the SBH reduction effectively rather than the fixed oxide charge. It should be noted that the SBH is not pinned at the metal/TiO2 interface, as reported in the literature.  $^{38,39)}$  A possible reason for this is that the  ${\rm TiO}_2$  is not thick enough to prevent the interaction of wave-functions between the metal and the SiC substrate. The Fermi-level pinning effect with different TiO<sub>2</sub> thicknesses and alloying temperatures should be studied to clarify the pinning mechanism between the metal and the dielectric layer.

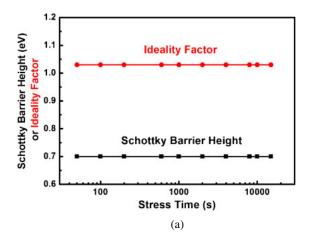

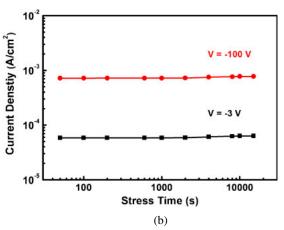

#### 3.3 Reliability testing

Figure 8 shows the SBH, ideality factor, and reverse biased leakage current of the Ti SBD with 2-nm-thick  ${\rm TiO_2}$  stressed with accumulated time. A high stress current of about 300 A/cm² was applied at forward bias under room temperature. In Fig. 8(b), the reverse biased leakage current was measured when the stress duration was finished. A minor increase in the reverse biased leakage current is observed. However, the variations before and after stress are only 8.4 and 7.4% at -3 and  $-100\,{\rm V}$ , respectively. The extracted SBH and ideality factor are constant. According to the consistent results before and after testing, it is suggested that the  ${\rm TiO_2}$  layer is stable for forward stress.

**Fig. 8.** (Color online) Parameters of the Ti/TiO<sub>2</sub> (2 nm)/SiC SBD after current stress at  $\sim 300 \, \text{A/cm}^2$  for 15000 s. The parameters are (a) Schottky barrier height and ideality factor and (b) reverse current at V=-3 and  $-100 \, \text{V}$ . All parameters are very stable.

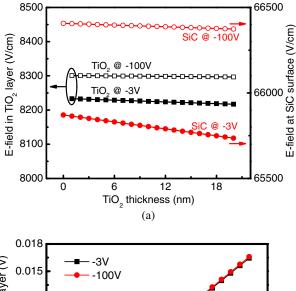

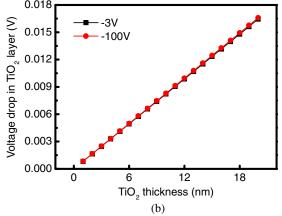

Figure 9 shows the electric fields at both sides of the TiO<sub>2</sub>/ SiC interface at reverse biases of -3 and -100 V and the voltage drops across the TiO<sub>2</sub> layer as a function of the TiO<sub>2</sub> thickness. The parameters used for the calculation are permittivity of TiO2 is 80, permittivity of SiC is 10, doping concentration of SiC is  $3 \times 10^{15} \,\mathrm{cm}^{-3}$ , and thickness of the SiC epitaxial layer is 5 µm. Since the dielectric constant of TiO<sub>2</sub> is 5–8 times higher than that of the SiC and the TiO<sub>2</sub> thickness is much smaller than the depletion width in SiC, the TiO<sub>2</sub> capacitance is much higher than the depletion capacitance. Therefore, almost all of the voltage drops across the SiC but not across the TiO2 layer. Furthermore, the electric field in TiO2 is much lower than the critical field of TiO<sub>2</sub>, which is about 0.3 MV/cm. 45) These results indicate that the inserted thin TiO2 layer would not affect the reverse breakdown performance of the SBD. Nevertheless, SiCbased SBDs are usually operated at near breakdown voltage and under high-temperature condition. To simulate the work environment, more harsh reliability tests should be applied on the SBDs with TiO<sub>2</sub> inserted.

## 4. Conclusions

In this study, SBDs on 4H-SiC substrates were fabricated with different TiO<sub>2</sub> thicknesses to investigate the effect of the dielectric insertion on the SBH modulation. The maximum

**Fig. 9.** (Color online) (a) Calculated electric fields at both sides of the  $TiO_2/SiC$  interface and (b) calculated voltage drops across the  $TiO_2$  layer at V = -3 and -100 V.

SBH modulation of 0.3 eV is achieved with a 5-nm-thick  $TiO_2$  insertion layer between Ti and SiC. The similar  $R_{on}$ distributions suggest that the TiO2 insertion does not degrade the SBDs. The pinning factor increases slightly from 0.8 to 0.87 so that the MIGS model cannot explain the change of the SBH completely. The fixed oxide charge model or newly formed interfacial layer are also excluded because the TEM image of the Ni/TiO<sub>2</sub> (2 nm)/SiC structure shows no new interfacial layer but a gradually crystallized TiO2 layer. The main mechanism of the SBH modulation is attributed to the interface dipole. Finally, a high-level current stress was applied on the SBDs with TiO2 inserted. The SBH, ideality factor, and reverse leakage current are similar before and after stress. It is suggested that the dielectric insertion technique can be used to control the SBH of SBDs and to form low resistance ohmic contacts.

## Acknowledgements

The authors would like to thank the Nano Facility Center and the Center for Nanoscience and Technology at National Chiao-Tung University for providing the experimental facilities. This work was supported in part by the Ministry of Education in Taiwan under the ATU program, and was supported in part by the National Science Council, Taiwan, R.O.C. under contract No. NSC 100-2221-E-009-010-MY2.

- T. Kimoto, T. Urushidani, S. Kobayashi, and H. Matsunami, IEEE Electron Device Lett. 14, 548 (1993).

- 2) J. B. Casady and R. W. Johnson, Solid-State Electron. 39, 1409 (1996).

- 3) J. R. Jenny, S. G. Müller, A. Powell, V. F. Tsvetkov, H. M. Hobgood, R. C. Glass, and C. H. Carter, Jr., J. Electron. Mater. 31, 366 (2002).

- 4) N. S. Saks and A. K. Agarwal, Appl. Phys. Lett. 77, 3281 (2000).

- R. Raghunathan, D. Alok, and B. J. Baliga, IEEE Electron Device Lett. 16, 226 (1995).

- V. Saxena and A. J. Steckl, Proc. Int. Semiconductor Device Research Symp., 1997, p. 542.

- Q. Wahab, T. Kimoto, A. Ellison, C. Hallin, M. Tuominen, R. Yakimova, A. Henry, J. P. Bergman, and E. Janzén, Appl. Phys. Lett. 72, 445 (1998).

- V. Saxena, J. N. Su, and A. J. Steckl, IEEE Trans. Electron Devices 46, 456 (1999).

- 9) R. Talwar and A. K. Chatterjee, J. Electron Devices 6, 194 (2008).

- 10) J. Robertson, J. Vac. Sci. Technol. B 27, 277 (2009).

- T. V. Blank, Yu. A. Goldberg, E. A. Posse, and F. Yu. Soldatenkov, Semiconductors 44, 463 (2010).

- 12) T. Kimoto, Proc. Symp. VLSI Technology, 2010, p. 9.

- 13) A. Itoh and H. Matsunami, Phys. Status Solidi A 162, 389 (1997).

- 14) F. Roccaforte, F. Giannazzo, F. Iucolano, J. Eriksson, M. H. Weng, and V. Raineri, Appl. Surf. Sci. 256, 5727 (2010).

- 15) W. R. Harrell, J. Zhang, and K. F. Poole, J. Electron. Mater. 31, 1090 (2002).

- 16) S. K. Gupta, A. Azam, and J. Akhtar, Physica B 406, 3030 (2011).

- M. Sochacki, A. Kolendo, J. Szmidt, and A. Werbowy, Solid-State Electron. 49, 585 (2005).

- W. Daves, A. Krauss, V. Häublein, A. J. Bauer, and L. Frey, J. Electron. Mater. 40, 1990 (2011).

- A. V. Kuchuk, V. P. Kladko, A. Piotrowska, R. Ratajczak, and R. Jakieła, Mater. Sci. Forum 615–617, 573 (2009).

- M. Xu, X. Hu, Y. Peng, K. Yang, W. Xia, G. Yu, and X. Xu, J. Alloys Compd. 550, 46 (2013).

- 21) T. Uemoto, Jpn. J. Appl. Phys. 34, L7 (1995).

- 22) S. Y. Han, K. H. Kim, J. K. Kim, H. W. Jang, K. H. Lee, N.-K. Kim, E. D. Kim, and J.-L. Lee, Appl. Phys. Lett. 79, 1816 (2001).

- S.-C. Chang, S.-J. Wang, K.-M. Uang, and B.-W. Liou, Solid-State Electron. 49, 1937 (2005).

- 24) F. La Via, F. Roccaforte, A. Makhtari, V. Raineri, P. Musumeci, and L. Calcagno, Microelectron. Eng. 60, 269 (2002).

- B. E. Coss, C. Smith, W.-Y. Loh, P. Majhi, R. M. Wallace, J. Kim, and R. Jammy, IEEE Electron Device Lett. 32, 862 (2011).

- 26) J. Hu, A. Nainani, Y. Sun, K. C. Saraswat, and H.-S. P. Wong, Appl. Phys. Lett. 99, 252104 (2011).

- 27) J.-Y. J. Lin, A. M. Roy, A. Nainani, Y. Sun, and K. C. Saraswat, Appl. Phys. Lett. 98, 092113 (2011).

- M. Kobayashi, A. Kinoshita, K. Saraswat, H.-S. P. Wong, and Y. Nishi, J. Appl. Phys. 105, 023702 (2009).

- D. Connelly, C. Faulkner, P. A. Clifton, and D. E. Grupp, Appl. Phys. Lett. 88, 012105 (2006).

- Y. Zhou, W. Han, Y. Wang, F. Xiu, J. Zou, R. K. Kawakami, and K. L. Wang, Appl. Phys. Lett. 96, 102103 (2010).

- Y. Zhou, M. Ogawa, X. Han, and K. L. Wang, Appl. Phys. Lett. 93, 202105 (2008).

- 32) G. Kioseoglou, A. T. Hanbicki, R. Goswami, O. M. J. van 't Erve, C. H. Li, G. Spanos, P. E. Thompson, and B. T. Jonker, Appl. Phys. Lett. 94, 122106 (2009)

- T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Express 1, 051406 (2008).

- 34) T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Lett. 91, 123123 (2007).

- 35) J. F. Wager and J. Robertson, J. Appl. Phys. **109**, 094501 (2011).

- 36) B. E. Coss, P. Sivasubramani, B. Brennan, P. Majhi, R. M. Wallace, and J. Kim, J. Vac. Sci. Technol. B 31, 021202 (2013).

- 37) Y.-C. Yeo, T.-J. King, and C. Hu, J. Appl. Phys. 92, 7266 (2002).

- 38) W. Mönch, J. Appl. Phys. 111, 073706 (2012).

- 39) B.-Y. Tsui and M.-H. Kao, Appl. Phys. Lett. 103, 032104 (2013).

- A. Itoh, T. Kimoto, and H. Matsunami, IEEE Electron Device Lett. 16, 280 (1995).

- M. Bhatnagar, B. J. Baliga, H. R. Kirk, and G. A. Rozgonyi, IEEE Trans. Electron Devices 43, 150 (1996).

- D. J. Ewing, L. M. Porter, Q. Wahab, X. Ma, T. S. Sudharshan, S. Tumakha, M. Gao, and L. J. Brillson, J. Appl. Phys. 101, 114514 (2007).

- S. Tumakha, D. J. Ewing, L. M. Porter, Q. Wahab, X. Ma, T. S. Sudharshan, and L. J. Brillson, Appl. Phys. Lett. 87, 242106 (2005).

- 44) S. K. Kim, W.-D. Kim, K.-M. Kim, C. S. Hwang, and J. Jeong, Appl. Phys. Lett. 85, 4112 (2004).

- J. W. Lim, S. J. Yun, and J. H. Lee, Electrochem. Solid-State Lett. 7, F73 (2004).