## Submicron organic thin-film transistors fabricated by film profile engineering method

Ming-Hung Wu, Horng-Chih Lin, Hung-Cheng Lin, Hsiao-Wen Zan, Hsin-Fei Meng, and Tiao-Yuan Huang

Citation: Applied Physics Letters **105**, 043304 (2014); doi: 10.1063/1.4892404

View online: http://dx.doi.org/10.1063/1.4892404

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/105/4?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Independently driven four-probe method for local electrical characteristics in organic thin-film transistors under controlled channel potential

Rev. Sci. Instrum. 82, 093902 (2011); 10.1063/1.3637489

Fabrication of thin-film organic transistor on flexible substrate via ultraviolet transfer embossing

Appl. Phys. Lett. 90, 243502 (2007); 10.1063/1.2747670

## Performance of organic thin-film transistors

J. Vac. Sci. Technol. B 24, 1728 (2006); 10.1116/1.2209992

Self-aligned self-assembly process for fabricating organic thin-film transistors

Appl. Phys. Lett. 85, 1849 (2004); 10.1063/1.1784871

Organic polymeric thin-film transistors fabricated by selective dewetting

Appl. Phys. Lett. 81, 4260 (2002); 10.1063/1.1524301

## Submicron organic thin-film transistors fabricated by film profile engineering method

Ming-Hung Wu, <sup>1</sup> Horng-Chih Lin, <sup>1,a)</sup> Hung-Cheng Lin, <sup>2</sup> Hsiao-Wen Zan, <sup>2</sup> Hsin-Fei Meng, <sup>3</sup> and Tiao-Yuan Huang <sup>1</sup>

<sup>1</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

<sup>2</sup>Department of Photonics and Institute of Electro-Optics, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

<sup>3</sup>Institute of Physics, National Chiao Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan

(Received 23 April 2014; accepted 22 July 2014; published online 1 August 2014)

In this work, we explore and demonstrate the feasibility of a film profile engineering (FPE) concept in fabricating pentacene-based organic thin-film transistors (OTFTs) with submicron channel length. The FPE scheme utilizes a suspended bridge built on the wafer and the specific deposition conditions to form thin films with desirable profiles. In order to form a continuous pentacene channel under the bridge, the background pressure of thermal evaporator is adjusted by pumping down the filling  $N_2$  to a specific level. The results show that, by setting the deposition pressure at 3 mtorr, functional operations of OTFTs with channel length ranging from 0.4 to 0.6  $\mu$ m are obtained. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4892404]

Organic thin-film transistors (OTFTs) have attracted considerable attention because of their potential for use in electronic devices and displays, such as switching devices for active matrix flat-panel displays (AMFPDs), low-end smart cards, and electronic identification tags. The channel length of most reported OTFTs is typically a few microns. To improve the performance of devices such as on-current and operation speed, a smaller channel length is highly desired.<sup>2–5</sup> During the past few years, several approaches have been proposed to fabricate OTFTs with submicron channel length. 6-9 In 2005, Iwao et al. used electron-beam lithography to achieve the top-contact OTFTs with submicron channel length. In that work a suspended resist structure composed of three stacked resist layers was cleverly prepared prior to the subsequent two-step oblique evaporation of pentacene channel. After the formation of the channel layer, the S/D metal layer was evaporated in the same chamber and patterned with the suspended structure in a self-aligned manner. From the viewpoint of practical manufacturing, however, the use of electron-beam lithography is obviously not suitable for large-area applications as throughput is concerned. In addition, the fabrication of the suspended structure and the twostep evaporation of pentacene channel which involves the tilt of the substrate are complicated.

Recently, we have reported a film profile engineering (FPE) concept for fabricating high-performance oxide-based thin-film transistors (TFTs). Owing to the unique deposition conditions of several tools, this technique can be implemented to deposit films with desired profiles. In this study, we aim to develop the proposed FPE concept with the modified deposition pressure of evaporator systems to fabricate high-performance OTFTs with submicron channel length and address the above mentioned issues in the earlier work.

In the previous report on the fabrication of ZnO TFTs with the FPE scheme, <sup>10</sup> an RF magnetron sputter was used

to deposit the continuous and highly concave channel film beneath the suspended bridge built over the center of the device. In this study, a thermal evaporator was employed for depositing the pentacene channel and a major consideration on the deposition pressure is raised. Deposition of evaporators is usually set in the range from  $10^{-6}$  to  $10^{-5}$  Torr, unuch lower than that of the sputter deposition ( $\sim$ mtorr). Such a low pressure may hinder the formation of a continuous layer, as the scattering probability in the chamber is too small to affect the directionality of the deposition species. To address this issue, in the experiments we intentionally manipulate the background  $N_2$  pressure in the chamber and study its impacts on the device characteristics.

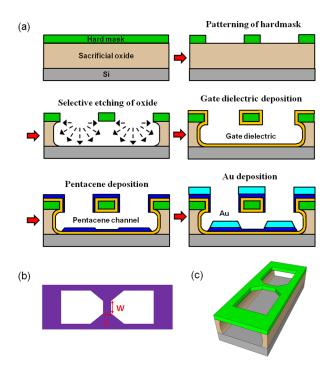

The detailed FPE procedure for fabricating the pentacene-based OTFTs is shown in Fig. 1(a). The completed device is bottom-gated and, for simplicity, the n-type Si wafer is used as the gate. First, a 400 nm-thick tetraethylorthosilicate (TEOS) oxide serving as a sacrificial layer and a 200 nm-thick undoped polycrystalline silicon (poly-Si) serving as a hard mask were sequentially deposited on the Si substrate by low-pressure chemical vapor deposition (LPCVD). Then, the undoped poly-Si was lithographically patterned by an I-line stepper using the layout design illustrated in Fig. 1(b) to define the source and drain regions of the device. Channel length (L) and width (W) are also specified in the figure. An HF-containing solution was then used to etch the sacrificial oxide until the undoped poly-Si bridge was suspended. Fig. 1(c) shows the 3D-view of the etched structure after this step. Next, a TEOS oxide with nominal thickness of 50 nm was deposited and used as the gate dielectric by plasma-enhanced chemical vapor deposition (PECVD) at 300 °C under a pressure of 500 mtorr. Afterwards the pentacene channel was deposited by thermal evaporator with nominal thickness of 150 nm. Before the deposition the chamber of the evaporator was filled with pure N<sub>2</sub> gas at atmosphere. For realization of the FPE scheme, we adjusted the background pressure of the chamber

a)Electronic mail: hclin@faculty.nctu.edu.tw

FIG. 1. (a) The FPE process flow for fabricating the pentacene-based organic TFTs. (b) The one-mask design which defines the dimension of devices. (c) The 3D view of the etched structure.

by pumping down the N2 to a specific value. In this work, the  $N_2$  was pumped to 3 mTorr or  $5 \times 10^{-6}$  Torr in order to verify the impact of the pressure. The two pressures are chosen because of the vacuum design of the thermal coater which is pumped with a mechanical pump and turbo pump. The background is 3 mtorr when only the mechanical pump is used, and reduces down to  $5 \times 10^{-6}$  torr as the turbo pump is turned on. Subsequently, the pentacene vapor was introduced to deposit the organic channel. Note that, as the partial pressure of the pentacene vapor was estimated to be around  $10^{-6}$  torr or smaller, the deposition pressure was actually close to the background pressure. Finally, a 100 nm-thick Au layer was deposited by evaporation at  $5 \times 10^{-6}$  torr in the same chamber to form S/D metal pads. Width of the devices is  $3 \mu m$ , while L is designed to be 0.4, 0.5, 0.6, 0.8, 1, or 2 μm. Cross-sectional scanning electron microscopy (SEM) was used to investigate the structure of OTFTs. The electrical properties of the OTFTs were measured by a B1500 semiconductor parameter analyzer in ambient air at room temperature.

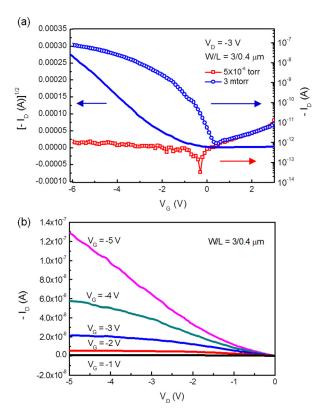

Fig. 2(a) shows the measured transfer characteristics of the fabricated OTFTs with channel width of 3  $\mu$ m and length of 0.4  $\mu$ m at drain voltage of -3 V. The two devices compared in this figure are with the pentacene channel deposited at background pressures of 3 mtorr and  $5 \times 10^{-6}$  torr, respectively. Clearly the background pressure during the deposition greatly affect the device performance: The one with the higher pressure shows the p-type switching behavior. In contrast, the other deposited with an ultra-low pressure fails to show any switching behavior and the drain current is solely contributed by the gate leakage. In Fig. 2(b), the output characteristics of the functional device are shown. From I-V characteristics, the saturation field-effect mobility ( $\mu_{\rm eff,\ sat}$ ), threshold voltage (V<sub>th</sub>), on/off current ratio, and

FIG. 2. (a) Transfer characteristics of two fabricated devices with different pentacene deposition pressures. (b) Output characteristics of the device with pentacene deposition pressure of 3 mtorr.

sub-threshold swing (S.S.) of the functional OTFT are estimated to be  $0.028 \text{ cm}^2 \text{ V}^{-1} \text{s}^{-1}$ , -1.41 V,  $2.4 \times 10^6$ , and 301 mV/dec, respectively.

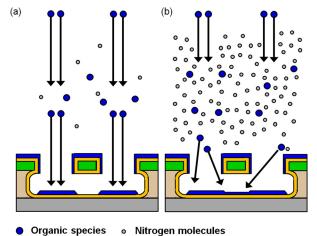

The above results reveal that the proper modification in the deposition pressure of the thermal evaporator is instrumental for the realization of the proposed FPE method. Figs. 3(a) and 3(b) are the schematic diagrams showing the scattering mechanisms during the evaporation of pentacene channel at the relatively low and high deposition pressures, respectively, in the thermal evaporator. In Fig. 3(a), the air is so scarce that the vaporized pentacene species transporting from the heated source to the substrate essentially encounter no scattering. As a result, the deposited pentacene is

Organic species o Millogen molecules

FIG. 3. Schematic diagrams showing the deposition of pentacene channel at (a) low and (b) high pressures by thermal evaporator.

shadowed by the suspended bridge and disconnected underneath the bridge. In Fig. 3(b), for the case with the deposition pressure increases to 3 mtorr, the density of nitrogen molecules in the air rises accordingly. Scattering rate of the evaporated pentacene species in the air is thus greatly promoted. The portion of the scattered pentacene species into the region underneath the bridge allows the formation of a continuous channel between the source and drain regions, as illustrated in Fig. 3(b).

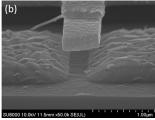

To gain more insight, we have employed SEM to check the deposited pentacene films. Figures 4(a) and 4(b) show the cross-sectional SEM images of two fabricated OTFTs with L of  $0.4 \, \mu \text{m}$ . The deposition pressures are 3 mtorr and  $5 \times 10^{-6}$  torr in Figs. 4(a) and 4(b), respectively. From the pictures, it is confirmed that the suspended poly-Si bridge serves as a shadow mask for tailoring the deposited thin films. Besides, it is clearly seen that, under the deposition pressure of 3 mtorr, an ultra-thin and continuous pentacene channel is formed beneath the suspended bridge. In contrast, no pentacene was deposited between the source and drain regions when the deposition pressure is reduced to  $5 \times 10^{-6}$  torr. The latter result well explain why the corresponding device does not show any turn-on behavior in Fig. 2(a).

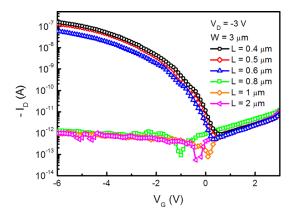

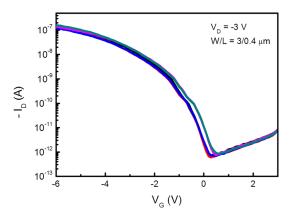

In order to understand more about the effects of the suspended bridge on the device fabrication and the resultant device performances, we have also characterized devices with various L with the pentacene channel deposited at 3 mtorr. The measured transfer characteristics, as shown in Fig. 5, can be divided into two groups which are relevant to their channel length. For devices with L of 0.6 µm or shorter, switching characteristics are obtained. The remaining devices with L of 0.8 µm or longer show no turn-on behavior with the drain current equals to the gate leakage, similar to the case shown in Fig. 2(a) with deposition pressure of  $5 \times 10^{-6}$  torr. Figure 6 shows the transfer characteristics of five devices with same L of  $0.4 \,\mu m$  located on different dies. The results confirm that the variation in device performance is small. The above observed trend indicates that a sufficiently long bridge would effectively prohibit the collided pentacene species from diffusing into the regions beneath the bridge for forming a continuous channel film and, as a result, the device fails because of the disconnected channel. The structure-dependent device characteristics highlight the important role of the length of the suspended bridge in the fabrication of FPE OTFTs. Value of the critical length is

FIG. 4. Cross-sectional SEM images of two fabricated OTFTs with L of 0.4  $\mu$ m. The deposition pressure is (a) 3 mtorr with an ultra-thin and continuous pentacene channel clearly formed beneath the suspended bridge and (b)  $5 \times 10^{-6}$  torr with no pentacene formed between the source and drain regions.

FIG. 5. Transfer characteristics of OTFTs with various channel lengths.

determined in large part by the deposition pressure and thickness of the sacrificial oxide.

Table I lists the major features of lithography tools and structural dimensions, as well as the characteristics of pentacene-based OTFTs obtained in this work together with those reported in Ref. 6. The comparison is made as the fabricated devices of the two studies are similar in structure with nominally identical channel dimensions. In this work, an I-line-based lithographic process was employed and the patterning involved the formation of a suspended bridge, as mentioned in the former section. In the previous work,<sup>6</sup> exposure of a three-layered resist with e-beam was done for forming a suspended resist structure. Note that in terms of the shape and role, the suspended resist structure is similar to the suspend hardmask bridge employed in this work. Overall, our proposed method without relying on e-beambased lithography is much more suitable for the large-area applications. As for the deposition approach of the channel film, we intentionally modify the deposition pressure of the thermal evaporator in a N<sub>2</sub> ambient, the process is thus simpler than the two-step oblique evaporation developed in the previous work. From the electrical parameters extracted with the transfer curves, it can be seen that the on/off ratio and subthreshold swing of our devices are much better while the saturation field-effect mobility is comparable as compared with those obtained in Ref. 6.

In our proposed method, the properly modified deposition pressure in the thermal evaporator is the most critical

FIG. 6. Transfer characteristics of five OTFTs distributed at different dies on the wafer with channel length of  $0.4\,\mu\mathrm{m}$  confirming small variation of the device performance.

TABLE I. Features and characteristics of pentacene-based OTFTs in this work, compared with Ref. 6.

|                                | This work              | Ref. 6               |

|--------------------------------|------------------------|----------------------|

| Suspended structure            | Etching undoped        | Exposing             |

| fabrication                    | poly-Si and TEOS oxide | three-layered resist |

| Lithography tool               | I-line stepper         | E-beam               |

| Channel deposition method      | Modified               | Two-step oblique     |

|                                | deposition pressure    | evaporation          |

| W/L (µm)                       | 3/0.4                  | 3/0.4                |

| Threshold voltage (V)          | -1.41                  | 0.0106               |

| Mobility (cm <sup>2</sup> /Vs) | 0.028                  | 0.029                |

| S.S. (V/decade)                | 0.301                  | 6.9                  |

| On/off ratio                   | $2.4 \times 10^{6}$    | $2.5 \times 10^{2}$  |

parameter for the realization of the FPE concept. A major concern for this method is the abundant nitrogen molecules contained in the chamber during the deposition process. Its major purpose is to increase the collision rates of the airborne organic molecules so that sufficient amount of flux reaching the channel center beneath the bridge can be attained. To further improve the performance of OTFTs, promoting the crystallinity of the channel film is feasible. This is achievable by performing a surface treatment on the gate dielectric to form self-assembled monolayers (SAM)<sup>11</sup> which provide an ordered template for subsequent channel film deposition. It is expected that the performance of FPE OTFTs will be improved considerably if the above SAM process procedure is implemented.

In short, we have investigated the feasibility of FPE method on the fabrication of pentacene-based OTFTs with submicron channel length. The deposition of pentacene channel was carried out in a  $N_2$  ambient of the thermal

evaporator. The results indicate that the background pressure during the deposition is vital and should be sufficiently high for the realization of FPE devices. Although the ultra-thin channel cannot be seen in the TEM images, functional devices are verified with the deposition pressure set at 3 mtorr. Another major parameter is the length of the suspended bridge which must be short enough to enable the formation of a continuous channel.

This work was sponsored in part by the Ministry of Science and Technology, Taiwan, under No. NSC-102-2221-E-009-097-MY3, and NCTU-UCB I-RiCE program, under No. MOST-103-2911-I- 009-302, and the Ministry of Education in Taiwan under ATU Program.

<sup>&</sup>lt;sup>1</sup>M. Kitamura and Y. Arakawa, J. Phys.: Condens. Matter **20**, 184011 (2008).

<sup>&</sup>lt;sup>2</sup>M. D. Austin and S. Y. Chou, Appl. Phys. Lett. **81**, 4431 (2002).

<sup>&</sup>lt;sup>3</sup>G. Horowitz, J. Mater. Res. **19**, 1946 (2004).

<sup>&</sup>lt;sup>4</sup>G. S. Tulevski, C. Nuckolls, A. Afzali, T. O. Graham, and C. R. Kagan, Appl. Phys. Lett. 89, 183101 (2006).

<sup>&</sup>lt;sup>5</sup>F. Ante, D. KälBlein, U. Zschieschang, T. W. Canzler, A. Werner, K. Takimiya, M. Ikeda, T. Sekitani, T. Someya, and H. Klauk, Small 7, 1186 (2011).

<sup>&</sup>lt;sup>6</sup>I. Yagi, K. Shigeto, K. Tsukagoshi, and Y. Aoyagi, Jpn. J. Appl. Phys., Part 1 44, L479 (2005).

<sup>&</sup>lt;sup>7</sup>B. A. Mattis, Y. Pei, and V. Subramanian, Appl. Phys. Lett. **86**, 033113 (2005)

<sup>&</sup>lt;sup>8</sup>C. Auner, U. Palfinger, H. Gold, J. Kraxner, A. Haase, T. Haber, M. Sezen, W. Grogger, G. Jakopic, J. R. Krenn, G. Leising, and H. Ota, Org. Electron. 10, 1466 (2009).

<sup>&</sup>lt;sup>9</sup>Y. Ishii, H. Sakai, and H. Murata, Nanotechnology 22, 205202 (2011).

<sup>&</sup>lt;sup>10</sup>H. C. Lin, R. J. Lyu, and T. Y. Huang, IEEE Electron Device Lett. 34, 1160 (2013).

<sup>&</sup>lt;sup>11</sup>B. C. Shekar, J. Lee, and S. W. Rhee, Korean J. Chem. Eng. 21, 267 (2004).