Fabricating Thin-Film Transistors on Plastic Substrates Using Spin Etching and Device Transfer

# Shuo-Cheng Wang,<sup>z</sup> Ching-Fa Yeh, Chung-Ti Hsu, and Jen-Chung Lou

Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan

This work presents a novel method for transferring thin-film transistors (TFTs) from a Si wafer to another flexible plastic substrate. First, high-performance poly-Si TFTs were fabricated on a 1.5  $\mu$ m thick SiO<sub>2</sub> on a Si wafer and then attached to a flexible plastic substrate by optical adhesive. Next, spin-etching was utilized to remove the backside Si, using SiO<sub>2</sub> as a stopping layer. A qualitative model was established to explain the relationship between the chemical flow rate/rotation speed to the etching rate and the uniformity of Si removal. The Si etching rate exceeded 200  $\mu$ m/min while the Si to SiO<sub>2</sub> selectivity of 250 was maintained given optimized spin-etching parameters. Substrate bonding and Si spin-etching steps caused no degradation or yield loss as compared to the electrical characteristics before transference. Additionally, extrinsic stress only weakly affected the properties of poly-Si resistors and TFTs on a flexible plastic substrate.

© 2005 The Electrochemical Society. [DOI: 10.1149/1.1860491] All rights reserved.

Manuscript submitted December 5, 2003; revised manuscript received September 14, 2004. Available electronically February 1, 2005

Thin-film transistors (TFTs) on flexible plastic substrates are of considerable interest because of several advantages including light weight, thinness, flexibility, shock resistance, and low cost. TFT devices are widely applied to large area electronics such as flat-panel display, "smart" labels on consumer items, smart cards, and sensors, while the small active matrix liquid-crystal display (AMLCD) with extremely high resolution is also in great demand for digital cameras and cellular phones.<sup>1-5</sup> However, the fabrication of high-performance TFTs on plastics is extremely challenging for the following reasons: first, the maximum process temperature must be lower than the glass transition temperature  $T_{\sigma}$  of plastic backplanes so that many conventional high-temperature processes such as oxidation, recrystallization, or activation must be modified. Second, because the thermal expansion coefficient of plastic substrate ( $6.2 \times 10^{-5/\circ}$ C) is much larger than that of Si  $(2.4 \times 10^{-6/\circ} \text{C})$ , film cracking or delaminating may occur. Dimensional instability of substrates also causes difficulties for fine pattering of the devices during photolithography process. Finally, issues of reproducibility and manufacturability on flexible substrates should also be addressed.

Two types of approaches have been considered to overcome these obstacles. One utilizes various low-temperature processes including excimer laser annealing, metal-induced lateral crystallization, plasma-enchanced chemical vapor deposition (PECVD), and sputtering, etc. to fabricate TFTs directly on plastic substrates.<sup>1,5</sup> The other method, indirectly, fabricates TFTs first on a glass or quartz substrate and then transferred the devices to the plastic sub-strate by etching or laser ablation.<sup>6,7</sup> The authors of this study have also proposed a novel technique of device transfer by backside etching (DTBE) which combines chemical-mechanical polishing (CMP) with wet chemical etching processes to fabricate TFTs on a rigid glass or plastic substrate.<sup>8</sup> Unlike the other methods, the DTBE technique relies on no expensive excimer laser equipment. Furthermore, because the starting material of the DTBE technique is a silicon wafer, its processes are fully compatible with mature complementary metal oxide semiconductor (CMOS) industry where maximum process temperature can be up to 1100°C. Although hightemperature poly-Si TFTs have been fabricated on quartz substrate for years, the extremely high cost of quartz (at least ten times higher than a Si wafer with the same size) limits its application and popularity.<sup>9,10</sup> Contrarily, utilizing DTBE technique, both highperformance integrated circuits and TFT arrays can be easily fabricated by conventional CMOS processes and then transferred from the Si wafer to the other low-melting-temperature substrates.

In this work, the CMP step in the previous DTBE method was

replaced by the spin-etching process. In contrast to CMP, the spinetching process exerts little mechanical stress or thermal stress on the sample, enabling the device to be transferred to a thin flexible backplane. Besides, spin etching consumes fewer chemicals than conventional wet etching; the fresh chemicals keep supplying to the sample during spin etching, so the etching rate is high and the throughput is comparable to conventional wet etching. This investigation examines the spin-etching properties, the mechanism of silicon etching and the electrical characteristics of transferred thin-film devices.

## Experimental

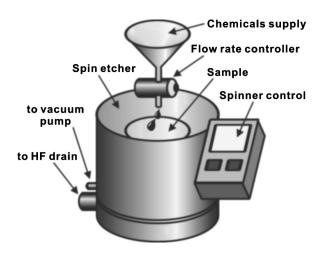

*Spin-etching process.*—Before the backside silicon are removed and the thin-film devices are transferred to a plastic substrate, the properties of the spin-etching process, including the etching rate, the uniformity and the selectivity, etc. should be clarified. Figure 1 schematically depicts the spin-etching equipment; the etching chemicals were dropped into the spinner through a manual valve in a funnel at an adjustable flow rate. The spinner was made of Teflon and was manufactured by Laurell Technologies Corp. A mixture of hydrofluoric acid (HF), nitric acid (HNO<sub>3</sub>), and some acetic acid (CH<sub>3</sub>COOH) was used as the main etchant for silicon. The spin speed of the samples varied from 1000 to 4000 rpm, while the flow rate of the etchant ranged from 100 to 333 mL/min.

The etching rate of silicon was calculated from the difference between the sheet resistance  $R_S$  of a 4 in. wafer before and after spin-etching process, *i.e.*, the change in wafer thickness can be expressed as

$$\Delta$$

thickness  $(T) = \rho/R_{\text{S-before}} - \rho/R_{\text{S-after}}$

where  $\rho$  is the resistivity of a Si wafer.

To test the etching selectivity of Si to silicon nitride or silicon dioxide, a layer of 2300 Å  $Si_3N_4$  or a 6000 Å thick  $SiO_2$  was formed on a Si substrate by LPCVD and wet oxidation, respectively. Both the etching selectivity and the etching uniformity were accurately measured using an ellipsometer.

Fabrication of thin-film devices.—In the DTBE process, both poly-Si resistors and TFTs were fabricated on the 4 in. wafers. First, a 1.5  $\mu$ m thermal oxide layer was grown on a Si substrate as an etching-stop layer against poly etchant. Then, a 1000 Å amorphous Si layer was deposited by LPCVD at 550°C and patterned to form an active region.<sup>11-13</sup> A 1000 Å thick TEOS-SiO<sub>2</sub> layer by PECVD and a 250 nm thick poly-Si layer by LPCVD at 620°C were then deposited as gate insulator and gate electrodes, respectively. Self-aligned phosphorous implantation at a dosage of 5 × 10<sup>15</sup> cm<sup>-2</sup> with an energy of 60 keV was carried out to generate the source/drain areas.

<sup>&</sup>lt;sup>z</sup> E-mail: scwang.ee88g@nctu.edu.tw

Figure 1. The schematic diagram of spin-etching equipment.

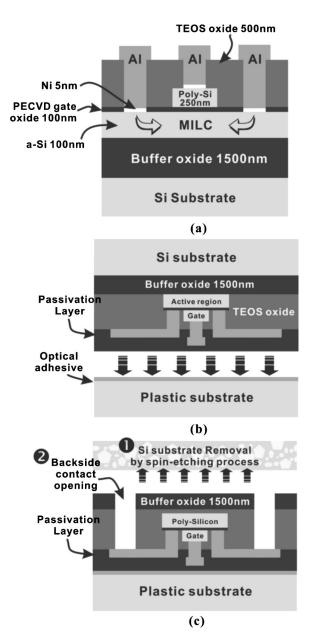

After the passivation oxide was deposited by PECVD and the contact holes were opened, a 5 nm Ni layer was evaporated onto the contact windows and then the samples were annealed at 550°C in a furnace for 48 h to recrystallize the channel region. Next, to further increase the grain size and active the dopants simultaneously, the samples were annealed in an N<sub>2</sub> ambient at 900°C for 1 h, resulting in the so-called "secondary crystallization" effect.<sup>13</sup> Afterward, the samples underwent a standard backend process to form the source/drain and gate metallization. Finally, a passivation process using NH<sub>3</sub> plasma was performed for 1 h.<sup>14</sup> The cross-sectional view of the finished TFT was shown in Fig. 2a. Before the thin-film devices were transferred to the plastic substrate, the electrical characteristics of the TFTs and poly-resistors were measured using Agilent 4156 semiconductor-parameter analyzer.

Device transfer process.—After the device characteristics were measured, a 3000 Å TEOS-oxide was deposited on the surface to protect the TFTs from damage by the organic adhesive. Next, as shown in Fig. 2b, the wafer (with devices on it) was bonded to a flexible plastic substrate with a thickness of 110  $\mu$ m by the optical adhesive and then cured at 80°C for 3 h on a hot plate. Afterward, spin-etching process with Si etchant was applied to remove the backside Si. As the thickness of the backside Si was reduced, the flexible plastic substrate tended to deform because it had a low Young's modulus. Accordingly, a supporting glass substrate had to be attached below the plastic substrate to prevent the samples from cracking during the etching process of backside silicon.

The spin etching step automatically stopped because the Si etchant has a high etching selectivity of 250 to the etching-stop layer,  $SiO_2$ . Finally, a photolithography process was performed to open the contact pads, as indicated in Fig. 2c. Again the electrical characteristics of TFTs or poly resistors were measured to examine the influence of DTBE.

### **Results and Discussion**

Spin etching process.—The etchants most commonly used in the isotropic etching of silicon are mixtures of hydrofluoric acid (HF), nitric acid (HNO<sub>3</sub>), and acetic acid (CH<sub>3</sub>COOH), the so-called HNA system<sup>15</sup> or poly etcher. The reaction is initiated by promoting Si from its initial state to a higher oxidation state

$$Si + 2h^+ \rightarrow Si^{2+}$$

The holes are produced by the following autocatalytic process

$$\begin{split} \mathrm{HNO}_3 \,+\, \mathrm{HNO}_2 &\rightarrow \, 2\mathrm{NO}_2^- \,+\, 2\mathrm{h}^+ \,+\, \mathrm{H_2O} \\ \\ 2\mathrm{NO}_2^- \,+\, 2\mathrm{H}^+ &\rightarrow \, 2 \ \ \mathrm{HNO}_2 \end{split}$$

Figure 2. The process flow of device transfer by backside etching (DTBE) technique.

$\rm Si^{2+}$  combines with  $\rm OH^-$  (from the dissociation of  $\rm H_2O)$  to yield Si(OH)\_2, which subsequently liberates  $\rm H_2$  to form SiO\_2. SiO\_2 then dissolves in HF

$$SiO_2 + 6HF \rightarrow H_2SiF_6 + H_2O$$

The overall reaction can be written as

$$Si + HNO_3 + 6HF \rightarrow H_2SiF_6 + HNO_2 + H_2O + H_2$$

Here, the acetic acid acts as a buffer agent, which controls the dissociation of the nitric acid and preserves the oxidizing power of  $HNO_3$  over a wide range of dilutions during etching.

The most serious problem encountered during backside etching concerns the process temperature. Because the thermal expansion coefficients of Si and the polymeric materials are significant, the plastic substrate easily rolls up and cause the Si to peel away from the plastic during the exothermic reaction of backside etching process. Moreover, several plastic substrates and adhesives are eroded

G228

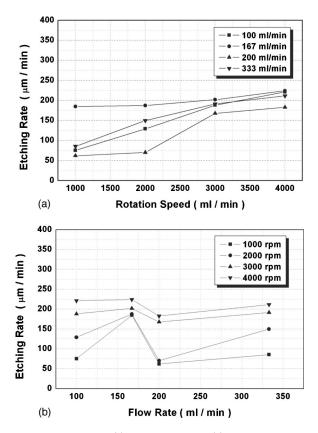

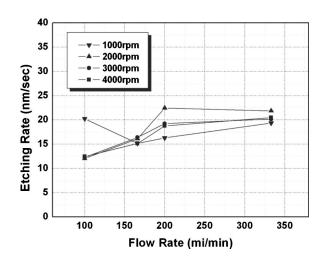

Figure 3. Etching rate vs. (a) rotation speed and (b) chemical flow rate.

by hydrofluoric or nitric acid, so the conventional wet etching cannot be applied to them. In spin etching, however, the sample is spun at a high speed, while the fresh cooling chemicals are supplied continuously to the wafer surface; accordingly, the influence of temperature is almost eliminated and the plastic substrate or adhesives are not damaged.

Figures 3a and b plots the curves of etching rate versus flow rate and rotation speed, respectively. Figure 3a reveals that the etching rate increases with the rotation speed, and that the maximum etching rate exceeds 200  $\mu$ m/min at the highest spin speed of 4000 rpm and a chemical flow rate of 167 mL/min. Consequently, spin etching is a very efficient process compared to conventional wet etching (~2  $\mu$ m/min at 25°C). Given a 4 in. wafer with a thickness of 550  $\mu$ m, the DTBE process can be completed in 3-5 min. Nevertheless, Fig. 3b shows no apparent relationship between the etching rate and the flow rate at a fixed spin speed. Specifically, the etching rate reaches a maximum at the flow rate of 167 mL/min and considerably declines above a flow rate of 200 mL/min.

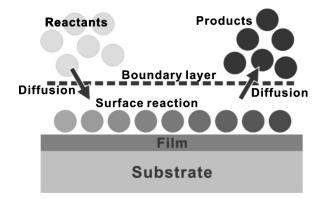

A simple mechanism of spin-etching process depicted in Fig. 4 is proposed to further explain the observed phenomenon. The etching procedure involves three steps: (*i*) First, a boundary layer is formed near the silicon surface where the etching species are rapidly consumed. All of the reactants diffuse through this boundary layer to support the reaction (mass transport control), (*ii*) then, reaction species at the surface, *e.g.*, HNO<sub>3</sub> and HF, will react with Si, in a process that depends strongly on the temperature (surface reaction control), and finally (*iii*) the reaction products diffuse through the boundary layer and return to the bulk of the liquid (product diffusion control).

In spin-etching, the spin speed mainly affects steps (i) and (iii), because a higher rotation speed yields a thinner boundary layer and thus a faster diffusion rate of both reactants and products. Accordingly, as shown in Fig. 3a, the etching rate keeps increasing with spin speed at every flow rate and gradually saturates when the rota-

Figure 4. The proposed mechanism of spin-etching process.

tion speed larger than 3000 rpm, implying that the system is then in the surface reaction control regime. In this regime, increasing the flow rate of etching chemicals may cool the surface of the sample and slightly change the reaction rate.

At a low rotation speed (<2000 rpm), however, the total process is more like a conventional wet etching rather than a spin etching. Without help from the centrifugal force, the reaction products near the silicon surface would now be repelled by the supplied chemicals so that the etching rate increases with the flow rate from 100 to 167 mL/min, as shown in Fig. 3b, indicating that the system is in the diffusion control regime. Moreover, the system leaves the diffusion control regime and enters the surface reaction control regime as the flow rate increases. The etching speed then decreases significantly owing to the cooling effect of chemicals.

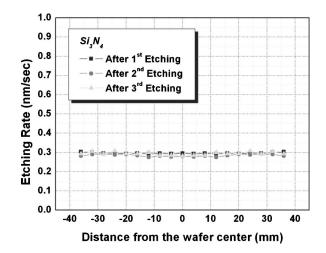

Figure 5 shows the etching rate with respect to the etching uniformity for  $Si_3N_4$ . A 4 in. wafer with a  $Si_3N_4$  layer of 2300 Å was spun and etched by the poly etchant for 360 s; every 120 s, the etching process was terminated and the film thickness of  $Si_3N_4$  was measured using an ellipsometer. The rotation speed was 4000 rpm and the flow rate was 100 mL/min. From Fig. 5, we find that not only was the etching repeatability was also satisfactory. (Data on the thickness of the film near the wafer edge could not be obtained using our equipment.) The etching selectivity of Si to  $Si_3N_4$  is larger than  $10^4$ , indicating that the silicon nitride formed by LPCVD is an ideal etching stop layer against poly etchant.

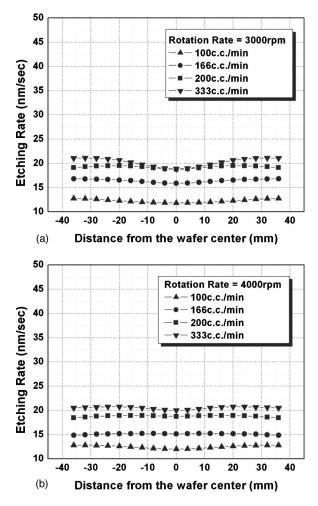

The etching characteristics of poly etchant for  $SiO_2$  were also investigated. As shown in Fig. 6, the etching rate increases with the flow rate, and gradually saturates at a flow rate above 200 mL/min.

Figure 5. The spin-etching uniformity of the silicon nitride film obtained by poly etchant.

Figure 6. The spin-etching rate of silicon dioxide versus chemical flow rates under different spin speed.

Because the relative concentration of hydrofluoric acid was low in our poly etchant and the hydrofluoric acid was consumed very quickly during etching, the etching mechanism is diffusioncontrolled and this mechanism depends on the chemical refresh rate. Additionally, the rotation speed negligibly influences to etching rate, except at 1000 rpm. It is notable that the etching rate greatly increases at the lowest flow rate (100 mL/min) and rotation speed. We presumed that the temperature at the surface had arisen, resulting in the increment of surface reaction rates. The etching selectivity of Si to SiO<sub>2</sub> is larger than 150. Although this value is inferior to that of silicon nitride, a thick SiO<sub>2</sub> stop layer with lower stress than Si<sub>3</sub>N<sub>4</sub> can be formed through wet oxidation and patterned easily with HF. Consequently, we chose SiO<sub>2</sub> rather than Si<sub>3</sub>N<sub>4</sub> as an etching stop layer in DTBE process.

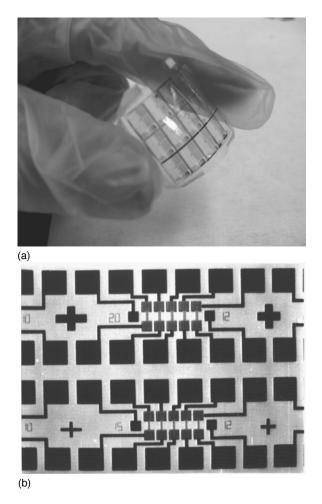

Figures 7a and b compare the etching uniformity for SiO<sub>2</sub> with different rotation speeds. From Fig. 7a, we can observe a U-shaped curve of etching uniformity, but the etching uniformity can be improved by increasing the rotation speed, as indicated in Fig. 7b. A similar phenomenon can also be found during backside Si etching. Figure 8 shows a photograph of devices after they were transferred to another plastic substrate by DTBE technique at a spin speed of 4000 rpm and a flow rate of 167 mL/min. The TFT arrays were originally fabricated on a 4 in. (10 cm diam) wafer. During spinetching, the etching rates near the wafer edge and that at the wafer center were higher than that in other areas, so the patterns that had been in these areas were destroyed by poly etchant even when a protecting oxide stop layer was present. Finally, the transferred devices formed a ring-shaped pattern with a diameter of 5 cm. To solve this problem of nonuniformity, the nozzle structure should be modified to spray the etchant more evenly to make the etching rates equal all over the wafer. Efforts to transfer larger samples using the DTBE technique are under way. In this work, we transferred TFTs or poly resistors from a  $4 \times 4$  cm chip of a Si wafer for a better yield of experiments.

*Fabricating of thin-film devices by DTBE.*—Because the devices were not directly fabricated on the plastic substrate using DTBE method, the characteristics of the plastic substrates were not strictly constrained. Nevertheless, the following properties for an optimal polymeric backplane are still required

1. The glass transition temperature  $T_g$  of a plastic substrate should exceed 130°C, because the samples after being transferred would undergo a photolithography process with a hard baking temperature of 120°C for the photoresist.

Figure 7. The spin-etching uniformity of silicon dioxide obtained at a spin speed of (a) 3000 rpm and (b) 4000 rpm.

Figure 8. A ring-shaped pattern with a diameter of 5 cm formed by DTBE.

Figure 9. (a) Photograph of several TFT arrays transferred to a flexible plastic substrate, and (b) photograph of optical microscopy observed with back light source.

2. The optimal polymeric backplane should have good chemical resistance, especially to HF,  $HNO_3$ , development (TMAH) and acetone (ACE).

3. It should have a low thermal expansion coefficient to ensure the accuracy of alignment during lithography process.

4. The substrate should have a high transparency and low reflectance for a transmission-type image display.

5. The substrate should have a low moisture absorption.

Many conventional plastic substrates including polyethersulfone (PES), polyarylate (PAR), polycarbonate (PC), and polyethylene terephthalate (PET) meet the above criteria, but we utilized a new kind of cyclic olefin polymers (COP) named ARTONfilm in this work.<sup>16</sup> ARTONfilm, purchased from JSR corp., possesses several advantages such as good light transmittance above 93%, high T<sub>g</sub> of 170°C, low water absorption and good adhesion to hard coatings, etc. Besides, the requirements for optical adhesives are similar to that for plastic substrate.

Figure 9a presents a flexible ARTON substrate on which the thin-film devices had been transferred successfully. The finished die size was  $3 \times 3$  cm. The optical microscope image of these devices observed with back light source is shown in Fig. 9b. The dark regions represent aluminum pads, poly-Si gates, and S/D electrodes, which are all opaque, while the white area is the transparent plastic substrate, adhesive, and SiO<sub>2</sub>. The backside Si had been thoroughly removed during spin-etching process and no physical damage was observed.

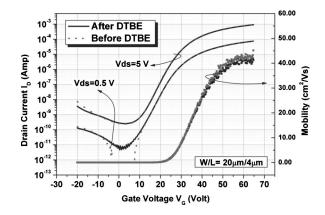

Figure 10.  $I_{\rm D}\text{-}V_{\rm G}$  curves and mobility curves of TFTs before and after DTBE process.

Electrical characteristics of thin-film devices after DTBE.—Figure 10 illustrates the  $I_D$ - $V_{GS}$  and field-effect mobility curves of a TFT before and after DTBE. Notably, the DTBE process does not degrade the electrical characteristics of TFTs, such as threshold voltage, mobility, ON/OFF current ratio and subthreshold swing. The field-effect mobility is 43 cm<sup>2</sup>/V s, as determined by<sup>17</sup>

$$\mu_{\rm FE} = \frac{L}{C_{\rm ox} \cdot W \cdot 0.1} \times g_{\rm m}$$

[1]

where *L* is the channel length, *W* is the channel width,  $C_{ox}$  is the gate oxide capacitance, and  $g_{\rm m}$  is transconductance. The ON/OFF current ratio is larger than 10<sup>6</sup> when the threshold voltage is around 10 V. The variation of electrical properties was not observed, especially the anomalous improvement of field-effect mobility and sub-threshold swing found in the author's previous work.<sup>8</sup> Here, the samples were all passivated by NH<sub>3</sub> plasma and the trap states in the grain boundary were not affected when the capping oxide layer was deposited.

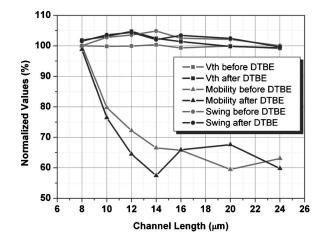

The electrical characteristics of devices on a bending substrate in a flexible display should not be degraded. Statistically, Fig. 11 summarized several key electrical properties of TFTs with different gate length (while gate width =  $20 \ \mu$ m) before and after transfer. Each data point was averaged by at least three devices and then normalized to the value of the gate length equal to 8  $\mu$ m. For example

Figure 11. Normalized electrical characteristics of TFTs after DTBE process versus channel length.

Figure 12. The testing base and probes for bending measurements.

Normalized mobility

$$\mu_{W/L=20/10}^{\text{norm}} = \frac{\mu_{W/L=20/10}}{\mu_{W/L=20/8}} \times 100\%$$

[2]

It can be found that both the threshold voltage and subthreshold swing exhibit no dependence on the channel length while the fieldeffect mobility decreases with increasing the gate length, because the efficiency of Ni-induced lateral recrystallization initiated at the source/drain contacts becomes poorer for a longer distance of silicide diffusion. The TFTs with short gate length thus occupy fewer defective grain boundaries and contribute to high field-effect mobility. Besides, for DTBE technique, the devices on a wafer underwent several bonding (annealing of the optical adhesive), etching and photolithography processes; accordingly, the electrical characteristics of TFTs would be influenced slightly by heat, organic contaminants, or moisture generated in these steps, resulting in a larger deviation of electrical characteristics than those before the transfer processes.

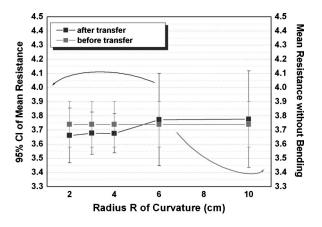

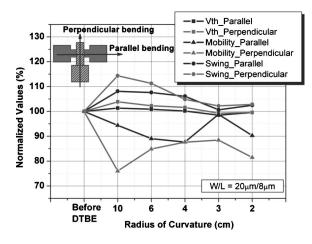

To examine the influence of mechanical stress on the device performance, several testing bases with various radii of curvature were made; the poly resistors or TFTs after transfer were fixed to the testing base and the electrical characteristics were measured, as shown in Fig. 12. Figure 13 plots the confidence interval (CI) of poly resistance in different bending cases. The average resistance dose not change after DTBE even at the smallest bending curvature of 2 cm, but the distribution of resistance is wider than those before transfer. Additionally, Fig. 14 illustrates the electrical properties of TFTs with W/L =  $20 \,\mu$ m/8  $\mu$ m under various radii of bending curvature, where parallel bending means that the direction of strain is

Figure 13. Resistance of poly resistors measured under different bending curvatures.

Figure 14. Comparison of electrical properties of TFTs before DTBE and that measured at various bending curvatures after DTBE.

parallel to the current path. And the devices under bending tests all suffer compressive stress since the TFTs after DTBE were upsidedown attached to the testing base. The experimental data are normalized to the value before DTBE. According to the research of Wagner et al., the mobility of amorphous Si TFTs would slightly decrease with increasing the compressive strain because of possible variation of optical bandgap of a-Si:H under compression.<sup>18</sup> Nevertheless, no significant correlation between the electrical properties of TFTs and different bending curvatures can be found in Fig. 14. We speculate that the elastic optical adhesive as well as thick etching stop/capping oxide layers may absorb the extrinsic stress during bending tests, and therefore the thin-film devices sandwiched between these layers suffer lower stress. Actually, when low modulus, small thickness substrate, and encapsulation are used, the thin-film approximation breaks down and the whole structure can be bent to extremely small radii, even being folded like a map.<sup>19,20</sup>

#### Conclusions

Fabricating high-performance thin-film transistors on plastics is extremely challenging. This work proposed an indirect process for transferring thin-film devices on a silicon wafer to another polymeric backplane. Spin-etching process was applied to overcome the issues about heat and mechanical stress resulted from CMP or conventional wet chemical etching. Moreover, the electrical characteristics of poly-Si resistors or TFTs are not changed after transfer process or the bending measurement, confirming that the device transfer technique with backside spin-etching process a practical means of fabricating thin-film devices on a flexible plastic substrate or fragile glass substrate. The DTBE technique is highly compatible with the conventional high-temperature CMOS process. If it could be combined with modern Ni-mediated crystallization or continuous grain silicon technology, the integration of a display and complex logic circuits on a plastic substrate can be expected in the near future.<sup>13,21</sup>

#### Acknowledgment

The authors thank their colleagues at Nano Facility Center in NCTU for their assistance in device fabrication. This work was supported by the National Science Council, Taiwan, R.O.C., under contract no. NSC92-2215-E-009-025

National Chiao-Tung University assisted in meeting the publication costs of this article.

#### References

- 1. P. G. Carey, P. M. Smith, S. D. Theiss, P. Wickboldt, T. W. Sigmon, Y. J. Tung, and

- T. J. King, in *Proceedings of IEEE LEOS'98*, IEEE, p. 126 (1998).

M. G. Kane, *Inf. Disp.*, 18, 12 (2002).

- 3. M. Luniak, in Proceedings of the First International IEEE Conference on Polymers

and Adhesives in Microelectronics and Photonics, IEEE, p. 314 (2001).

- 4. E. Lueder, R. Buerkle, M. Muecke, R. Klette, R. Bunz, and T. Kallfass, Inf. Disp., Lucad, R. Burke, M. Mater, R. Krete, R. Burk, and T. Kalmas, M. D. 7, 29 (1999).

C. E. Forbes, *SID Digest*, **2002**, 1200.

T. Shimoda and S. Inoue, *Tech. Dig. - Int. Electron Devices Meet.*, **1999**, 289.

A. Asano, *SID Digest*, **2002**, 1196.

- 8. S. C. Wang, C. F. Yeh, C. K. Huang, and Y. T. Dai, Jpn. J. Appl. Phys., Part 1, 42, L1044 (2003).

- F. Emoto, K. Senda, E. Fujii, A. Nakamura, A. Yamamoto, Y. Uemoto, and G. Kano, *IEEE Trans. Electron Devices*, **37**, 1462 (1990).

A. G. Lewis, I. W. Wu, T. Y. Huang, A. Chiang, and R. H. Bruce, *Tech. Dig. Int.*

- Electron Devices Meet., 1990, 843.

- H. Kim, J. G. Couillard, and D. G. Ast, *Appl. Phys. Lett.*, **72**, 803 (1998).

E. Ibok and S. Garg, *J. Electrochem. Soc.*, **140**, 2927 (1993).

- 13. H. Wang, M. Chan, S. Jagar, V. M. Poon, M. Qin, Y. Wang, and P. K. Ko, IEEE Trans. Electron Devices, 47, 1580 (2000).

- 14. C. M. Yu, H. C. Lin, T. Y. Huang, and T. F. Lei, J. Electrochem. Soc., 150, G843 (2003).

- 15. H. Robins, J. Electrochem. Soc., 108, 114 (1960).

- 16. http://www.jsr.co.jp

- 17. S. M. Sze, Physics of Semiconductor Devices, p. 441, Wiley, New York (1985).

- H. Gleskova, S. Wagner, W. Soboyejo, and Z. Suo, J. Appl. Phys., 92, 6224 (2002).

S. Wagner, H. Gleskova, P. H. Hsu, J. C. Sturm, and Z. Suo, in Proceedings of the

- Tenth International Display Workshops, SID, p. 303 (2003).

Z. Suo, E. Y. Ma, H. Gleskova, and S. Wagner, Appl. Phys. Lett., 74, 1177 (1999).

T. Mizuki, J. S. Matsuda, Y. Nakamura, J. Takagi, and T. Yoshida, IEEE Trans. Electron Devices, 51, 204 (2004).