# 0.13-μm RF CMOS and Varactors Performance Optimization by Multiple Gate Layouts

Chien-Chih Ho, Student Member, IEEE, Chin-Wei Kuo, Student Member, IEEE, Yi-Jen Chan, Senior Member, IEEE, Wan-Yih Lien, and J.-C. Guo

Abstract-0.13-\(\mu\)m radio frequency (RF) CMOS devices with multifinger gate structure have been fabricated by the standard logic process, and the measured effective gate-length is 80 nm. Extensive RF characterization has been done to obtain cutoff frequency  $(f_T)$ , associated power gain cutoff frequency  $(f_{\text{max}})$ , minimum noise figure  $(NF_{\min})$ , output power  $(P_{\mathrm{out}})$ , and power added efficiency (PAE) for RF circuit design and to explore the optimized gate layout in terms of the extracted RF device parameters. Our important finding to be reported in this paper is that an optimized unit finger width  $(W_F)$  exists by trade-off among  $f_T$ ,  $f_{

m max}, NF_{

m min}, P_{

m out}$  , and PAE. Under fixed total width to achieve the same current drivability  $\left(I_{ds}

ight)$ , the smaller  $W_F$  and the larger finger number  $(N_F)$  leads to higher  $f_{\max}$  but lower  $f_T$  due to trade-off between gate resistance  $(R_g)$  and parasitic gate capacity tance. As for  $NF_{\min}$  complicated by  $f_T$  and  $R_g$ , counter-balance between parasitic gate capacitance and  $R_g$  leads to nearly constant  $NF_{

m min}$  w.r.t. various splits of  $(W_F,N_F)$ . Regarding  $P_{

m out}$  and PAE,  $W_F$  of 4  $\mu$ m and  $N_F$  of 18 is the optimized layout parameter, which offers the maximum  $P_{\mathrm{out}}$  of around 11 dBm and PAE of 30.5% at 5.8 GHz. The performances of accumulation-mode MOS varactors with different gate layout structures are also investigated in this report. Since the same area varactors with different gate layout may result in different parasitic resistance and fringing capacitance, which will affect the capacitance tuning range and the associated Q-factor. The maximum Q-factor is about 59 of the 120  $\mu$ m<sup>2</sup> gate area varactor, and its tuning range is from 210 fF to 1.64 pF, where the maximum  $C_{

m m\,ax}/C_{

m m\,in}$  ratio is about 7.8.

Index Terms—0.13- $\mu$ m CMOS,  $NF_{\min}$ , RF power, varactor.

## I. INTRODUCTION

**B** Y SCALING down the CMOS gate dimension, it results in an improvement in the radio-frequency (RF) performance in terms of the RF noise and power characteristics [1], [2]. Due to the low-cost and high-integration benefits, where the low-power performance advantage in the baseband is well established, the CMOS technology has recently been recognized as a good candidate to realize the RF front-end circuits in the wireless communications. Recent works concerning the RF performance of CMOS devices have been released [3]–[6]. The performances such as current gain cutoff frequency  $(f_T)$ , associated power gain cutoff frequency  $(f_{max})$ , minimum

Manuscript received June 8, 2004; revised October 19, 2004. This work was supported by the Taiwan Semiconductor Manufacturing Company. The review of this paper was arranged by Editor S. Kimura.

Y.-J. Chan is with the Department of Electrical Engineering, National Central University, Chungli, Taiwan 32054, R.O.C. (e-mail: yjchan@ee.ncu.edu.tw).

C.-C. Ho, C.-W. Kuo, and W.-Y. Lien is with the Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan 300, R.O.C.

J.-C. Guo is with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan 300, R.O.C.

Digital Object Identifier 10.1109/TED.2004.839868

noise figure  $(NF_{\min})$ , and transconductance  $(g_m)$  have been improved greatly in parallel with a rapid technology evolution. However, by scaling down the CMOS device, the optimum layout of transistors for high frequency and low noise application becomes a critical issue, which is worthwhile for us to pay attention

The total gate-width of the FET-type device is the key factor to guarantee the amount of delivering RF output power. A multifinger structure with a small gate finger width is the most popular approach to reduce the input gate resistance, which results in a performance improvement as well as RF noise figure reduction. However, by further shrinking the gate finger width  $(W_F)$ , namely increasing the gate-finger number  $(N_F)$ , the layouts become the stripe-shape rather than the square-shape. This nonoptimized layout will introduce the additional parasitics from the lossy Si substrates, especially the parasitic capacitances, which will degrade the device microwave performance. In this report, we investigated four different types of CMOS devices with a drawn length of 0.13  $\mu$ m and varying  $W_F$  and  $N_F$  to keep the total gate-width constant, including  $2 \mu m \times 36$  fingers,  $4 \mu m \times 18$  fingers,  $6 \mu m \times 12$  fingers and 8  $\mu$ m × 9 fingers, respectively, by means of the device RF power and noise performance. By scaling down the CMOS gate dimension together with the advanced low-k and Cu metal technologies, recent published results in terms of RF performance demonstrated an  $f_T$  of 155 GHz and an  $f_{\text{max}}$ of 60 GHz [7]-[9]. In this work, the optimized gate layout MOSFET fabricated by 0.13-\(\mu\)m Copper logic process (w/o low-k dielectric) which considering the high frequency, power, and noise performance demonstrates the  $f_T$  of 104 GHz and  $f_{\rm max}$  of 68 GHz.

Besides the optimum layout transistors of the Si-based RF components, high-quality on-chip voltage-controlled capacitors (varactors) also play an important role in the integrated RF passive devices. Varactors can be used in the LC-tank voltage-controlled oscillators for providing a large tuning range of capacitance. Recently, the accumulation-mode MOS varactors have been proven to be superior to the reverse-biased p-n junction varactors in terms of power consumption, phase noise and tuning range in the voltage-controlled oscillators (VCOs) design [10], [11]. As to the technology scaling down, the thinner used gate oxide results in the capacitance increase. The capacitance tuning range can therefore be enhanced from the MOS varactors. However, the optimum layout of MOS varactors for achieving quality-factor (Q) and capacitance tuning range is worthwhile to be investigated. This report characterizes the performance of four different types MOS varactors with

| Width $(W_F) \times \text{finger}(N_F)$ | I <sub>ds</sub> (mA/mm)@                     | $g_{\mathrm{m}}$ | $f_T$ | f <sub>max</sub> |

|-----------------------------------------|----------------------------------------------|------------------|-------|------------------|

| $(\mu m)$                               | $V_{ds}=1.2 \text{ V}, V_{gs}=1.1 \text{ V}$ | (mS/mm)          | (GHz) | (GHz)            |

| 2×36                                    | 715                                          | 911              | 99    | 70               |

| 4×18                                    | 719                                          | 911              | 104   | 68               |

| 6×12                                    | 731                                          | 887              | 107   | 65               |

| 8×9                                     | 717                                          | 889              | 107   | 62               |

TABLE I MEASURED  $g_m$ ,  $f_T$ , and  $f_{\max}$  of the Total Device Width of 72- $\mu$ m Devices of These Four Different Gate Configuration

different gate finger length (L), width (W), branch numbers (B), and group numbers (G).

## II. EXPERIMENTAL MEASUREMENT SETUP

Effective gate-length of 80-nm nMOS devices used in this work were fabricated by using the foundry  $0.13-\mu m$  CMOS standard logic process with the Cu metal. The draw length for the typical devices on layout (not exactly equal to the mask size due to some pattern enhancement technique) is  $0.13 \mu m$ , and the exactly physical gate length is 80 nm after through the whole process flow, which was examined by the scanning electron microscope (SEM). The fabricated transistors were first characterized by dc I-V measurements. The S-parameters measurements were carried out up to 40 GHz by using the CAS-CADE on-wafer probes, an HP8510C network analyzer, and the dummy devices for the open and short calibration to eliminate the probe pads parasitic effects in Si substrates [12]. The RF noise figure and associated gain were obtained by using the ATN-NP5B noise parameter extraction system up to 10 GHz, which covers the most important frequency band for the wireless communication. The device power performance was measured by using the Maury load-pull system. The C-V curves of the MOS varactor were measured by an HP4284, and the Q-factor was extracted from the S-parameters by an HP8510C network analyzer.

## III. MOS DEVICE MICROWAVE CHARACTERISTICS

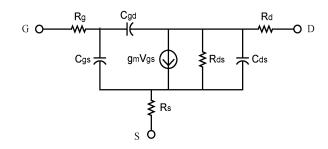

Dc and RF characteristics are listed in Table I for the  $0.13-\mu m$ RF nMOS with multifinger gate structure of four  $(W_F, N_F)$ splits. The dc peak transconductances  $(q_m s)$  are in the range of 890–910 mS/mm. The  $f_T$  increases from 99 to 107 GHz by increasing the  $W_F$  from 2  $\mu m$  to 8  $\mu m$  with a corresponding decrease of  $N_F$  from 36 to 9, which makes the total gate area constant. However, the  $f_{\rm max}$  demonstrates the opposite trend, namely decreasing from 70 to 62 GHz, corresponding to an increase of  $W_F$  and decrease of  $N_F$ . To investigate the mechanism responsible for the measured results, which may be related to the layout configurations, we analyzed the device measured S-parameters by extracting their small-signal equivalent circuit model. The parameters extraction method from [13] was adopted in this work. Fig. 1 shows the small-signal equivalent circuit model for the RF CMOS devices, and the extracted components from the S-parameters for the 0.13- $\mu$ m nMOS with four splits of gate layout are listed in Table II. The initial values of these components were directly obtained from some specific biasing points, such as at gate zero or peak  $q_m$  bias. The polycide gate finger is directly connected to the metal one layer by

Fig. 1. Small-signal equivalent circuit model of the 0.13- $\mu$ m gate-length MOSFET.

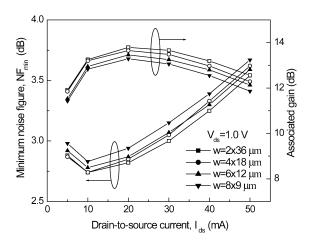

Fig. 2. Measured  $NF_{\min}$  and associated gain versus the drain current for these four different gate layout configuration of 0.13- $\mu$ m CMOS devices at 5.8 GHz.

the contacts on gate pads. Therefore, the extracted  $R_g$  from the measured S-parameters contains the resistance due to the gate fingers and pad contacts. However, our multifinger type gate design can significantly reduce the gate associated resistance. By decreasing  $W_F$  and increasing  $N_F$ , the total gate resistance  $(R_g)$  decreases systematically from 9.1  $\Omega$  for 8  $\mu$ m  $\times$  9 fingers to 5.2  $\Omega$  for 2  $\mu$ m  $\times$  36 fingers. However, in the meanwhile the gate associated parasitic capacitance  $(C_{gs}, C_{gd})$  increases with  $N_F$ , which introduces more parasitic gate capacitance associated with a stripe-shaped gate configuration. Since the  $f_T$  is proportional to  $g_m/2\pi(C_{gs}+C_{gd})$ , the higher parasitic capacitance in the 2  $\mu$ m  $\times$  36 gate configuration device results in a lower value of  $f_T$ . On the other hand, the  $f_{max}$  is strongly related to the input impedance, dominated by the  $R_g$ , and the lower  $R_g$  in the 2  $\mu$ m  $\times$  36 device accounts for the higher  $f_{max}$ .

Fig. 2 shows the  $NF_{\rm min}$  and the associated gain at 5.8 GHz versus drain current  $(I_{ds})$  for RF nMOS with the mentioned gate layout splits but without the intentional measurement

| TABLE II                                                                                                |

|---------------------------------------------------------------------------------------------------------|

| EXTRACTED SMALL-SIGNAL EQUIVALENT CIRCUIT COMPONENTS OF THESE FOUR DIFFERENT GATE CONFIGURATION DEVICES |

|                                                                                                         |

| Width $(W_F) \times \text{finger}(N_F)$ | Rg         | R <sub>d</sub> | Rs         | R <sub>ds</sub> | Cgs  | $C_{gd}$ | $C_{ds}$ |

|-----------------------------------------|------------|----------------|------------|-----------------|------|----------|----------|

| (µm)                                    | $(\Omega)$ | $(\Omega)$     | $(\Omega)$ | $(\Omega)$      | (fF) | (fF)     | (fF)     |

| 2×36                                    | 5.2        | 5.0            | 2.3        | 80              | 86   | 30       | 33       |

| 4×18                                    | 6.0        | 4.0            | 2.2        | 79              | 80   | 28       | 31       |

| 6×12                                    | 6.9        | 4.1            | 2.2        | 80              | 79   | 26       | 31       |

| 8×9                                     | 9.1        | 4.1            | 2.4        | 77              | 76   | 25       | 30       |

TABLE III

POWER PERFORMANCE OF THE TOTAL DEVICE WIDTH OF 72- $\mu$ m Devices of These Four Different Gate Configuration at 5.8-GHz Operation

| Width $(W_F) \times \text{finger}(N_F)$ | NF <sub>min</sub> (dB) | Gain | Pout  | Max. efficiency |

|-----------------------------------------|------------------------|------|-------|-----------------|

| (µm)                                    | @ 10 mA                | (dB) | (dBm) | (%)             |

| 2×36                                    | 2.74                   | 12.4 | 10.5  | 27              |

| 4×18                                    | 2.74                   | 13.2 | 10.9  | 31              |

| 6×12                                    | 2.78                   | 13.3 | 10.7  | 29              |

| 8×9                                     | 2.83                   | 12.6 | 10.4  | 26              |

de-embedding. The  $NF_{\min}$  can be characterized by the following equation [14]:

$$NF_{\min} = 1 + K \cdot \frac{f}{f_T} \sqrt{g_m \left(R_g + R_s\right)} \propto \sqrt{\frac{R_g + R_s}{g_m}}$$

(1)

where  $R_s$  is the source series resistance and K is the fitting parameter. The  $NF_{\min}$  systematically decreases by reducing the  $I_{ds}$ , reaching a minimum value at 10 mA. From the other point of view, a higher channel current in the device causes a higher noise level due to the increase of carrier random fluctuations. The increase of  $NF_{\min}$  below 10 mA is mainly associated with the gain reduction near the device threshold region. A slight gain reduction at high current level regime is consistent with the dc  $g_m$  gain profiles. As shown in Fig. 2, the device of 2  $\mu$ m  $\times$  36 fingers achieves the lowest  $NF_{\min}$  of 2.74 dB and highest associated gain of 13.79 dB, which is due to the lowest  $(R_q + R_s)$  resistance.

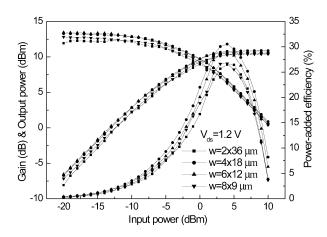

In brief, by decreasing  $W_F$  and increasing  $N_F$ , the RF CMOS exhibits better  $NF_{\min}$  performance. However, the device RF power performance does not demonstrate the same trend as that of  $NF_{\min}$ . Fig. 3 and Table III show the output power performance of the RF nMOS with total width of 72  $\mu$ m at 5.8 GHz. The devices were matched to obtain the maximum output power by the source and load tuners. The power performance is dependent not only on the gate resistance  $(R_q)$ , but also the parasitic capacitances quite significantly. As shown in Fig. 3, the 4  $\mu$ m × 18 fingers device reveals the highest output power  $(P_{\text{out}})$ , power gain and power added efficiency (PAE). Although the 2  $\mu$ m × 36 finger device achieves the lowest parasitic resistance contributing to the lowest  $NF_{\min}$ , the 4  $\mu$ m $\times$  18 finger device demonstrates the best power performance, where  $P_{\text{out}}$  is 10.9 dBm with a gain of 13.2 dB and PAE of 30.5% at 5.8 GHz. Again, gate associated parasitic capacitance is considered as the major factor to be traded off with  $R_q$ , and the gate layout of the multifinger structure is a tradeoff between RF noise and power performance. The stripe-shaped layout device achieves the best noise performance and the  $f_{\text{max}}$ ; however, it also introduces more parasitics which degrades the RF power characteristics. Therefore, for the RF CMOS with a total gate width of 72  $\mu$ m in this study, the

Fig. 3. Measured RF output power performance versus the input power for these four different gate layout configuration of 0.13- $\mu$ m CMOS devices at 5.8 GHz.

optimized gate layout in terms of  $f_T$ ,  $f_{\rm max}$ ,  $NF_{\rm min}$ ,  $P_{\rm out}$ , and PAE is 4  $\mu$ m × 18 fingers.

## IV. MOS VARACTOR MICROWAVE CHARACTERISTICS

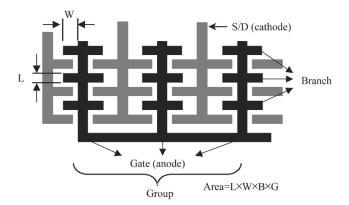

Fig. 4 shows the layout of the feather type MOS varactor. The goal in our MOS varactor design is to enlarge the capacitance density within a limited area, i.e., enhancing the  $C_{\rm max}$ value. Therefore, we use the feather type MOS varactor design instead of the traditional finger type MOS varactor design. The n<sup>+</sup>/n-well MOS varactors with a multifinger and feather structure gate were fabricated by using the  $0.13-\mu m$  CMOS technologies. The terminals of the source, drain, and bulk were shorted together. By biasing a positive voltage between the gate and the well, the device is accumulated, and the capacitance equals the gate oxide capacitance. By supplying a reversed bias, the device channel is depleted and the series capacitance decreased. The ratio of the  $C_{\text{max}}/C_{\text{min}}$  defines the varactor tuning range. The  $C_{\rm ox}(C_{\rm max})$  increases as the oxide thickness scales down, where the scaled technology provides a wider tuning range. To achieve the optimum layout in terms of the Q-factor and capacitance ratio, we varied the gate finger length, width, group numbers and branch numbers to keep the total gate area constant of 120  $\mu$ m<sup>2</sup>, including 0.25  $\mu$ m × 1  $\mu$ m × 120 × 4 (type

| Area $(L \times W \times B \times G)$        | Capacitance tuning | C <sub>max</sub> /C <sub>min</sub> | Parasitic resistance | Q-factor |

|----------------------------------------------|--------------------|------------------------------------|----------------------|----------|

|                                              | range (pF)         | ratio                              | (ohm) @ -1.0 V       | @ -1.0 V |

| Type A $(0.25 \times 1 \times 120 \times 4)$ | 0.38~1.53          | 4.0                                | 7.5                  | 53       |

| Type B $(0.5 \times 1 \times 60 \times 4)$   | 0.28~1.57          | 5.6                                | 6.8                  | 54       |

| Type C $(0.5 \times 2 \times 60 \times 2)$   | 0.26~1.59          | 6.1                                | 6.4                  | 55       |

| Type D $(1 \times 2 \times 30 \times 2)$     | 0.21~1.64          | 7.8                                | 5.7                  | 59       |

TABLE IV MEASURED CAPACITANCE, Q-FACTOR, AND PARASITIC SERIES RESISTANCE OF THE DIFFERENT GATE LAYOUT STRUCTURE MOS VARACTORS WITH A GATE BIAS AT  $-1.0~\rm V$

Fig. 4. Layout of the MOS varactor with the multifinger structure gate.

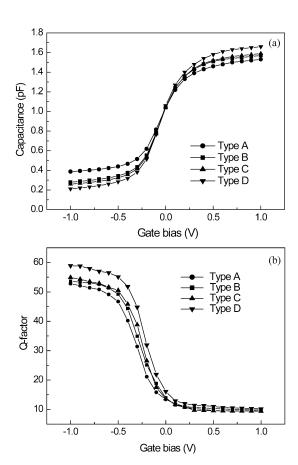

A),  $0.5 \mu m \times 1 \mu m \times 60 \times 4$  (type B),  $0.5 \mu m \times 2 \mu m \times 60 \times 2$ (type C) and  $1 \mu m \times 2 \mu m \times 30 \times 2$  (type D), respectively. The range of gate bias voltage was from -1.0 V to 1.0 V. Since the same area varactors with different layout (L, W, G, B) have different fringing capacitance and parasitic resistance, the capacitance and Q-factor will be different for the same gate area varactors with different layout structures. Fig. 5 shows the measured capacitances and Q-factors of these four types of varactors at 2.4 GHz. As shown in Table IV, the capacitance tuning range of type A structure with higher group (G) and branch (B)numbers is the lowest among other types, and the maximum Q-factor is 53. From the parameter-extraction method in [15], the main series parasitic resistance and capacitance values of the varactor are shown in Table IV. The type A varactor, due to the  $L=0.25~\mu\mathrm{m}$  and the stripe-shaped layout configuration, introduces more parasitic series resistance and the fringing capacitance, respectively. It therefore results in a low Q-factor and a low capacitance tuning range. As to the type D varactor, where the L is 1  $\mu$ m and the layout is more square-shaped, the Q-factor and the capacitance tuning range can be enhanced simultaneously. The maximum Q-factor of 59 with a tuning range ratio of 7.8 is achieved in the type-D varactor.

This 0.13- $\mu m$  feather type MOS varactor, shown in Fig. 4, has a higher parasitic resistance, ranging between 5.7 to 7.5  $\Omega$ , which limits the Q-values even though using this advanced device technology. The Q-values in the  $C_{\rm max}$  region are generally lower than the finger type varactors, which is due to the enhanced capacitance and a higher parasitic resistance, i.e.,  $Q \sim (RC)^{-1}$ . The change of parasitic resistance between  $C_{\rm max}$  and  $C_{\rm min}$  is small. The layout consideration in varactor design is similar to the conclusions obtained from the nMOS investigation, i.e., stripe-shaped configuration introducing more parasitics.

Fig. 5. (a) Measured capacitance of the MOS varactors with different gate layout structure. (b) Measured Q-factor of the MOS varactors with different gate layout structure at 2.4 GHz.

# V. CONCLUSIONS

In this work, high-frequency power and noise characterization has been done on 0.13- $\mu$ m nMOS to investigate the optimized gate layout in terms of the extracted RF performance parameters  $f_T$ ,  $f_{\rm max}$ ,  $NF_{\rm min}$ ,  $P_{\rm out}$ , and PAE. The tradeoff among all the parameters is strongly related with the associated parasitic gate resistance  $(R_g)$  and capacitances  $(C_{gs}, C_{gd})$ . For this study, the gate layout of 4  $\mu$ m  $\times$  18 fingers is identified as the optimum design in terms of  $f_T$ ,  $f_{\rm max}$  and  $NF_{\rm min}$ ,  $P_{\rm out}$ , PAE at 5.8 GHz. In the varactor gate layout structure design, for the purpose of providing larger capacitance tuning range and Q-factor, the gate layout should consider more on the parasitic resistance and the capacitance, where the stripe-shaped layout is not suitable in this regard.

#### ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratories (NDL) for the noise figure measurement.

#### REFERENCES

- [1] E. Morifuji, H. S. Momose, T. Ohguro, T. Yoshitomi, H. Kimijima, F. Matsuoka, M. Kinugawa, Y. Katsumata, and H. Iwai, "Future perspective and scaling down roadmap for RF CMOS," in *Dig. Tech. Papers VLSI Symp.*, 1999, pp. 163–164.

- [2] Y. H. Wu, A. Chin, C. S. Liang, and C. C. Wu, "The performance limiting factors as RF MOSFETs scaling down," in *Proc. RF-IC Symp.*, 2000, pp. 151–155.

- [3] C. H. Huang, C. H. Lai, J. C. Hsieh, J. Liu, and A. Chin, "RF noise in 0.18-\(\mu\)m and 0.13-\(\mu\)m MOSFETs," IEEE Microwave Wireless Components Lett., vol. 12, pp. 464–466, 2002.

- [4] P. H. Woerlee, M. J. Knitel, R. V. Langevelde, D. B. M. Klaassen, L. F. Tiemeijer, A. J. Scholten, and A. T. A. Z. Duijnhoven, "RF CMOS performance trends," *IEEE Trans. Electron Devices*, vol. 48, pp. 1776–1782, Aug. 2001.

- [5] C. S. Kim, H. K. Yu, H. Cho, S. Lee, and K. S. Nam, "CMOS layout and bias optimization for RF IC design applications," in *IEEE MTT-S Dig.*, 1997, pp. 945–948.

- [6] J. N. Burghartz, M. Hargrove, C. S. Webster, R. A. Groves, M. Keene, K. A. Jenkins, R. Logan, and E. Nowak, "RF potential of a 0.18-μm CMOS logic device technology," *IEEE Trans. Electron Devices*, vol. 47, pp. 864–870, Apr. 2000.

- [7] H. Yoshimura et al., "A CMOS technology platform for 0.13 μm generation SOC," in Dig. Tech. Papers VLSI Symp., 2000, pp. 144–145.

- [8] T. Schiml et al., "A 0.13 μm CMOS platform with Cu/low-k interconnects for system on chip applications," in Dig. Tech. Papers VLSI Symp., 2001, pp. 101–102.

- [9] T. Schafbauer et al., "Integration of high-performance, low-leakage and mixed signal features into a 100 nm CMOS technology," in Dig. Tech. Papers VLSI Symp., 2002, pp. 62–63.

- [10] F. Svelto, P. Erratico, S. Manzini, and R. Castello, "A metal-oxide-semi-conductor varactor," *IEEE Electron Device Lett.*, vol. 20, pp. 164–166, Jan. 1999.

- [11] P. Andreani and S. Mattisson, "On the use of MOS varactors in RF VCOs," *IEEE J. Solid-State Circuits*, vol. 35, pp. 905–910, June 2000.

- [12] H. Cho and D. Burk, "A three-step method for the de-embedding of high frequency S-parameter measurements," *IEEE Trans. Electron Devices*, vol. 38, pp. 1371–1375, June 1991.

- [13] S. H. Jen, C. C. Enz, D. R. Pehlke, M. Schroter, and B. J. Sheu, "Accurate modeling and parameter extraction for MOS transistors valid up to 10-GHz," *IEEE Trans. Electron Devices*, vol. 46, pp. 2217–2227, Nov. 1999.

- [14] H. Fujui, "Optimal noise figure of microwave GaAs MESFETs," *IEEE Trans. Electron Devices*, vol. ED-26, pp. 1032–1037, 1979.

- [15] S. S. Song and H. Shin, "A new RF model for the accumulation-mode MOS varactor," in *IEEE MTT-S Dig.*, 2003, pp. 1023–1026.

Chien-Chih Ho (S'04) was born in Taipei, Taiwan, R.O.C., in 1977. He received the B.S. and Ph.D. degrees from the Department of Electrical Engineering, National Central University, Chungli, Taiwan, in 1998, and 2004, respectively.

He joined Taiwan Semiconductor Manufacturing Company Ltd. (TSMC), Hsinchu, Taiwan, in 2004, working in the areas of CMOS microwave integrated circuit design and characterization.

Chin-Wei Kuo (S'04) was born in Keelung, Taiwan, R.O.C., in 1976. He received the B.S. and Ph.D. degrees from the Department of Electrical Engineering, National Central University, Chungli, Taiwan, in 1997 and 2003, respectively.

He joined Taiwan Semiconductor Manufacturing Company Ltd. (TSMC), Hsinchu, Taiwan, in 2003, working in the areas of CMOS device modeling and RF characterization.

Yi-Jen Chan (M'92–SM'01) received the B.S.E.E. degree from National Cheng Kung University, Tainan, Taiwan, R.O.C., the M.S.E.E. degree from National Tsing Hua University, Hsinchu, Taiwan, and the Ph.D. degree in electrical engineering and computer science from the University of Michigan, Ann Arbor, in 1982, 1984, and 1992 respectively.

He is currently with the Department of Electrical Engineering, National Central University, Chungli, Taiwan. His current research interests include submicron device technology, microwave devices and

integrated circuits, and optoelectronic integrated circuits.

**Wan-Yih Lien** was born in Taiwan, R.O.C., in 1963. He received the Ph.D. degree in power mechanical engineering from National Tsing-Hua University, Hsinchu, Taiwan, in 1995.

He joined the Logic Technology Division, Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu, in 1995. He has done extensive research in DRAM, mixed-signal and RF processes of CMOS technology, and three-dimensional electromagnetic simulation on RF passive components.

**J.-C. Guo** received the B.S.E.E. and M.S.E.E. degrees from National Tsing-Hua University (NTHU), Taiwan, R.O.C., in 1982 and 1984, respectively, and the Ph.D. degree in electronics engineering from the National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1994.

Previously, she was working in the semiconductor industry with focus on device design and VLSI technology development for around 19 years. In 1984, she joined the ERSO/ITRI, where she was engaged in semiconductor integrated circuit technologies with

broad scope to cover the high-voltage, high-power, submicron project, and high-speed SRAM technologies, etc. From 1994 to 1998, she was with Macronix International Corporation, where she was engaged in high-density and low-power flash memory technology development. In 1998, she joined Vanguard International Semiconductor Corporation, where she served as a Department Manager, responsible for advanced DRAM device technology development. In 2000, she joined Taiwan Semiconductor Manufacturing Company (TSMC), Hsinchu, where she served as a Program Manager in charge of 0.1-µm logic CMOS FEOL, high-performance-analog and RF CMOS technology development. She joined NCTUs Electrical Engineering faculty in 2003. Her current research interests cover RF CMOS and high-performance analog device design and modeling, novel nonvolatile memory technology, and circuit technology, and circuit technology for SOC. She has authored or co-authored more than 30 technical papers and has been granted 12 international patents in her professional field.