# HfO<sub>2</sub> MIS Capacitor with Copper Gate Electrode

Tsu-Hsiu Perng, Chao-Hsin Chien, Ching-Wei Chen, *Student Member, IEEE*, Ming-Jui Yang, Peer Lehnen, Chun-Yen Chang, *Fellow, IEEE*, and Tiao-Yuan Huang, *Fellow, IEEE*

Abstract—Metal-insulator-semiconductor capacitors fabricated using atomic vapor deposition HfO2 dielectric with sputtered copper (Cu) and aluminum (Al) gate electrodes. The counterparts with SiO<sub>2</sub> dielectric were also fabricated for comparison. Bias-temperature stress and charge-to-breakdown  $(Q_{

m BD})$ test were conducted to examine the stability and reliability of these capacitors. In contrast with the high Cu drift rate in an SiO<sub>2</sub> dielectric, Cu in contact with HfO<sub>2</sub> seems to be very stable. The HfO<sub>2</sub> capacitors with a Cu-gate also depict higher capacitance without showing any reliability degradation, compared to the Al-gate counterparts. These results indicate that HfO2 with its considerably high density of 9.68 g/cm<sup>3</sup> is acting as a good barrier to Cu diffusion, and it thus appears feasible to integrate Cu metal with the post-gate-dielectric ultralarge-scale integration manufacturing processes.

*Index Terms*—Bias-temperature stress, copper-gate (Cu-gate) electrode, hafnium dioxide (HfO).

## I. INTRODUCTION

HEN the gate length of MOSFETs is scaled down to a 0.1- $\mu$ m regime with the corresponding gate oxide thickness thinner than 3 nm, some major problems arise in realizing high-performance ultralarge-scale integration (ULSI) circuits. Specifically, device performance and reliability can be seriously degraded by the intolerably high direct-tunneling leakage current, increased gate resistance, worsened polysilicon gate depletion, and boron penetration [1], [2]. To alleviate these problems, a high dielectric constant (high- $\kappa$ ) gate insulator and metal gate have been proposed to meet the stringent performance requirement [3], [4]. Various high- $\kappa$  dielectric materials, such as Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub>, have been extensively studied [4]–[8]. Among these dielectrics, HfO<sub>2</sub> is very promising for the next-generation gate dielectric of MOSFETs, because of its high dielectric constant, excellent thermal stability, and large band gap, etc. [9], [10].

Recently, Cu has successfully replaced the conventional aluminum alloys as the interconnect metal in the advanced ULSI manufacturing, due to its superior conductivity and better electromigration resistance. Despite its success as the metal inter-

Manuscript received August 12, 2004; revised October 5, 2004. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract 93A0500001. The review of this letter was arranged by Editor A Chatteriee.

T.-H. Perng, C.-W. Chen, C.-Y. Chang, and T.-Y. Huang are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

C.-H. Chien and M.-J. Yang are with the National Nano Device Laboratories, Hsinchu 30050, Taiwan, R.O.C. (e-mail: chchien@ndl.gov.tw).

M.-J. Yang is with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C., and also with National Nano Device Laboratories, Hsinchu 30050, Taiwan, R.O.C.

P. Lehnen is with AIXTRON AG, Aachen 52072, Germany. Digital Object Identifier 10.1109/LED.2004.839221

connect of choice, Cu has still not gained acceptance as the gate electrode of the transistor because the positively charged Cu ions are known to drift very rapidly in thermal oxide under the influence of electric field, and can cause severe reliability degradation in oxide [11].

For the high- $\kappa$  dielectrics, replacing the conventional polysilicon gate electrode with metal gate has been proposed because of the interface instability between the high- $\kappa$  dielectrics and polysilicon gate [10], [12]–[14]. However, Cu has never been under consideration, to the best of our knowledge, mainly because of the concern of the rapid Cu ion drift in the dielectric as mentioned above. In this letter, Cu was used for the first time as the metal gate electrode directly on top of a high- $\kappa$  dielectric, i.e., HfO<sub>2</sub>. Based on the results from the bias-temperature stress (BTS) and charge-to-breakdown ( $Q_{\rm BD}$ ) measurement, the HfO<sub>2</sub>-based Cu-gate capacitors show not only enhanced capacitance but also no noticeable reliability degradation compared to Al-gate counterparts. Our results strongly suggest the feasibility of a full Cu process from the gate electrode to the back-end-of-line (BEOL) in future ULSI fabrication.

#### II. EXPERIMENTAL

Standard 6-in (100) p-type Si wafers, with resistivity of 15–25  $\Omega$ -cm, were used in this study. Following a standard RCA cleaning process, a layer of 10-nm-thick HfO<sub>2</sub> using tetrakis diethylamido hafnium precursor was deposited by atomic vapor deposition (AVD) on an AIXTRON Tricent system at a substrate temperature of 400 °C in oxygen ambient. Wafers were subsequently split into two groups. We sputtered 500-nm-thick Cu through a metal mask as the gate electrode for one group, with 500-nm-thick Al for the control group. Finally, all wafers received a 500-nm-thick Al deposition on the wafer backside. The device area is  $1.7 \times 10^{-4}$  cm<sup>2</sup>. It is worth noting that control wafers with 10-nm-thick SiO<sub>2</sub> dielectric were also fabricated in this study for comparison. The current-voltage characteristics were measured using a Keithley Model 4200-SCS semiconductor characterization system, and the capacitance was measured using an Agilent 4284A precision LCR meter at a frequency of 100 kHz. Constant current stress (CCS) was conducted for evaluating reliability. In order to investigate the thermal stability of HfO<sub>2</sub> film with Cu electrode, an effective electric field of +1 MV/cm at elevated temperatures ranging from 100 °C to 200 °C was applied to the gate stacks for BTS testing.

## III. RESULTS AND DISCUSSIONS

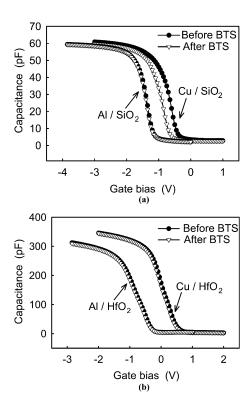

Fig. 1(a) displays typical capacitance–voltage (C-V) characteristics of Cu–SiO<sub>2</sub>-Si and Al–SiO<sub>2</sub>-Si capacitors, both before and after BTS test, at 150 °C for 1000 s. The applied

Fig. 1. C-V curves of (a) Cu–SiO<sub>2</sub>–Si and Al–SiO<sub>2</sub>–Si capacitors and (b) Cu–HfO<sub>2</sub>–Si and Al–HfO<sub>2</sub>–Si capacitors before and after BTS at 150  $^{\circ}$ C for 1000 s. The applied field was +1 MV/cm.

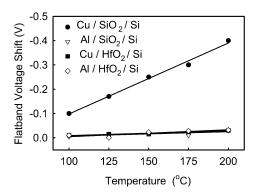

field was +1 MV/cm. A significant negative flatband voltage  $(V_{\rm FB})$  shift of about  $-0.4~{\rm V}$  is observed for the Cu–SiO<sub>2</sub>–Si capacitor, indicating that positively bulk charges (i.e., Cu ions) are introduced into the dielectric [15]. In contrast, only negligible  $V_{\rm FB}$  shift is found for the Al-SiO<sub>2</sub>-Si capacitors after BTS test. It is well known that Al is quite stable in contact with SiO<sub>2</sub>. This is because a very thin self-limiting Al<sub>2</sub>O<sub>3</sub> layer is formed between the Al electrode and SiO<sub>2</sub>, and acts as a good diffusion barrier for further element diffusion and/or reaction [16]. Fig. 1(b) exhibits the C-V characteristics of Cu-HfO<sub>2</sub>-Si and Al-HfO<sub>2</sub>-Si capacitors before and after BTS test at +1 MV/cm, 150 °C for 1000 s. Quite amazingly, there is essentially no  $V_{\rm FB}$  shift observed after BTS. Although a slightly larger  $V_{\rm FB}$  value was observed for Cu-HfO<sub>2</sub>-Si capacitor, the corresponding work function (4.9 eV) still fell into the required window for p-channel devices. This result indicates that HfO<sub>2</sub> is electrically stable with Cu gate electrode. It is speculated that the stability is due to the considerably high density of HfO<sub>2</sub>  $(9.68 \text{ g/cm}^3)$  [17], which is more than two times that of Al<sub>2</sub>O<sub>3</sub> (3.97 g/cm<sup>3</sup>). As a result, HfO<sub>2</sub> serves not only as a promising gate dielectric but also an excellent barrier against Cu diffusion, even though the density data quoted above are for bulk materials rather than thin films. Fig. 2 depicts  $V_{\rm FB}$  shifts of Cu–HfO<sub>2</sub>-Si, Al-HfO2-Si, Cu-SiO2-Si, and Al-SiO2-Si capacitors as a function of temperature ranging from 100 to 200 °C after BTS test. The BTS stress was performed at +1 MV/cm for 1000 s. Clearly,  $V_{\rm FB}$  shifts are negligible except for the Cu–SiO<sub>2</sub>–Si capacitors. These results imply that HfO2 can effectively block Cu ion drift at least up to 200 °C.

Fig. 2.  $V_{\rm FB}$  shifts of Cu–SiO<sub>2</sub>–Si, Al–SiO<sub>2</sub>–Si, Cu–HfO<sub>2</sub>–Si, and Al–HfO<sub>2</sub>–Si capacitors after BTS test at +1 MV/cm for 1000 s. The temperatures were varied from 100 °C to 200 °C.

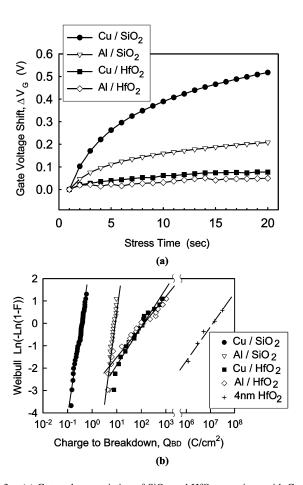

Fig. 3. (a) Gate voltage variation of  $SiO_2$  and  $HfO_2$  capacitors with Cu and Al gate electrodes subjected to CCS as a function of time; (b) cumulative  $Q_{\rm BD}$  plots of Cu–HfO<sub>2</sub>–Si, Al–HfO<sub>2</sub>–Si, Cu–SiO<sub>2</sub>–Si, and Al–SiO<sub>2</sub>–Si capacitors.

Fig. 3(a) shows the gate voltage variation as a function of time for the  ${\rm SiO_2}$  and  ${\rm HfO_2}$  capacitors with different gate electrodes, when subjected to CCS. The stressing current used was  $-1~{\rm mA/cm^2}$ . The reason why we used such low current density for stressing is owing to the fact that the  $Q_{\rm BD}$  is extremely hard to be monitored under the condition of  $-100~{\rm mA/cm^2}$  for the Cu–SiO<sub>2</sub>–Si capacitors when Cu was incorporated. In the case of SiO<sub>2</sub> capacitors, a larger voltage shift observed in the Cu-gate capacitor, compared to the Al-gate counterpart, implies

the incorporation of Cu ions into SiO<sub>2</sub> dielectric during BTS test does result in higher electron trapping rate. By contrast, different metal gates (i.e., Al and Cu) only lead to indiscernible change in gate voltage shift during CCS for the HfO<sub>2</sub>-based capacitors. These results suggest that the SiO<sub>2</sub> dielectric is more vulnerable than HfO2 to Cu diffusion. As a result, the SiO2 capacitors will breakdown more easily when Cu is employed as the gate electrode. Fig. 3(b) shows the Weibull distributions of the charge-to-breakdown  $(Q_{BD})$  for all four capacitor configurations. Consistent with the results in Fig. 3(a), the value of 63%  $Q_{\rm BD}$  for the Cu-gate SiO<sub>2</sub> capacitors is more than one order of magnitude lower than that for the Al-gate SiO<sub>2</sub> capacitors. This severe reliability degradation is the main reason why Cu is excluded from the conventional FEOL processes of silicon-based ULSI manufacturing. However, our finding strongly indicates that this is no longer an issue for the HfO<sub>2</sub> dielectric. From the cumulative  $Q_{\rm BD}$  plots of HfO<sub>2</sub> capacitors with the Cu and Al gate electrodes, no significant difference is observed between the two groups, indicating that Cu diffusion has only negligible effects on the reliability of HfO2-based capacitors. No degradation was observed even though 4-nm-thick HfO<sub>2</sub> was used in Cu–HfO<sub>2</sub>–Si capacitor, as shown in Fig. 3(b) [18].

## IV. CONCLUSIONS

AVD-deposited HfO<sub>2</sub> capacitors using Cu and Al as the gate electrode have been fabricated and investigated for the first time. The counterparts with thermally grown SiO<sub>2</sub> dielectric were also constructed for comparison. Our results clearly show that HfO<sub>2</sub> dielectric depicts superior resistance against Cu diffusion after BTS test, compared to SiO<sub>2</sub>. Moreover, the presence of Cu metal in direct contact with HfO<sub>2</sub> has negligible impact on the reliability of the HfO<sub>2</sub> capacitor. The fact that HfO<sub>2</sub> can behave as a good barrier against Cu diffusion is attributed to its considerably high density. This finding is important as it suggests the feasibility of a Cu integration process from the p-channel gate electrode to BEOL interconnect, which will allow the use of the gate electrode as the first-level metal simultaneously, resulting in a simplified process.

#### ACKNOWLEDGMENT

The authors would like to thank the National Nano Device Laboratories, National Applied Research Laboratories, for technical support.

#### REFERENCES

- [1] C. Hu, "Gate oxide scaling limits and projection," in *IEDM Tech. Dig.*, 1996, pp. 319–322.

- [2] Y. Momiyama, H. Minakata, and T. Sugii, "Ultra-thin Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> gate insulator with TiN gate technology for 0.1 μm MOSFET's," in *Symp. VLSI Tech. Dig.*, 1997, pp. 135–136.

- [3] A. Yagishita, T. Saito, K. Nakajima, S. Inumiya, K. Matsuo, T. Shibata, Y. Tsunashima, K. Suguro, and T. Arikado, "Improvement of threshold voltage deviation in damascene metal gate transistors," *IEEE Trans. Electron Devices*, vol. 48, pp. 1604–1611, Aug. 2001.

- [4] J. L. Autran, R. Devine, C. Chaneliere, and B. Balland, "Fabrication and characterization of Si-MOSFET's with PECVD amorphous Ta<sub>2</sub>O<sub>5</sub> gate insulator," *IEEE Electron Device Lett.*, vol. 18, pp. 447–449, Sept. 1997.

- [5] C. H. Lee, H. F. Luan, W. P. Bai, S. J. Lee, T. S. Jeon, Y. Senzaki, D. Roberts, and D. L. Kwong, "MOS characteristics of ultra thin rapid thermal CVD ZrO<sub>2</sub> and Zr silicate gate dielectrics," in *IEDM Tech. Dig.*, 2000, pp. 27–30.

- [6] L. Kang, K. Onishi, Y. Jeon, B. H. Lee, C. Kang, W.-J. Qi, R. Nieh, S. Gopalan, R. Choi, and J. C. Lee, "MOSFET devices with polysilicon on single-layer HfO<sub>2</sub> high-κ dielectrics," in *IEDM Tech. Dig.*, 2000, pp. 35–38.

- [7] C. K. Maiti, S. Chatterjee, G. K. Dalapati, and S. K. Samanta, "Electrical properties of  ${\rm Ta_2O_5}$  gate dielectric on strained-Si," *Electron. Lett.*, vol. 39, pp. 497–499, Mar. 2003.

- [8] A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, "Device and reliability of high-κ Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>," in Symp. VLSI Tech. Dig., 1999, pp. 135–136.

- [9] E. P. Gusev, D. A. Buchanan, E. Cartier, A. Kumar, D. DiMaria, S. Guha, A. Callegari, S. Zafar, P. C. Jamison, D. A. Neumayer, M. Copel, M. A. Gribelyuk, H. Okorn-Schmidt, C. D'Emic, P. Kozlowski, K. Chan, N. Bojarczuk, L.-A. Ragnarsson, P. Ronsheim, K. Rim, R. J. Fleming, A. Mocuta, and A. Ajmera, "Ultrathin high-κ gate stacks for advanced CMOS devices," in *IEDM Tech. Dig.*, 2001, pp. 451–454.

- [10] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-κ gate dielectrics: Current status and material properties considerations," *J. Appl. Phys.*, vol. 89, no. 10, pp. 5243–5275, 2001.

- [11] S.-Q. Wang, "Barriers against copper diffusion into silicon and drift through silicon dioxide," MRS Bull., pp. 30–40, Aug. 1994.

- [12] K. Onishi, R. Choi, C. S. Kang, H.-J. Cho, Y. H. Kim, R. E. Nieh, J. Han, S. A. Krishnan, M. S. Akbar, and J. C. Lee, "Bias-temperature instabilities of polysilicon gate HfO<sub>2</sub> MOSFETs," *IEEE Trans. Electron Devices*, vol. 50, pp. 1517–1524, June 2003.

- [13] H. Hu, C. Zhu, Y. F. Lu, M. F. Li, B. J. Cho, and W. K. Choi, "A high performance MIM capacitor using HfO<sub>2</sub> dielectrics," *IEEE Electron De*vice Lett., vol. 23, pp. 514–516, Sept. 2002.

- [14] W. P. Bai, N. Lu, J. Liu, A. Ramirez, D. L. Kwong, D. Wristers, A. Ritenour, L. Lee, and D. Antoniadis, "Ge MOS characteristics with CVD HfO<sub>2</sub> gate dielectrics and TaN gate electrode," in *Symp. VLSI Tech. Dig.*, 2003, pp. 121–122.

- [15] A. L. S. Loke, C. Ryu, C. P. Yue, J. S. H. Cho, and S. S. Wong, "Kinetics of copper drift in PECVD dielectrics," *IEEE Electron Device Lett.*, vol. 17, pp. 549–551, Dec. 1996.

- [16] A. Mallikarjunan, S. P. Murarka, and T. M. Lu, "Metal drift behavior in low dielectric constant organosiloxane polymer," *Appl. Phys. Lett.*, vol. 79, pp. 1855–1857, Sept. 2001.

- [17] M. Balog and M. Schieber, "Chemical vapor deposition and characterization of HfO<sub>2</sub> films from organo-hafnium compounds," *Thin Solid Films*, vol. 41, pp. 247–259, 1977.

- [18] Y. H. Kim, K. Onishi, C. S. Kang, R. Choi, H. J. Cho, R. Nieh, J. Han, S. Krishnan, A. Shahriar, and J. C. Lee, "Hard and soft-breakdown characteristics of ultra-thin HfO<sub>2</sub> under dynamic and constant voltage stress," in *IEDM Tech. Dig.*, 2002, pp. 629–632.