## Effects of annealing temperature on electrical resistance of bonded n Ga As wafers

Po Chun Liu, Cheng Lun Lu, YewChung Sermon Wu, Ji-Hao Cheng, and Hao Ouyang

Citation: Applied Physics Letters 85, 4831 (2004); doi: 10.1063/1.1823592

View online: http://dx.doi.org/10.1063/1.1823592

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/85/21?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Current-voltage characteristics of p - Ga As n - Ga N heterojunction fabricated by wafer bonding Appl. Phys. Lett. **90**, 102107 (2007); 10.1063/1.2710750

Argon plasma exposure enhanced intermixing in an undoped In Ga As P In P quantum-well structure J. Appl. Phys. **100**, 046103 (2006); 10.1063/1.2227267

Low-temperature In P Ga As wafer bonding using sulfide-treated surface Appl. Phys. Lett. **88**, 061104 (2006); 10.1063/1.2172024

Low-temperature layer splitting of (100) GaAs by He + H coimplantation and direct wafer bonding Appl. Phys. Lett. **82**, 2413 (2003); 10.1063/1.1567045

Characterization of GaAs-based n-n and p-n interface junctions prepared by direct wafer bonding J. Appl. Phys. **92**, 7544 (2002); 10.1063/1.1522484

## Effects of annealing temperature on electrical resistance of bonded *n*-GaAs wafers

Po Chun Liu, Cheng Lun Lu, and YewChung Sermon Wu<sup>a)</sup>

Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, Republic of China

## Ji-Hao Cheng and Hao Ouyang

Department of Materials Engineering, National Chung Hsing University, Taichung 402, Taiwan, Republic of China

(Received 13 April 2004; accepted 20 September 2004)

The electrical characteristics and microstructures of n-type (100) GaAs bonded interfaces were systematically investigated. Experimental results indicated that GaAs did not bond directly to itself, but via an amorphous oxide layer at 400 °C. When temperatures increased above 400 °C, the oxide bonded area declined and finally disappeared. Electrical resistance decreased with bonding temperature. However, the resistance increased with temperatures exceeding 850 °C. © 2004 American Institute of Physics. [DOI: 10.1063/1.1823592]

The bonding of III-V semiconductors was developed for two-layer optoelectronic devices. 1-3 Bonding processes are normally performed at elevated temperatures to increase bonding strength and bonded area. 4,5 The most significant problems encountered are excess electrical resistance caused by interfacial defects, bulk defects, and surface defects. Interfacial defects were found to comprise mostly voids and inclusions caused by natural topographical irregularities, surface contamination (including native oxide), and solvent residues or trapped gases between the wafers. The causes of bulk and surface defects are more complex, and the extensive literature in the field reveals that these include dislocations, impurities, vacancies, interstitials, precipitates, and antisite defects. Arsenic antisite defects (arsenic on gallium sites As<sub>Ga</sub>) and clusters of other defects are generally known as EL2 (a deep donor in GaAs);<sup>6</sup> the concentration of these defects increases with arsenic concentration in the crystal.7 When wafers were bonded at elevated temperatures, the evaporation rate of arsenic from the surface exceeded that of gallium (about 2.5 times at 827 °C), which decreased the arsenic (and thus the EL2) concentration. If the wafer was semi-insulating, the evaporation of arsenic converted the outer surface from semi-insulating to p-type. This reduction of the EL2 (donor) concentration was a major factor that was responsible for the change in the electrical resistance of the GaAs single wafers.<sup>5</sup> This work investigates the origin of electrical resistances by systematically studying the bonding mechanisms, and by performing extensive materials and electrical characterization.

Si doped n-type (100) GaAs wafers were used. Wafers were diced into  $1 \times 1$  cm<sup>2</sup> samples using a diamond saw, and solvent-cleaned in a clean room. Cleaned wafers were pressed against each other in a differential thermal expansion fixture<sup>9</sup> with careful edge-to-edge alignment, such that the crystallographic directions in the plane of the bonded interface were arranged as in a single-crystal zinc-blende lattice. Then, the fixture was loaded into a furnace and was annealed

Two GaAs structures were used in this study—(1) single GaAs wafers and (2) two-layer bonded stacks. The single GaAs wafers were processed under identical thermal conditions and were used to separate the bulk and surface effects from the interfacial effects.

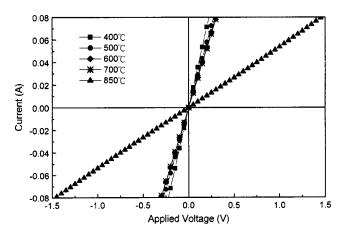

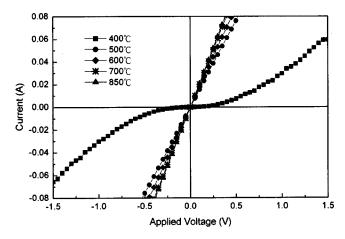

Figure 1 plots current versus voltage (I-V) for single GaAs wafers heat-treated at temperatures between 400 and 850 °C. Processing at temperatures that exceed 700 °C increase the electrical resistances of the heat-treated GaAs above those of the unprocessed GaAs wafers. No interface is involved in single wafer experiments, so the resistances must be increased by bulk and surface defects. Hall effect measurements revealed that the carrier concentration decreased from  $4.32 \times 10^{18}$  to  $3.02 \times 10^{16}$  cm<sup>-3</sup> as the processing temperature increased from room temperature to 850 °C. When  $20~\mu m$  was polished away, the carrier concentration increased to  $5.95 \times 10^{17}$  cm<sup>-3</sup>. The results indicated that changes of carrier concentration were caused mainly by arsenic depletion, as mentioned previously.

In addition to the above-described mechanism, other factors that may affect electrical resistance include the following. (1) The diffusion of As away from the EL2 center to

FIG. 1. Current–voltage characteristic of single *n*-type (100) GaAs wafers processed at temperatures from 400 to 850 °C for 2 h in argon ambient.

at temperatures from 400 to  $\,850~^{\circ}\text{C}$  for 2 h in argon ambient.

a) Author to whom correspondence should be addressed; electronic mail: Sermonwu@stanfordalumni.org

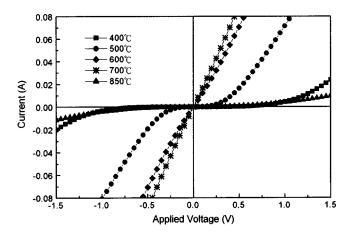

FIG. 2. Current–voltage characteristic of bonded two-layer (100) wafers processed at temperatures from 400 to  $850\,^{\circ}$ C for 2 h in argon ambient.

form large precipitates (leading to p-type conversion); (2) the diffusion of impurities inwards from the wafer surfaces (to an extent that increases with temperature and time); and (3) the plastic deformation of GaAs under a fixed compressive load (to an extent that increases with temperature  $^{10-12}$ ), producing a greater density of dislocations. These factors may explain why some degradation in electrical resistance persists even after the As-depleted surfaces (surface defects) were polished away.

Figure 2 plots I-V for GaAs wafers bonded at temperatures between 400 and 850 °C. GaAs does not bond at temperatures below 400 °C and the resistance of GaAs bonded at 400 °C was very large. A more or less continuous decrease in resistance was expected with increasing bonding temperature, since mass transport (diffusion, vapor transport, etc.) and reaction rate increase with temperature. However, at temperatures over 850 °C, the increase of the resistance was due mainly to the reduction of the surface carrier concentration caused by incongruent evaporation. Surface polishing reduced the electrical resistance of the bonded wafers; however, the resistance did not return to its original value.

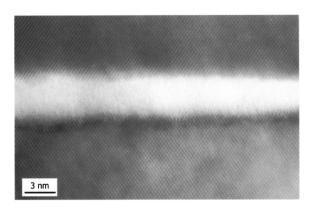

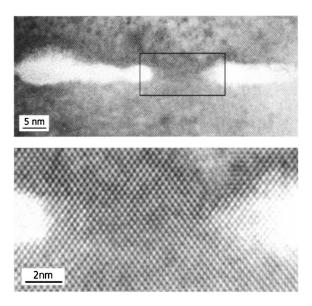

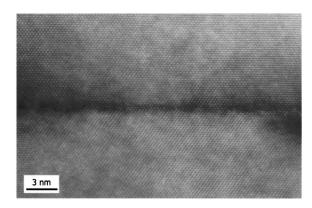

Transmission electron microscopy (TEM) analysis of these specimens indicated that various bonding mechanisms were involved. At 400 °C, GaAs does not bond directly to itself, but via an amorphous oxide layer, as shown in Fig. 3. When the bonding temperature increased, the amorphous oxide layer became discontinuous and local GaAs bonded areas were formed, as shown in Fig. 4. The GaAs bonded areas increased with the bonding temperature. Finally, when pro-

FIG. 3. Cross-sectional high resolution TEM image of a (100) GaAs interface bonded at 400 °C, showing an oxide layer at the interface.

FIG. 4. Cross-sectional high resolution TEM image of a (100) GaAs interface bonded at 500 °C, showing a locally GaAs bonded interface combined with an array of amorphous oxide regions.

cessed at 850 °C, most GaAs wafers were found to be bonded directly to themselves. As presented in Fig. 5, no oxide layer was found between GaAs even though a native oxide layer was likely to have formed on the wafer surfaces before they were loaded into the furnace.

The above-mentioned observations of the amorphous oxide layer (oxygen distribution) around the interface were verified by the following methods: energy dispersive x-ray spectroscopy line-scan and high-angle annular-dark field. The oxygen content was found to increase as the distance from the interface decreased. <sup>13</sup>

In related works, Shi *et al.*<sup>14</sup> bonded GaAs wafers at 400 °C for 1 h and then annealed them at 600 °C for various periods. They found that GaAs could be successfully bonded at 400 °C because of the presence of continuous oxide at the interface. During annealing at 600 °C, a drastic change in interface morphology caused by atomic rearrangement led to the formation of a locally GaAs-bonded interface combined with an array of bubblelike amorphous oxide regions. Shi *et al.* believed that the oxide layer became discontinuous because the atomic rearrangement reduced the GaAs/oxide interface energy. However, they made no attempt to bond wafers at temperatures higher than 600 °C.

FIG. 5. Cross-sectional high resolution TEM image of a (100) GaAs interface bonded at 800 °C, showing intimate contact between GaAs with no intervening oxide layer.

FIG. 6. Current–voltage characteristic of bonded two-layer p-type (100) GaAs wafers.

In our work, as the temperature increased above 400 °C, the oxide-bonded areas gradually decreased until they finally disappeared. We posit that this increase of the area of the GaAs bonded interface was due mainly to the indiffusion of oxide into the GaAs wafers, which can be modeled by a one-dimensional diffusion equation based on a reference point at the center of the bonded interface. The diffusion constant of oxygen into GaAs is given by

$$D = 2 \times 10^{-3} \exp(-1.1 \text{ eV/kT}) \text{ cm}^2 \text{ s}^{-1},$$

where T is the bonding temperature and k is the gas constant. When T=850 °C, the diffusivity of oxygen in GaAs, D, equals  $2.55 \times 10^{-8}$  cm<sup>2</sup> s<sup>-1</sup>. A typical 2 h diffusion process can affect the oxygen concentration within  $\approx \sqrt{Dt}$   $\approx 135~\mu \text{m}$  of the bonded interface.

The primary function of the oxygen in GaAs was to reduce the donor (Si) concentration through the formation of complexes between oxygen and donors, thereby reducing the carrier concentration. The reduction of the carrier concentration at the bonded interface was confirmed using spreading resistance probe (SRP), indicating that the SRP signal (resistance) at the interface was about double that inside the GaAs bulk. In other words, the indiffusion of oxygen into GaAs negatively affects the carrier concentration, indicating that this indiffusion may explain why the some degradation in electrical resistance was detected even after the As-depleted surfaces (surface defects) had been polished away.

For comparison, cleaned *p*-type GaAs samples were pressed against each other and annealed under identical thermal conditions. The resistance was found to fall as the bonding temperature increased, as shown in Fig. 6. These results differed completely from those for *n*-type GaAs. In other

words, the indiffusion of oxygen was the major cause of increases of resistance at the *n*-GaAs bonded interface.

In summary, this study examined the relationship between bonding temperatures and electrical characteristics of *n*-type (100) GaAs bonded wafers. Experimental results indicate that GaAs was successfully bonded at 400 °C by continuous oxide at the interface. The GaAs bonded areas increased with the bonding temperature. Finally, when processed at 850 °C, most GaAs wafers were found to be bonded directly to themselves. GaAs bonded areas increased with bonding temperature, so electrical resistance decreased with bonding temperature. However, the resistance increased with temperature over 850 °C due to the reduction of the surface carrier concentration and the indiffusion of oxygen into the GaAs bonded interface.

The authors would like to thank the National Science Council (NSC) of the Republic of China under Contract No. NSC 92-2216-E-009-012. Technical support from the National Nano Device Laboratory of NSC and the Nano Facility Center of National Chiao Tung University are also acknowledged.

<sup>1</sup>F. A. Kish, D. A. Vanderwater, M. J. Peanasky, M. L. Ludowise, S. G. Hummel, and S. J. Rosner, Appl. Phys. Lett. **67**, 2060 (1995).

<sup>2</sup>Z. L. Liau and D. E. Mull, Appl. Phys. Lett. **56**, 737 (1990).

<sup>3</sup>T. Akatsu, A. Plößs, H. Stenzel, and U. Gösele, J. Appl. Phys. **86**, 7146 (1999).

<sup>4</sup>Y. S. Wu, P. C. Liu, R. S. Feigelson, and R. K. Route, J. Appl. Phys. **91**, 1973 (2002).

<sup>5</sup>Y. S. Wu, R. S. Feigelson, R. K. Route, D. Zheng, L. A. Gordon, M. M. Fejer, and R. Byer, J. Electrochem. Soc. **145**, 366 (1998).

<sup>6</sup>O. Oda, H. Yamamoto, M. Seiwa, G. Kano, T. Inoue, M. Mori, H. Shinakura, and M. Oyake, Semicond. Sci. Technol. **7**, A215 (1992).

<sup>7</sup>D. E. Holems, R. T. Chen, K. R. Elliot, C. G. Kirkparick, and P. H. Wu, IEEE Trans. Electron Devices **ED–29**, 1045 (1982).

<sup>8</sup>C. T. Foxton, J. A. Harvey, and B. A. Joyce, J. Phys. Chem. Solids 34, 1693 (1973).

<sup>9</sup>C. P. Chao, Y. S. Wu, T. L. Lee, and Y. H. Wang, Jpn. J. Appl. Phys., Part 2 **42**, 5527 (2003).

<sup>10</sup>R. Behrensmeier, H. G. Brion, H. Siethoff, P. Veyssiere, and P. Haasen, Mater. Sci. Eng., A 137, 173 (1991).

<sup>11</sup>S. Guruswamy, R. S. Rai, K. T. Faber, and J. P. Hirth, J. Appl. Phys. **62**, 4130 (1987).

<sup>12</sup>S. Guruswamy, R. S. Rai, K. T. Faber, J. P. Hirth, J. E. Clemans, S. McGuigan, R. N. Thomas, and W. Mitchel, J. Appl. Phys. 65, 2508 (1989).

H. Ouyang, J. H. Cheng, C. L. Lu, and Y. S. Wu, Nano Lett. (submitted).

F. Shi, K. L. Chang, J. Epple, C. F. Xu, K. Y. Cheng, and K. C. Hsieh, J. Appl. Phys. 92, 7544 (2002).

<sup>15</sup>J. Rachmann and R. Biermann, Solid State Commun. **7**, 1771 (1969).

<sup>16</sup>D. S. Ruby, K. Arai, and G. E. Stillman, J. Appl. Phys. **58**, 825 (1985).

<sup>17</sup>J. F. Woods and N. G. Ainsile, J. Appl. Phys. **34**, 1469 (1963).

<sup>18</sup>R. H. Wallis, M.-A. di Forte Poission, M. Bonnet, G. Beuchet, and J.-P. Duchemin, Inst. Phys. Conf. Ser. **56**, 73 (1981).