## Low voltage lead titanate/Si one-transistor ferroelectric memory with good device characteristics

C. L. Sun, S. Y. Chen, C. C. Liao, and Albert Chin

Citation: Applied Physics Letters 85, 4726 (2004); doi: 10.1063/1.1814440

View online: http://dx.doi.org/10.1063/1.1814440

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/85/20?ver=pdfcov

Published by the AIP Publishing

### Articles you may be interested in

Resistive switching characteristics in dielectric/ferroelectric composite devices improved by post-thermal annealing at relatively low temperature

Appl. Phys. Lett. 104, 092903 (2014); 10.1063/1.4867260

Retention in nonvolatile silicon transistors with an organic ferroelectric gate

Appl. Phys. Lett. 94, 263507 (2009); 10.1063/1.3158959

Semiconductive metal oxide ferroelectric memory transistor: A long-retention nonvolatile memory transistor

Appl. Phys. Lett. 86, 123513 (2005); 10.1063/1.1886252

Low-temperature integration of lead-based ferroelectric capacitors on Si with diffusion barrier layer

Appl. Phys. Lett. 80, 3599 (2002); 10.1063/1.1477281

Fabrication and characterization of a Pb 5 Ge 3 O 11 one-transistor-memory device

Appl. Phys. Lett. **79**, 1661 (2001); 10.1063/1.1401092

APPLIED PHYSICS LETTERS VOLUME 85, NUMBER 20 15 NOVEMBER 2004

# Low voltage lead titanate/Si one-transistor ferroelectric memory with good device characteristics

### C. L. Sun<sup>a)</sup> and S. Y. Chen

Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan, Republic of China

#### C. C. Liao and Albert Chin

Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan, Republic of China

(Received 30 April 2004; accepted 1 September 2004)

We have developed one-transistor ferroelectric memory using lead titanate (PTO) as a gate dielectric directly formed on Si without any buffer layer. The PTO/Si metal—oxide—semiconductor field-effect transistor memory has shown a large threshold voltage shift of 1.6 V at only  $\pm 4$  V program/erase voltages. The corresponding good interface was achieved by lowering the anneal temperature to 450 °C. Besides the sharp capacitance change of 0.17  $\mu$ F/V cm², it was also evidenced by the high mobility of 169 cm²/V s close to high- $\kappa$  HfO<sub>2</sub>. In addition, long retention >1000 s and endurance >10<sup>11</sup> stress cycles in the device suggested good memory characteristics. © 2004 American Institute of Physics. [DOI: 10.1063/1.1814440]

Among various memory devices, ferroelectric memories are particularly remarkable due to the unique nonvolatile behavior, good scale down potential, and fast switching time. Currently, high capacity (>1 Mbyte) ferroelectric RAM has been demonstrated in the cell configuration consisting of one-transistor (1T) and one-capacitor. But in order to further scale down the cell size, it is necessary to integrate the ferroelectric materials in the 1T ferroelectric metal-oxidesemiconductor field-effect transistor (FeMOSFET). 1-9 However, the strong interface reaction between ferroelectric materials and Si remained the major technology obstacle for this 1T memory in the last decade.<sup>3</sup> Recently, the adoption of a buffer gate dielectric between ferroelectric materials and Si shed a light to overcome the interdiffusion problem as a result of the inevitable high anneal temperature of ferroelectrics.<sup>4–8</sup> For example, using Al<sub>2</sub>O<sub>3</sub> as the good dielectric and diffusion barrier, <sup>10,11</sup> we have achieved the record large ferroelectric memory window of 13 V in this kind of stack gate structure.8 Unfortunately, the relatively large writing voltage was usually required owing to the voltage drop on the Al<sub>2</sub>O<sub>3</sub> dielectric so as to hinder the widely industrial applications. On the other hand, although the low temperature process has already been demonstrated in the organic permanent memory transistor, it still requires relatively high operation voltage caused by thick gate insulator.9 Besides the good threshold voltage shift  $(\Delta V_T)$  at a low writing voltage, the high carrier mobility is also requested in mainstream MOSFET technology.<sup>12</sup> Therefore, it is really challenging to develop a next-generation low voltage 1T Fe-MOSFET memory.

It has been reported that  $Pb(Zr,Ti)O_3$  solid solution with higher Ti fraction would need a lower anneal temperature. Supposedly, this low anneal temperature should be helpful to prevent the formation of interfacial layer, <sup>13</sup> which is essential to decrease the programming voltage in the low voltage operation. To study this effect, we have calculated the electric field ( $E_{\rm ferro}$ ) in the ferroelectric material:

$$E_{\text{ferro}} = V_g / \left( d_{\text{ferro}} + \frac{\varepsilon_{\text{ferro}}}{\varepsilon_{\text{interface}}} d_{\text{interface}} \right). \tag{1}$$

The  $E_{\rm ferro}$ ,  $\varepsilon_{\rm ferro}$ , and  $d_{\rm ferro}$  are the electric field, dielectric constant, and thickness in ferroelectric layer, where the  $\varepsilon_{\rm interface}$  and  $d_{\rm interface}$  are the dielectric constant, and thickness in interfacial layer. Because the  $\Delta V_T$  is from ferroelectric polarization, a larger  $E_{\rm ferro}$  is desired. Thus, decreased  $d_{\rm interface}$  and  $\varepsilon_{\rm ferro}$  are the solution to increase the desired  $E_{\rm ferro}$ . This can be also obtained by lowering the anneal temperature of lead titanate (PTO) simultaneously though the ferroelectric property of PTO may be degraded by trading off the  $E_{\rm ferro}$ . Thus in this letter we investigated lead titanate as a ferroelectric gate material directly grown on Si substrates with the low temperature annealing. Particularly, while the anneal temperature could be lowered down to 450 °C, it indicates the potential application for embedded memories and could also help terminate the contamination to integrated circuit

P-type 4 in. Si wafers with a resistivity of approximately 10  $\Omega$  cm were used in this study. After device isolation and source–drain  $n^+$  region definition, the around 90-nm-thick PTO layer was deposited by spin coating, dried at 90 °C for 30 s, and annealed at 450 °C. The entire process details were

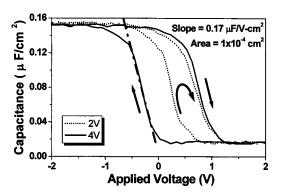

FIG. 1. 1 MHz C–V characteristics of PTO/Si FeMOS capacitor. The capacitor size is  $10^{-4}$  cm<sup>2</sup> and the gate length of the FeMOSFET is  $10 \mu m$ .

a)Electronic mail: clsun@ms.ntu-ccms.ntu.edu.tw

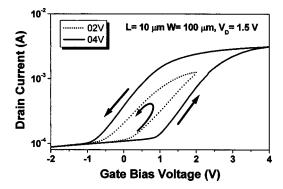

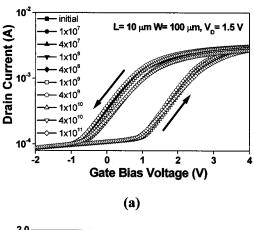

FIG. 2.  $I_D$ – $V_G$  characteristics of PTO/Si FeMOSFETs. The capacitor size is  $10^{-4}~\rm cm^2$  and the gate length of the FeMOSFET is  $10~\mu m$ .

described in our previous reports. <sup>5–7</sup> HF-vapor passivation <sup>10,11</sup> was used to suppress the native oxide formation before PTO formation. Finally, Al electrodes were formed and the device size was  $10~\mu m \times 100~\mu m$ . The device performance was characterized by capacitance–voltage (C-V) and current–voltage (I-V) measurements.

Figures 1 and 2 show the device memory characteristics measured from 1MHz C-V of FeMOS capacitor and drain current-gate bias voltage  $(I_D-V_G)$  characteristics of FeMOS-FET, respectively. The very high  $I_D$  in Fig. 2 is due to high- $\kappa$  property of PTO that is important for VLSI scaling down. fo-13 The ferroelectric characteristics are evidenced from the clockwise C-V hysteresis loops and counterclockwise  $I_D$ – $V_G$  hysteresis loops, as shown by arrows. For a low ±4 V program and erase voltage, a memory window of 1.6 V is obtained from both the flatband voltage shift in C-Vcurves. Additionally, the  $\Delta V_T$  change in  $I_D$ – $V_G$  characteristics indicates the excellent memory device performance. The possible reason for such low writing voltage is because the gate voltage is directly applied on the ferroelectric material instead of generating the voltage drop on the interfacial layer or inserted dielectric diffusion barrier.8 Although the PTO annealed at low temperature could have a relatively poor crystallinity or small permanent polarization, from the device point-of-view, avoiding the interfacial oxide layer is much more important than the crystal structure because a small polarization of ferroelectrics is still enough for memory operation.<sup>4</sup> The excellent device characteristics can also be evidenced by the very sharp capacitance change  $(\Delta C/\Delta V)$  of  $0.17 \mu F/V \text{ cm}^2$ , implying very sensitive ferroelectric domain switching under voltage sweeping.

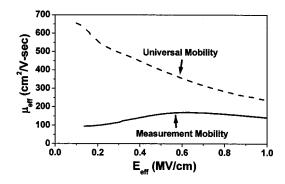

To further study the interface quality, we have measured the effective mobility of the 1T PTO/Si FeMOSFET. Figure

FIG. 3. The effective mobility of the low temperature formed PTO/Si subject PTO/Si FeMOSFE FeMOSFETs.

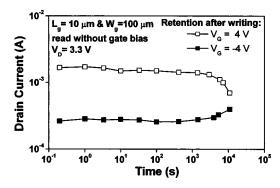

FIG. 4. The measured retention characteristics of the PTO/Si memory at  $\pm 4$  V writing voltages.

3 shows the effective mobility ( $\mu_{\rm eff}$ ) dependence on effective electric field ( $E_{\rm eff}$ ) obtained from the  $I_D$ – $V_G$  measurements. The effective mobility peak of 169 cm²/V s is obtained, which is comparable to the best data in high- $\kappa$  HfO<sub>2</sub> MOSFET. This high mobility indicates that good interface between PTO and Si can be achieved at such low anneal temperature. It is noteworthy that the extraordinary high- $\kappa$  and high mobility nature would play a crucial role for further device scaling down into the sub-0.1  $\mu$ m range.

In the roadmap of nonvolatile memories, data retention is another important factor. Figure 4 displays the time-dependent current changes and retention characteristics of the PTO/Si memory. The open and closed data points represent the drain currents after applying program/erase voltage of  $\pm 4$  V to gate. As shown in Fig. 4, it can be observed that the drain currents do not significantly fall down or go up-

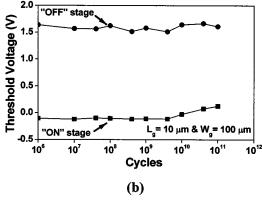

FIG. 5. (a) The endurance characteristics and (b) threshold voltage changes of PTO/Si FeMOSFETs after 1 MHz±4 V writing with different stress cycles.

ward within the time range of 1000 s. Consequently, a retention time of >1000 s can be claimed from the time-independent current values. The good retention could also support the absence of the interfacial layer that not only behaves as a series capacitor but also generates a depolarization field.

We have further done the measurement of the endurance of 1T PTO/Si memory. Figures 5(a) and 5(b) illustrate the endurance characteristics in  $I_D$ – $V_G$  and  $\Delta V_T$  of PTO/Si memory, respectively. The ON and OFF states in  $V_T$  before and after stress are determined from the  $I_D$ – $V_G$  hysteresis loops under the stress condition of  $\pm 4$  V at 1 MHz. As shown in Fig. 5(a), the nearly identical  $I_D$ – $V_G$  curves after repeated cycling are in agreement with the good endurance  $>10^{11}$  cycles in Fig. 5(b). This good endurance is attributed to the fact that the low program/erase electric fields could generate the relatively small amount of defects in the PTO/Si memory structure.

In conclusion, a ferroelectric PTO/Si 1T memory with large memory window, high mobility, sharp capacitance change, and good endurance has been demonstrated. Unlike using the buffer layer in stack gate structure, the low temperature annealing for the single-layer ferroelectric gate has been proved to be extremely essential in preventing the formation of an interfacial layer. The good memory character-

istics in this FeMOSFET show the technical potential for next-generation memory application.

This work has been supported by NSC93-2215-E-009-001 of Taiwan.

- <sup>1</sup>S. Y. Wu, IEEE Trans. Electron Devices 499 (1974).

- <sup>2</sup>S. Y. Wu, Ferroelectrics **11**, 379 (1976).

- <sup>3</sup>S. L. Miller and P. J. McWhorter, J. Appl. Phys. **72**, 5999 (1992).

- <sup>4</sup>J.-P. Han and T. P. Ma, Appl. Phys. Lett. **72**, 1185 (1998).

- <sup>5</sup>M. Y. Yang, S. B. Chen, A. Chin, C. L. Sun, B. C. Lan, and S. Y. Chen, Tech. Dig. Int. Electron Devices Meet. **2001**, 795 (2001).

- <sup>6</sup>C. L. Sun, S. Y. Chen, S. B. Chen and A. Chin, Appl. Phys. Lett. **80**, 3168 (2002).

- <sup>7</sup>C. L. Sun, S. Y. Chen, M. Y. Yang, and A. Chin, J. Electrochem. Soc. **148**, F203 (2001).

- <sup>8</sup>C. L. Sun, S. Y. Chen, S. B. Chen, and A. Chin, Appl. Phys. Lett. 80, 1984 (2002).

- <sup>9</sup>R. Schroeder, L. A. Majewski, and M. Grell, Adv. Mater. (Weinheim, Ger.) 7, 633 (2004).

- <sup>10</sup>A. Chin, C. C. Liao, C. H. Lu, W. J. Chen, and C. Tsai, Symposium on VLSI Technology, 1999, p. 133.

- <sup>11</sup>A. Chin, Y. H. Wu, S. B. Chen, C. C. Liao, and W. J. Chen, *Symposium on VLSI Technology*, 2000, p. 19.

- <sup>12</sup>K. Onishi, C. S. Kang, R. Choi, H. J. Cho, S. Gopalan, R. Nieh, S. Krishnan, and Jack C. Lee, *Symposium on VLSI Technology*, 2002, p. 22.

- <sup>13</sup>C. H. Huang, D. S. Yu, A. Chin, W. J. Chen, C. X. Zhu, M.-F. Li, B. J. Cho, and D. L. Kwong, Tech. Dig. Int. Electron Devices Meet. 2003, 319