# Thermal Gradient in Solder Joints under Electrical-Current Stressing

T.L. SHAO, 1 S.H. CHIU, 1 CHIH CHEN, 1,4 D.J. YAO, 2 and C.Y. HSU3

1.—Department of Material Science and Engineering, National Chiao Tung University, Hsin-chu 300, Taiwan, Republic of China. 2.—Institute of Microelectromechanical System, National Tsing Hua University, Hsin-chu 300, Taiwan, Republic of China. 3.—Department of Power Mechanical Engineering, National Tsing Hua University. 4.—E-mail: chih@cc.nctu.edu.tw

The thermal gradient and temperature increase in SnAg3.5 solder joints under electrical-current stressing have been investigated by thermal infrared microscopy. Both positive and negative thermal gradients were observed under different stressing conditions. The magnitude of the thermal gradient increases with the applied current. The measured thermal gradients reached 365°C/cm as powered by 0.59 A, yet no obvious thermal gradient was observed when the joints were powered less than 0.25 A. The temperature increase caused by joule heating was as high as 54.5°C when powered by 0.59 A, yet only 3.7°C when stressed by 0.19 A. The location of heat generation and path of heat dissipation are believed to play crucial roles in the thermal gradient. When the major heat source is the Al trace, the thermal gradient in the solder bumps is positive; but it may become negative because the heat generated in the solder itself is more prominent.

**Key words:** SnAg3.5, solder joints, electrical current stressing, thermal gradients

# INTRODUCTION

As the required device density and power of flipchip packages increase, lelectromigration (EM) of solder joints under high electrical-current stressing has attracted much attention.<sup>2–4</sup> Solder bump pitch has decreased rapidly; in turn, the contact area of the solder bumps and the diameter of under bump metallization (UBM) decrease rapidly too. On the other hand, the operation current for the bumps keeps increasing, resulting in a dramatic rise of the current density in the solder bump. Therefore, joule heating in the older joints becomes a reliability issue.<sup>5</sup> Because EM is the result of a combination of thermal and electrical effects on mass migration, a large joule heating will cause higher temperature in the solder bumps and accelerate the EM failure. During EM testing, the bumps are powered at elevated ambient temperature for accelerated testing. Hence, the temperature in the bumps during testing may be much higher than that of the ambient caused by joule heating and may affect the mean-time-to-failure analysis.6

In addition to the overall rising of temperature caused by joule heating, there might exist a thermal gradient across the solder bump. In general, most joule heating is generated in the Al trace on the Si chip side because its electrical resistance is at least one order of magnitude larger than those of the solder bump and the Cu line in the substrate. Therefore, the temperature in the Si chip might be higher than that in the substrate, as reported by Ye et al.<sup>7</sup> Consequently, thermomigration caused by a thermal gradient of 1,500°C/cm in the solder bumps might account for the void formation on the anode (chip) side. However, no experimental data are available to verify the bump temperature and the thermal gradient under current stressing. In this paper, temperature rising in solder bumps caused by various current-stressing conditions is measured. Different thermal gradients across solder bumps were detected. The reasons that cause the different thermal gradients are discussed.

## **EXPERIMENTAL**

In the flip-chip package of solder bumps to be tested, the Si chip size was  $9.5~\text{mm} \times 6~\text{mm}$  and `the

(Received March 10, 2004; accepted June 25, 2004)

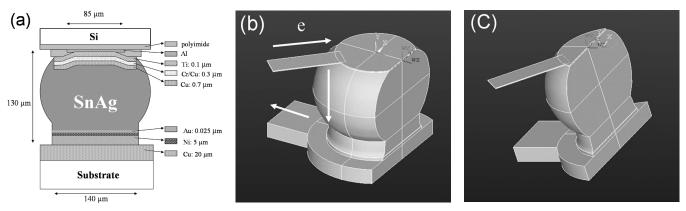

Fig. 1. Schematic diagrams of the bumps used in this study: (a) Cross-sectional view showing the materials and the dimension of a bump in a flip-chip package. (b) Schematic of Bump 1 in which 97% of the solder remains. (b) Schematic of Bump 2 in which 14% of the solder remains.

thickness was 350 um. The dimension of the Al trace in the chip side was 40-µm wide and 1.5-µm thick. The UBM was 105 µm in diameter, and the opening contacted with Al pads was 85 µm in diameter. The UBM consisted of 0.7-µm Cu, 0.3-µm Cr-Cu, and 0.1-µm Ti. Solder paste of Sn96.5Ag3.5 was printed through a metal stencil onto the UBM pads of the Si chip and reflowed to form a bumped chip. To fabricate flip-chip joints, the bumped chips were first mounted on a bismaleimide triazine (BT) substrate to form a flip chip, then the flip-chip package was reflowed again and underfilled. A schematic cross-section diagram of the flip-chip package is shown in Fig. 1a. The directions of electron flow under stressing are indicated by the arrows.

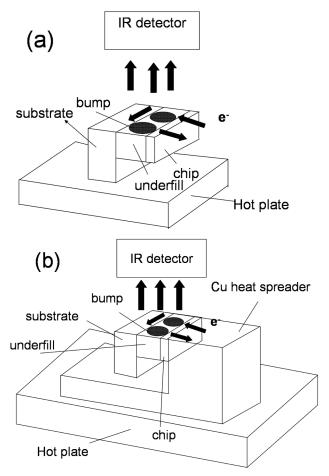

To measure the temperature increase in the solder joints caused by the current stressing, two specimens with different locations of cross section were prepared, as seen schematically in Fig. 1. Bump 1 was polished laterally until the contact opening is visible, in which approximately 97% mass of the bump is left (Fig. 1b). Bump 2 was polished much further with only about 14% mass of the bump left (Fig. 1c). The current stressing of the specimens was performed on a hot plate in the air ambient. The experimental setup is shown in Fig. 2a, in which the specimens were powered by various currents on a hot plate maintained at 70°C.

Another experimental setup was employed to enhance heat dissipation in the chip side (Fig. 2b). The Si chip side was bonded to an L-shaped Cu plate, which served as a heat spreader. Prior to the current stressing, the emissivity of the specimen was calibrated at 70°C. After the calibration, the bumps were powered by a desired current. Then, a temperature measurement was performed to record the temperature distribution (map) after the temperature reached a stable state. The temperatures in the solder joints were mapped by a QFI thermal infrared microscopy (Quantum Focus Instruments, Vista, CA), which has a 0.1°C temperature resolution and a 2-µm spatial resolution.

Fig. 2. Schematic of the experimental setup during temperature measurement for: (a) a flip-chip package and (b) a flip-chip package with a Cu heat spreader attached to the chip side.

#### RESULTS

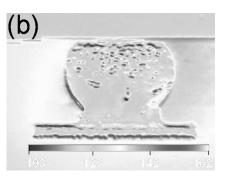

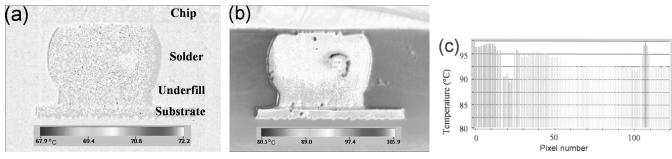

The temperature distribution in Bump 1 before current stressing is shown in Fig. 3a. The temperature variation inside the bump is less than 5°C. This large temperature fluctuation is due to its rough surface. When the joint was powered by 0.586 A, the temperature distribution in the joint changed (Fig. 3b). The average temperature increase in the

Fig. 3. (a) Temperature map of Bump 1 before current stressing, showing a uniform temperature distribution in the solder; (b) temperature map of Bump 1 powered by 0.59 A; and (c) temperature profile along the dashed line in (b), showing a positive thermal gradient.

bump caused by the current stressing was as high as 54.5°C, and the temperature rising in the surrounding underfill reaches 70°C. The temperature increase in the Si chip near the bump is about 55°C and approximately 60°C for the BT substrate near the bump. It is worth noting that the variation in surface morphology may affect the temperature measurement by the infrared technique. As seen in Fig. 3b, the measured temperature has had a larger fluctuation around the defect in the bump or the step along the peripheral of the bump. This temperature fluctuation may be due to emissivity deviation caused by surface-morphology variation. Besides, because of a long data-acquisition time of about 12 sec, the image around the peripheral of the bump may have shifted a few micrometers.

The thermal gradient is defined here as the subtraction of the average temperature near the substrate end in the bump from the average temperature near the chip end in the bump, then divided by the bump height, i.e.,  $(T_{\rm chip} - T_{\rm subs})$ /h. Figure 3c shows the temperature profile along the dashed line in Fig. 3b in which the average temperature in the chip end is higher than that in the substrate end. The thermal gradient was estimated to be 365°C/cm.

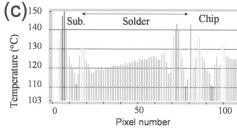

The temperature map in Bump 2 before current stressing is shown in Fig. 4a. The temperature variation inside the bump is less than 1°C. The temperature distribution in the bump when powered by 0.285 A is shown in Fig. 4b. The average temperature increase in the bump caused by the current stressing was 22.6°C, and the temperature rise in the underfill reaches 29.1°C. The temperature in the

BT substrate is about 5°C higher than that in the Si chip under the preceding stressing condition.

We have observed negative thermal gradients under different stressing conditions in Bump 2. Figure 4c shows the temperature profile along the dashed line in Fig. 4b in which the average temperature in the bump close to the chip end is lower than that close the substrate end. Thus, a negative thermal gradient of -139°C/cm exists in this bump. The measured thermal gradients and temperature increases are summarized in Table I. For Bump 1, the thermal gradient was 369°C/cm when powered by 0.59 A, and it decreased with the stressing current. When powered by 0.19 A, it decreased down to 58°C/cm, which corresponds to a difference of 0.5°C across the bump. However, positive thermal gradients were observed in Bump 1 when powered from 0.19 A to 0.59 A. For Bump 2, all the thermal gradients appear to be negative for the four stressing conditions, indicating that the temperature in the substrate end in the bump is higher than that in the chip end.

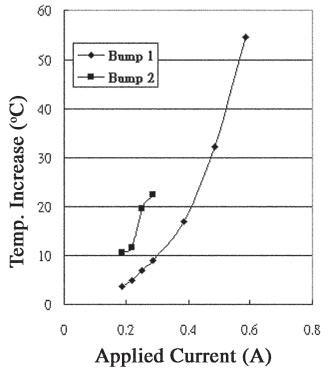

The measured temperature increases in Bumps 1 and 2 for various stressing conditions are shown in Fig. 5. The temperature risings increase as the stressing currents increase for both bumps. For Bump 1, the temperature increase was as high as 54.5°C when powered by 0.59 A while only 3.7°C when powered by 0.19 A. For Bump 2, the temperature increase was 22.6°C as powered by 0.285 A while it was 10.7°C when powered by 0.19 A.

With the Cu heat spreader attached to the chip side, the temperature rise in Bump 1 reduced to

Fig. 4. (a) Temperature map of Bump 2 before current stressing, showing a uniform temperature distribution in the solder; (b) temperature map of Bump 2 powered by 0.29 A; and (c) temperature profile along the dashed line in (b), showing a negative thermal gradient.

| Applied<br>Current<br>(A) | Current<br>Density in<br>Al Trace<br>(A/cm <sup>2</sup> ) | Bump 1<br>(97% Mass of the Solder Left)            |                     |                                | Bump 2<br>14% Mass of the Solder Left)             |                     |                                |  |  |  |

|---------------------------|-----------------------------------------------------------|----------------------------------------------------|---------------------|--------------------------------|----------------------------------------------------|---------------------|--------------------------------|--|--|--|

|                           |                                                           | Bump<br>Current<br>Density<br>(A/cm <sup>2</sup> ) | Temp. Increase (°C) | Thermal<br>Gradient<br>(°C/cm) | Bump<br>Current<br>Density<br>(A/cm <sup>2</sup> ) | Temp. Increase (°C) | Thermal<br>Gradient<br>(°C/cm) |  |  |  |

| 0.59                      | $\overline{9.8	imes10^5}$                                 | $\overline{1	imes10^4}$                            | 54.5                | 365                            | N/A                                                | N/A                 | N/A                            |  |  |  |

| 0.49                      | $8	imes 10^5$                                             | $8.3	imes10^3$                                     | 32.2                | 293                            | N/A                                                | N/A                 | N/A                            |  |  |  |

| 0.39                      | $6.4	imes10^5$                                            | $6.6	imes10^3$                                     | 17.1                | 215                            | N/A                                                | N/A                 | N/A                            |  |  |  |

| 0.29                      | $4.7	imes10^5$                                            | $4.9 	imes 10^3$                                   | 9.1                 | 127                            | $3.6	imes10^4$                                     | 22.6                | -139                           |  |  |  |

| 0.25                      | $4.2	imes10^5$                                            | $4.3	imes10^3$                                     | 6.9                 | 98                             | $3.2 	imes 10^4$                                   | 19.8                | -115                           |  |  |  |

| 0.22                      | $3.6	imes10^5$                                            | $3.8	imes10^3$                                     | 5.0                 | 67                             | $2.8	imes10^4$                                     | 11.7                | -73                            |  |  |  |

| 0.19                      | $3.1	imes10^5$                                            | $3.2 	imes 10^3$                                   | 3.7                 | 57                             | $2.3	imes10^4$                                     | 10.9                | -73                            |  |  |  |

Table I. The Temperature Increase and Thermal Gradient in the Bumps under Various Curent-Stressing Conditions

The calculated bump-current density was based on the remaining contact opening of the chip side.

19.1°C when powered by 0.59 A, and its thermal gradient also decreased to  $332^{\circ}$ C/cm. For Bump 2, powered by 0.29 A with the Cu heat spreader, both the temperature rise and thermal gradient declined to 7.7°C and  $-116^{\circ}$ C/cm, respectively. Thus, with the Cu heat spreader, the temperature rise in the powered bumps was reduced significantly, yet the thermal gradient remains the same positive or negative trend with a smaller magnitude.

### **DISCUSSION**

We have inferred that the Al trace is the major heat-generating source for Bump 1. The resistance of a complete (unpolished) bump is estimated to be 8 m $\Omega$  while the resistance of the 1,000- $\mu$ m Al trace is about 180 m $\Omega$ . The temperature of Bump 1 rises as the stressing current increases (Fig. 5). The temperature increase may be mainly due to the heat flux from the Al trace. However, when powered by the same current, the temperature increase in Bump 2 is at least two times larger than that in Bump 1, which implies that an additional heat source may be the solder bump itself because of its higher heating power and lesser mass. If we consider the heat generated from the bump only, and the heat causes the bump temperature increase of  $\Delta T$ :

$$P = I^2 R = mC_p \Delta T \tag{1}$$

where P is joule heating power, I is current, R is the resistance of the bump, m is the mass of the bump, Cp is the heat capacity, and  $\Delta T$  is the temperature increase caused by joule heating. Based on the preceding equation, the temperature increase in Bump 2 caused by self-joule heating is 48 times larger than that in Bump 1 when powered by the same current. Alternatively, it can be also explained in terms of heating power per unit volume. The heating power per unit volume is  $j^2\rho$ , where j is current density, and  $\rho$  is electrical resistivity. The current density in the Al trace when powered by 0.59 A is approximately  $1\times10^6$  A/cm². For a complete SnAg bump used in this study, the corresponding current density is

Fig. 5. The measured temperature increase in Bumps 1 and 2 as a function of applied currents.

approximately  $10^4$  A/cm². Because the electrical resistivity of Al is  $2.6~\mu\Omega\cdot cm$  while  $12.3~\mu\Omega\cdot cm$  for the eutectic SnAg solder, the heating power per unit volume is approximately 2,000 times larger than that of the solder. Thus, the major heat source is the Al trace. However, the current density in Bump 2 is about 7 times larger than that in a complete bump, raising the heating power per unit volume to 1/40 of that in the Al trace. In addition, most of the solder was surrounded by the underfill, which is a poor heat conductor as seen in Table II. Therefore, it is possible that the heat generated in the solder may influence the thermal gradient and temperature increase in smaller solder bumps.

| Table II. Material Properties Used in the Lumped Thermal-Resistance Model |                                                                                                  |              |                      |                       |  |  |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------|----------------------|-----------------------|--|--|

| Material                                                                  | Chip                                                                                             | Solder       | Underfill            | Substrate             |  |  |

| Thermal conductivity (W/m °C) Thermal resistance (°C/W)                   | $     \begin{array}{r}             \hline             147 \\             72.15     \end{array} $ | 50<br>741.53 | $0.5 \\ \sim 20,000$ | $0.17 \\ \sim 75,000$ |  |  |

Chip

Chip

Underfill

Solder

Uuderfill

Substrate

Runderfill

Rsolder

Runderfill

Rsubstrate

Fig. 6. Lumped thermal-resistance model for the flip-chip package used in this study.

Furthermore, heat dissipation may play a crucial role in the temperature increase and thermal gradient. From a lumped thermal-resistance model shown in Fig. 6, thermal resistance can be calculated on the basis of the material properties listed in Table II. It is obvious that most of the generated heat flows through the chip side instead of the substrate side based on the thermal model. The thermal gradient inside the solder could be affected by the dominant heat sources, either generated from the Al trace or from the solder itself. If the heat generated from the Al trace is dominant over the solder itself, the thermal gradient inside the solder could be positive; if the heat generated from the solder itself is dominant over the Al trace, the thermal gradient inside the solder could be negative.

Therefore, we expect Bump 2 to possess negative thermal gradients under the stressing conditions because the major heat generated is the solder itself, and most of the heat dissipates through the Si chip. With the Cu heat spreader, the thermal resistance in the chip side was reduced significantly, resulting in a much lower temperature increase. Nevertheless, the

thermal gradient was less affected because the paths of heat dissipation remained unchanged when the heat spreader is added.

### **CONCLUSIONS**

In summary, the thermal gradient and temperature increase in the SnAg3.5 solder bumps have been measured under different stressing conditions. The temperature rise in the bump increased with the stressing current. It rose to 54.5°C when powered by 0.59 A, but it descended to 19.1°C when a Cu heat spreader was attached to the Si chip side. Both positive and negative thermal gradients were observed under different stressing conditions. The magnitude of the thermal gradients increased as the applied power increased, and it reached 365°C/cm as powered by 0.59 A. However, no obvious thermal gradient was observed when the bumps are powered less than 0.25 A.

#### ACKNOWLEDGEMENTS

The authors thank Professor K.N. Tu, UCLA, for helpful discussions and the National Science Council of Republic of China for the financial support of this study through Grant No. 90-2216-E-009-042.

# REFERENCES

- International Technology Roadmap for Semiconductors: Assembly and Packaging Section (San Jose, CA: Semiconductor Industry Association, 2003), pp. 4–9.

- 2. K.N. Tu, J. Appl. Phys. 94, 5451 (2003).

- 3. S. Brandenburg and S. Yeh, Proc. Surface Mount Int. Conf. Exhib. (Edina, MN: SMTA, 1998), pp. 337–344.

- C.Y. Liu, C. Chen, C.N. Liao, and K.N. Tu, Appl. Phys. Lett. 75, 58 (1999).

- T.Y.T. Lee, T.Y. Lee, and K.N. Tu, Proc. 51st Electronic Components Technology Conf. (Piscataway, NJ: IEEE, 2001), pp. 558–563.

- W.J. Choi, E.C.C. Yeh, and K.N. Tu, J. Appl. Phys. 94, 5665 (2003).

- H. Ye, C. Basaran, and D. Hopkins, *Appl. Phys. Lett.* 82, 7 (2003)