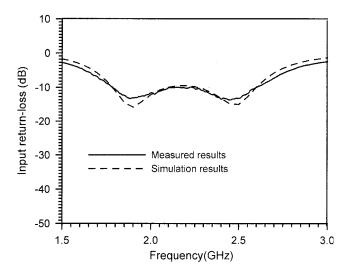

Figure 2 Measured and simulated input-return losses of the nonuniform-width folded-slot antenna fed by CPW

GHz, and a broader bandwidth of 37.4% (1.78–2.60 GHz) for VSWR < 2, which agrees well with the simulation results.

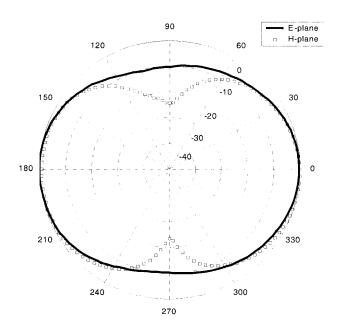

Figure 3 shows the normalized radiation patterns of the foldedslot antenna for the E- and H-planes, operating at the ISM band. These patterns were measured in the anechoic chamber of the Electrical Engineering Department of National Taiwan University. Because of the antenna's balanced feeding port, the radiation patterns appear to be rather symmetric. Comparing the measured data of the electric field at different frequencies, we find that the gain is about 4 dBi and the variation less than 1 dB over the desired frequency range. The gain variation is always obvious over the wide bandwidth on the slot antenna [6].

# 6. CONCLUSION

Using a nonuniform-width slot, we have presented a folded-slot antenna fed by CPW with tuning slits. The measured results show

**Figure 3** Measured radiation patterns for the CPW-fed nonuniform-width slot antenna for the E-plane (solid line —) and H-plane ( $\square$   $\square$   $\square$   $\square$  at the ISM band

that the device's bandwidth is broader than that of a conventional folded-slot antenna. In addition, it is applicable on an MMIC device because it does not occupy an unacceptably large space.

### REFERENCES

- B.K. Kormanyos, W. Harokopus, L. Katehi, and G. Rebeiz, CPW-fed active slot antennas, IEEE Trans Microwave Theory Tech MTT-42 (1994), 541–545.

- A.A. Eldek, A.E. Elsherbeni, C.E. Smith, and K.F. Lee, Wideband rectangular slot antenna for personal wireless communication systems, IEEE AP-Antennas Propagat Mag 44 (2002), 146–155.

- S.G. Santiago and J.J. Caurin, Study of a CPW inductively coupled slot antenna, IEEE Trans Antennas Propagat AP-47 (1999), 58-64.

- 4. H.S. Tsai and R.A. York, Multi-slot  $50\Omega$  antennas for quasi-optical circuits, IEEE Microwave Guided Wave Lett 5 (1995), 180-182.

- S.V. Robertson, N.I. Dib, G. Yang, and L.P.K. Katehi, A folded-slot antenna for planar quasi-optical mixer applications, IEEE AP-S Int Symp Dig, Columbus, OH (1993), 600–603.

- A.U. Bhobe, C.L. Holloway, M. Piket-May, and R. Hall, Coplanar waveguide fed wideband slot antenna, Electron Lett 36 (2000), 1340– 1342

- © 2004 Wiley Periodicals, Inc.

# HIGH-PERFORMANCE BULK AND THIN-FILM MICROSTRIP TRANSMISSION LINES ON VLSI-STANDARD SI SUBSTRATES

C. C. Chen, B. F. Hung, Albert Chin, and S. P. McAlister Institute of Electronics

National Chiao Tung University

Hsinchu, Taiwan, R.O.C.

National Research Council of Canada

Ottawa, Canada

Received 18 March 2004

ABSTRACT: Microstrip transmission lines with very low power loss of 0.4 dB/mm at 50 GHz have been fabricated on Si substrates using an optimized ion-implantation process. These devices have the inherent advantages of smaller chip size and better power performance than CPW lines. Using the same approach, high-performance thinfilm microstrip lines are also developed, showing a loss of 0.9 dB/mm at 20 GHz. This approach is compatible with existing VLSI backend layout technology. © 2004 Wiley Periodicals, Inc. Microwave Opt Technol Lett 43: 148–151, 2004; Published online in Wiley InterScience (www.interscience.wiley.com). DOI 10.1002/mop. 20404

**Key words:** microstrip lines; Si; ion implantation; CPW; thin-film; VLSI

### 1. INTRODUCTION

Scaling of Si device technology into the nm-scale regime yields Si transistors with performance reaching into the sub-THz range [1]. However, the performance of MMICs on Si substrates is inferior to those on semi-insulating GaAs ( $\sim 10^7~\Omega$ -cm) due to the large loss of passive devices on low-resistivity Si (10  $\Omega$ -cm) substrates [2, 3]. To overcome this problem, we have previously proposed and demonstrated a method to reduce the large RF loss in standard Si substrates using ion implantation, which can selectively form high-resistivity ( $10^6~\Omega$ -cm) regions in VLSI-standard Si substrates ( $10~\Omega$ -cm) [4–7]. Excellent coplanar waveguide (CPW) transmission lines with only 0.6-dB loss at 110 GHz [8], as well as

CPW-based broadband filters with small insertion loss (1.6 dB) and 10 GHz bandwidth at 91 GHz [9], have been demonstrated using this technique. In this paper, we successfully demonstrate high-performance microstrip lines on Si substrates. Using protonion implantation, the power loss of the microstrip transmission line is reduced significantly from 6.7 dB/mm to only 0.4 dB/mm at 50 GHz. In addition, we also fabricate thin-film microstrip transmission lines using current VLSI backend interconnect processes with a loss of ~0.9 dB/mm at 20 GHz. This approach has the inherent merit of being fully compatible with current VLSI technology without requiring additional masks or process steps.

### 2. DESIGN PROCESS

Standard 10  $\Omega$ -cm resistivity Si wafers of 200- $\mu$ m thickness were used in this study. Bulk microstrip transmission lines were fabricated on 1.5- $\mu$ m-SiO<sub>2</sub>/Si substrates using 4- $\mu$ m-thick A1 of 3-mm length and 60- $\mu$ m width. Thick A1 was deposited on the backside of the wafer to form the bulk microstrip transmission line. For thin-film microstrip transmission lines, a 0.75-mm-length and 20- $\mu$ m-width strip was formed using the top metal layer (metal-6) of a conventional VLSI backend process, with the first metal layer used as the ground plane. Two-port S-parameters were measured up to 50 GHz using an HP8510C network analyzer.

### 3. EXPERIMENTAL RESULTS AND DISCUSSION

### 3.1. Bulk Microstrip Lines on Si

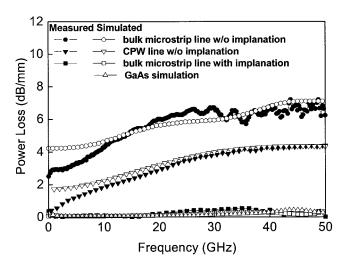

Figure 1 shows the power loss for a 3-mm-long microstrip line on 1.5- $\mu$ m SiO<sub>2</sub>-isolated Si, where the loss increases from 2.8 dB/mm to 6.7 dB/mm as the frequency increases to 50 GHz. This loss is greater than that of the CPW transmission line, as shown in Figure 1, over the same frequency range. The larger loss in the microstrip transmission line than in the CPW line is due to the vertical EM field being fully inside the lossy Si substrate, whereas the horizontal EM field in CPW line is only partially within the Si substrate

The increasing power loss at high frequency is an issue for Si RF IC technology, since future wireless communications require higher frequencies and bandwidths. As shown in Figure 1, our microstrip transmission lines with proton implantation show an improved power loss of  $\leq$ 0.4 dB/mm at 50 GHz. This value is

**Figure 1** Measured and EM-simulated power loss of 3-mm-long bulk microstrip transmission lines. For comparison, results for a 1-mm-long CPW line are included. Implantation produces a large loss reduction, from 6.7 dB/mm to 0.4 dB/mm at 50 GHz

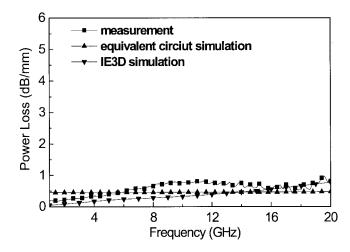

**Figure 2** Measured and EM-simulated power loss of 0.75-mm-long thin-film microstrip transmission lines. The measured loss at 20 GHz is <1 dB/mm, that is much lower than the bulk CPW (3 dB/mm) and microstrip lines (6 dB/mm) in Fig. 1 without implantation

similar to that of CPW transmission lines with the same ion implantation [6, 8] and comparable to the loss in semi-insulating GaAs obtained from EM simulation using IE3D.

### 3.2. Thin-film Microstrip Lines on Si

Using the same approach of forming a high-resistivity layer by proton implantation, we have also designed and fabricated thinfilm microstrip transmission lines. The isolation layer is from the multiple layers of  $\mathrm{SiO}_2$  used in the VLSI backend process. Figure 2 shows the measured and EM-simulated power loss. As can be seen, the power loss is  $\sim\!0.9$  dB/mm at 20 GHz, which is much lower than that of the unimplanted bulk CPW and microstrip lines shown in Figure 1. Although the loss of the thin-film microstrip line at 20 GHz is larger than the 0.25 dB/mm in ion-implanted bulk microstrip lines, this process uses simple layout technology without adding additional mask and process.

Because the transmission line is a passive device, the RF loss L is equivalent to the generated noise [8] with equivalent noise temperature of  $(L-1)T_0$ . The noise from advanced 0.18- $\mu$ m and 0.13- $\mu$ m MOSFETs is ~2.5 dB at 20 GHz [10], whereas the unimplanted CPW and microstrip transmission lines typically

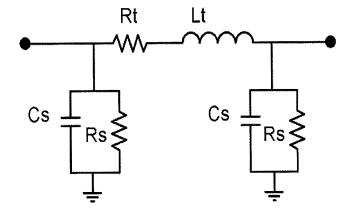

**Figure 3** Physically based equivalent circuit for the microstrip transmission lines (Lt is the line inductor, Rt is the parasitic resistor of the transmission line). The substrate loss is modeled by the shunt Rs and Cs to ground

10show larger noise and would dominate the overall noise floor of an RF system. However, the noise floor can be significantly reduced by using the thin-film microstrip line, even for a length as long as 1 mm. Further improvement may be possible by improving the dielectric loss of the low-temperature-formed SiO<sub>2</sub> or by increasing the thickness of the dielectric layer. This will be possible using the advanced 1-poly-9-metal layer (1P-9M) process of the 90-nm technology node and beyond. This will further reduce the performance gap with the bulk microstrip transmission line using proton implantation or that on GaAs, with the inherent merit of only changing the layout of current VLSI.

# 3.3. Modeling and Analysis

We use the physically based equivalent-circuit model shown in Figure 3 to simulate the S-parameters. Lt and Rt are the series

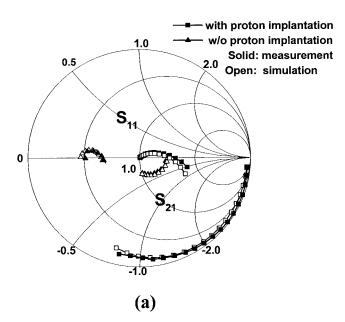

**Figure 4** Measured and equivalent-circuit modeled *S*-parameters of (a) bulk and (b) thin-film microstrip transmission lines on Si substrates. The effect of proton implantation is shown in (a). The different curve lengths are due to different frequency ranges: 50 GHz in (a) and 20 GHz in (b)

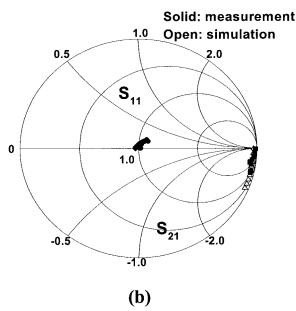

**Figure 5** Extracted magnitude of the substrate impedance/mm derived from the bulk and thin-film microstrip transmission lines. The effect of proton implantation is to increase the substrate impedance and thus reduce the loss of the bulk microstrip transmission line

inductor and parasitic resistor from the long microstrip transmission-line body, respectively. The symmetrical Rs and Cs at the respective input and output ports represent the RF signal losses to the ground plane, which should be large for the bulk microstrip line formed on VLSI-standard low resistivity Si substrate (10  $\Omega$ -cm) without ion implantation.

The measured and simulated S-parameters of the bulk and thin-film microstrip transmission lines, with or without implantation, are shown in Figures 4(a) and 4(b). Good agreement is obtained between the measured and modeled S-parameters, suggesting that the equivalent-circuit model in Figure 3 is appropriate.

The extracted substrate impedances, deduced from the Rs-Cs subcircuits for both bulk and thin-film microstrip transmission lines, are shown in Figure 5. For the bulk microstrip lines on standard Si, the proton implantation can increase the substrate impedance by more than one order of magnitude. For the thin-film microstrip lines, the relatively high substrate impedance arises from the high-resistivity  $SiO_2$  dielectric inside the microstrip-line body.

### 4. CONCLUSION

We have achieved extremely low power loss for both bulk (0.4 dB/mm at 50 GHz) and thin-film (0.9 dB/mm at 20 GHz) microstrip transmission lines on VLSI-standard Si substrates. Proton implantation has selectively transformed the low-resistivity Si substrates of the bulk microstrip transmission line into a high-resistivity state. The high performance of thin-film microstrip line results from the high-resistivity SiO<sub>2</sub>-dielectric being inside the microstrip-line body. Both transmission lines can be integrated into RF circuits and distributed devices at a reduced size, as compared with the use of CPW lines.

### **ACKNOWLEDGMENT**

We would like to thank Dr. G. W. Huang at NDL for helping with the measurements. This work has been supported by NSC (92-2215-E-009-017).

# REFERENCES

B. Yu, H. Wang, A. Joshi, Q. Xiang, E. Ibok, and M.-R. Lin, 15-nm gate length planar CMOS transistor, Int Electron Dev Mtg (IEDM) Tech Dig (2001), 937–939.

- T. Ohguro, K. Kojima, H.S. Momose, S. Nitta, T. Fukuda, T. Enda, and Y. Toyoshima, Improvement of high resistivity substrate for future mixed analog-digital application, VLSI Tech Symp Dig (2002), 158–159.

- E.C. Park, S.H. Baek, T.S. Song, J.B. Yoon, and E. Yoon, Performance comparison of 5GHz VCOs integrated by CMOS compatible high Q MEMS inductors, IEEE MTT-S Int Microwave Symp Dig, Philadelphia, PA (2003), 721–724.

- 4. A. Chin, K. Lee, B.C. Lin, and S. Horng, Picosecond photoresponse of carriers in Si ion-implanted Si, Appl Phys Lett 69 (1996), 653–656.

- Y.H. Wu, A. Chin, K.H. Shih, C.C. Wu, S.C. Pai, C.C. Chi, and C.P. Liao, RF loss and cross talk on extremely high resistivity (10K-1M-cm) Si fabricated by ion implantation, IEEE MTT-S Int Microwave Symp Dig (2000), 241–244.

- K.T. Chan, A. Chin, C.M. Kwei, D.T. Shien, and W.J. Lin, Transmission-line noise from standard and proton-implanted Si, IEEE MTT-S Int Microwave Symp Dig, Pheonix, AZ (2001), 763–766.

- K.T. Chan, A. Chin, Y.B. Chen, Y.-D. Lin, D.T.S. Duh, and W.J. Lin, Integrated antennas on Si, proton-implanted Si and Si-on-quartz, Int Electron Dev Mtg (IEDM) Tech Dig (2001), 903–906.

- K.T. Chan, A. Chin, S.P. McAlister, C.Y. Chang, V. Liang, J.K. Chen, S.C. Chien, D.S. Duh, and W.J. Lin, Low RF loss and noise of transmission lines on Si substrates using an improved ion implantation process, IEEE MTT-S Int Microwave Symp Dig 2, Philadelphia, PA (2003), 963–966.

- K.T. Chan, A. Chin, J.T. Kuo, C.Y. Chang, D.S. Duh, W.J. Lin, C.X. Zhu, M.F. Li, and D.L. Kwong, Microwave coplanar filters on Si substrates, IEEE MTT-S Int Microwave Symp Dig 3, Philadelphia, PA (2003), 1909–1912.

© 2004 Wiley Periodicals, Inc.

# CHARACTERIZATION OF RESISTIVE-LOADED WIRE LOOP IN UWB (IMPULSE) RADIO

### Hui Feng Li,1,2 Zhi Ning Chen,1 and Le-Wei Li2,3

Department of Radio Systems

Institute for Infocomm Research

Science Park Road, #02-21/25 TeleTech Park

Singapore 117674

Department of Electrical and Computer Engineering

National University of Singapore

Kent Ridge Crescent

HPCES Programme, Singapore-MIT Alliance

National University of Singapore

Kent Ridge Crescent

Kent Ridge Crescent

Singapore 119260

Received 31 March 2004

ABSTRACT: This paper discusses the applicability of loaded circular-loop antennas for impulse radio systems using a time-domain integral-equation (TDIE) method. The circular loops loaded with lumped and distributed resistances are characterized for pulse radiation and reception. The effects of the loads on the current distributions are investigated. The performance of the system comprising two identical loop antennas is examined and validated by measurement for ultra-wideband applications. © 2004 Wiley Periodicals, Inc. Microwave Opt Technol Lett 43: 151–156, 2004; Published online in Wiley InterScience (www.interscience.wiley.com). DOI 10.1002/mop.20405

**Key words:** time-domain integral equations; loaded loop antennas; transient response; ultra-wide band

### 1. INTRODUCTION

Recently, the applications of ultra-wideband (UWB) technology to commercial radio systems have gained increasing interest from both academia and industry. UWB systems usually require antennas to be broadband, small in size, and omnidirectional. There are many proposed antennas for UWB systems, such as thin wire monopoles, planar monopoles, loop antennas, and so forth. Among them, the loop antenna in a simple form has the advantages of small size and omnidirectional features, but its impedance bandwidth is narrow. Similar to straight dipoles and monopoles, loading techniques can be used to broaden the bandwidth of a loop antenna. This paper investigates the effects of the applied load on the performance of the loop antenna for UWB impulse radio.

A lot of work has been done on the transient response of loop antennas [1–4]. For example, the singularity expansion method (SEM) was successfully applied to the broadband equivalent circuit synthesis of circular-loop antennas for the perfectly conducting loop and uniformly loaded loop. However, the SEM cannot easily analyze a loop with a nonuniform load. Therefore, the time-domain integral-equation (TDIE) method, which is capable of modeling various load schemes, is selected for the analysis of loaded-loop antennas.

In this paper, circular loops loaded with lumped and distributed resistances are investigated. The effects of the load are discussed with the aid of snapshots of the currents on the loops. The efficiency of the loop antennas with different load schemes is compared and discussed. The radiation patterns over a wide frequency range are examined. To evaluate the reception ability, the normalized sensitivity is calculated. The voltage-transfer functions and received pulses for antenna systems built with such loops are compared and validated by measurements.

### 2. ANTENNA GEOMETRY AND LOAD SCHEMES

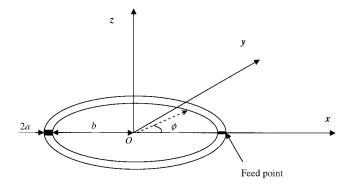

Figure 1 shows the geometry of the circular-loop antenna under study. The loop radius is b=13 mm and the wire radius is a=0.5 mm. Therefore, the shape factor of the loop is  $\Omega=2\ln(2\pi b/a)=10.2$ . The internal impedance at the feed point is  $100\Omega$ . The angle  $\phi$  represents the position on the loop. To investigate the characteristics of the loaded loops, four load schemes are considered.

## 2.1 Perfectly Conducting Loop

This is a closed and perfectly conducting wire-loop antenna.

### 2.2 Lumped Absorbing Load

The lumped resistive load at the position  $\phi = \pi$  is 240 $\Omega$ , which is called the absorbing load in this paper. The optimized absorbing load results in very little or no ringing in the late time of the

Figure 1 Geometry of the loop antenna