- [5] Richard G. Cosway and Michael W. Hodel, "Effect of RTA on thin thermal oxide," J. Electrochem. Soc., vol. 135, p. 533, 1988.

- [6] H. Wendt, A. Spitzer, W. Bensch, and K.V. Sichart, "Improvement of oxide quality by rapid thermal annealing," J. Appl. Phys., vol. 67, p. 7531, 1990.

- [7] J. C. Hsieh, Y. K. Fang, C. W. Chen, N. S. Tsai, M. S. Lin, and F. C. Tseng, "Study and improvement of anomalous interface state of metal-oxide-semiconductor structure induced by rapid thermal post-oxide annealing," *J. Appl. Phys.*,vol. 73, p. 5432, 1993.

- [8] P. Heremans, J. Witter, G. Groeseneken, and H. Maes, "Analysis of the charge pumping technique and its application for the evaluation of MOSFET degradation," *IEEE Trans. Electron Devices*, vol. 36, p. 1318, 1989.

- [9] W. Chen, A. Balasinski, and T. P. Ma, "Lateral profiling of oxide charge and interface traps near MOSFET junctions," *IEEE Trans. Electron Devices*, vol. 40, p. 187, 1993.

- [10] E. H. Nicollian and J. R. Brews, MOS (Metal-Oxide-Semiconductor) Physics and Technology. New York: Wiley, 1982, chap. 16.

- [11] P. L. Castro and B. E. Deal, "Low-temperature reduction of fast surface states associated with thermally oxidized silicon," *J. Electrochem. Soc.: Solid-state Science and Technology*, vol. 118, p. 280, 1971.

## Correlation of Polysilicon Thin-Film Transistor Characteristics to Defect States via Thermal Annealing

Horng Nan Chern, Chung Len Lee, and Tan Fu Lei

Abstract—Based on the response of electrical characteristics of hydrogenated polysilicon thin-film transistors (TFT's) to post-hydrogenation thermal annealing, the relationship of device parameters to deep states and tail states are distinguished. The deep states which affect the threshold voltage and subthreshold swing recover quickly, while the tail states which influence the leakage current and field effect mobility respond to the thermal annealing only after the annealing temperature exceeds 375°C for 30 min.

### I. INTRODUCTION

To realize high-performance TFT's, it is necessary to reduce the defects of the polysilicon film. When polysilicon TFT's are subjected to  $\rm H_2$  plasma treatment, their defect states are reduced and the performance is improved [1]-[5]. Recently, the passivation mechanisms of the  $\rm H_2$  plasma treatment on defect states in the polysilicon film have been widely investigated [2]-[5]. It is generally recognized that the density of defect states in the polysilicon is continuous across the forbidden band gap [6], and the deep-states and the tail-states have different effects on the characteristics of

Manuscript received December 7, 1992; revised September 21, 1993. The review of this brief was arranged by Associate Editor Y. Nishi. This work was supported in part by the National Science Council of the R.O.C. through contract NSC-81-0404-E009-138.

The authors are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, R.O.C.

IEEE Log Number 9215149.

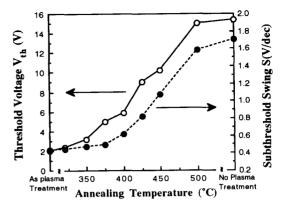

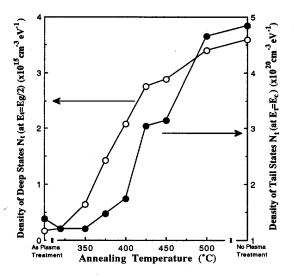

Fig. 1. The variation of (a) threshold voltage and subthreshold swing, and (b) minimum drain current measured at Vd=5 V and field effect mobility after thermal annealing at the temperature range from 320°C to 500°C. The characteristics of as plasma-treated and no plasma-treated devices are also shown for comparison.

polysilicon TFT's [2]–[5]. Migliorato and Meakin [2] found that the deep-states associated with dangling bonds result in high generation rates and anomalous off current, while the tail-states associated with the local disorder pin the Fermi-level and lead to a high threshold voltage and a low field effect mobility. From the on-state current simulation, A. Ono et al. [5] obtained the same results. On the other hand, different relationship was reported by B. A. Khan et al. [4] and I.-W. Wu et al. [3]. They found that the leakage current is dominated by the tail state density. In this brief, the correlation of polysilicon TFT characteristics to defect states is studied through post-hydrogenation thermal annealing. Experimentally, it is found that the deep states which affect the threshold voltage  $(V_{\rm th})$  and subthreshold swing (5) recover quickly under the thermal annealing, and the tail states which influence the leakage current  $(I_{\rm off})$  and field effect mobility  $(\mu)$  respond slowly to the thermal annealing.

## II. EXPERIMENTS

Amorphous silicon films of thickness 1100 Å were deposited on thermally oxidized silicon wafers by a low-pressure chemical vapor

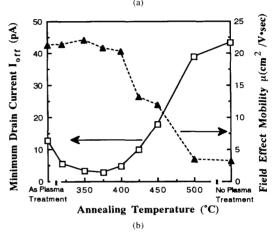

Fig. 2. The experimental (symbols) and calculated results (solid lines) of  $V_{\rm th}(T)$  for as plasma-treated, 350°C, 400°C, 450°C annealed and no plasma-treated devices. The derived  $N_{\rm tc}({\rm cm}^{-3}~{\rm eV}^{-1})$  and  $T_g$  values are also shown for each device.

deposition (LPCVD) system at  $550^{\circ}$ C. The wafers were then annealed at  $550^{\circ}$ C for 48 hours in an  $N_2$  ambient to transform the film to polysilicon. After defining the active islands, 750 Å gate oxide was grown in dry  $O_2$  at  $1000^{\circ}$ C. Another 3500 Å polysilicon film was then deposited at  $625^{\circ}$ C by the LPCVD system to be the gate electrode. After defining the gate length,  $5 \times 10^{15}$  cm<sup>-2</sup> phosphorous was implanted to dope the source, drain and gate. The dopants were activated at  $900^{\circ}$ C for 30 min in  $N_2$  gas. Hydrogenation was performed in a commercial 13.56 MHz parallel-plate plasma reactor with  $H_2$  and  $N_2$  gas mixture at  $300^{\circ}$ C for 30 min. All wafers were then covered with 5000Å plasma-enhanced chemical vapor deposition (PECVD)  $SiO_2$  for passivation. Contact holes were opened, and A1 + 1%Si was deposited and then patterned. Finally, the wafers were subjected to thermal annealing at the temperature range of  $320^{\circ}$ C- $500^{\circ}$ C for 30 min in  $N_2$  ambient.

### III. RESULTS AND DISCUSSIONS

The threshold voltage  $(V_{\rm th})$  and subthreshold swing (S) and the minimum drain current ( $I_{\rm off}$ ) and field effect mobility ( $\mu$ ) after thermal annealing for different annealing temperatures are plotted in Fig. 1 (a) and (b), respectively. The field effect mobility is measured in the linear region at  $V_d = 0.1$  V, and at the maximum transconductance. The  $V_{

m th}$  increases with the annealing temperature and the S increases slightly at the low annealing temperature (< 375°C) and increases rapidly at the higher annealing temperature. For  $I_{\text{off}}$  and  $\mu$ , they do not respond to the thermal annealing until the annealing temperature is greater than 375°C. These two different types of responses of device parameters to the annealing imply that different kinds of defect states are involved during the annealing. From the data of Fig. 1 (a) and (b), it can be derived that  $V_{\rm th}$  and S are related to the same type of defect states which recover quickly under the annealing, and  $I_{\rm off}$  and  $\mu$  are related to another type of defect states which have a stronger S-H bonding and recover only at the annealing temperature above 375°C. It had been experimentally demonstrated that for the band tail states [6], the density of defect states  $(N_t)$  can be expressed in an exponential form in the energy bandgap as  $N_t(E_t) = N_{tc} \cdot \exp[(E_t - E_c)/kT_g]$ , where the  $N_{tc}$  is the defect state density at conductance band  $E_c$ ,  $E_t$  is the energy level of the defect state and  $T_g$  is a characteristic parameter of defect states. Using the above exponential distribution of defect states,

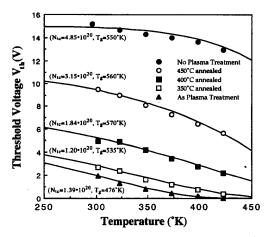

Fig. 3. The derived values of the density of deep-states  $N_t$  (at  $E_t = E_g/2$ ) and tail-states  $N_t$  (at  $E_t = E_c$ ) with respect to the annealing temperature.

Fortunato and Migliorato [7] developed an analytical expression for the threshold voltage:

$$V_{\rm th} = \frac{t_{\rm ox}}{\varepsilon_{\rm ox}} \left( \frac{q \cdot N_c}{k \cdot T_g \cdot N_{\rm tc}} \right)^{\frac{T}{2(T - T_g)}} \times \left( \frac{2\varepsilon_s}{q} \cdot N_{\rm tc} \cdot (k \cdot T_g)^2 \cdot \left( 1 + \frac{T}{T_g} \right) \right)^{\frac{1}{2}}$$

(1)

where  $t_{ox}$  is the thickness of the gate oxide and T is the temperature. This value is very close to the extracted value from the intercept on the voltage axis of the straight line in the drain current  $I_d$  versus the gate voltage  $V_g$  plot [7]. Equation (1) can be fitted with our experimental data for  $V_{

m th}$  measured at the temperature range of 28°C ~ 150°C for our TFT's annealed at different temperatures. These fittings are shown in Fig. 2, and the derived  $N_{

m tc}$  and  $T_g$  values are also shown for each device. A good agreement with the experiment is found. The derived values for  $T_g$  are in the range of 476°K to 570°K which are very closed to the values reported in the literature [6]. The extracted values for the deep-state and tail-state density are plotted in Fig. 3 with respect to the annealing temperature. It can be seen that the tail-state density does not respond, in fact, decreases slightly, to the annealing until the annealing temperature reaches 375°C. This behavior is very consistent with those of  $I_{\rm off}$  and  $\mu$ of Fig. 1 (b), where  $I_{\rm off}$  and  $\mu$  decreases and increases slightly respectively in the temperature range of 320°C and 350°C and then increases and decreases respectively after the annealing temperature exceeds 375°C. While the deep-state density, which is defined as the  $N_t$  (at  $E_t = E_a/2$ ), increases quickly with the annealing temperature. This behavior is the same as those of  $V_{\rm th}$  and S of Fig. 1 (a). This observed correlation of TFT characteristics to defect states can be explained as follows: As the device is operated from the OFF-state to the ON-state, the surface Fermi-level will move from the position of bulk Fermi-level toward  $E_c$ . If there are deep states, the gateinduced carriers will be trapped by these deep-states. Hence,  $V_{\rm th}$  as well as the subthreshold swing S are affected. As the device is fully turned on, the surface Fermi-level will move close to  $E_c$ . At this moment, it is the mobility which is affected by the tail states since the ON-state current is mainly determined by the mobility.

#### IV. CONCLUSION

The correlation of the electrical characteristics of polysilicon TFT to defect states has been studied through the post-hydrogenation thermal annealing. It is found that  $V_{\rm th}$  and S degrade quickly after annealing above 320°C for 30 min through the recovery of mid-gap deep-states, while  $I_{\rm off}$  and  $\mu$  respond slowly to annealing through the recovery of tail-states.

#### REFERENCES

- T. I. Kamins and P. J. Marcoux, "Hydrogenation of transistors fabricated in polysilicon films," *IEEE Electron Device Lett.*, vol. 1, p. 159, 1980.

- [2] P. Migliorato and D. B. Meakin, "Material properties and characteristics of polysilicon transistors for large area electronics," *Applied Surface Sci.*, vol. 30, p. 353, 1987.

- [3] I-W. Wu, T. Y. Huang, W. B. Jackson, A. G. Lewis, and A. Chiang, "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, p. 181, 1991.

- [4] B. A. Khan and R. Pandya, "Activation energy of source-drain current in hydrogenated and unhydrogenated polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 37, p. 1727, 1990.

- [5] K. Ono, T. Aoyama, N. Konishi, and K. Miyata, "Analysis of current-voltage characteristics of low-temperature-processed polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 39, p. 792, 1992.

- [6] H. J. Queisser and J. Werner, "Electrical and electronical properties of grain boundaries in silicon," in *Mat. Res. Soc. Symp. Proc.*, vol. 106, p. 53, 1988.

- [7] G. Fortunato and P. Migliorato, "Model for the above-threshold characteristics and threshold voltage in polycrystalline silicon transistors," *J. Appl. Phys.*, vol. 68, p. 2463, 1990.

# The Effects of Metal-n<sup>+</sup> Interface and Space Charge Limited Conduction on the Performance of Amorphous Silicon Thin-Film Transistors

Serag M. GadelRab and Savvas G. Chamberlain

Abstract—We derive a contact current density expression that accounts for both the metal- $n^+$  film interface resistance and the space charge limited conduction in amorphous silicon thin-film transistors. Our model demonstrates that the metal- $n^+$  interface behavior dominates over space charge limited conduction for the a-Si:H film thicknesses used in pixel switching.

## I. INTRODUCTION

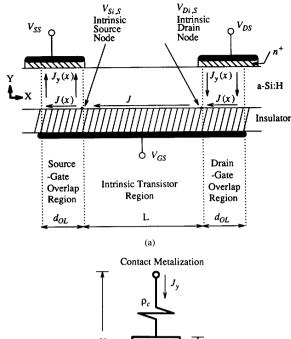

Amorphous silicon thin-film transistors (a-Si:H TFT's) form the basic building block for contact image sensors and active matrix LCDs. In such applications the resistances associated with the source and drain contacts significantly affect the TFT performance. Fig. 1(a) shows that an overlap exists between the source/drain contacts and the gate. The behavior of the TFT is independent of the overlap length,  $d_{\rm OL}$ , provided that the overlap is longer than a critical

Manuscript received June 9, 1993; revised October 12, 1993. The review of this brief was arranged by Associate Editor J. R. Pfiester. This work was supported in part by research funds from ITRC, NSERC, NCR Canada and in part by DALSA Inc.

The authors are with the Electrical and Computer Engineering Department, University of Waterloo, Waterloo, Ontario N2L 3G1, Canada.

IEEE Log Number 9214899.

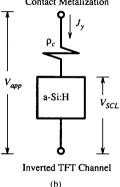

Fig. 1. (a) An idealized TFT structure showing the three regions of the TFT: two gate-contact overlap regions and an intrinsic TFT region. J(x) flows horizontally in the inverted channel while  $J_y(x)$  flows vertically between the channel and the contact metallizations. (b) A simple model representing the contact resistances.

length of approximately 1  $\mu$ m [1]. In this work  $d_{\rm OL}$  is assumed to be longer than this critical overlap length. The inverted channel current density, J (A/cm), flows at the gate-insulator/semiconductor interface. Within the gate-contact overlaps the contact limited current per unit contact area,  $J_y$  (A/cm²), flows vertically between the contacts and the channel.  $J_y$  is a function of the space charge limited (SCL) conduction through the intrinsic a-Si:H layer and the resistance of the metal- $n^+$  layer interface. The former was shown to be the dominant factor for a-Si:H layer thicknesses of  $\approx 0.2-0.3$   $\mu$ m [1]. Consequently, workers have ignored the interface resistance when formulating device models [2]–[4]. In this brief we develop an expression for  $J_y$  that accounts for both resistances. We then investigate the independent effects of the interface resistance and the SCL conduction on the TFT current by incorporating our  $J_y$  expression into a full TFT model.

Although a Schottky barrier is formed at the metal-n<sup>+</sup> interface, measurements have shown that it may be modeled as an ohmic element [5]. In this work we assume an ohmic contact with a