# Transient Effect Assisted NBTI Degradation in p-Channel LTPS TFTs under Dynamic Stress

Chia-Sheng Lin, Ying-Chung Chen, Ting-Chang Chang, b,c,d,\*,z Hung-Wei Li,e Shih-Ching Chen,<sup>b</sup> Wei-Che Hsu,<sup>b</sup> Fu-Yen Jian,<sup>c</sup> Te-Chih Chen,<sup>b</sup> and Ya-Hsiang Tai<sup>f</sup>

<sup>a</sup>Department of Electrical Engineering, <sup>b</sup>Department of Physics, <sup>c</sup>Institute of Electro-Optical Engineering, and <sup>d</sup>Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung, Taiwan 80424, Taiwan

$^e$ Department of Photonics and Institute of Electro-Optical Engineering and  $^f$ Department of Photonics and Display Institute, National Chiao Tung University, Hsinchu 30010, Taiwan

This work investigates dynamic negative bias temperature instability (NBTI) in p-channel low-temperature polycrystalline silicon thin-film transistors (LTPS TFTs) with different rise and fall times. Experimental results reveal identical increases in the interface state density  $(N_{ii})$  induced by different dynamic NBTI stress conditions. Nevertheless, the degradation of the grain boundary trap  $(N_{\text{trap}})$  becomes more significant as rise time decreases to 1  $\mu$ s. Because the surface inversion layer cannot form during the short rise time, transient bulk voltage will cause excess holes to diffuse into the poly-Si bulk. Therefore, the significant  $N_{\text{trap}}$  increase is assisted by this transient effect.

© 2010 The Electrochemical Society. [DOI: 10.1149/1.3507253] All rights reserved.

Manuscript submitted November 18, 2009; revised manuscript received October 7, 2010. Published November 11, 2010.

Low-temperature polycrystalline-silicon thin-film transistors (LTPS TFTs) have been widely investigated for flat-panel applications, such as for active matrix liquid crystal displays and active-matrix organic light-emitting diodes. 1-3 Compared to amorphous silicon thin-film transistors (a-Si TFTs), LTPS TFTs have a higher electron mobility and driving current. Since the maximum process temperature is lower than 600°C, LPTS TFTs can be fabricated on relatively cheap glass. Consequently, the LTPS TFTs can integrate both the pixel array and peripheral circuits on the same glass substrate to realize a system-on-panel display. <sup>4,5</sup> Because drive circuits are designed using a CMOS inverter and therefore must suffer dynamic voltage pulses, negative bias temperature instability (NBTI) in p-channel LTPS TFTs under dynamic stress has been reported to be an important problem.<sup>6-9</sup> However, most studies have emphasized the recovery effect for threshold voltage during the dynamic voltage stress and have discussed the relationship between NBTI degradation and stress-frequency. The dependence of NBTI degradation on the period of transient variation of stress bias has not been analyzed in detail.

This work studies the NBTI effect in p-channel LTPS TFTs under various rise and fall times by extracting the interface state density  $(N_{\rm it})$  and the grain boundary trap density  $(N_{\rm trap})$  after NBTI stresses. In addition, the waveform and transient current were monitored by digital oscilloscope during dynamic stress to investigate the mechanism of device degradation. This analysis observed an increase in the bulk voltage in the transient region of the poly-Si bulk, which causes a diffusion of excess holes into the bulk when rise time is very short. This transient effect, therefore, is responsible for further degradation of grain boundary trap density  $(N_{\text{trap}})$ .

# **Experimental**

In this work, the commercial standard p-channel LTPS TFTs fabricated on a Corning 1737 glass substrate with top-gate structures were prepared. First, a 500 nm thick buffer-oxide was deposited on the glass. Next, a 50 nm amorphous-Si (a-Si) film was deposited by plasma enhanced chemical vapor deposition (PECVD) at 380°C on the buffer-oxide, followed by dehydrogenation via furnace annealing process at 450°C. Then the a-Si films were crystallized by a 308 nm XeCl excimer laser with a line-shaped beam power of 350 mJ/cm<sup>2</sup>. After patterning the films of polysilicon, 80 nm thick gate insulator was deposited by tetraethyl orthosilicate base oxide and 300 nm Mo

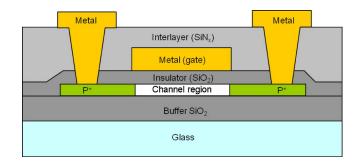

was deposited as a gate metal by sputtering. After the gate metal definition process, the overlap between the gate and the source/drain regions are defined 0.75 µm and self-aligned boron implantation with a dose of 2  $\times$  10<sup>15</sup> cm<sup>-2</sup> to form the P<sup>+</sup> regions at source/drain regions. The rapid thermal anneal irradiation process was performed to activate the dopant impurities after the source/drain regions implantation. The NH<sub>3</sub> plasma treatment was performed at 300°C to passivate the dangling bonds at the poly-Si/SiO2 interface and at the grain boundaries. A 500 nm SiN<sub>x</sub> layer was deposited by the PECVD as the interlayer dielectric. Finally, the contact holes were patterned by dry etching and Al metallization was performed. The cross-sectional view of the p-channel LTPS TFT is shown in Fig. 1. The thin-film transistors (TFTs) studied in this work are 6 µm in length and 10 µm in width.

The I-V curves and pulse waveform were measured by a Keithley 4200 semiconductor parameter analyzer and an Agilent DSO8104A digital oscilloscope, respectively. The measurements subsequent to the stress condition were performed with gate voltage sweeping from 5 to - 10 V, and the drain voltage was set to -0.1~V.

## **Results and Discussion**

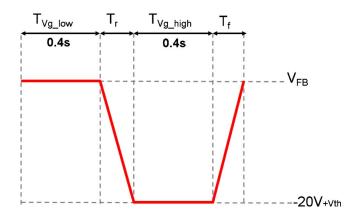

The dynamic NBTI stress waveform is shown in Fig. 2. A pulse with amplitude between 0 and -20 V was applied to the gate while source/drain were grounded. During the dynamic stress operation, times of high and low levels in the pulse period were fixed at 0.4 s and represented by  $T_{\rm vg\_high}$  and  $T_{\rm vg\_low},$  respectively. The transient times of the gate pulse when switched from 0 to -20 V and -20 to 0 V were defined as rise time  $(T_r)$  and fall time  $(T_f)$ . In order to investigate the relationship between transient effect and

Figure 1. (Color online) Cross-sectional views of p-channel LTPS TFTs.

Electrochemical Society Active Member.

<sup>&</sup>lt;sup>z</sup> E-mail: tcchang@mail.phys.nsysu.edu.tw

Figure 2. (Color online) Waveform of stress pulse applied to the gate.

dynamic NBTI induced degradation during the  $T_f$  and  $T_r$ , three stress conditions were performed. First, rise time and fall time were fixed to 0.1 s for standard NBTI stress. Either the rise time or fall time alone was reduced to 0.1  $\mu s$  for the other two conditions. In all three stress conditions, the number of gate pulses was set at 2000 and the temperature was set at 125 °C.

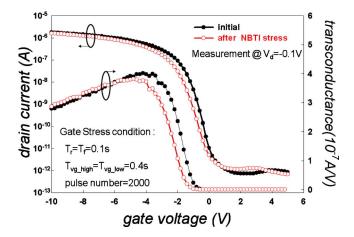

Figure 3 shows the linear  $I_d$ – $V_g$  transfer characteristics of LTPS TFTs at the initial status and after standard NBTI stress. Subthreshold swing (S.S), transconductance ( $g_m$ ), and on-current ( $I_{\rm on}$ ) were clearly degraded after the standard NBTI stress. In addition, the threshold voltage ( $V_{\rm th}$ ) after standard NBTI stress shifted in the negative direction. In general,  $V_{\rm th}$  shift of TFT is caused by charge trapping or defect creation in the gate oxide. However, since charge trapping requires a high electric field across the gate oxide (above 6 MV/cm),  $^{10}$  the electric field across this gate dielectric (about 3 MV/cm) is not high enough to cause hole injection. Therefore, the disorder-induced model could be eliminated.  $^{11,12}$  Consequently, in this work, the degradation observed in S.S,  $g_m$ , and  $I_{\rm on}$  can be considered to be mainly caused by conventional NBTI degradation.

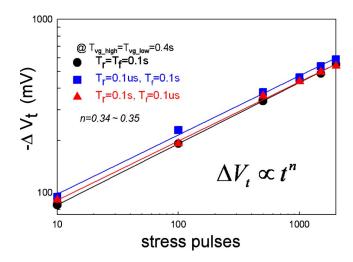

Figure 4 shows the negative shift of the threshold voltage  $(-\Delta V_{\rm th})$  as a function of stress pulse number under the different NBTI stress conditions. The  $V_{\rm th}$  was defined as the gate voltage at which the drain current equals 10 nA in the subthreshold region. It can be seen from Fig. 4 that these  $-\Delta V_{\rm th}$  increase with an increase in stress pulse number, showing power law dependence. The exponent factor n can be extracted from the power law relationship,  $V_{\rm th} = At^n$ , where n is approximately 0.34 in this experiment. This value indicates that the diffusion-controlled electrochemical reaction

**Figure 3.** (Color online)  $I_d$ – $V_g$  transfer characteristics when the device operates in the linear region for the LTPS TFT at the initial condition and standard NBTI stress condition.

Figure 4. (Color online) Relationship between negative threshold voltage shift and number of stress pulses.

is the principal degradation mechanism for all the NBTI stresses. These results are similar to those of our previous study,  $^{16}$  which found that NBTI degradation originated from the interface state ( $N_{\rm it}$ ) increase and grain boundary trap ( $N_{\rm trap}$ ) increase. In order to understand the influences of rise and fall times on NBTI stress more clearly, the  $N_{\rm it}$  and the  $N_{\rm trap}$  increase for all stress conditions will be analyzed.

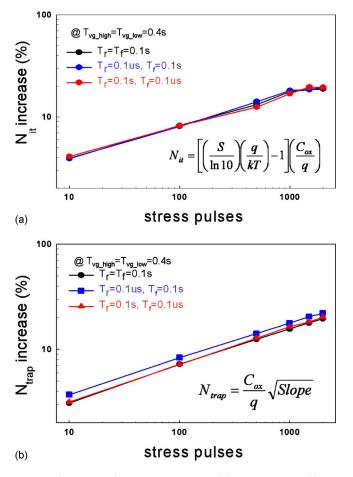

The  $N_{\rm it}$  can be extracted from the S.S by ignoring the depletion capacitance in the active layer according to the following equation, <sup>17</sup> with  $N_{\rm it}$  trap increase occurring not only at the SiO<sub>2</sub>/poly-Si interface but also in the grain boundary in the weak inversion region. Here, the subthreshold swing is defined as half the gate voltage necessary to increase the drain current by 2 orders of magnitude (from  $10^{-11}$  to  $10^{-9}$  A) in the subthreshold region

$$N_{\rm it} = \left[ \left( \frac{S}{\ln 10} \right) \left( \frac{q}{kT} \right) - 1 \right] \left( \frac{C_{\rm ox}}{q} \right)$$

[1]

Figure 5a shows the correlation between the  $N_{\rm it}$  increase and the number of stress pulses for the three different rise and fall times. It is apparent that the  $N_{\rm it}$  increase is independent of rise and fall times. The nearly identical  $N_{\rm it}$  increase for these different stresses is due to the same  $T_{\rm vg\_high}$  and  $T_{\rm vg\_low}$ . The degradation was mainly due to the H dissociation caused by inversion holes during  $T_{\rm vg\_high}$  and the dissociated H recovery during  $T_{\rm vg\_low}$ .

dissociated H recovery during  $T_{\rm vg\_low}$ .

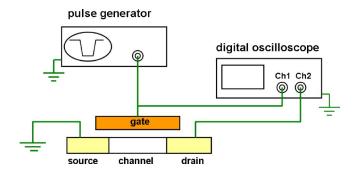

The  $N_{\rm trap}$  increase can be estimated by the Levinson and Proano method,  $^{4,18}$  such that it includes the  $N_{\rm it}$ . The relationship between the  $N_{\rm trap}$  increase and the number of stress pulses is shown in Fig. 5b, where it is clear that the  $N_{\rm trap}$  increase is more serious under stress with a shorter rise time but was independent of fall time. In n-channel TFTs, the main degradation mechanism was by the drainavalanched hot-carrier induced impact ionization as a result of carriers being emitted from trap states when fall time is less than 1 ms. 19 However, in our experiment, the turn-off voltage was only 0 V and the ionization rate of the hole was lower than the ionization rate of the electron.<sup>20</sup> Therefore, the degradation of the grain boundary near the source/drain caused by the emitted carriers did not occur in this experiment. In order to understand the dominant mechanism in the  $N_{\text{trap}}$  increase for the short rise time, both the input gate voltage and the corresponding bulk voltage ( $V_{\rm bulk}$ ) were monitored by a digital oscilloscope, as shown in Fig. 6. The source was grounded, and the drain was connected to the 2-channel of the digital oscilloscope while the temperature was 125°C. The pulse voltage was applied to gate from the pulse generator and was connected to the 1-channel.

**Figure 5.** (Color online) Relationship between (a)  $N_{\rm it}$  increase and (b)  $N_{\rm trap}$  increase under different number of stress pulses.

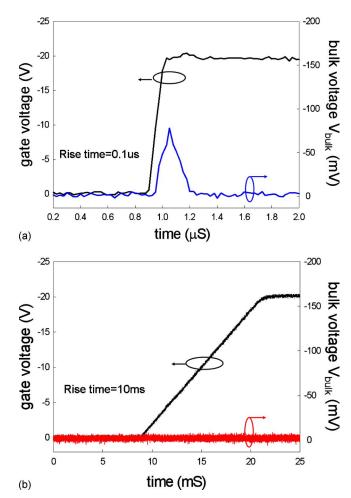

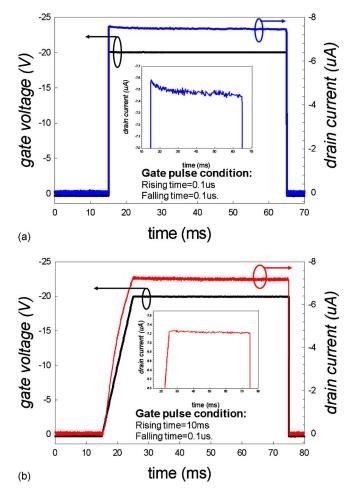

The relationship between the bulk voltage ( $V_{\rm bulk}$ ) and the gate voltage ( $V_g$ ) is shown in Fig. 7a and b for  $T_r$  of 0.1  $\mu s$  and 1 ms, respectively. It can be seen from Fig. 7a that there was a transient increase in the voltage of poly-Si bulk when the gate voltage was switched from 0 to -20 V in a very short rise time ( $T_r = 0.1$   $\mu s$ ). As the rise time is short, the inversion layer is not immediately formed at the interface between the SiO<sub>2</sub> and poly-Si, and the applied gate voltage is partially dropped at the bulk region, causing the transient bulk voltage increase. The typical turn-on time of the c-Si FETs is a few tens of nanoseconds. This experimental result suggests that the switching delay in LTPS TFTs can be attributed to the high trap density. Figure 7b shows the gate voltage switched from

**Figure 6.** (Color online) Schematic view of an installation used to monitor  $V_{\rm bulk}$ . The source was grounded, and the drain was connected to the 2-channel of the digital oscilloscope.

**Figure 7.** (Color online) Relationship between bulk voltage and gate voltage for rise times of (a)  $0.1 \mu s$  and (b) 10 ms.

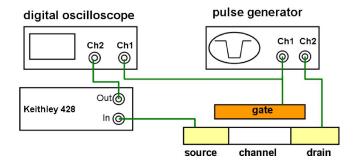

0 to -20 V over a long rise time ( $T_r = 10 \text{ ms}$ ). Clearly, the  $V_{\text{bulk}}$  remains at 0 V, even during the transient time, because the inversion charges move along the channel as the gate pulse varies, finally electrically connecting the source and the drain. Therefore, the  $V_{\text{bulk}}$  is the same as the source voltage. Based on these results, we further analyzed the transient effect on drain current using a transient measurement system, as shown in Fig. 8. The gate terminal was connected to the 1-channel of the pulse generator and the digital oscilloscope, and the gate bias was changed from 0 to -20 V. The drain was connected to the 2-channel of the pulse generator, which was switched from 0 to -0.1 V. The source was connected to the input of a current-to-voltage converter (Keithley 428) such that the output voltage signal and the corresponding drain current could be

Figure 8. (Color online) Schematic of the transient measurement system.

**Figure 9.** (Color online) Relationship between the transient drain current and the gate voltage for rise time of (a)  $0.1~\mu s$  and (b) 10~ms, insets show the transient drain current under turn-on region.

displayed by the 2-channel of the digital oscilloscope. The measurement temperature was set to  $125\,^{\circ}$ C. The result of the transient current measurement was shown in Fig. 9.

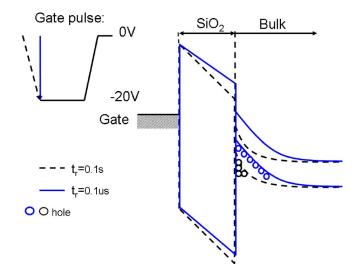

Figures 9a and b show the relationship between the gate voltage and the transient drain currents under rise times of 0.1 µs and 0.1 ms, and the insets show only the transient drain current during the turn-on region. It can be seen from Fig. 9a, that the measured drain current exhibits the peak current at the beginning of the turn-on region and slowly returns to a steady current with the increasing measurement time. This phenomenon can be explained by recalling that, in Fig. 7a, the inversion layer is not immediately formed at the SiO<sub>2</sub>/poly-Si interface, causing the transient bulk voltage in poly-Si bulk. When the negative voltage drops in the poly-Si bulk, holes will diffuse from the p-type source/drain into the Si bulk due to the forward bias. Therefore, excess holes cause the peak transient current to occur at the beginning of the turn-on region. The corresponding energy band diagram is shown in Fig. 10. On the contrary, for a long rise time of 10 ms, the transient current is fixed to the steady value (steady-state current) during the turn-on time because the holes (inversion charges) can respond to the variation in the gate voltage.

Figure 10 shows the schematic energy band diagram of LTPS TFTs during different rise times. In the short rise time because the inversion layer is not formed immediately during such a short rise time, surface band bending is not apparent and part of  $V_g$  becomes dropped into the poly-Si bulk, resulting in excess holes diffusing from the source/drain. This phenomenon is also consistent with the result shown in Fig. 7a and 9a. Because there are many passivated

**Figure 10.** (Color online) Energy band diagram of LTPS TFT under different rise times.

Si–H bonds in grain boundaries in the poly-Si bulk region, the reaction between the transient-effect-induced excess holes and the Si–H bonds will cause a more serious  $N_{\rm trap}$  increase in the poly-Si bulk during the NBTI stress. In addition, in the long rise time condition, the inversion layer forms immediately. Consequently, the main influence of the  $N_{\rm trap}$  increase was the steady-state current.

#### Conclusion

In this work, dynamic NBTI stress in p-channel LTPS TFTs under different rise and fall times is investigated. Degradation occurred to the threshold voltage, subthreshold swing, and on-current in all kinds of dynamic NBTI stresses. For shorter and longer pulse rise time, the  $N_{\rm it}$  increase is similar due to the dissociation of inversion holes and H at the interface at  $T_{\rm vg\_high}$ . Nevertheless, for a very short rise time, a pronounced  $N_{\rm trap}$  increase is observed. This is because the inversion layer is not formed immediately and part of the gate voltage  $\rm V_g$  is dropped into the poly-Si bulk, inducing excess holes. Therefore, the transient-effect-induced excess holes are the main reason for the more serious  $N_{\rm trap}$  increase in the poly-Si bulk.

### Acknowledgments

The work was supported by the National Science Council under contract NSC-99-2120-M-110-001 and 97-2112-M-110-009-MY3.

National Sun Yat-Sen University assisted in meeting the publication costs of this article.

### References

- H. Kuriyama, S. Kiyama, S. Noguchi, T. Kuahara, S. Ishida, T. Nohda, K. Sano, H. Iwata, S. Tsuda, and S. Nakano, Tech. Dig. Int. Electron Devices Meet., 1991, 563

- 2. W. B. Tam and T. Shimoda, SID Int. Symp. Digest Tech. Papers, 2004, 1406. 3. Y. Matsueda, R. Kakkad, Y. S. Park, H. H. Yoon, W. P. Lee, J. B. Koo, and H. K.

- Y. Matsueda, R. Kakkad, Y. S. Park, H. H. Yoon, W. P. Lee, J. B. Koo, and H. K. Chung, SID Int. Symp. Digest Tech. Papers, 2004, 1116.

- K. Yoneda, R. Yokoyama, and T. Yamada, in Symposium on VLSI Circuits Proceedings, IEEE, p. 85 (2001).

- H. Tokioka, M. Agari, M. Inoue, T. Yamamoto, H. Murai, and H. Nagata, Proc. Soc. Inf. Display, IEEE, 280 (2001).

Y. Toyota, M. Hatano, T. Shiba, and M. Ohkura, IEEE Trans. Electron Devices, 54,

- 2452 (2007).

T. M. Pan, and C. H. Liu, Electrochem. Solid-State Lett., 8, G348 (2005).

- 8. G. Chen, M. F. Li, C. H. Ang, J. Z. Zheng, and D. L. Kwong, *IEEE Electron Device Lett.*, 23, 734 (2002).

- 9. J. C. Liao, Y. K. Fang, C. H. Kao, and C. Y. Cheng, *IEEE Electron Device Lett.*, 29, 477 (2008).

- C.-Y. Chen, J.-W. Lee, S.-D. Wang, M.-S. Shieh, P.-H. Lee, W.-C. Chen, H.-Y. Lin, K.-L. Yeh, and T.-F. Lei, *IEEE Trans. Electron Devices*, 53, 2993 (2006).

- V. Huard, C. Parthasarathy, N. Rallet, C. Guerin, M. Mammase, D. Barge, and C. Ouvrard, in *Proceedings of the IEDM*, 797 (2007).

- 12. V. Huard, M. Denais, F. Perrier, N. Revil, C. Parthasarathy, A. Bravaixc, and E.

- Vincent, Microelectron. Reliab., 45, 83 (2005).

- Vincent, Microelectron. Reliab., 45, 83 (2005).

S. Maeda, S. Maegawa, T. Ipposhi, H. Nishimura, T. Ichiki, J. Mitsuhashi, M. Ashida, T. Muragishi, Y. Lnoue, and T. Nishimura, J. Appl. Phys., 76, 8160 (1994).

A. T. Krishnan, V. Reddy, and S. Krishnan, Tech. Dig. Int. Electron Devices Meet., 2001, 39.3.1.

S. Ogawa and N. Shiono, Phys. Rev. B, 51, 4218 (1995).

C. S. Lin, Y. C. Chen, T. C. Chang, W. C. Hsu, S. C. Chen, H. W. Li, K. J. Tu, F. V. Chen, T. C. Chang, W. C. Hsu, S. C. Chen, H. W. Li, K. J. Tu, F.

- Y. Jian, and T. C. Chen, Electrochem. Solid-State Lett., 12, H229 (2009).

17. C. A. Dimitriadis, P. A. Coxon, L. Dozsa, L. Papadimitriou, and N. Economou, IEEE Trans. Electron Devices, 39, 598 (1992).

- 18. R. E. Proano, R. S. Misage, and D. G. Ast, IEEE Trans. Electron Devices, 36, 9

- 19. Y. Toyota, T. Shiba, and M. Ohkura, IEEE Trans. Electron Devices, 52, 1766 (2005).

- Y. Taur and T. H. Ning, Fundamental of Modern VLSI Devices, Cambridge University, Cambridge, England, p. 93 (1998).

Y. Z. Xu, F. J. Clough, E. M. S. Narayanan, Y. Chen, and W. I. Milne, IEEE

- Electron Device Lett., 20, 80 (1999).

- N. Bavidge, M. Boero, P. Migliorato and T. Shimoda, Appl. Phys. Lett., 77, 3836 (2000).