# Performance and Off-State Current Mechanisms of Low-Temperature Processed Polysilicon Thin-Film Transistors with Liquid Phase Deposited SiO<sub>2</sub> Gate Insulator

Ching-Fa Yeh, Shyue-Shyh Lin, Tzung-Zu Yang, Chun-Lin Chen, and Yu-Chi Yang

Abstract-Polysilicon thin-film transistors (poly-Si TFT's) with liquid phase deposition (LPD) silicon dioxide (SiO2) gate insulator were realized by low-temperature processes (< 620°C). The physical, chemical, and electrical properties of the new dielectric layer were clarified. The low-temperature processed (LTP) poly-Si TFT's with W/L = 200  $\mu$ m/10  $\mu$ m had an on-off current ratio of 4.95  $\times$  10<sup>6</sup> at  $V_D=5$  V, a field effect mobility of 25.5 cm<sup>2</sup>/V·s at  $V_D=0.1$  V, a threshold voltage of 6.9 V, and a subthreshold swing of 1.28 V/decade at  $V_D = 0.1$  V. Effective passivation of defects by plasma hydrogenation can improve the characteristics of the devices. The off-state current  $(I_L)$  mechanisms of the LTP poly-Si TFT's were systematically compared and clarified. The I<sub>L</sub> is divided into three regions; the  $I_L$  is attributable to a resistive current in region I (low gate bias), to pure thermal generation current in region II (low drain bias), and to Frenkel-Poole emission current in region III (high gate bias and drain bias).

#### I. INTRODUCTION

THIN-film transistors (TFT's) on transparent substrate are important for making the active matrix of a liquid crystal display (LCD). Because polysilicon thin-film transistors (poly-Si TFT's) have a high field-effect mobility, the potential to realize very large area LCD's [1], and a capability for peripheral driver circuit integration [2]–[4], much effort has been devoted to developing high-performance poly-Si TFT's.

Using conventional glass substrate is advantageous for reducing the cost of fabricating TFT's. To realize glass substrate TFT's, the maximum process temperature must be below 600°C. Under this limitation, a high-quality low-temperature processed (LTP) polysilicon active layer and gate insulator are indispensable components for realizing high-performance low-temperature poly-Si TFT's. The solid phase crystallization (SPC) [5] method has been widely used to fabricate the polysilicon active layer, for the SPC method produces a smooth top surface and large grain size. As for the gate insulator, various chemical vapor deposition (CVD) methods have been used to fabricate the dielectric layer [6], [7]. But all

Manuscript received October 16, 1992; revised September 13, 1993. The review of this paper was arranged by Associate Editor W. F. Kosonocky. This work was supported by the National Science Council, Republic of China, under contract number NSC 81-0404-E-009-122.

C.-F. Yeh, S.-S. Lin, T.-Z. Yang and C.-L. Chen are with the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

Y.-C. Yang is with the Institute of Electro-Physics, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C.

IEEE Log Number 9214409.

of these CVD methods require expensive equipment and the processes involved are very complex. Recently, a new SiO<sub>2</sub> formation technology using the liquid phase deposition (LPD) method has been developed [8]. LPD SiO<sub>2</sub> film has two main advantages in comparison with other CVD methods: First, the substrate temperature during deposition can be greatly reduced, because LPD SiO<sub>2</sub> film can be deposited at room temperature. Second, the apparatus used is simple and inexpensive. LPD SiO<sub>2</sub> technology is thus an economical candidate for replacing high-cost CVD technologies. In this research, poly-Si TFT's with LPD SiO<sub>2</sub> gate insulator are first developed. The physical, chemical, and electrical properties of LPD SiO<sub>2</sub> and the performance of the LTP poly-Si TFT's are then described in detail.

In general, poly-Si TFT's suffer from relatively high OFF current compared with a-Si TFT's. This is a serious problem for pixel TFT's, since the fundamental principle of active matrix displays is based on static operation without leakage current. To hold the signal levels for acceptable image quality, the off-state current has to be as low as 1 pA/ $\mu$ m [9], which is an important criterion for poly-Si TFT's. Hence considerable effort has been devoted to clarifying the conduction mechanisms of  $I_L$ . However, as yet no consensus on the nature of the mechanisms has emerged. Some researchers have assumed that the conduction mechanism of  $I_L$  is dominated by only one of the mechanisms [10]-[12]. But recently, it has been discovered, shown that the conduction mechanism of  $I_L$  is dependent on gate bias  $(V_{GS})$ , drain bias  $(V_{DS})$ , device size, device structure, and fabrication conditions [13]-[16]. That is, the conduction mechanism is not determined by a unique mechanism. In this paper, the conduction mechanisms of  $I_L$  in poly-Si TFT's with LPD SiO<sub>2</sub> gate insulator will be investigated and compared with other conduction mechanisms which have been reported.

## II. EXPERIMENTAL

# A. Liquid Phase Deposition (LPD) SiO<sub>2</sub>

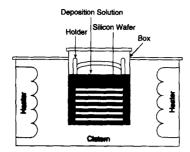

A schematic diagram of the apparatus for preparing LPD  $SiO_2$  is shown in Fig. 1. First, to prepare an immersing solution, 35 g of silica powder was added to 1 liter of hydrosilicofluoric acid ( $H_2SiF_6$ ) to obtain a silica-saturated  $H_2SiF_6$  solution. Furthermore, to supersaturate the solution

Fig. 1. Schematic diagram of the apparatus for LPD SiO<sub>2</sub> deposition.

with  $SiO_2$ , boric acid solution (0.1 M) was continuously added to the solution.

The basic chemical reaction kinetics of  $SiO_2$  deposition are represented by the following two equilibrium processes:

$$H_2SiF_6 + 2H_2O \rightleftharpoons 6HF + SiO_2 \tag{1}$$

$$H_3BO_3 + 4HF \rightleftharpoons BF_4^- + H_3O^+ + 2H_2O.$$

(2)

In (1), addition of silica leads to a reaction shift from right to left. Therefore the solution saturated with silica will include minimum hydrofluoric acid. However, this equilibrium can be changed by adding boric acid to the solution. Normally boric acid reacts easily with hydrofluoric acid, as shown in (2), thereby consuming hydrofluoric acid and bringing about the transient state supersaturated with SiO<sub>2</sub> described by (1). This supersaturation of SiO<sub>2</sub> enhances (1) from left to right followed by silica deposition on the substrate.

To investigate the characteristics of LPD SiO<sub>2</sub> film, n-type, (100) silicon substrates with 4–7  $\Omega$ -cm resistivity were used in our experiment. Various SiO<sub>2</sub> films were deposited at different temperatures to compare the deposition rate. The SiO<sub>2</sub> films were characterized by measuring their thickness and the refractive index using an ellipsometer. The chemical composition was analyzed by FTIR and Auger electron spectroscopy (AES). The etching rate was examined with P-etch solution (48% HF: 70% HNO<sub>3</sub>: H<sub>2</sub>O = 3:2:60) at room temperature. Electrical properties were investigated on MOS capacitors with aluminum gate contact of 0.12 mm<sup>2</sup> in area. The density of interface trap states was determined by high-frequency (1 MHz) capacitance-voltage (C-V) measurements [17].

## B. TFT Fabrication

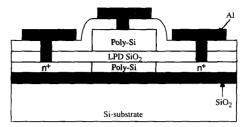

Fig. 2 shows a cross-sectional view of the fabricated poly-Si TFT. An under-layer of SiO<sub>2</sub> (500 nm thick) was thermally grown on a (100) silicon substrate. The polysilicon layer (100 nm thick) was prepared by the SPC method [5]. After the polysilicon layer was patterned into islands, SiO<sub>2</sub> gate insulator (100 nm thick) was deposited at 40°C by the LPD method. Then gate polysilicon (350 nm thick) was deposited by LPCVD at 620°C and patterned.  $P^+$  (5 × 10<sup>15</sup> cm<sup>-2</sup>, 40 KeV) self-aligned implanted source and drain regions were formed by thermal annealing for 24 hours at 600°C. After the interlayer of insulator was formed, the contact holes were opened, and an aluminum layer (500 nm thick) was evaporated and patterned. Finally, hydrogenation was performed in a plasma reactor at 300°C for 60 min.

Fig. 2. Cross-sectional view of fabricated LTP poly-Si TFT with LPD SiO<sub>2</sub> gate insulator.

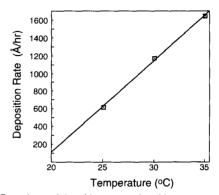

Fig. 3. Dependence of deposition rate on deposition temperature for LPD  ${

m SiO_2}$  film.

maner :

| TABLE I                         |                                         |                                            |

|---------------------------------|-----------------------------------------|--------------------------------------------|

|                                 | LPD-SiO <sub>2</sub>                    | CVD-SiO <sub>2</sub>                       |

| FTIR Si-O-Si Peak               | 1092.5 cm <sup>-1</sup>                 | 1070 cm <sup>-1</sup>                      |

| Refractive Index                | 1.43                                    | 1.45                                       |

| P-etch Rate                     | 24 A/sec                                | 25A/sec                                    |

| Leakage Current Density (at 5V) | $2.2 \times 10^{-12}$ A/cm <sup>2</sup> | $9.0 \times 10^{-12}$<br>A/cm <sup>2</sup> |

| Dielectric Breakdown Field      | 7 MV/cm                                 | 5.8 MV/cm                                  |

| Dielectric Constant (1MHz)      | 3.5                                     | 4.3                                        |

# III. RESULTS AND DISCUSSION

#### A. Characteristics of LPD SiO<sub>2</sub> Film

The dependence of LPD  $SiO_2$  deposition rate on deposition temperature is shown in Fig. 3, which indicates that the  $SiO_2$  deposition rate is enhanced with the increase in deposition temperature.

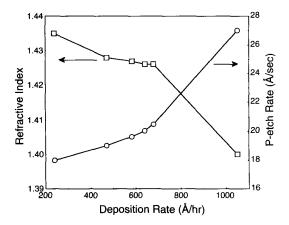

The characteristics of LPD  ${\rm SiO_2}$  film are summarized in Table I, which also compares LPD  ${\rm SiO_2}$  and CVD  ${\rm SiO_2}$  [18]. For the LPD  ${\rm SiO_2}$  film, the refractive index is about 1.42  $\sim$  1.44, which is lower than the 1.462 of thermal  ${\rm SiO_2}$  but nearly the same as the value for CVD  ${\rm SiO_2}$ . The lower refractive index may be due to a porous structure [19]. This is consistent with the results for the P-etch rate. The P-etch rate of LPD  ${\rm SiO_2}$  is about 20 Å/s. This value is larger than that for non-porous oxide (2  $\sim$  8 Å/s) [19]. The dependence

Fig. 4. Dependence of P-etch rate and refractive index on deposition rate for LPD  ${\rm SiO_2}$  film.

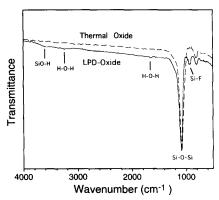

Fig. 5. FTIR spectra of LPD SiO2 and thermal SiO2.

of refractive index and P-etch rate on LPD  $\mathrm{SiO}_2$  deposition rate is shown in Fig. 4. The refractive index increases but the P-etch rate decreases with a decrease in the deposition rate. This is because the film deposited at lower deposition rate has a denser (less porous) structure, which leads to a larger refractive index and a lower P-etch rate. Thus to control the film quality, it is necessary to select an optimal deposition condition with a low deposition rate.

Typical FTIR spectra of LPD SiO<sub>2</sub> film are shown in Fig. 5. The absorption bands around 1090 cm<sup>-1</sup> and 810 cm<sup>-1</sup> are due to Si-O-Si stretching and bending vibration, respectively. These absorption bands are similar to those of thermal oxide. indicating that LPD oxide is amorphous in structure [19]. Another main absorption band around 930 cm<sup>-1</sup> found in the LPD SiO<sub>2</sub> spectra may be attributed to Si-F stretching vibration. The fluorine (F) contained in the Si-F bond must be incorporated from the H<sub>2</sub>SiF<sub>6</sub> solution. At the same time, we find that only a few absorption bands related to water appear in the LPD SiO<sub>2</sub> spectrum. (O-H stretching due to H<sub>2</sub>O is shown in the absorption bands around 3300 cm<sup>-1</sup> and 1640 cm<sup>-1</sup>, while O-H stretching due to SiO-H is shown in the band around 3650 cm<sup>-1</sup>.) These bands reveal that LPD SiO<sub>2</sub> film contains only little water. Because this characteristic is very important for the electrical and structural stability of the film, we conclude that the LPD SiO<sub>2</sub> film is of good quality.

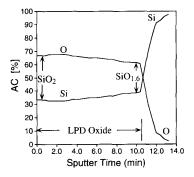

Fig. 6. AES depth profile of LPD SiO<sub>2</sub> film.

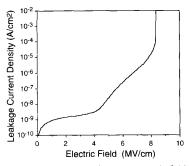

Fig. 7. Characteristics of current density versus electric field for LPD SiO<sub>2</sub> MOS capacitors.

The AES depth profiles of LPD SiO<sub>2</sub> films are shown in Fig. 6. Only silicon (Si) and oxygen (O) atoms are detected in these films. The ratio of Si/O determined by AES is about 1/2 on the surface of the LPD SiO<sub>2</sub> films. However, the ratio of Si/O is larger than 1/2 in the interior of the films. We conclude that LPD oxide films are Si-rich films. The Sirich composition near the Si/SiO<sub>2</sub> interface thus influences the electrical characteristics of LPD SiO<sub>2</sub> films, as described below.

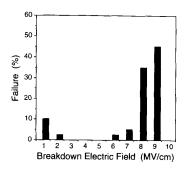

Fig. 7 is a typical current-voltage (I-V) curve of MOS capacitors with LPD SiO<sub>2</sub> film as dielectric. The leakage current density is about 3 nA/cm² at an electric-field of 4 MV/cm, and the maximum breakdown electric-field  $(E_{\rm BD})$  is about 7  $\sim$  8 MV/cm. The leakage current densities of LPD SiO<sub>2</sub> film are slightly high. This may be due to the Si-rich composition of LPD SiO<sub>2</sub> film. The conduction mechanisms of LPD-oxide are similar to those reported for silicon-rich CVD SiO<sub>2</sub> [20]. That is, the current conduction in the Si-rich LPD SiO<sub>2</sub> film is likely to be due to direct tunneling from one Si-island to an adjacent one, and the characteristic hump in the I-V curve at high field probably results from Poole-Frenkel type conduction. The distribution of breakdown electric field  $(E_{\rm BD})$  is shown in Fig. 8; the maximum  $E_{\rm BD}$  of the LPD SiO<sub>2</sub> film is 8  $\sim$  9 MV/cm.

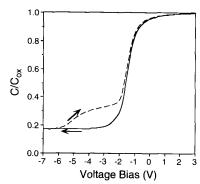

Fig. 9 shows the C-V curves of MOS capacitors with LPD  $\mathrm{SiO}_2$  film as dielectric. The C-V curves reveal the presence of many positive charges, slow states, and fast states in the LPD  $\mathrm{SiO}_2$  film, which are related to oxygen vacancies. In addition, injection type hysteresis is observed in the inversion region.

Fig. 8. Distribution of breakdown electric field  $(E_{\mathrm{BD}})$  for LPD  $\mathrm{SiO_2}$  MOS capacitors.

Fig. 9. Typical capacitance versus voltage characteristics for MOS capacitors with LPD SiO<sub>2</sub> as dielectric.

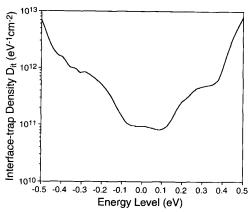

Fig. 10. A typical distribution of interface trap density for MOS capacitors with LPD  ${

m SiO_2}$  as dielectric.

It may result from fast trapping centers near the middle-gap correlated with the Si-rich structure. The Terman method [17] was used to calculate a typical distribution of interface-trap density  $(D_{\rm it})$ , and the result is shown in Fig. 10. It appears one order of magnitude larger than the  $1\times 10^{10}~{\rm cm^{-2}~eV^{-1}}$  of thermal SiO<sub>2</sub> in the mid-gap, which makes it comparable to the value for CVD SiO<sub>2</sub>.

The experimental results on the electrical characteristics of I-V and C-V are summarized in Table I. From the table, we can conclude that LPD  $\mathrm{SiO}_2$  film exhibits satisfactory electrical integrity.

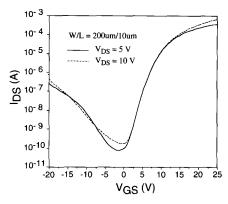

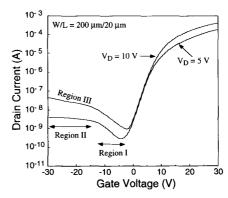

Fig. 11. Typical drain current versus gate bias characteristics for LTP poly-Si TFT's with LPD SiO<sub>2</sub> gate insulator.

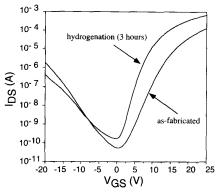

Fig. 12. Comparison of drain current versus gate bias characteristics between as-fabricated and hydrogenated poly-Si TFT's with LPD SiO<sub>2</sub> gate insulator.

# B. Performance of LTP Poly-Si TFT's

Fig. 11 shows the drain current versus gate bias  $(I_{\rm D}\text{-}V_{\rm G})$  characteristics for  $W/L=200~\mu\text{m}/10~\mu\text{m}$  poly-Si TFT's with LPD SiO $_2$  gate insulator under constant drain voltage of 5 V and 10 V. Threshold voltage was determined from the extrapolated curve of the  $\sqrt{I_{\rm D}}-V_{\rm G}$  characteristics in the saturated region  $(V_{\rm D}=10~{\rm V})$ . Field-effect mobility was calculated from the maximum transconductance in the linear region  $(V_{\rm D}=0.1~{\rm V})$ . For these LTP poly-Si TFT's, an on-off current ratio of 4.95 ×  $10^6$  at  $V_{\rm D}=5{\rm V}$ , field effect mobility of 25.5 cm²/V·s at  $V_{\rm D}=0.1~{\rm V}$ , threshold voltage of 6.9 V, and subthreshold swing of 1.28 V/decade were obtained.

It is well known that carrier trapping, barrier formation, and dopant segregation in the network of grain boundaries and other defects in the  $\mathrm{Si/SiO_2}$  interface can cause gross deviation in electronic properties from those of crystalline silicon. Hence to improve device performance, it is essential to reduce trap densities effectively. It has been shown that hydrogen plasma treatment can effectively reduce trap state density and improve device characteristics [21], [22]. A comparison of the  $I_{\mathrm{D}}$ - $V_{\mathrm{G}}$  characteristics of as-fabricated and hydrogenated poly-Si TFT's with LPD  $\mathrm{SiO_2}$  gate insulator is shown in Fig. 12. The characteristic parameters of poly-Si TFT's obtained before and after hydrogenation are summarized in Table II. The data in

| TABLE II                                        |                     |                         |

|-------------------------------------------------|---------------------|-------------------------|

|                                                 | As-fabricated       | Hydrogenation (3 hours) |

| Field Effect Mobility (cm <sup>2</sup> /V· sec) | 17.9                | 25.5                    |

| Threshold Voltage (V)                           | 12.9                | 6.91                    |

| Subthreshold Swing (V/dec)                      | 2.11                | 1.28                    |

| Trap State Density (cm <sup>-2</sup> )          | $7.25\times10^{12}$ | $4.2\times10^{12}$      |

the table reveal that the field effect mobility has been improved from 17.9 cm<sup>2</sup>/V·s to 25.5 cm<sup>2</sup>/V·s, and the threshold voltage has been improved from 12.9 V to 6.9 V. Although the three-hour hydrogenation treatment markedly improves the electrical characteristics of poly-Si TFT's, the hydrogenation time must far exceed three hours to greatly improve the performance of poly-Si TFT's [23].

## C. Off-State Current (I<sub>L</sub>) of LTP Poly-Si TFT's

When negative gate bias  $(V_{\rm GS})$  is applied, a considerable OFF-state current  $(I_L)$  will be found. This current results from two basic mechanisms: 1) Resistive current, which arises when the applied  $V_{\rm GS}$  is not negatively large enough to form a p-layer in the channel region. In this case  $I_L$  can be assumed to be an ohmic current flowing through the polysilicon bulk layer. This situation usually occurs when  $V_{\rm GS}$  is smaller than flat band voltage  $(V_{\rm FB})$  but larger than the negative value of the threshold voltage  $(-V_{\rm th})$ . 2) Junction leakage current, which arises when  $V_{\rm GS}$  is more negative than  $-V_{\rm th}$ . In that case, holes are induced to form a p-type channel region, and subsequently a reverse-biased p-n junction is formed between drain and channel. The junction leakage current is caused by electron-hole pairs generated via grain boundary traps in the depletion region.

There are also three other, related mechanisms through which a trapped hole at an energy level  $E_t$  can be generated to the valence band: (a) Pure thermal emission or thermal generation, which is due to thermal excitation of trapped holes in the valence band. (b) Pure field emission or tunneling, which is due to field ionization of trapped hole tunneling through the potential barrier into the valence band. (c) Thermionic field emission or Frenkel–Poole emission, which is due to field-enhanced thermal excitation of trapped holes in the valence band. The applied field causes the barrier to become low and thin enough that either thermal emission or thermal excitation to virtual states prior to tunneling can easily occur.

The pure field emission current has the strongest dependence on the applied field but is essentially independent of temperature, so it dominates at low temperature and high field conditions. The pure thermal emission current is proportional to the intrinsic carrier concentration  $(n_i)$  of silicon, and  $n_i$  is proportional to  $\exp[-E_g/2k_BT]$  (where  $E_g$  is the energy gap of silicon). For this reason, the activation energy of the pure thermal emission current should be approximately equal

Fig. 13. Dependence of OFF-state current on gate bias with drain bias as a parameter for LTP poly-Si TFT's with LPD SiO<sub>2</sub> gate insulator.

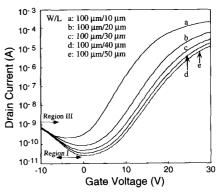

Fig. 14. Dependence of OFF-state current on gate bias at  $V_D=5\,\mathrm{V}$  for poly-Si TFT's with channel length as a parameter.

to  $E_g/2$ . In addition, the pure thermal generation current is nearly independent of  $V_{\rm GS}$ . On the other hand, both field emission and Frenkel-Poole emission current increase with  $V_{\rm GS}$ . The difference between them is that the increase of the field emission current with  $|V_{\rm GS}|$  tends to approach a saturation value, while the Frenkel-Poole emission current does not [10]. Furthermore, the activation energy of the latter is larger than that of the former.

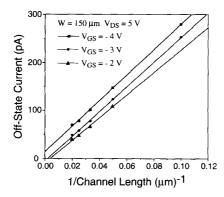

Fig. 13 shows the typical dependence of  $I_L$  on  $V_{\rm GS}$  and  $V_{\rm DS}$  for samples with  $W/L=200~\mu {\rm m}/20~\mu {\rm m}$ , respectively. In order to distinguish the mechanism of the OFF-state current, the leakage current can be divided into three parts: 1) a low gate bias region I (at the region around  $-10 V < V_{GS} < 0$ V), 2) an almost flat region II, in which  $I_L$  does not change with a decrease in  $V_{GS}$ , and 3) a gate-bias dependent region III at high drain bias. Although  $I_L$  increases with negative  $V_{\rm GS}$  both in region I and region III, the difference can be distinguished by the relationship between  $I_L$  and  $V_{GS}$  with channel length (L) as a parameter (Fig. 14).  $I_L$  in region II and region III is independent of L, while  $I_L$  in region I decreases as L increases. The dependence of  $I_L$  on 1/L, as shown in Fig. 15, indeed indicates that  $I_L$  in region I varies linearly with 1/L. From the above description, it is obvious that  $I_L$  in region I is a resistive current and  $I_L$  in region II and region III is a junction leakage current.

Fig. 15. Dependence of OFF-state current on the reverse of channel length at  $V_D=5$  V for poly-Si TFT's with  $W=150~\mu \mathrm{m}$ .

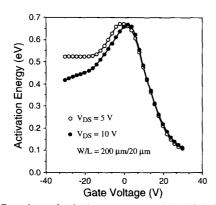

Fig. 16. Dependence of activation energy on gate bias with drain bias at 5 V and 10 V for poly-Si TFT's with LPD  ${\rm SiO_2}$  gate insulator.

To further clarify the mechanism of  $I_L$  in region II and III, the temperature dependence was studied. The activation energies were calculated from an Arrhenius plot by means of leakage currents obtained at  $25^\circ$ ,  $50^\circ$ ,  $75^\circ$ ,  $100^\circ$ , and  $125^\circ$  C. The dependence of activation energy on  $V_{\rm GS}$  with  $V_{\rm DS}$  at 5 V and 10 V is shown in Fig. 16. The activation energies in region II are close to the  $E_g/2$  of silicon and almost independent of  $V_G$ . In contrast, an increase of negative  $V_{\rm GS}$  causes a decrease of activation energy in region III. These results lead to the conclusion that  $I_L$  is attributable to pure thermal generation in region II and to Frenkel–Poole emission in region III. The width of region II decreases. For devices at  $V_{\rm DS}=5$  V,  $I_L$  is almost independent of  $V_{\rm GS}$  up to  $V_{\rm GS}=-30$  V, and it vanishes when  $V_{\rm DS}=10$  V.

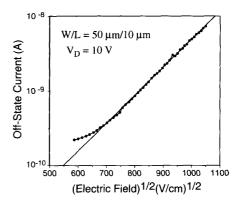

Furthermore, according to [11], the Frenkel–Poole mechanism gives a current  $I_{\rm FE}$  of the form

$$I_{\rm FE} = I_0 \exp(\alpha \sqrt{E_{\rm PK}}) \tag{3}$$

where

$$\alpha = \frac{(q)^{3/2}}{(\pi \varepsilon_{\rm Si})^{1/2} kT}.\tag{4}$$

Fig. 17. Measured log  $I_L$  versus  $(E_{\rm PK})^{1/2}$  at  $V_D$  = 10 V on a semilog scale for poly-Si TFT's with W/L = 50  $\mu$ m/10  $\mu$ m.

$I_0$  is the generation current at zero electric field, and  $E_{\rm PK}$  is the peak electric field given by

$$E_{\rm PK} = \frac{(V_{\rm GS} - V_{\rm DS} - V_{\rm FB})\varepsilon_{\rm SiO_2}}{t_{\rm ox}\varepsilon_{\rm Si}}$$

(5)

where  $\varepsilon_{\rm SiO_2}$  is the permittivity of silicon dioxide and  $t_{\rm ox}$  is the thickness of silicon dioxide.

Fig. 17 plots  $\log I_L$  versus  $(E_{\rm PK})^{1/2}$  at room temperature for our sample. A straight line fits the data reasonably well in the high electric field region. This also proves that  $I_L$  in region III is dominated by Frenkel-Poole emission.

Although the above results and discussion are all in terms of n-channel poly-Si TFT's, similar results were obtained for p-channel poly-Si TFT's. In other words, the basic conduction mechanisms of OFF-state current in p-channel poly-Si TFT's also include resistive current, thermal generation current, and Frenkel-Poole emission current. However, the weight of each mechanism is different for n-channel and p-channel TFT's.

#### IV. CONCLUSION

Polysilicon thin film transistors using liquid phase deposition silicon dioxide (SiO2) as gate insulator were realized by low-temperature processes (< 620°C). The LPD SiO<sub>2</sub> method has been shown to be an economical approach that supplies a good dielectric layer. LTP poly-Si TFT's with  $W/L = 200 \mu \text{m}/10 \mu \text{m}$  have an on-off current ratio of  $4.95 \times 10^6$  at  $V_D = 5$  V, a field effect mobility of 25.5 cm<sup>2</sup>/V·s at  $V_D = 0.1$  V, a threshold voltage of 6.9 V, and a subthreshold swing of 1.28 V/decade at  $V_D = 0.1$  V. Effective passivation of defects by plasma hydrogenation can improve the characteristics of these devices. The behavior of off-state current in LTP poly-Si TFT's has also been clarified. The conduction mechanisms of off-state currents can be divided into two parts, one attributable to a resistive current in the low gate bias region, the other to a junction leakage current in the high gate bias region. The junction leakage currents observed in our samples were due to two basic mechanisms, pure thermal generation and Frenkel-Poole emission. Clarification of leakage current mechanisms should enable us to find fundamental principles by which to reduce the off-state current.

#### REFERENCES

- [1] J. Ohwada, "Driving condition for low temperature poly-Si LCD," SID Dig., 1986, p. 55. [2] Y. Oana, "A 240  $\times$  360 element active matrix LCD with integrated

- gate-bus drivers using poly-Si TFTs," *SID Dig.*, 1984, p. 312.

[3] S. Morozumi, K. Oguchi, T. Misawa, R. Araki, and H. Ohshima, "4.25-

- in, and 1.51-in. B/W and full-color LCD video displays addressed by poly-Si TFTs," *SID Dig.*, 1984, p. 316.

[4] J. Ohwada, "Peripheral drive circuits for poly-Si TFT LCD," in *Extended*

- Abstr. 1987 (19th) Conf. Solid State Devices and Materials, p. 55.

[5] M. K. Hatalis and D. W. Greve, "High-performance thin-film transistors in low-temperature crystallized LPCVD amorphous silicon films," IEEE Electron Device Lett., vol. 8, p. 361, 1987.

[6] H. Ohshima and S. Morozumi, "Future trends for TFT integrated circuits

- on glass substrates," in IEDM Tech Dig., p. 157, 1989.

- [7] A. Mimura, T. Suzuki, N. Konishi, T. Suzuki, and K. Miyata, "Lowtemperature polysilicon TFT with two-layer gate insulator using photo-CVD and APCVD SiO2," IEEE Electron Device Lett., vol. 9, p. 290,

- [8] C. F. Yeh, S. S. Lin, C. L. Chen, and Y. C. Yang, "Novel Technique for SiO<sub>2</sub> formed by Liquid-Phase Deposition for Low-Temperature Processed Polysilicon TFT," IEEE Electron Device Lett., vol. 14, p.

- [9] A. Chiang, I-W. Wu, M. Hack, A. G. Lewis, T. Y. Huang, and C-C. Tsai, "Polysilicon thin film transistor material and device technologies," in Extended Abstr. 1991 Conf. Solid State Devices and Materials, p. 586.

- [10] J. G. Fossum, A. Ortiz-Conde, H. Shichijo, and S. K. Banerjee, "Anomalous leakage current in LPCVD polysilicon MOSFET's," IEEE Trans. Electron Dev., vol. ED-32, p. 1878, Sept. 1985.

- [11] S. K. Madan and D. A. Antoniadis, "Leakage current mechanisms in Hydrogen-passivated fine-grain polycrystalline silicon on insulator MOSFET's," IEEE Trans. Electron Dev., vol. ED-33, p. 1518, Oct. 1986.

- [12] I. W. Wu, A. G. Lewis, T. Y. Huang, W. B. Jackson, and A. Chiang, "Mechanism and device-to-device variation of leakage current in polysilicon thin film transistors," in *IEDM Tech Dig.*, p. 867, 1990.

[13] P. Migliorato and D. B. Meakin, "Material properties and characteristics

- of polysilicon transistors for large area electronics," Applied Surface

- Sci., vol. 30, p. 353, 1987 [14] S. D. Brotherton, J. R. Ayres, and N. D. Young, "Characterization of low temperature poly-Si thin film transistors," Solid-State Electron., vol. 34. no. 7, p. 671, 1991.

- [15] M. Yazaki, S. Takenaka, and H. Ohshima, "Conduction mechanism of leakage current observed in metal-oxide-semiconductor transistors and poly-Si thin-film transistors," *Japan. J. Appl. Phys.*, vol. 31, p. 206.

- [16] K. Ono, T. Aovama, N. Konishi, and K. Mivata, "Analysis of currentvoltage characteristics of low-temperature-processed polysilicon thinfilm transistors," IEEE Trans. Electron Dev., vol. 9, p. 792, Apr. 1992.

- [17] E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology. New York: Wiley, p. 325, 1982.

[18] T. Homma, T. Katoh, Y. Yamada, I. Shimizu, and Y. Marao, "A new

- interlayer formation technology for completely planarized multilevel interconnection by using LPD," in *Proc. 1990 Symp. VLSI Technol.*,

- [19] W. A. Pliskin, "Comparison of properties of dielectric films deposited

- by various methods," *J. Vac. Sci. Technol.*, vol. 14, p. 1064, 1977. [20] D. J. DiMaria and D. W. Dong, "High current injection into SiO<sub>2</sub> from Si rich SiO<sub>2</sub> films and experimental applications," J. Appl. Phys., vol. 51, p. 2772, 1980.

- [21] A. Mimura, N. Konishi, K. Ono, J. I. Ohwada, Y. Hosokawa, Y. A. Ono, T. Suzaki, K. Miyata, and H. Kawakami, "High performance lowtemperature poly-Si n-channel TFTs for LCD," IEEE Trans. Electron Devices, vol. 36, p. 351, 1989.

- [22] T. I. Kamins and P. J. Marcoux, "Hydrogenation of transistors fabricated in polysilicon-silicon films," IEEE Electron Device Lett., vol. EDL-1, p.

- [23] I. W. Wu, T. Y. Huang, W. B. Jackson, A. G. Lewis and A. Chiang. "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation," IEEE Electron Device Lett., vol. 12, p. 181, 1991

Ching-Fa Yeb was born in Hsinchu, Taiwan, on September 20, 1948. He received the B. S. degree from National Oceanic University, Keelung, Taiwan, ROC, in 1971, the M. S. and Ph.D. degrees from the University of Tokyo, Tokyo, Japan, in 1979 and 1982, respectively, all in electrical engineering.

From 1982 to 1988, he was with the Fuji Xerox's Electronic Technology Laboratories, Ebina, Japan, where his work concerned the research and development of semiconductor process technologies and devices, particularly on dry process technology

and contact amorphous-Si Image sensor, and high-voltage MOSFET. He is now an Associate Professor at the Department of Electronics Engineering & Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan. His research interests include thin-film transistor, power devices, silicon-wafer directly bonding technologies, and low-temperature processed materials and devices.

Dr. Yeh is a member of Japanese Journal Applied Physics Society, and he also as an oversea member of program committee of the international Conference on Solid State Devices and Materials.

Shvue-Shvh Lin was born in Nantou, Taiwan, on November 10, 1967. He received the B.S. and M.S. degrees in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, ROC, in 1990 and 1992, respectively. Currently, he is working towards the Ph.D. degree in electronics engineering at National Chiao-Tung University.

His current research interest is in the research and development of liquid-phase deposition silicon dioxide film and its application on the semiconductor devices.

Tzung-Zu Yang was born in Pingtung, Taiwan, on July 11, 1969. He received the B.S. and M.S. degrees in electronics engineering from National Chiao-Tung University in 1991 and 1993, respec-

Currently, he is working with the Electronic Research and Service Organization, Industrial Technology Research Institute, Hsinchu, Taiwan, ROC, where he is engaged in the research of field emission display.

Chun-Lin Chen was born in Tainan, Taiwan, on February 13, 1965. He received the B. S. degree in chemistry from Tam-Kang University, Taipei, Taiwan, ROC, in 1988 and the M.S. degree in applied chemistry from National Chiao-Tung University in 1991. Currently, he is working towards the Ph.D. degree in electronics engineering at National Chiao-Tung University.

His current research interest is in the research and development of liquid-phase deposition silicon dioxide film and its application on the semiconductor devices.

Yu-Chi Yang was born in Maioli, Taiwan, on January 21, 1968. He received the B.S. and M.S. degrees in electrophysics from National Chiao-Tung University in 1990 and 1992, respectively. Currently, he is serving in the Chinese Army as a Second Lieutenant.