# Separation of Channel Backscattering Coefficients in Nanoscale MOSFETs

Ming-Jer Chen, Senior Member, IEEE, Huan-Tsung Huang, Member, IEEE, Yi-Chin Chou, Rong-Ting Chen, Yin-Ta Tseng, Po-Nien Chen, and Carlos H. Diaz, Senior Member, IEEE

Abstract—Channel backscattering coefficients in the  $k_BT$ layer (near the source) of 1.65-nm-thick gate oxide, 68-nm gate length bulk n-channel MOSFETs are systematically separated into two distinct components: the quasithermal-equilibrium mean-free-path for backscattering and the width of the  $k_BT$  layer. Evidence to confirm the validity of the separation procedure is further produced: 1) the near-source channel conduction-band profile; 2) the existing value of  $k_BT$  layer width from the sophisticated device simulation; and 3) an analytic temperature-dependent drain current model for the channel backscattering coefficients. The findings are also consistent with each other and therefore corroborate channel backscattering as the origin of the coefficients. Other interpretations and clarifications are determined with respect to the very recently released Monte Carlo particle simulation. Consequently, it can be reasonably claimed that the separated components, as well as their dependencies on temperature and bias, are adequate while being used to describe the operation of the devices undertaken within the framework of the channel backscattering theory.

Index Terms—MOSFETs, nanoscale, scattering.

#### I. INTRODUCTION

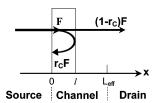

HANNEL backscattering theory has recently been introduced to provide the mesoscopic aspects of carrier transport in nanoscale MOSFETs [1]–[6]. In the schematic illustration of the theory for the saturation case shown in Fig. 1, a  $k_BT$  layer, where  $k_B$  (=  $8.614 \times 10^{-5} \ {\rm eV/^\circ K}$ ) is Boltzmann's constant and T is the temperature, exists in a small fraction (0  $\leq$  x  $\leq$  l) of the channel [2]–[6]. This specific zone located near the source critically determines the current drive at the drain

$$I_D = Q_{\text{inv}} v_{\text{inj}} \frac{(1 - r_C)}{(1 + r_C)} \tag{1}$$

where  $Q_{\rm inv}$  is the inversion-layer charge density per unit area at the top of the source-channel junction barrier,  $v_{\rm inj}$  is the thermal injection velocity at the top of the source-channel junction barrier, and  $r_C$  is the channel backscattering coefficient through the  $k_BT$  layer. The theory also argues that the backscattering coefficient  $r_C$  is functionally linked to both the quasithermal-equi-

Manuscript received February 10, 2004; revised May 10, 2004. This work was supported by the National Science Council under Contract 91-2215-E-009-045. The review of this paper was arranged by Editor R. Singh.

M.-J. Chen, Y.-C. Chou, R.-T. Chen, Y.-T. Tseng, and P.-N. Chen are with the Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan, R.O.C. (e-mail chenmj@faculty.nctu.edu.tw).

H.-T. Huang and C. H. Diaz are with the R/D Logic Technology Division, Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan, R.O.C. Digital Object Identifier 10.1109/TED.2004.833586

Fig. 1. Schematic diagram of channel backscattering theory. F is the incident flux from the source, l is the critical length over which a  $k_BT/q$  drop is developed, and  $r_C$  is the channel backscattering coefficient. The channel length  $L_{\rm eff}$  is the physical gate length minus the source/drain extensions.

librium mean-free-path  $\lambda$  for backscattering and the width l of the  $k_BT$  layer:  $r_C = l/(l + \lambda)$ .

Experimentally,  $r_C$  can be assessed by current–voltage (I-V) fitting [3], [7], [8] or a temperature dependent technique [9]. To describe the operation of the device within the framework of the channel backscattering theory,  $\lambda$  and l must be further decoupled from the experimental  $r_C$ ; however, little work was done in this direction.

On the other hand, very recently released Monte Carlo particle simulation [10] for the first time exhibited a relevant mechanism in a 10-nm gate length double-gate MOSFET case: the backscattering by the drain. The simulation [10] further revealed two other novel behaviors: (1) the reflection velocity distribution relative to the injection velocity distribution and (2) the non-Ohmic region in the drain. In a sense, these new mesoscopic properties must be taken into account when practically applying the currently recognized theory of channel backscattering to a certain device.

In this paper, assessment of  $r_C$  and its decoupling into  $\lambda$  and l both are systematically demonstrated in 68-nm gate length bulk MOSFETs. Evidence to confirm the validity of the separation procedure subsequently follows, which also consistently corroborates channel backscattering as the origin of the underlying  $r_C$ . Other interpretations and clarifications are determined relative to the above mentioned Monte Carlo simulation results. Eventually, the separated components, as well as their dependencies on temperature and bias, are used to describe the operation of the devices within the framework of the channel backscattering theory.

# II. DEVICES UNDER STUDY

Halo-implanted bulk n-channel MOSFETs were formed using a state-of-the-art process. Fitting of a C-V (capacitance versus voltage) curve led to the following process parameters: the physical gate oxide thickness  $t_{\rm OX}=1.65~{\rm nm}$ , the n<sup>+</sup> polysilicon doping concentration  $N_{\rm POLY}=9\times10^{19}~{\rm cm}^{-3}$ ,

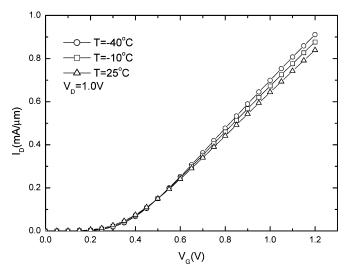

Fig. 2. Measured drain current versus gate voltage at  $V_D=1~\mathrm{V}$  for three temperatures.

and the channel doping concentration  $N_A=8\times10^{17}~{\rm cm}^{-3}$ . The physical gate length and width of the devices under study were 68 nm and 10  $\mu{\rm m}$ , respectively. Fig. 2 depicts measured drain current versus gate voltage characteristics at a drain voltage  $V_D=1$  V for three temperatures,  $-40\,^{\circ}{\rm C}$ ,  $-10\,^{\circ}{\rm C}$ , and  $25\,^{\circ}{\rm C}$ . The near-thermal-equilibrium threshold voltage  $V_{\rm tho}$  was 0.36, 0.34, and 0.33 V for temperatures of  $-40\,^{\circ}{\rm C}$ ,  $-10\,^{\circ}{\rm C}$ , and  $25\,^{\circ}{\rm C}$ , respectively, which were obtained using the peak transconductance extrapolation method at  $V_D=25~{\rm mV}$ . The temperature coefficient of  $V_{\rm tho}$  was  $-0.49~{\rm mV}/^{\circ}{\rm K}$ . The drain-induced-barrier-lowering (DIBL), defined under constant subthreshold conduction as the magnitude of the gate voltage shift divided by a change in drain voltage (from 25 mV to 1 V), was about 110 mV/V.

### III. ASSESSMENT OF $r_C$

To account for the source series resistance  $R_S$ , drain series resistance  $R_D$ , and DIBL, (1) is augmented into

$$I_D = C_{\text{eff}} \times \left[ (V_G - I_D R_S) - (V_{\text{tho}} - DIBL \times (V_D - I_D R_S - I_D R_D)) \right] \times v_{\text{inj}} \times \frac{1 - r_C}{1 + r_C}.$$

(2)

Here, the terms  $V_G - I_D R_S$  and  $V_D - I_D R_S - I_D R_D$  represent the intrinsic gate voltage and intrinsic drain voltage, respectively; and the term  $V_{\text{tho}} - DIBL \times (V_D - I_D R_S - I_D R_D)$  indicates the threshold voltage later designated as  $V_{

m th}$ . The effective gate capacitance  $C_{\text{eff}}$ , the near-thermal-equilibrium threshold voltage  $V_{\rm tho}$  and the thermal injection velocity  $v_{\rm inj}$  were all calculated in advance using a one-dimensional quantum mechanical numerical program [11] dedicated to an  $m n^+$  polysilicon/gate oxide/p-type substrate MOS system. This program employed the same algorithm on the basis of the triangular potential well approximation as in [12]. With known process parameters (i.e., t<sub>ox</sub>, N<sub>POLY</sub>, and N<sub>A</sub>) as input, the simulator quantified the subband energy levels and Fermi level, which in turn yielded electron population in the underlying two-dimensional electron gas (2DEG) inversion layer. The resulting inversion-layer charge density  $Q_{\text{inv}(eq)}$  under equilibrium conditions versus intrinsic

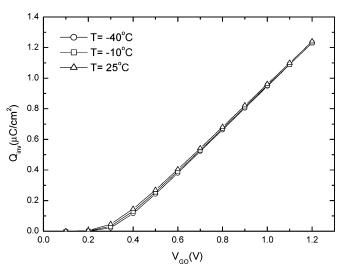

Fig. 3. Calculated inversion-layer charge density versus intrinsic gate voltage for three temperatures.

gate voltage  $V_{GO}$  is shown in Fig. 3, with temperature used as the parameter. Fitting to the one-dimensional MOS electrostatics formula  $Q_{\rm inv(eq)} = C_{\rm eff}(V_{GO} - V_{\rm tho})$  yielded  $C_{\rm eff} = 1.38~\mu{\rm F/cm^2}$  and the  $V_{\rm tho} = 0.32~{\rm V}$ , 0.31 V, and 0.30 V for temperatures of  $-40~{\rm ^{\circ}C}$ ,  $-10~{\rm ^{\circ}C}$ , and 25  ${\rm ^{\circ}C}$ , respectively. The corresponding threshold quantities, as well as temperature coefficient ( $-0.33~{\rm mV/^{\circ}K}$ ), are all comparable with those measured under quasithermal-equilibrium conditions (i.e.,  $V_D = 25~{\rm mV}$ , as mentioned above).

Again with the same subband levels and Fermi level as input, the effective thermal injection velocity at the top of the sourcechannel junction barrier can be readily calculated [4] as

$$v_{\rm inj} = \frac{\sum n_s^i v_{\rm inj}^i}{\sum n_s^i}$$

(3)

where  $n_s^i$  is the charge density associated with subband i in a certain direction (for example, a stream with a positive wavevector) and  $v_{\rm inj}^i$  is the corresponding thermal injection velocity [4], [13]

$$n_s^i = \gamma \frac{m_{di}}{\pi \hbar^2} \frac{k_B T}{2} \ell n \left[ 1 + \exp\left(\frac{E_f - E_i}{k_B T}\right) \right] \tag{4}$$

$$v_{\rm inj}^{i} = \sqrt{\frac{2k_B T m_{ci}}{\pi m_{di}^2}} \frac{\Im_{1/2} \left(\frac{E_f - E_i}{k_B T}\right)}{\ell n \left[1 + \exp\left(\frac{E_f - E_i}{k_B T}\right)\right]}.$$

(5)

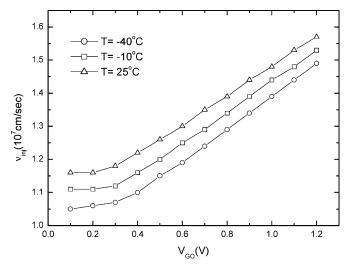

Here,  $\gamma$  is the valley degeneracy,  $m_{ci}$  is the conductivity effective mass for subband i,  $m_{di}$  is the density-of-states effective mass for subband i,  $E_i$  is the energy level of subband i,  $E_f$  is the Fermi level, and  $\Im_{1/2}$  is the Fermi–Dirac integral of order one-half. For twofold valleys,  $m_{ci} = m_t$  and  $m_{di} = m_t$ , and for fourfold valleys,  $m_{ci} = 2m_l m_t/(m_l + m_t)$ , and  $m_{di} = (m_l m_t)^{1/2}$ , where the longitudinal mass  $m_l = 0.916m_o$  and the transverse mass  $m_t = 0.19m_o$ . The results are displayed in Fig. 4 against intrinsic gate voltage with temperature used as the parameter. From these results, some important properties can be drawn. First, at low gate voltages, or at the nondegenerate limit, the thermal injection velocity considerably increases with temperature, regardless of gate voltage, as expected. Second, at

Fig. 4. Calculated thermal injection velocity versus intrinsic gate voltage for three temperatures.

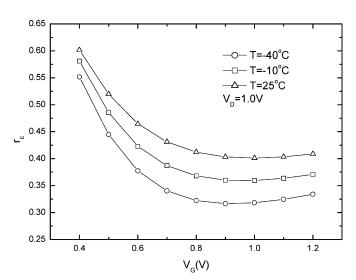

Fig. 5. Extracted backscattering coefficients corresponding to Fig. 2.

high gate voltages, or near the degenerate limit, the thermal injection velocity increases with gate voltage whereas the rate of increase declines with increasing temperature. The same dependencies are mentioned elsewhere [4].

The source series resistance  $R_S$  was about 75  $\Omega$ - $\mu$ m, which was determined using the ratio-and-shift method on long-channel devices (up to 10  $\mu m$ ) from the same manufacturing process. As usually adopted, the drain series resistance  $R_D$  was assumed to be equal to  $R_S$ . Now all the parameters in (2) are known, except  $r_C$ . At this time,  $r_C$  can be assessed by fitting (2) to  $I_D$  versus  $V_G$  in Fig. 2. The results are given in Fig. 5 against gate voltage with temperature used as the parameter. It can be seen that: 1)  $r_C$  decreases with increasing gate voltage and then, critically, tends to saturate and 2)  $r_C$ decreases with decreasing temperature, in agreement with [9]. On the other hand, the Monte Carlo simulation [10] revealed a non-Ohmic property in the drain of the ultra short channel devices. This specific case of  $R_D = 0$  was also included in the calculation and the corresponding change in  $r_C$  was found to be very small. The reasons are that  $R_D$  of 75  $\Omega$ - $\mu$ m multiplied

Fig. 6. Measured mobility versus intrinsic gate voltage for three temperatures.

Fig. 7. Extracted mean-free path versus intrinsic gate voltage for three temperatures.

by the drain current (0.64 mA/ $\mu$ m in Fig. 2, for example) is negligible relative to  $V_D = 1$  V.

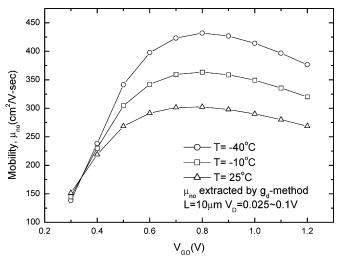

# IV. SEPARATED COMPONENTS

Long-channel devices from the same process were also employed to characterize near-thermal-equilibrium mobility  $\mu_{\rm no}$ . Fig. 6 displays measured mobility versus intrinsic gate voltage with temperature used as the parameter, which was obtained using a drain conductance method [14]. It can be seen that the mobility versus gate voltage curve can be separated into three well-known distinct components [14]: Coulombic scattering, phonon scattering, and surface roughness scattering. Further observation points out that different temperature dependencies exist between different components, as expected.

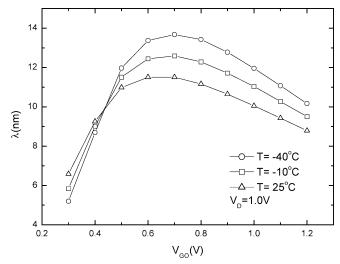

The mean-free-path  $\lambda$  in the  $k_BT$  layer is functionally linked to  $\mu_{\rm no}$  and  $\upsilon_{\rm inj}$  through  $\lambda=2\mu_{\rm no}(k_BT/q)/\upsilon_{\rm inj}$  [1]–[6]. Substituting the measured  $\mu_{\rm no}$  and calculated  $\upsilon_{\rm inj}$  into the formula,  $\lambda$  was quantified as plotted in Fig. 7 against intrinsic gate voltage with temperature used as the parameter. It can be seen that a critical gate voltage of 0.45 V exists, above which the mean-free-path decreases with increasing temperature, and below which

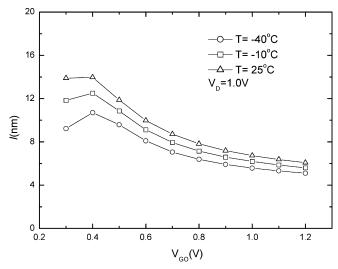

Fig. 8. Extracted  $k_BT$  layer width corresponding to Fig. 2.

an increase in temperature produces an increase in the mean-free-path. The former dependence can be attributed to the surface roughness scattering dominating while the thermal injection prevails in the latter. Since the magnitude of the mean-free-path has been known, the corresponding  $k_BT$ -layer width can readily be obtained from Fig. 5. The results are shown in Fig. 8 versus gate voltage for three temperatures. It can be seen that the  $k_BT$  layer narrows with increasing gate voltage and decreasing temperature. A change in temperature produces a broad spread in  $k_BT$ -layer widths, especially at low gate voltages.

## V. EVIDENCE

Evidence to confirm the validity of the above separation procedure is produced: 1) the near-source channel conduction-band profile; 2) the  $k_BT$  layer width in the literature involving sophisticated device simulation; and 3) an analytic temperature-dependent drain current model for the channel backscattering coefficients. The findings are also consistent with each other and therefore corroborate channel backscattering as the origin of the  $r_C$  in underlying devices.

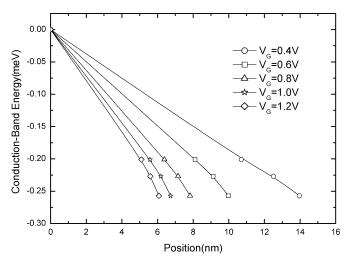

# A. Near-Source Channel Conduction-Band Profile

Within the framework of the channel backscattering theory, the channel conduction band is bent downward by a thermal energy  $k_BT$  while traversing from the injection point (i.e., the top of the source-channel junction barrier) to the end of the  $k_BT$  layer. According to this definition, the temperature dependent  $k_BT$ -layer widths in Fig. 8 were transformed into the near-source channel conduction-band profile as plotted in Fig. 9. Strikingly, it can be seen that the potential gradient increases in magnitude with increasing distance from the source. Indeed, sophisticated device simulations on bulk devices [8], [15] exhibited the same trend. Thus, the conduction-band profile in Fig. 9 can serve as strong evidence for the work.

# B. Existing Value of l

Hydrodynamic device simulation [15] on a 2.5-nm-thick physical gate oxide, 50-nm channel length bulk MOSFET yielded an l value of around 9.5 nm at  $V_G = V_D = 1$  V. Our

Fig. 9. Near-source channel conduction-band profile transformed from Fig. 8.

extracted value at the same applied biases is 6.7 nm (see Fig. 8) for a 1.65-nm-thick physical gate oxide, 68-nm gate length bulk MOSFET. We found that the difference between the two lvalues can almost be eliminated if the two factors are offset in advance. The first factor is the different potential drop across the source: the study in [15] conducted by Choi used 0.25 V, whereas we used 0.05 V. Therefore a downward shift of 0.2 V in gate voltage from 1 to 0.8 V is required for fair comparison, giving a corresponding l of 7.8 nm. The second factor is due to the different gate oxide thickness. A first-order approximation (0.2-V threshold voltage was assumed; the equivalent electrical gate oxide thickness in inversion was about 3.35 nm in [15] and 2.5 nm in our work) was performed to retain the same inversion-layer charge density, leading to an updated gate voltage of around 0.65 V. At this point the  $k_BT$  layer width becomes 9.3 nm, quite close to the 9.5-nm result exhibited in [15].

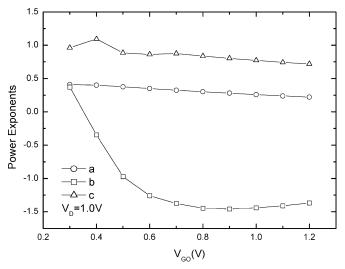

### C. Temperature-Dependent Drain Current Model for $\lambda/l$

An analytical temperature dependent drain current model in [9] is extended in general form as follows:

$$\frac{dI_D}{dT} \times \frac{1}{I_D} = \frac{-\eta}{(V_G - V_{th})} + \frac{a}{T} + \frac{2}{T}(b + 1 - a - c)\frac{1}{2 + \frac{\lambda}{T}}.$$

(6)

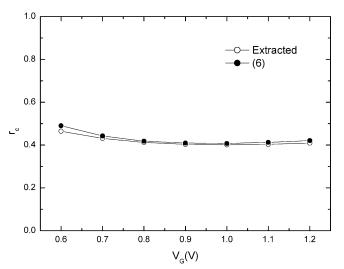

Here,  $\eta$  stands for the temperature coefficient of near-thermal-equilibrium threshold voltage. The other constants appear in the following power law relationship: the injection thermal velocity  $v_{\rm inj} \propto T^{\rm a}$ ; the low lateral-field mobility  $\mu_{\rm no} \propto T^{\rm b}$ ; and the width of the  $k_BT$  layer  $l \propto T^{\rm c}$ . The numerical constants a,b, and c can be determined from the temperature dependencies of the calculated  $v_{\rm inj}$  in Fig. 4, the measured  $\mu_{\rm no}$  in Fig. 6, and the extracted l in Fig. 8, respectively. The resulting power exponents are plotted in Fig. 10 against gate voltage. Then by substituting these constants and experimental drain currents into (6), we obtained the channel backscattering coefficients at 25 °C, as shown in Fig. 11. Again, a good agreement was achieved.

## VI. FURTHER DISCUSSION

Further interpretations and clarifications can be determined relative to the backscattering by the drain in the ultra short channel (10-nm channel length) double-gate MOSFET at

Fig. 10. Fitted power exponents versus gate voltage.

Fig. 11. Comparison of extracted  $r_C$  at 25 °C with that from (6).

${\rm V}_D=0.2~{\rm V}$  [10]. First, quasiballistic electrons moving out of the  $k_BT$  layer and entering into the remainder of the channel experience a process of energy loss via phonon emission. This loss in energy increases with increasing channel length, as in our device, which effectively prohibits backscattering from the drain reaching the beginning point of the channel. Second, the large drain voltage of 1 V applied in our work causes a large barrier height to be encountered near the drain, which significantly increases the difficulties the backscattered electrons from the drain have been overcoming the barrier height. Finally, in a bulk device operated in saturation as in our work, the distributions of the electric field and the current flow lines near the drain are essentially two dimensional, which effectively enlarges the path of the drain backscattering to the source.

The simulation work [10] further pointed out the possible difference between the distribution shape of the injection velocity and that of the reflection velocity. On the other hand, under the quasiballistic conditions (i.e., the energy loss in a backscattering event can be ignored on average), the events of multiple backscatterings through the  $k_BT$  layer can lead to a relationship

of  $r_C = l/(l+\lambda)$  (see [1, Chapter 2] for details). In other words, a simple form of  $r_C = l/(l+\lambda)$  can apply equally to the forward and backward flux streams. Therefore, according to the work of [10], if a single  $r_C$  is used, then the average reflection velocity at the top of the source-channel barrier should be expressed as the injection velocity  $v_{\rm inj}$  multiplied by a certain factor  $\theta \ (\geq 1)$ . Here,  $\theta$  is introduced to reflect the contribution of the fast carriers [10]:  $\theta = 1$  means that the distribution of the reflection velocity at the top of the source-channel barrier can be approximated by a hemi-Maxwellian distribution as that of the injection velocity; and  $\theta$  increases with the increasing importance of the fast carriers through an extended tail of the distribution profile. In a similar way leading to (1), the drain current in the presence of factor  $\theta$  can be derived as follows:

$$I_D = Q_{inv} v_{inj} \frac{(1 - \theta r_C)}{(1 + r_C)}.$$

(7)

As described in detail above, a single  $v_{\rm inj}$  as a first-order approximation appears to work well, suggesting  $\theta \approx 1$  in our work.

Therefore, we can now reasonably claim that the separated components, as well as their dependencies on temperature and bias, can be adequately used to describe the operation of the device within the framework of the channel backscattering theory. For example, at operating conditions of 25 °C and  $V_G = V_D =$ 1 V the conduction band from the injection point of the channel is bent down by a thermal energy of 25.7 meV to a distance of l = 6.7 nm (see Fig. 8). Then a bending of approximately 1 eV is subsequently developed across the remainder of the channel. The mean-free-path  $\lambda$  is 10.1 nm (also see Fig. 7) for backscattering in 6.7-nm-wide  $k_BT$  layer, effectively producing a backscattering coefficient  $r_C$  of 0.4. The mean-free-path is larger than the width of the layer, confirming the quasiballistic transport. The injected charge density from the source is 0.72  $\mu C/cm^2$  with the injection velocity of 1.48  $\times 10^7$  cm/sec. The incident flux stream multiplied by the transmission probability  $(= 1 - r_C)$  constitutes the drain current of 0.64 mA/ $\mu$ m. A similar argument can apply to other biases and temperatures.

## VII. CONCLUSION

Separation of channel backscattering coefficients in 68-nm gate length bulk n-channel MOSFETs has been systematically performed. Consistent evidence has confirmed the validity of the separation procedure and has corroborated channel backscattering as the origin of the assessed coefficients. Other interpretations and clarifications have been determined with respect to the backscattering by the drain, the injection and reflection velocity distributions, and the non-Ohmic property in the drain. The separated components have eventually been used to describe the operation of the underlying device within the framework of the channel backscattering theory.

#### ACKNOWLEDGMENT

One of the authors, M.-J. Chen, is deeply grateful to Dr. C. Choi, Department of Electrical Engineering, Stanford University, for the granted presentation slides of his Ph.D. dissertation entitled "Modeling of Nanoscale MOSFETs".

# REFERENCES

- [1] S. Datta, *Electronic Transport in Mesoscopic Systems*. Cambridge, U.K.: Cambridge Univ. Press, 1995.

- [2] M. S. Lundstrom, "Elementary scattering theory of the Si MOSFET," IEEE Electron Device Lett., vol. 18, pp. 361–363, July 1997.

- [3] F. Assad, Z. Ren, S. Datta, and M. S. Lundstrom, "Performance limits of silicon MOSFET's," in *IEDM Tech. Dig.*, Dec. 1999, pp. 547–550.

- [4] F. Assad, Z. Ren, D. Vasileska, S. Datta, and M. S. Lundstrom, "On the performance limits for Si MOSFET's: A theoretical study," *IEEE Trans. Electron Devices*, vol. 47, pp. 232–240, Jan. 2000.

- [5] M. S. Lundstrom and Z. Ren, "Essential physics of carrier transport in nanoscale MOSFET's," *IEEE Trans. Electron Devices*, vol. 49, pp. 133–141, Jan. 2002.

- [6] M. S. Lundstrom, Fundamentals of Carrier Transport, 2nd ed. Cambridge, U.K.: Cambridge Univ. Press, 2000.

- [7] G. Timp, J. Bude, K. K. Bourdelle, J. Garno, A. Ghetti, H. Gossmann, M. Green, G. Forsyth, Y. Kim, R. Kleiman, F. Klemens, A. Kornblit, C. Lochstampfor, W. Mansfield, S. Moccio, T. Sorsch, D. M. Tennant, W. Timp, and R. Tung, "The ballistic nano-transistor," in *IEDM Tech. Dig.*, Dec. 1999, pp. 55–58.

- [8] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of carrier velocity in deeply scaled NMOS: How close to the thermal limit?," *IEEE Electron Device Lett.*, vol. 22, pp. 95–97, Feb. 2001.

- [9] M.-J. Chen, H.-T. Huang, K.-C. Huang, P.-N. Chen, C.-S. Chang, and C. H. Diaz, "Temperature dependent channel backscattering coefficients in nanoscale MOSFETs," in *IEDM Tech. Dig.*, Dec. 2002, pp. 39–42.

- [10] M. Mouis and S. Barraud, "Velocity distribution of electrons along the channel of nanoscale MOS transistors," in ESSDERC Proc., Sept. 2003, pp. 147–150.

- [11] K.-N. Yang, H.-T. Huang, M.-C. Chang, C.-M. Chu, Y.-S. Chen, M.-J. Chen, Y.-M. Lin, M.-C. Yu, S. M. Jang, C. H. Yu, and M.-S. Liang, "A physical model for hole direct tunneling current in p<sup>+</sup> poly-gate pMOSFET's with ultrathin gate oxides," *IEEE Trans. Electron Devices*, vol. 47, pp. 2161–2166, Nov. 2000.

- [12] H. H. Mueller and M. J. Schulz, "Simplified method to calculate the band bending and the subband energies in MOS capacitors," *IEEE Trans. Electron Devices*, vol. 44, pp. 1539–1543, Sept. 1997.

- [13] K. Natori, "Ballistic metal-oxide-semiconductor field effect transistor," J. Appl. Phys., vol. 76, pp. 4879–4890, Oct. 1994.

- [14] S. I. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I — Effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, pp. 2357–2362, Dec. 1994.

- [15] C. Choi, "Modeling of nanoscale MOSFETs," Ph.D. dissertation, Stanford Univ., Stanford, CA, 2002.

**Huan-Tsung Huang** (S'90–M'00) received the B.E.degree in electrical engineering from National Cheng-Kung University, Taiwan, R.O.C., and the M.S. and Ph.D. degrees in electronics from National Chiao-Tung University, Taiwan, in 1988, 1990, and 2000, respectively.

From 1992 to 2000, he was with the Ta-Hua Institute of Technology as a Lecturer in the Electronic Department. In 2000, he joined the R/D Logic Technology Division, Taiwan Semiconductor Manufacturing Company (TSMC), Ltd., Hsinchu,

Taiwan, where he is engaged in characterization and development of advanced devices and gate stacks. His current research interests include leading edge-gate dielectric development, shallow-junction formation, and nano-device characterization.

Yi-chin Chou was born in Changhua, Taiwan, R.O.C., in 1980. He received the B.S. degree in electrical engineering from National Tsing-Hua University, Hsinchu, Taiwan, in 2002. He is currently pursuing the M.S. degree in the Silicon Mesoscopic System Laboratory, Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan.

His research interests are focused on device physics, modeling and simulation of silicon nano CMOS.

Rong-Ting Chen was born in Kaohsiung, Taiwan, R.O.C, in 1980. He received the B.S. degree in electrical engineering from National Dong-Hwa University, Hualien, Taiwan, in 2003. He is currently pursuing the M.S. degree in the Silicon Mesoscopic System Laboratory, Department of Electronics Engineering, National Chiao-Tung University, Hsinchu, Taiwan.

His research interests are focused on device physics and modeling of silicon nano CMOS.

Ming-Jer Chen (S'78–M'79–SM'98) received the B.S. degree in electrical engineering (with highest honors) in 1977 from National Cheng-Kung University, Taiwan, R.O.C., and the Ph.D. degree in electronics engineering in 1985 from National Chiao-Tung University (NCTU), Taiwan.

In 1985, he joined the faculty of the Department of Electronics Engineering, NCTU, where he became a full Professor in 1993. From 1987 to 1992, he served as a Consultant for Taiwan Semiconductor Manufacturing Company Ltd., Hsinchu, Taiwan, where he led

a team from NCTU and ERSO/ITRI to build up a series of process window and design rule. He has been granted six U.S. patents and six Taiwanese patents covering the high-precision analog capacitors, 1-T SRAM cell, dynamic threshold MOS, and ESD protection. During the 2000–2001 academic year, he was a Visiting Professor at the Department of Electrical Engineering and the Center for Integrated Systems, Stanford University, Stanford, CA. His research interests have long been focused on technology reliability physics and currently on nanoscale electronics. He has supervised 12 Ph.D. students and over 80 Master's students.

Dr. Chen is a member of Phi Tau Phi.

Yin-Ta Tseng was born in Chia-Yi, Taiwan, R.O.C. He received the B.E. degree in electrical engineering from National Cheng-Kung University, Taiwan, and the M.S. degree in electronics engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 1999 and 2003, respectively.

In 2003, he joined Taiwan Semiconductor Manufacturing Company (TSMC), Ltd., Hsinchu, Taiwan. His research interests center on the physics of semiconductor devices, nano-device modeling, and carrier transport.

**Po-Nien Chen** was born in Miao-Li, Taiwan, R.O.C. He received the B.S. and M.S. degrees in electrical engineering from National Chiao-Tung University, Taiwan, in 1999 and 2003, respectively.

In 2004, he joined Taiwan Semiconductor Manufacturing Company (TSMC), Ltd., Hsinchu, Taiwan. His research interests concentrate on the physics of semiconductor devices, nano-device characterizing/modeling, and the carrier-transport mechanism.

Carlos H. Diaz (M'86–SM'98) received the B.S. and M.S. degrees in electrical engineering from Universidad de Los Andes, Bogota D.C., Colombia, and the Ph.D. degree in electrical engineering from the University of Illinois at Urbana-Champaign.

He joined Taiwan Semiconductor Manufacturing Company (TSMC)'s Research and Development team, Hsin-Chu, Taiwan, R.O.C., in 1998. He is currently Deputy Director in the Logic Technology Division, responsible for the development of TSMC's logic transistor technology. He is TSMC's

representative to the ITRS PIDS TWG. Before joining TSMC, he was a Member of the Technical Staff in ULSI Laboratory, Hewlett-Packard Laboratories, Palo Alto, CA, working on process integration, device design, and physics reliability. While at HP, he was also a Lecturer on VLSI technology for the University of California at Berkeley extension program. He holds 15 U.S. patents, has published more than 60 papers in technical journals and international conferences, and has co-authored one book.

Dr. Diaz served in the International Conference on Simulation of Semiconductor Processes and Devices, the IEEE International Reliability Physics Symposium, and the EOS/ESD Symposium program committees. Currently, he is a member of the VLSI Technology Symposium, and a member of the technical program committees for Solid State Devices and Materials and the International Electron Devices Meeting. He was the recipient of two Semiconductor Research Corporation (SRC) inventor awards.