## Interface-blocking mechanism for reduction of threading dislocations in SiGe and Ge epitaxial layers on Si ( 100 ) substrates

T. H. Yang, G. L. Luo, E. Y. Chang, Y. C. Hsieh, and C. Y. Chang

Citation: Journal of Vacuum Science & Technology B 22, L17 (2004); doi: 10.1116/1.1781188

View online: http://dx.doi.org/10.1116/1.1781188

View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/22/5?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

#### Articles you may be interested in

Electroacoustic conversion in modulation-doped SiGe Si heterostructures

Low Temp. Phys. 34, 63 (2008); 10.1063/1.2832357

Influence of the cavity on the low-temperature photoluminescence of SiGe Si multiquantum wells grown on a silicon-on-insulator substrate

Appl. Phys. Lett. 88, 121901 (2006); 10.1063/1.2187433

Features of the Shubnikov-de Haas oscillations of the conductivity of a high-mobility two-dimensional hole gas in a SiGe Ge SiGe quantum well

Low Temp. Phys. 32, 82 (2006); 10.1063/1.2161933

Recombination activity and electrical levels of dislocations in p -type Si SiGe structures: Impact of copper contamination and hydrogenation

J. Appl. Phys. **96**, 6425 (2004); 10.1063/1.1812602

Evidence of Si SiGe heterojunction roughness scattering

Appl. Phys. Lett. 85, 4947 (2004); 10.1063/1.1828224

# Re-register for Table of Content Alerts

Create a profile.

Sign up today!

# Interface-blocking mechanism for reduction of threading dislocations in SiGe and Ge epitaxial layers on Si(100) substrates

#### T. H. Yang

Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan 30050, Republic of China

#### G. L. Luo<sup>a)</sup>

Microelectronics and Information Systems Research Center, Room 414, National Chiao Tung University, Hsinchu, Taiwan 30050, Republic of China

### E. Y. Chang, Y. C. Hsieh, and C. Y. Chang

Department of Materials Science and Engineering, National Chiao Tung University, Hsinchu, Taiwan 30050, Republic of China

(Received 23 January 2004; accepted 14 June 2004; published 13 October 2004)

A mechanism of interface blocking was proposed to reduce the threading dislocations in the SiGe and Ge layers on Si(100) substrates. In this work, epitaxial  $Si_{1-x}Ge_x/Si_{1-(x-y)}Ge_{x-y}$  and  $Ge/Si_yGe_{1-y}$  layers were grown by UHV/CVD. It was surprisingly found that if the variation of the Ge composition, y, across the interface of  $Si_{1-x}Ge_x/Si_{1-(x-y)}Ge_{x-y}$  or  $Ge/Si_yGe_{1-y}$  is higher than a certain value, most of the threading dislocations appear to be blocked and confined in the underlying  $Si_{1-(x-y)}Ge_{x-y}$  or  $Si_yGe_{1-y}$  layer by the interface. It implies that this finding can provide a simple way to grow high-quality relaxed SiGe and Ge layers on the Si substrates. © 2004 American Vacuum Society. [DOI: 10.1116/1.1781188]

## I. INTRODUCTION

Heterostructures of SiGe and Ge epitaxial layers on Si substrates have attracted considerable attention due to their potential device applications and compatibility with Si-based technology. In particular, strain-relaxed SiGe and Ge layers provide a virtual substrate for the growth of highelectron-mobility structures and for the integration of III-V devices on Si. In addition, the integration of Ge with Si is of much importance for the application of Ge photodetectors. The major problems of these relaxed layers are the high density of threading dislocations and the high surface roughness arising from the 4.2% lattice mismatch between Ge and Si. Various growth techniques and treatments have been developed to solve these problems. It has been reported that the compositionally graded buffer (CGB) layers,2 lowtemperature Si buffer layers,<sup>3</sup> compliant silicon-on-insulator (SOI) substrate, 4 two-step procedure, 5 and selective area growth combined with thermal cycle annealing<sup>6</sup> can be used to grow high-quality strain-relaxed SiGe and Ge layers. Among them, the CGB layers are the most practically and widely used ones today. However, the CGB layers still have two major challenges. First, these CGB layers often suffer from a thickness of  $\sim 10 \ \mu m$  with a Ge composition grading from 0 to 1.0, which increases crucially the price of SiGe devices and hinders their integration with conventional

Si-based circuits. Second, the CGB layers often exhibit a cross-hatch pattern, which makes the surfaces very rough.<sup>7</sup>

It has been<sup>8</sup> reported earlier that the strained isoelectronically In-doped GaAs layer grown on GaAs wafers allow one to reduce the dislocations density drastically, where the authors found that the interface formed between the In-doped GaAs layer and GaAs substrate can bend the dislocations. We believe that a similar mechanism can be easily used to grow SiGe and Ge layers with reduced dislocation densities on the Si(100) substrates.

#### II. EXPERIMENT

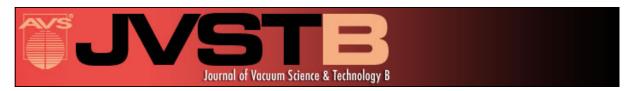

In our laboratory, the epitaxial SiGe and Ge layers were grown by UHV/CVD equipment using silane and germane as the Si and Ge sources. Usually, growth temperature of 550 °C was used to grow  $Si_{1-x}Ge_x$  layers with x < 0.3, and 420 °C was used to grow Ge layer and Si<sub>1-x</sub>Ge<sub>x</sub> layer with x > 0.8. The samples in this work were grown based on two structures (see Fig. 1). For the structure (a), a  $Si_{1-(x-y)}Ge_{x-y}$ was first grown. After in situ annealing it at 950 °C for 5 min for strain relaxation, a second layer  $Si_{1-x}Ge_x$  was then grown. For the structure (b), a Si<sub>v</sub>Ge<sub>1-v</sub> was first grown. After in situ annealing it at 750 °C for 15 min for strain relaxation, a Ge layer was subsequently grown. Finally, an annealing of 750 °C for 15 min was performed again for removing of defects that possibly generate in the Ge layer grown at low temperature. Transmission electron microscopy (TEM) was used to observe the dislocation distribution and

L17

a) Author to whom correspondence should be addressed; electronic mail: luogl@faculty.nctu.edu.tw

Fig. 1. Samples structures (a) and (b); their detail growth conditions were described in context.

interaction with the interfaces. These TEM measurements were carried out on a Philips Tecnai 20 microscope. The crystalline quality of Ge layer was additionally evaluated by the double-crystal x-ray diffraction (DCXD) measurement.

#### III. RESULTS AND DISCUSSION

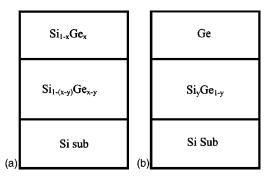

Figure 2 is a cross-sectional TEM (XTEM) image of a sample on which was grown directly a  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layer about 7500 Å. No measure was taken to control the dislocations. This sample was also annealed at 950 °C for 5 min for its full relaxation. From the image, a large number of threading dislocations are observed to generate from the interface of  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}/\mathrm{Si}$  and continue through the entire epitaxial layer to the surface.

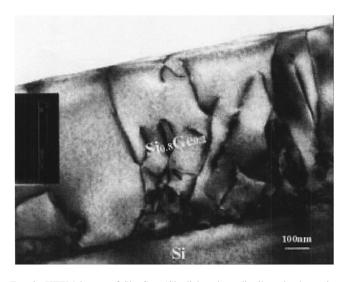

Figure 3 is an XTEM image of a sample on which was grown an epitaxial structure of  $\mathrm{Si}_{0.76}\mathrm{Ge}_{0.24}/\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  in which the first  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layer is about 1.2  $\mu\mathrm{m}$  thick, and the second  $\mathrm{Si}_{0.76}\mathrm{Ge}_{0.24}$  layer is about 0.5  $\mu\mathrm{m}$  thick. It is seen that some threading dislocations that generate within the first  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layer are blocked by the interface of  $\mathrm{Si}_{0.76}\mathrm{Ge}_{0.24}/\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$ , but others still penetrate through the interface to the top layer.

Fig. 2. XTEM image of  $\rm Si_{0.8}Ge_{0.2}/Si;$  dislocations distribute in the entire epitaxial layer.

Fig. 3. XTEM image of  ${\rm Si_{0.76}Ge_{0.24}/Si_{0.8}Ge_{0.2}/Si}$ ; some dislocations are blocked by the interface, but the other dislocations penetrate the interface.

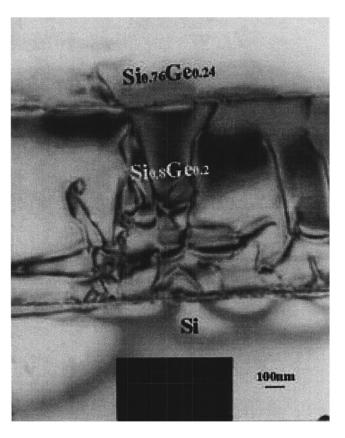

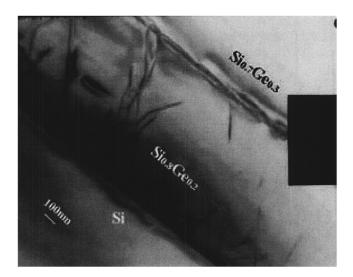

However, for the sample on which was grown an epitaxial structure of  $Si_{0.7}Ge_{0.3}/Si_{0.8}Ge_{0.2}$  in which the first  $Si_{0.8}Ge_{0.2}$  layer is about 1.2  $\mu$ m thick, and the second  $Si_{0.7}Ge_{0.3}$  layer is about 0.6  $\mu$ m thick, it is seen that the dislocations that generate within the first  $Si_{0.8}Ge_{0.2}$  layer are remarkably blocked by the interface of  $Si_{0.7}Ge_{0.3}/Si_{0.8}Ge_{0.2}$ . The threading dislocations that can penetrate through the interface are much reduced (see Fig. 4).

Fig. 4. XTEM image of  $\mathrm{Si_{0.7}Ge_{0.3}/Si_{0.8}Ge_{0.2}/Si}$  almost all the dislocations are blocked by the interface of  $\mathrm{Si_{0.7}Ge_{0.3}/Si_{0.8}Ge_{0.2}}$ .

(a)

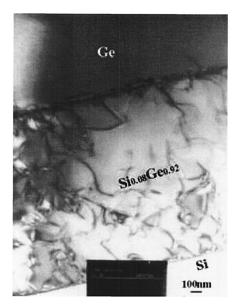

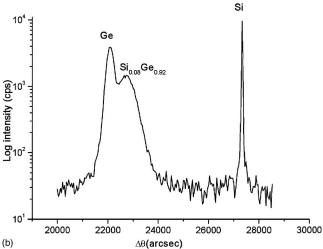

Fig. 5. (a) XTEM image of  $Ge/Si_{0.08}Ge_{0.92}/Si$ ; high-density of dislocations are blocked effectively by the interface of  $Ge/Si_{0.08}Ge_{0.92}$ ; (b) double-crystal x-ray diffraction result for this sample.

Figure 5(a) is an XTEM of a sample on which the first layer is a 1.5  $\mu$ m thick Si<sub>0.08</sub>Ge<sub>0.92</sub> layer, and the second layer is a 1.0  $\mu$ m thick Ge layer. It is surprisingly found that the high-density dislocations that generate within the Si<sub>0.08</sub>Ge<sub>0.92</sub> layer are also blocked drastically by the interface of Ge/Si<sub>0.08</sub>Ge<sub>0.92</sub>. The top Ge layer exhibits a good crystalline quality with a low threading dislocation density. Under the optical microscope, by counting the etch pits that were selectively etched by solution of CH<sub>3</sub>COOH:HNO<sub>3</sub>:HF:I<sub>2</sub> = 67 ml:20 ml:10 ml:30 mg for 10 s, we estimated that the dislocation density in this top Ge layer is about 6

$\times 10^6/\text{cm}^2$ . Figure 5(b) is the DCXD result for this sample. The peak of Ge is sharp, which also implies that the crystal-line quality of the top Ge layer is superior. Moreover, the total thickness of these two layers is only about 2.5  $\mu$ m, which is much less than that of traditional CGB structure.

The mechanism of interface blocking of dislocations is considered to be due to the dislocation bending behavior under the stress field. When the stress field around the interface is strong enough, the dislocation can be bent and traverse along the interface. From the XTEM images, it can be found that the interfaces of Si<sub>0.7</sub>Ge<sub>0.3</sub>/Si<sub>0.8</sub>Ge<sub>0.2</sub> and Ge/Si<sub>0.08</sub>Ge<sub>0.92</sub> (see Figs. 4 and 5) are rough. It implies that a strong nonuniform stress field exists at these interfaces. When the dislocations in these two samples meet the interfaces, they can be blocked very effectively. The phenomenon of dislocation bending under the stress can also be found in other material structures such as the GaN lateral overgrowth on the sapphire substrate reported by Ref. 9 recently, where the authors observed many dislocations bend at the edges of the GaN ridge due to the stress distributed there.

### **IV. CONCLUSION**

In conclusion, a mechanism of interface blocking was proposed to reduce the threading dislocations in the SiGe and Ge layers on Si(100) substrates. When the variation of the Ge composition, y, across the interface of  $\mathrm{Si}_{1-x}\mathrm{Ge}_x/\mathrm{Si}_{1-(x-y)}\mathrm{Ge}_{x-y}$  or  $\mathrm{Ge/Si}_y\mathrm{Ge}_{1-y}$  is higher than a certain value, most of the threading dislocations appear to be blocked and confined in the underlying  $\mathrm{Si}_{1-(x-y)}\mathrm{Ge}_{x-y}$  or  $\mathrm{Si}_y\mathrm{Ge}_{1-y}$  by the interface. For samples of  $\mathrm{Si}_{0.7}\mathrm{Ge}_{0.3}/\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}/\mathrm{Si}$  (y=0.1) and  $\mathrm{Ge/Si}_{0.08}\mathrm{Ge}_{0.92}/\mathrm{Si}$  (y=0.08), both top layers show low dislocation densities. It implies that the mechanism of interface blocking can be easily used to control the dislocations for growth of the relaxed SiGe and Ge layers on the Si substrates.

<sup>1</sup>D. J. Paul, Adv. Mater. (Weinheim, Ger.) 11, 191 (1999).

S. B. Samavedam and E. A. Fitzgerald, J. Appl. Phys. **81**, 3108 (1997).

C. S. Peng, H. Chen, Z. Y. Zhao, J. H. Li, D. Y. Dai, Q. Huang, J. M. Zhou, Y. H. Zhang, C. H. Tung, T. T. Sheng, and J. Wang, J. Cryst. Growth **201**, 530 (1999).

<sup>&</sup>lt;sup>4</sup>Y. H. Luo, J. L. Liu, G. Jin, J. Wan, K. L. Wang, C. D. Moore, M. S. Goorsky, C. Chih, and K. N. Tu, Appl. Phys. Lett. **78**, 1219 (2001).

<sup>&</sup>lt;sup>5</sup>A. Sakai, K. Sugimoto, T. Yamamoto, M. Okada, H. Ikeda, Y. Yasuda, and S. Zaima, Appl. Phys. Lett. 79, 3398 (2001).

<sup>&</sup>lt;sup>6</sup>H. C. Luan, D. R. Lim, K. K. Lee, K. M. Chen, J. G. Sandland, K. Wada, and L. C. Kimerling, Appl. Phys. Lett. **75**, 2909 (1999).

<sup>&</sup>lt;sup>7</sup>S. Yu. Shiryaev, F. Jenson, and J. W. Peterson, Appl. Phys. Lett. **64**, 3305 (1994).

<sup>&</sup>lt;sup>8</sup>H. Beneking, Cryst. Prop. Prep. **31**, 21 (1991).

<sup>&</sup>lt;sup>9</sup>T. S. Kuan, C. K. Inoki, Y. Hsu, D. L. Harris, R. Zhang, S. Gu, and T. F. Kuech, MRS Internet J. Nitride Semicond. Res. **5S1**, W2.6 (2000).