# Novel One-Step Aqueous Solutions to Replace Pregate Oxide Cleans

Tung Ming Pan, Tan Fu Lei, Fu Hsiang Ko, Tien Sheng Chao, Tzu Huan Chiu, and Chih Peng Lu

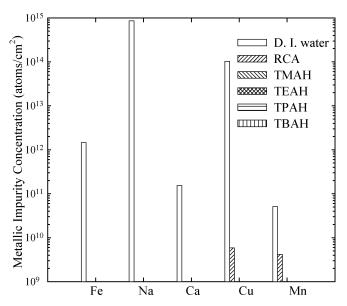

Abstract—We have developed a number of novel solutions to use for one-step pregate oxide cleaning; they are based on tetraalkylammonium hydroxides of varying alkyl chain lengths, namely tetramethylammonium hydroxide, tetraethylammonium hydroxide, tetrapropylammonium hydroxide (TPAH), and tetrabutylammonium hydroxide (TBAH). We added these surfactants together with ethylenediaminetetraacetic acid (EDTA) into the RCA SC-1 cleaning solution to enhance the efficiency of cleaning. With the exception of the TBAH solution, the cleaning efficiency of these solutions toward particles was 4%-7% higher than that of the conventional RCA method. Our cleaning methods have better efficiency toward the removal of Fe, Na, Ca, Cu, and Mn contaminants. We found that the conventional RCA method results in  $10^9$ – $10^{10}~atoms/cm^2$  of Cu and Mn after cleaning. The electrical breakdown field of MOS capacitors was enhanced when using the new cleaning method. The literature model for surface adsorption and double-layer formation explains the cleaning behavior of the tetraalkylammonium ion-containing solutions. The removal of surface particles and metallic contaminants and the degree of surface roughness agree with the model's predictions. We believe that the best solution for use in one-step cleaning—one that comprises EDTA and TPAH—can replace the traditional RCA cleaning method. This new method has great potential for pregate oxide cleaning because it has the advantages of faster cycle times, lower costs, and greater efficiency.

*Index Terms*—Cleaning, ethylenediaminetetraacetic acid (EDTA), pregate oxide, RCA method, tetrapropylammonium hydroxide (TPAH).

## I. INTRODUCTION

**D** URING the further miniaturization and integration of ultralarge scale integration (ULSI), it becomes increasingly critical to raise the cleanliness level of the silicon surface. Owing to the importance of a clean silicon surface prior to oxidation, the reliability of the gate oxide becomes even more

Manuscript received February 2, 2002; revised May 13, 2004. This work was supported in part by Merck-Kanto Advanced Chemicals Ltd. under Contract C87140 and in part by the National Science Council, Taiwan under Contract NSC88-2215-E009-045.

T. M. Pan was with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C. He is now with the Department of Electronics Engineering, Chang Gung University, Kweishan, Taoyuan 333, Taiwan, R.O.C.

T. F. Lei and T. H. Chiu are with the Department of Electronics Engineering and Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

F. H. Ko is with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C.

T. S. Chao is with the National Nano Device Laboratories, Hsinchu 300, Taiwan, R.O.C., and also with the Department of Electrophysics, National Chaio Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: tschao@cc.nctu.edu.tw).

C. P. Lu is with Merck-Kanto, Advanced Chemicals Ltd., Taoyuan 328, Taiwan, R.O.C..

Digital Object Identifier 10.1109/TSM.2004.831944

stringent than ever before [1]. The thickness of the gate oxide decreases from 13–16 to 6–11 Å as the device's dimensions decrease from 150 to 65 nm [2]. Gate-oxide integrity (GOI) is closely related to the lifetime of the device [3]. In general, incomplete cleaning will have a deteriorating effect on device performance. Each contaminant has a specific effect on device reliability: particles on the surface result in low breakdown fields and low yields, while organic contaminants decrease the oxidation rate and oxide quality [4]. Furthermore, metal contamination will cause a low breakdown field, a high junction leakage current, an increasing oxide trap, reduced minority carrier lifetime, shifted threshold voltage, and hot-carrier degradation. The well-known RCA cleaning method [5], which is universally applied during wafer processing for removing contaminants, was originally developed by Kern and Puotinen in 1970 and has been applied in industry for over 30 years. The essential cleaning process uses a sulfuric acid/hydrogen peroxide mixture (SPM, H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub>), dilute hydrofluoric acid (DHF, HF/H<sub>2</sub>O), and a two-step cleaning recipe. Cleaning with SPM is mainly undertaken to remove organic impurities on the surface, while the DHF is used for native oxide removal. The two-step cleaning recipes are Standard Clean One (SC-1, NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O) and Standard Clean Two (SC-2, HCl/H<sub>2</sub>O<sub>2</sub>/H<sub>2</sub>O). The ammonium hydroxide/hydrogen peroxide mixture (SC-1 or APM) is used for removing surface organic materials, particles, and some trace metals. The cleaning with the hydrochloric acid/hydrogen peroxide mixture (SC-2 or HPM) is undertaken to remove most metallic contaminants by forming soluble metal chloride complexes.

The problems of the conventional wet cleaning process include the number of steps and the high consumption of chemicals and ultrapure water. Reducing the number of cleaning steps is the most efficient way to overcome these drawbacks. A modified method based on conventional RCA cleaning has been proposed recently to meet the stringent challenges faced in the preparation of ultra-thin oxide [6]. The concept of using onestep cleaning has been proposed in the literature for lowering the process cost and cycle time. For example, Ohmi et al. [7] proposed a new advanced wet-chemical cleaning process that omits the RCA SC-2 step when highly purified HF solution is used as the last step prior to gate oxide growth. IMEC [6] proposed a cleaning recipe that does not require either NH<sub>4</sub>OH or HCl. The spiking of tetramethylammonium hydroxide (TMAH) into cleaning solutions can enhance the particle removal efficiency, and spiking ethylenediaminetetraacetic acid (EDTA) can decrease contamination by metallic impurities [8], [9]. In a previous study [9], we found that the length of the alkyl groups of tetraalkylammonium hydroxides can have important effects on

TABLE I

COMPONENTS OF THE SOLUTIONS USED FOR PREGATE OXIDE CLEANING

| Solutions | NH4OH | TAAH (0.26M)             | EDTA    |

|-----------|-------|--------------------------|---------|

| A         | 29%   | 0                        | 0       |

| В         | 29%   | 2.38% TMAH (MW = 91)     | 100 ppm |

| С         | 29%   | 3.84% TEAH (MW = 147)    | 100 ppm |

| D         | 29%   | 5.31% TPAH (MW = $203$ ) | 100 ppm |

| Е         | 29%   | 6.77% TBAH (MW = 259)    | 100 ppm |

TAAH = tetraalkylammonium hydroxide

the cleaning process. To the best of our knowledge, however, there are no reports that discuss how alkyl chain lengths affect the pregate oxide cleaning process. In principle, finding the optimal alkyl chain length would enhance the cleaning reliability and efficiently.

In this paper, several tetraalkylammonium hydroxides (TAAHs) of varying alkyl chain lengths were added into the SC-1/EDTA solution mixture to test their efficiency toward gate oxide cleaning. These TAAHs include tetramethylammonium hydroxide (TMAH), tetraethylammonium hydroxide (TEAH), tetrapropylammonium hydroxide (TPAH), and tetrabutylammonium hydroxide (TBAH). The aim of this study, therefore, was to investigate the influences of the spiking TAAHs on the hydrophilicity and roughness of the silicon surface. We discuss the mechanism of the interaction between the tetraalkylammonium solution and the silicon surface. Furthermore, we analyzed the abundance of particular, organic, and metallic impurities to evaluate the efficiency of the cleaning processes. We also have carefully evaluated the electrical characteristics of the gate oxide after its cleaning with the various solutions.

### II. EXPERIMENTAL

## A. Cleaning Solutions and Capacitor Fabrication Process

The compositions of the water-based cleaning solutions are specified in Table I. With the exception of the control solution, all other solutions are spiked with a predetermined concentration of either TMAH, TEAH, TPAH, or TBAH, and are spiked also with high-purity EDTA (MW = 292) having four values of p $K_a$  [10] of 1.99, 2.67, 6.16, and 10.26. All reagents used were of electronic or higher grade and were obtained from Merck (Darmsadt, Germany).

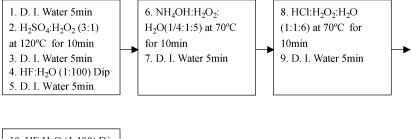

Metal oxide semiconductor (MOS) capacitors were fabricated on 6-in diameter, (100)-phase-oriented p-type wafers having a resistivity of 15–25  $\Omega$  · cm. All wafers were first cleaned by the standard RCA clean method. A 5000-Å field oxide was thermally grown at 1050 °C for 1 h for the isolation layer. The active region, having an area of  $10^{-4}$  cm<sup>2</sup>, was first defined by lithography (ASML PAS-2500 G-line stepper). The FH-6400L G-line resist (Fuji-Hunt Corp.) was spin-coated on hexamethyldisilazane (HMDS) vapor-primed wafer. The resist was then soft-baked on a hot plate at 90 °C for 1 min. After 436-nm light exposure by a stepper, the wafer was again baked at 120 °C for 1 min. The resist exposed with light could be developed using a 2.38% tetramethylammonium hydroxide solution. Finally, the hard bake was applied to the wafer. After lithography, the oxide was etched using the BOE solution  $(HF/NH_4F = 1:6)$ , and these wafers were then cleaned using either the traditional or one-step cleaning solutions (see Fig. 1). Immediately, a gate oxide of  $43.0 \pm 2.4 - \text{Å}$  thickness was grown thermally at 900 °C. The gate oxide thicknesses were  $43.0 \pm 3.6$ ,  $43.0 \pm 3.2$ , and  $43.0 \pm 4.5$  Å for the A, C, and E cleaning processes, respectively,  $44.0\pm2.9$  Å for the B cleaning processes, and  $42.5 \pm 2.6$  Å for the D cleaning processes. After oxidation, a 3000-Å poly-Si film was deposited at 620 °C in a low-pressure chemical vapor deposition (LPCVD) system. The poly-Si film was then doped with POCl<sub>3</sub> at 950 °C for 30 min, which resulted in resistivity of 20–30  $\Omega$ /cm<sup>2</sup>. A 5000-Å Al film was deposited on the wafer using a thermal coater. The gate dielectric of the MOS capacitor was defined by lithography, and then Al and poly-Si films were etched by wet solutions. The backside of the wafer was also deposited with a 5000-Å Al film using the evaporation method. Finally, all the samples were sintered at 400 °C for 30 min in an N2 atmosphere to form good ohmic contacts.

## B. Instrumental Analysis and Electrical Characterization

The thickness of gate oxide was evaluated using a SOPRA Model SE5 ellipsometer at four replicate measurements. The wafers were then placed in an ambient environment (outside) to obtain particle-contaminated wafers. These contaminated wafers were cleaned using the different cleaning solutions, followed by a rinse with DI water for 10 min. The efficiency of particle removal was obtained by measuring the number of particles before and after the cleaning process. The number of particles having sizes  $> 0.2 \mu m$  was counted using a Tencor Surfscan Model 4500 system. The surface roughness of the silicon wafer was measured using a Digital Instruments DI-5000 atomic force microscope (AFM). The amount of residual organic material on the poly-Si surface was determined using a Hitachi UG-21 thermal desorption system (TDS) and a UG-400P atmospheric-pressure-ionization mass spectrometer (APIMS). The desorption temperature of the TDS-APIMS was ramped from room temperature to 600 °C at a rate of 10 °C/min. The surface out-gassing was analyzed at m/e 16, 30, 44, and 58 (m/e is the mass-to-charge ratio of a specific molecular ion). To test the cleaning efficiencies of the various recipes toward metallic impurities, the wafers were subjected to immersion in a solution of a mixture of Fe, Na, Ca, Cu, and Mn ions (100 ppm each). The abundance of metallic impurities on the wafer before and after cleaning was determined using a RIGAKU Model 3700 total reflection X-ray fluorescence spectrometer (TXRF; the incident X-ray angle was 0.07°). The electrical properties, including the current density versus electric field and the time-dependent dielectric breakdown (TDDB), were measured using a Hewlett-Packard (HP) 4156B semiconductor parameter analyzer. The flat-band voltage was obtained by using a Keithley C-V system.

## III. RESULTS AND DISCUSSION

## A. Physical and Chemical Properties of Pregate Oxide Cleaning

We measured both the roughness and particle numbers present on the silicon surface after cleaning with the different solutions listed in Table I. TXRF and TDS-APIMS techniques

## Traditional cleaning step

10. HF:H<sub>2</sub>O (1:100) Dip 11. D. I. Water 5min 12. Spin Dry

## One-step cleaning step

Fig. 1. Comparison of the traditional cleaning and one-step cleaning procedures.

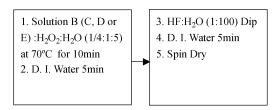

Fig. 2. Particle removal rate performance using the different cleaning methods; n=3.

were used to test the cleaning efficiency for metallic impurities and residual organics, respectively. Fig. 2 presents the observed residual particle numbers on the silicon surface after cleaning with the different solutions. The particle numbers on contaminated wafers before cleaning are 4000–6000 pieces, while those after cleaning are about 50–300 pieces. Apart from solution E (spiking with TBAH), we note that our one-step cleaning method has a significantly higher removal efficiency for particles relative to the traditional cleaning method (RCA).

The proposed surface adsorption and double-layer formation model [9] is very suitable for explaining the cleaning effect for surface particles in these systems. The model mentions that the tetraalkylammonium cations first adsorb onto the hydrophobic surface and the layer is positively charged. Then, the second layer is negatively charged with the anions (e.g., hydroxide). The contaminated particles before cleaning can be classified into hydrophilic and hydrophobic types. The hydrophilic particle has a weak interaction with silicon surface under alkaline condition, while the hydrophobic particle shows stronger interaction. [9] As the contaminated wafer with hydrophilic particles immerses into various tetraalkylammonium cleaning solutions, the effect of the solution composition is not significant due to weak attraction of the particle to the wafer surface. However, for the wafer with hydrophobic particles, the double-layer model plays an important role on explaining the cleaning efficiency. By using cleaning solutions B-D, both the surface of hydrophobic particle and silicon wafer can be gradually adsorbed by tetraalkylammonium ions for the first layer described in the model above. The surface adsorption of tetraalkylammonium ions facilitates the hydrophobic particle removal from the silicon surface by reducing the attraction. In contrast, cleaning solution E possesses the largest tetraalkylammonium ions cannot remove the hydrophobic particles from the silicon surface as efficiently because of geometric or steric effects. We speculate the tetrabutylammonium ions form a double-layer on contaminated particle and silicon surface except for their interface. Hence, their interface with van der

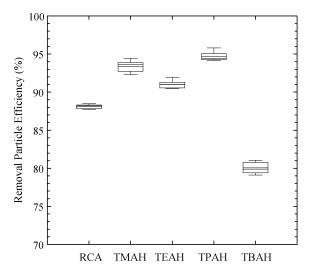

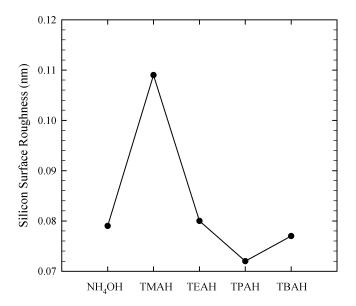

Fig. 3. Variation of silicon surface roughness  $(R_{\rm rms})$  after applying the various cleaning methods; n=3.

Waals attraction does not easily separate by cleaning solution E. In addition, the traditional method using cleaning solution A is not effective for adsorbing at the boundary regions of silicon as a result of the more hydrophilic character of NH<sub>4</sub>OH. These features explain why cleaning solutions B–D are effective on the issue of particle removal.

We also investigated the effect of the various cleaning methods on silicon-surface roughness. Fig. 3 illustrates the roughness that results from the various cleaning methods. The silicon surface obtained after cleaning with the TMAH-containing solution has the highest surface roughness. The TEAH, TPAH, and TBAH cations are initially adsorbed strongly in the primary layer, which prevents the direct reaction and etching of the hydroxide ions from the second layers [9]. The tetramethylammonium cation forms only weak interactions with the silicon surface, so, wet etching by the hydroxide ion occurs more easily. Solution A exhibits the highest degree of hydrophilicity. Because of the relatively hydrophobic character of the silicon, the NH<sub>4</sub><sup>+</sup> and OH<sup>-</sup> ions do not approach the surface readily and, hence, the etching rate of solution A is lower than that of solution B.

Fig. 4 displays the abundance of metallic contaminants on the silicon surface after cleaning using the various methods. Apart from the traditional cleaning method (solution A), the metallic impurities on the silicon surface cannot be detected when using our one-step cleaning process. This result is consistent with our findings reported in a previous publication [9] that spiking EDTA (100 ppm) into cleaning solutions can help in the removal of metal impurities. Under the alkaline conditions (pH > 12) of our proposed cleaning solutions, all the acidic protons of EDTA are fully removed (see values of p $K_{\rm a}$  listed above), and so the EDTA ions have the capability of undergoing hexadentate coordination with the metals ions. As a result, the surface metal impurities are removed efficiently when EDTA is added to the solution. In using the one-step cleaning method with tetraalky-lammonium-containing solutions, our greatest concern was the

Fig. 4. Metallic deposition on the silicon surfaces after RCA and the different cleaning methods; n=3.

nature of the interaction between the metal ions and the silicon surface. Interestingly, we found that the surface adsorption of tetraalkylammonium ions results in electrostatic repulsive forces that help in the removal of metal cations from the wafer's surface. The metal oxide, however, may be taken away from the surface by the adsorption of tetraalkylammonium ions. Another important evidence for this mechanism is to check the surface for residual TAAH organic material. The intensity of the surface organic materials was determined by TDS-APIMS measurement. The results indicate that the peak intensities of residual CH<sub>4</sub>, C<sub>2</sub>H<sub>6</sub>, C<sub>3</sub>H<sub>8</sub>, and C<sub>4</sub>H<sub>10</sub> after one-step cleaning with solutions B–E were in the range of 1-to-5-fold higher than when using the traditional method with solution A. Furthermore, the electrical results reported below verify that such levels of residual organic materials have no deteriorating effects.

## B. Electrical Properties After Cleaning With the Various Solutions

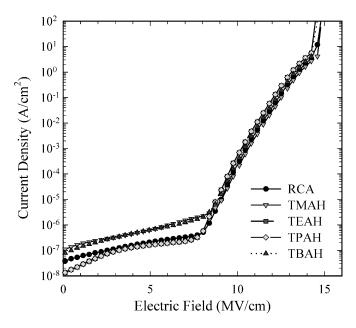

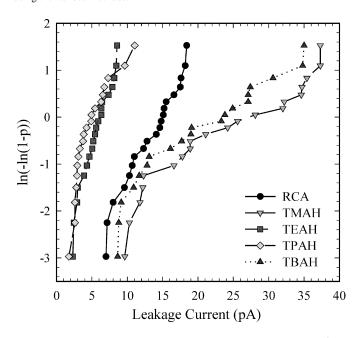

Fig. 5 illustrates the current density versus electric field characteristic (J-E characteristic) of the MOS capacitor after cleaning with the different solutions. The MOS capacitor obtained after one-step cleaning with solutions C and D exhibits the lowest leakage current density among the series. In contrast, the MOS capacitor obtained after cleaning with solutions B and E displays the largest leakage current density. Fig. 6 presents the Weibull distribution of leakage current at the same electric field (E = 1 MV/cm); it is clear that the device cleaned with solution D has the lowest distribution among these devices, and the device cleaned with solution B exhibits the widest and highest leakage-current distribution. Together with the findings from Figs. 5 and 6, the one-step cleaning solution D, which comprises TPAH and EDTA, is the best choice for achieving a high degree of device cleaning. These observations follow the same trends for the solutions removing particles and metallic impurities as described above. The greatest degradation of electrical properties after washing with solution B (TMAH and

Fig. 5. Current density versus the electric field characteristic of MOS capacitors having an oxide thicknesses of 4.3 nm, obtained after cleaning by using the various methods.

Fig. 6. Weibull distribution of leakage current at the same electric field ( $\rm E=1~MV/cm)$ ) of the MOS capacitors, obtained after cleaning with the different solutions.

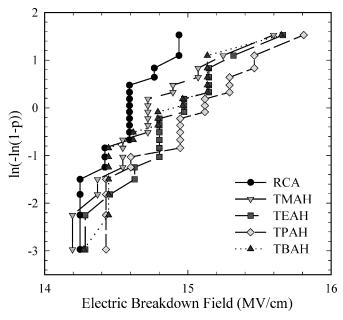

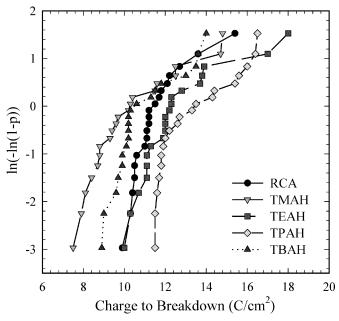

EDTA) is due to the high silicon surface roughness, as presented in Fig. 3. Fig. 7 presents the electric breakdown fields for the devices cleaned with the various recipes. It is obvious that the traditional method (RCA clean) results in a device having the lowest breakdown electric field in the series. A constant current stressing was used to determine the GOI reliability. In this measurement, an electron current is injected by tunneling through the oxide in the device. The gate voltage of the MOS capacitor is measured when the Si substrate is applied with a positive bias. Hence, for a p-type Si substrate, electrons are injected from the interface of poly-Si/SiO $_2$  to the interface of SiO $_2$ /Si. Fig. 8 displays the resultant charge to breakdown ( $Q_{\rm bd}$ ) under

Fig. 7. The Weibull distribution of the breakdown electric field of the MOS capacitors having an oxide thickness of 4.3 nm, obtained after cleaning by using the various methods.

Fig. 8. Charge-to-breakdown ratios of the MOS capacitors, obtained after cleaning by using the different methods. The thickness of the oxide layer is 4.3 nm.

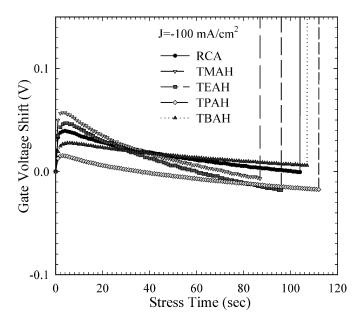

a constant current stressing of  $-0.1~\text{A/cm}^2$ . The device cleaned with solution D displays a larger value of  $Q_{\rm bd}$  than do those cleaned with the other solutions, while solution B exhibits the lowest distribution among the four cleaning solutions. It is found that  $Q_{\rm bd}$  and  $E_{\rm bd}$  do not show the same trends. This mechanism is very complex, but the trends when using solution D are clear. Therefore, this electrical observation also clearly suggests that solution D, which comprises TPAH and EDTA, is the best choice for cleaning. Fig. 9 depicts the charge trapping characteristics of capacitors cleaned with the various solutions under a constant current stressing of  $-0.1~\text{mA/cm}^2$ .

Fig. 9. Gate-voltage shift versus stress time under a constant current stress at  $-0.1\,\mathrm{mA/cm^2}$  of MOS capacitors, obtained after cleaning by using the different methods. The thickness of the oxide layer is 4.3 nm.

This figure also reveals that capacitors cleaned with solution D have a smaller voltage shift than do those cleaned with the other solutions. This improvement implies that this cleaning condition traps fewer electrons and has a lower rate of electron trapping. After careful evaluation of the cleaning solutions with respect to electrical characterization of the substrates, we believe that a cleaning solution containing TPAH and EDTA can be used to replace the conventional RCA method for pregate oxide cleaning.

#### IV. CONCLUSION

In this paper, we have demonstrated novel solutions for pregate oxide cleaning. By preparing a surfactant (TAAH) and a chelating agent (EDTA) into the NH<sub>4</sub>OH alkaline aqueous solution, the efficiency of the removal of particles and metals and the electrical characteristics of the capacitors are significantly improved. This finding can be explained by surface adsorption and double-layer formation of the tetraalkylammonium ions. Together with the time saved, the lower chemical consumption, and the need for less process water, the process of washing with a solution containing TPAH and EDTA seems to have a very promising future for pregate oxide and high-k gate oxide cleaning.

### REFERENCES

- [1] C. Hu, "Gate oxide scaling limits and project," *IEDM Tech. Dig.*, vol. 1996, pp. 319–322.

- [2] Semiconductor Industry Association, International Technology Roadmap for Semiconductor Updated, 2002.

- [3] I. Chen, S. E. Holland, and aC. Hu, "Electrical breakdown in thin gate and tunneling oxides," *IEEE Trans. Solid-State Devices*, vol. 20, pp. 333–342, Feb. 1985.

- [4] C. Y. Chang and S. M. Sze, ULSI Technology. New York: McGraw-Hill, 1996, ch. 2, p. 61.

- [5] W. Hern and D. A. Puotinen, "Cleaning solutions based on hydrogen peroxides for use in silicon semiconductor technology," RCA Rev., vol. 31, pp. 187–205, 1970.

- [6] M. M. Heyns, S. Verhaverbeke, M. Meuris, P. W. Mertens, H. Schmidt, M. Kubota, A. Philiposian, K. Dillenbeck, D. Graft, A. Schnegg, and R. De Blank, "New wet cleaning strategies for obtaining highly reliable thin oxides," in *Proc. Mat. Res. Soc. Symp.*, 1993, p. 35.

- [7] T. Ohmi, "Advanced wet chemical cleaning for future ULSI fabrication," in *Proc. 184th Meeting Electrohem. Soc.*, New Orleans, LA, 1993, pp. 495–496.

- [8] S. Verhaverbeke, M. Meuris, P. W. Mertens, M. M. Heyns, A. Philipossian, D. Graf, and A. Schnegg, "The effect of metallic impurities on the dielectric breakdown of oxides and some new ways of avoiding them," in *IEDM Tech. Dig.*, 1991, pp. 71–74.

- [9] T. M. Pan, T. F. Lei, T. S. Chao, M. C. Liao, F. H. Ko, and C. P. Lu, "One-step cleaning solution to replace the conventional RCA two-step cleaning recipe for pregate oxide cleaning," *J. Electrochem. Soc.*, vol. 148, pp. G315–G320, 2001.

- [10] J. Bjerrum, G. Schwarzenbach, and L. G. Sillen, Stability Constants. London, U.K.: Chemical Society, 1957, p. 76.

Tung Ming Pan was born in Taipei, Taiwan, in 1970. He received the B. S. degree from the National Chiao-Tung University (NCTU), Taiwan, R.O.C., in 1997 and the Ph.D. degree from the Institute of Electronics, NCTU, in 2001.

From 2000 to 2002, he was with the LOGIC Development Department, Technology and Process Development Division (TD), United Microelectronics Corporation (UMC), as a Principal Engineer. He was engaged in developing the 0.1- $\mu$ m device and process. Then, he transferred to the Reliability

Engineering, Quality and Reliability Assurance Division. He was responsible for 0.1- $\mu$ m device reliability and quality. In 2002, he jointed the Mixed-Signal Team, Elansat Technologies Corporation as a Senior Engineer. He was engaged to design high-speed and low power analog-to digital converter (ADC) and digital-to-analog converter (DAC). In 2004, he joined the faculty of the Department of Electronics Engineering, Chang Gung University, Taiwan, R.O.C., as an Assistant Professor. His current research areas focus on the cleaning processes of ultrathin oxynitride films, high-k gate dielectric materials, and device reliability for ultralarge scale integrated devices.

Prof. Pan won the first prize of the Lam Ph.D. Dissertation Award in 2001.

**Tan Fu Lei** was born in Keelung, Taiwan, P. R. China, on September 17, 1944. He received the B.S. degree in electrical engineering from the National Cheng Kung University, Tainan, Taiwan, in 1967 and the M.S. and Ph.D. degrees in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 1970 and 1979, respectively.

From 1970 to 1972, he was an Engineer with the Fine Products Microelectronics Corporation, Taiwan, working on the fabrication of small-signal transistors. From 1980 to 1982, he was the Plant Manager of Photronic Corporation, Taiwan. In 1983, he joined the faculty of the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University as an Associate Professor, where he is currently a Professor. From 1984 to 1986, he was the Director of the Semiconductor Research Center. From 1991 to 1998, he was also the Deputy Director of the National Nano Device Laboratory.

**Fu Hsiang Ko** was born in Hsinchu, Taiwan, in 1965. He received the B.S. degree in chemistry and the Ph.D. degree in nuclear science from the National Tsing Hua University, Taipei, Taiwan, in 1989 and 1996, respectively, and the M.S. degree in chemistry from the National Taiwan Normal University, Taipei, R.O.C., in 1991.

He joined the National Nano Device Laboratories, Hsinchu, Taiwan, as an Associate Researcher in October 1996, where he is currently engaged in developing the radioactive tracer and analytical methods

on lithographic and cleaning processes.

**Tien Sheng Chao** was born in Penghu, Taiwan, in 1963. He received the Ph.D. degree in electronics engineering from the National Chiao-Tung University, Hsinchu, Taiwan, in 1992.

He joined the National Nano Device Laboratories in July 1992 as an Associate Researcher, and became a Researcher in 1996, where he was engaged in developing the thin dielectrics preparations and cleaning processes. He joined the Department of Electrophysics, National Chiao Tung University as an Associate Professor in August 2001.

Chih Peng Lu was born in Tainan, Taiwan, 1959. He received the B.S. degree in chemistry from the National Tsing Hua University, Taipei, Taiwan, in 1981 and the M.B.A. from Saginaw Valley State University, University Center, Michigan, in 1998.

He is currently the Managing Director of Merck-Kanto Advanced Chemicals Ltd., Taoyuan, Taiwan.

**Tzu Huan Chiu** was born in Taichung, Taiwan, 1976. He received the B.S. degree in electronics engineering and the M.S. degree from the National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1998 and 2000, respectively.

His research areas focus on the development of novel cleaning solutions for ultralarge scale integrated applications.