Ceramics International 30 (2004) 1101-1106

www.elsevier.com/locate/ceramint

# Correlation between deep depletion and current–voltage saturation of SrTiO<sub>3</sub> gate dielectric capacitor

C.Y. Liu, T.Y. Tseng\*

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, ROC

Received 27 November 2003; accepted 22 December 2003

Available online 24 April 2004

### **Abstract**

$SrTiO_3$  (STO) gate dielectrics were deposited on p-type silicon substrate by radio-frequency (rf) magnetron sputtering in an  $Ar-O_2$  and  $Ar-N_2$  mixed ambient to form metal/insulator/semiconductor (MIS) capacitor to investigate capacitance–voltage (C-V) and current–voltage (I-V) characteristics. Schottky emission and Fowler–Nordheim tunneling mechanisms were responsible for the leakage current of nitrogen-grown STO-based MIS capacitors at the low and high electric field under accumulation condition, respectively, while the generation current dominated the leakage mechanism under the inversion condition due to the highly leaky insulator and the lack of electrons. The depletion width under the inversion condition would broaden to generate more electrons to maintain the leakage current and lead to capacitance decreasing under higher bias voltage, which is called as deep depletion. Therefore, the deep depletion and leakage current saturation under inversion condition would occur at the same time. The correlation between the deep depletion and the leakage mechanism in STO-based gate dielectric capacitor under inversion condition was used to extract the generation lifetime of silicon substrate. The normalized C-V measurements at 1 kHz under illumination were also made to examine the results of extracted generation lifetime. The extracted generation lifetime could provide a simple method to judge the quality of silicon substrates.

© 2004 Elsevier Ltd and Techna Group S.r.l. All rights reserved.

Keywords: A. Films; C. Electrical properties; C. Dielectric properties; C. Lifetime; E. Capacitors; SrTiO<sub>3</sub>

### 1. Introduction

Continuous device scaling is being performed by semiconductor industry to have better performance, high packaging density, and low cost [1]. With the device scaling, the thickness of gate dielectrics should also be scaled to have better channel control. Silicon dioxide serves as a good insulator material for gate dielectric because of its good electrical properties and process compatibility. However, conventional silicon dioxide that scales less than 2 nm will have unacceptably large leakage current due to direct tunneling mechanism. Therefore, materials with large dielectric constant could be used as alternative gate dielectrics to have the same equivalent oxide thickness (EOT) and thicker film to avoid large leakage current of direct tunneling mechanism. Many materials such as ZrTiO<sub>4</sub> [2], Al<sub>2</sub>O<sub>3</sub> [3], HfO<sub>2</sub> [4], ZrO<sub>2</sub> [5], and STO [6], have been investigated as alternative gate dielectrics. In the metal/ferroelectric/insulator/semiconductor

(MFIS) capacitors, STO could match the ferroelectric material to reduce the operation voltages of the capacitors due to its high dielectric constant [7]. Furthermore, STO is a perovskite-type material which provides a good buffer layer for the growth of perovskite-type ferroelectric thin films and can be epitaxially grown on silicon substrate.

Capacitance–voltage (C-V) characteristics of metal/insulator/semiconductor (MIS) capacitors are extensively used to study the dielectric and interfacial properties. Current–voltage (I-V) characteristics are also used to investigate the conduction mechanisms of MIS capacitors. Compared with conventional silicon dioxide, high-k gate dielectrics with larger leakage current should have some different C-V and I-V characteristics. However, the investigations of C-V and I-V characteristics for high-k gate dielectrics usually focus on the characteristics under accumulation condition. The systematic investigation of the C-V, I-V characteristic and their correlation under inversion condition is still lacking. Under inversion condition, the electron source of leakage current is from the silicon substrate. When the leakage current is too large, the supply of electrons from the substrate

<sup>\*</sup> Corresponding author. Tel.: +886-3-5731879; fax: +886-3-5724361. E-mail address: tseng@cc.nctu.edu.tw (T.Y. Tseng).

is not enough to maintain a large current. Therefore, the leakage current under inversion condition will be saturated. While the bias voltage under inversion condition is larger. more electrons would be generated to support higher leakage current. The depletion layer under inversion condition would broaden to generate more electrons and simultaneously deep depletion occurs. Generally, the substrate dopant concentration is extracted with the minimum of high-frequency capacitance. However, it is not easy to decide the value of minimum high-frequency capacitance while the deep depletion occurs. Nevertheless, the substrate dopant concentration could be extracted from the deep depletion of C-V characteristics. It can also be concluded that the leakage current under inversion condition obeys the generation current due to bulk trap. From the correlation between the C-V and I–V characteristics under inversion condition, the generation lifetime can also be extracted. It provides an easy method to examine the quality of silicon substrate processed under different conditions.

### 2. Experimental procedure

SrTiO<sub>3</sub> (STO) thin films were deposited at 500 °C on the 4 in. boron doped p-type (100) silicon wafer with  $1-10\,\Omega$  cm by radio-frequency (rf) magnetron sputtering technique with a 3 in. stoichiometric SrTiO3 target. Before deposition, the silicon substrates were cleaned by a standard RCA cleaning process and chemically etched in dilute HF solution to remove the native oxide. Then STO films were prepared at fixed rf power (150 W) and constant pressure (40 m Torr) which was maintained by the Ar-N<sub>2</sub> or Ar-O<sub>2</sub> mixed ambient with the 4:1 mixing ratio and a total flow of 10 sccm. The film thickness determined by ellipsometry ranged from 11 to 30 nm. The composition of STO thin films was analyzed by X-ray photoelectron spectroscopy (XPS). For the electrical measurement, Al metal layer was deposited by thermal evaporation and finally the top electrode with  $7 \times 10^{-4}$  cm<sup>2</sup> area was formed with lithography technique. Al was also used as backside electrode for ohmic contact by thermal evaporation. The electrical characteristics were evaluated by C-V and I-Vmeasurements on STO-based MIS capacitors at room temperature with Agilent 4284A LCR meter at 100 kHz and 4156A semiconductor parameter analyzer, respectively.

### 3. Results and discussion

## 3.1. Capacitance-voltage and current-voltage characteristics

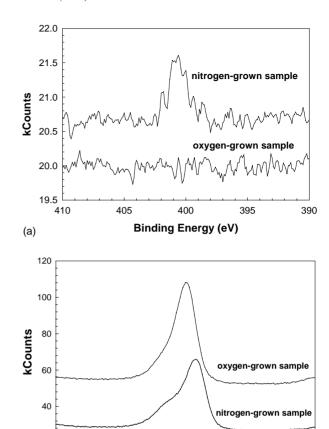

Fig. 1a shows that the nitrogen element is incorporated in the films grown in nitrogen atmosphere, while the oxygen-grown films have no nitrogen element. As it can be seen from Fig. 1b, the nitrogen-grown films have

Fig. 1. (a) The XPS characteristics of nitrogen in nitrogen-grown and oxygen-grown STO films. (b) The XPS characteristics of oxygen in nitrogen-grown and oxygen-grown STO films.

530

**Binding Energy (eV)**

525

20 540

(b)

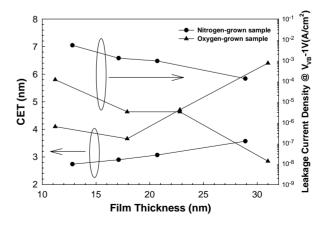

smaller oxygen content than the oxygen-grown films, as no significant amount of oxygen gas is present in the ambient during the deposition of nitrogen-grown films. It can be seen from Fig. 2 that the capacitance equivalent oxide thickness (CET) of nitrogen-grown samples was smaller than that of oxygen-grown samples. The nitrogen could

Fig. 2. Variation of CET and leakage current density with oxide thickness for nitrogen-grown and oxygen-grown STO films.

suppress the growth of interfacial layer when the thin films were deposited at high temperature [8,9]. Therefore, the nitrogen-grown samples should have smaller thickness of interfacial layer and smaller CET. The CET of nitrogen-grown sample increases with an increase of oxide thickness. Such increment of CET in nitrogen-grown film should be mainly the contribution from the increment of STO film thickness, and minor contribution from the interfacial layer. The leakage current density is affected by the oxygen vacancies, STO/Si and STO/Al interfaces. The oxygen vacancy concentration can be determined by using the following reaction

$$O_O \to V_O^{\bullet \bullet} + \frac{1}{2}O_2 + e'$$

(1)

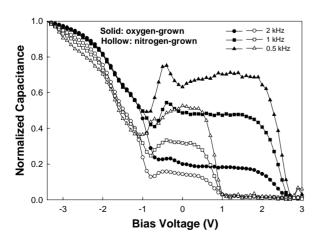

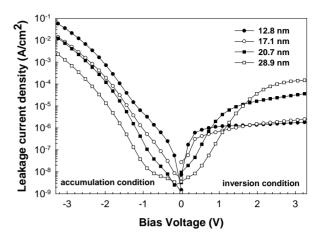

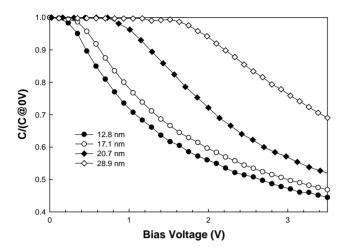

The leakage current of nitrogen-grown films is higher than that of oxygen-grown films as indicated in Fig. 2 which is mainly contributed by the higher amount of oxygen deficiencies in nitrogen-grown films under the consideration of lower expected traps of nitrogen-grown STO/Si interface and similar STO/Al interface between these two films. The result of Fig. 1b supports the point of higher oxygen vacancies in nitrogen-grown films. The normalized C-V curves measured under illumination at various frequencies for oxygen-grown and nitrogen-grown samples are shown in Fig. 3. The results in Fig. 3 indicate that the oxygen-grown sample has larger bulk trap density than nitrogen-grown sample [10]. The reason should result from the nitrogen that resists the atoms of nitrogen-grown STO film to diffuse into the silicon substrates. Fig. 4 indicates that the leakage current density of nitrogen-grown samples under accumulation condition increases with decreasing film thickness, which is attributed to the fact that the thinner film has larger electric field under the same bias voltage. The leakage current density under low positive bias voltage increases with decreasing film thickness, but it increases with increasing film thickness under high positive bias voltage. The saturation of leakage current under inversion condition is observed and the initiation voltage of saturated leakage current increases with increas-

Fig. 3. The normalized C–V curves measured under illumination at various frequencies for oxygen-grown and nitrogen-grown samples.

Fig. 4. Plots of leakage current density vs. bias voltage for various thickness STO-based MIS capacitors.

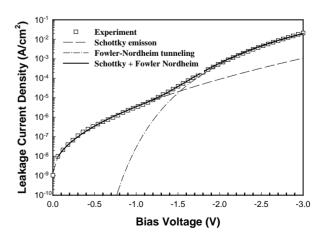

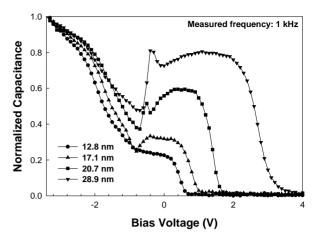

ing film thickness. Therefore, the conduction mechanisms of inversion condition should be quite different from those of accumulation condition. The measured data and simulation results of leakage current density under the accumulation condition are shown in Fig. 5. Schottky emission and Fowler–Nordheim tunneling mechanisms are responsible for the leakage current density at low electric field and high electric field under negative bias voltage, respectively. Fig. 6 depicts deep depletion of the capacitance–voltage characteristics under the inversion condition. The initiation voltage of deep depletion increases with increasing film thickness and the trend is similar with the initiation voltage of saturated leakage current. Therefore, the deep depletion may have some correlation with leakage current saturation.

### 3.2. Correlation between the deep depletion and leakage current saturation

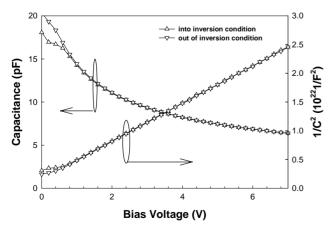

Fig. 7 shows C-V measurements swept into and out of inversion condition. Both C-V curves are almost identical except a voltage shift that occurs due to current stress

Fig. 5. Comparison between experimental data and simulation results of leakage current density under the accumulation condition of nitrogen-grown sample.

Fig. 6. Normalized capacitance measured at  $100\,\mathrm{kHz}$  for various dielectric film thickness of the MIS capacitors.

during the C-V measurement. Deep depletion could result from fast sweep rate of C-V measurements [12]. Deep depletion under inversion condition due to fast sweep rate would occur while sweeping into inversion condition, but would disappear while sweeping out of inversion condition. Therefore, the deep depletion shown in Figs. 6 and 7 is not due to fast sweep rate. For further confirmation, the time-dependent C-V and I-V measurements were also made. The C-V and I-V measurements proceeded with 0.1 V step and different delay times including 0, 0.05, 0.2, and 1 s. Delay time is used to reduce the effect of fast sweep rate. The results of C-V and I-V measurements indicate the same trend with different delay times and all capacitors exhibit the deep depletion phenomenon. The time-independent C-V and I-V results indicate that the deep depletion does not result from fast sweep rate. For MIS structure, the depletion width, W, is given by [11]

$$W = \sqrt{\frac{2\varepsilon_{\rm si}\psi_{\rm s}({\rm inv})}{qN_{\rm A}}} \tag{2}$$

Fig. 7. The C-V curves of sweep into and out of inversion condition direction.

where  $\varepsilon_{si}$  is the permittivity of silicon,  $\psi_s(inv)$  is the surface potential under inversion condition, q is the unit charge, and  $N_A$  the substrate dopant concentration. The formula of depletion capacitance,  $C_D$ , is given by

$$C_{\rm D} = \frac{A\varepsilon_{\rm Si}}{W} \tag{3}$$

where A is the capacitor area. Because the capacitance of gate dielectric is much larger than depletion capacitance under the inversion condition, the surface potential is almost equal to the gate bias voltage ( $V_{\rm G}$ ). Therefore, we can obtain

$$\psi_{\rm s} \cong V_{\rm G} \propto \frac{1}{C^2} \tag{4}$$

It can also be seen in Fig. 7 that both slopes of the  $1/C^2$ –V curves are almost the same and the  $1/C^2$ –V curve has good linear fitting results, indicating that the deep depletion should result from depletion width broadening. With Eq. (4), the substrate dopant concentration could be extracted from the slope of the  $1/C^2$ –V curve. The extracted substrate dopant concentration of nitrogen-grown samples range between  $1 \times 10^{15}$  and  $3 \times 10^{15}$  cm<sup>-3</sup>. The substrate dopant concentrations may be affected by thermal processing, so the extracted dopant concentrations have a little difference. The extracted dopant concentrations of nitrogen-grown samples are consistent with dopant concentration of the silicon substrate with 1–10  $\Omega$  cm resistivity. The leakage current density due to the generation current density is given by [13]

$$J = \int_{w_m}^{w} \frac{qn_{\rm i}}{\tau} \, \mathrm{d}x + qn_{\rm i}s + \frac{qn_{\rm i}^2 D_{\rm n}}{N_{\rm A}L_{\rm n}} \tag{5}$$

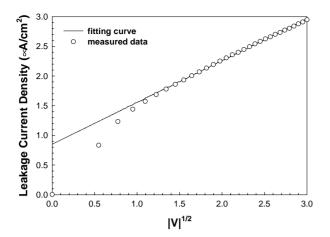

where J is the leakage current density, w the depletion width when the potential drop across the semiconductor is  $\psi_s$ ,  $w_m$  the depletion width at strong inversion,  $n_i$  the intrinsic concentration,  $\tau$  the generation lifetime, s the surface recombination velocity which depends on the interface state density, and  $D_n$  and  $L_n$  are diffusion coefficient and diffusion length of minority carriers, respectively. The generation current is contributed by three different mechanisms: bulk trap, interface trap, and diffusion current. The interface states should be same and contribute a constant component to the generation current under the deep depletion. Diffusion current dominating at high temperature can be neglected at room temperature. However, the bulk traps mainly contribute the increased generation current with increasing depletion width under the inversion condition. Therefore, the increased leakage current under the inversion condition at room temperature results from the bulk traps, not the interface trap and diffusion current. Fig. 8 shows the measured data and fitting curve of leakage current density under the inversion condition. With the Eq. (5) and the previous discussion, the solid line in J versus  $|V|^{1/2}$  plot (Fig. 8) provides a good fit to the data, indicating that the leakage current density under the inversion condition obeys the generation current mechanism due to the bulk trap. The

Fig. 8. Comparison between experimental data and generation current mechanism. The inset is the relation of leakage current density vs. bias voltage.

generation lifetime can be given by [11]

$$\tau = \frac{1}{\sigma v_{\rm th} N_{\rm t}} \tag{6}$$

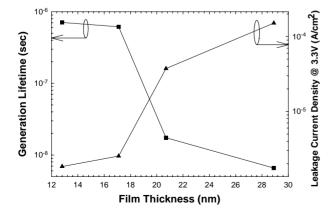

where  $\sigma$  is the capture cross section,  $v_{\text{th}}$  the carrier thermal velocity, and  $N_t$  the bulk trap density. From the correlation between the deep depletion and leakage current saturation, the generation lifetime of nitrogen-grown samples can be extracted. As can be seen in Fig. 9, the extracted generation lifetimes range from several micro to nano second. The generation lifetime of bulk silicon is 2.4 ms [11]. Because of some damage or diffusion of atoms into the silicon substrates during processing, the generation lifetime of nitrogen-grown samples should be smaller than that of bulk silicon. Therefore, the extracted generation lifetime, which is less than 2.4 ms, should be a reasonable value. It needs more time to deposit thicker STO films, which means more plasma damage or more impurity diffusion into silicon substrate. Therefore, the extracted generation lifetime of nitrogen-grown samples decreased with increasing film

Fig. 9. Plot of generation lifetime vs. oxide thickness for the nitrogengrown STO-based MIS capacitor.

Fig. 10. The normalized *C–V* curves measured under illumination at 1 kHz for various nitrogen-grown samples.

thickness. Because the substrate dopant concentrations of nitrogen-grown sample are almost the same, the sample with small generation lifetime should have large saturated leakage current density under the inversion condition. The normalized *C*–*V* curves measured under illumination at 1 kHz for various nitrogen-grown samples are shown in Fig. 10. The normalized capacitance increased with increasing STO film thickness for the bias voltage larger than –1 V, indicating that the bulk trap density of STO samples increased with increasing STO film thickness. The results are consistent with the extracted generation lifetime in Fig. 9. Therefore, the extracted generation lifetime could be a criterion for judging the quality of silicon substrate processed under different processing conditions.

### 4. Conclusions

The STO films have been deposited in Ar-O<sub>2</sub> or Ar-N<sub>2</sub>. mixed ambient to form MIS capacitors to investigate C-V and I-V characteristics. The CET of nitrogen-grown films is smaller than that of oxygen-grown films due to the nitrogen in the thin film that could suppress the interface growth. The leakage current density under the accumulation condition of nitrogen-grown samples is larger than that of oxygen-grown samples due to the higher amount of oxygen vacancies of nitrogen-grown films. The conduction mechanisms of accumulation condition and inversion condition of nitrogen-grown samples are quite different. Under the accumulation condition, the leakage current density of nitrogen-grown sample under low bias voltage and high bias voltage obeys Schottky emission mechanism and Fowler-Nordheim tunneling mechanism, respectively. Due to insufficient concentration of electrons to maintain leakage current under the inversion condition of nitrogen-grown samples, the depletion layer would broaden to generate more electrons. Therefore, the deep depletion and leakage current saturation should occur at the same time. The

leakage current density under the inversion condition of nitrogen-grown samples obeys generation current mechanism due to the bulk trap. The deep depletion could be used to extract the substrate dopant concentration. The correlation between deep depletion and leakage current saturation could extract the generation lifetime of the silicon substrate. Therefore, such method could be used to examine the quality of the silicon substrate processed under different conditions. We successfully explain that the deep depletion and leakage current saturation occur under the inversion condition for highly leaky high-k MIS capacitors.

#### Acknowledgements

The authors acknowledge the financial support from the National Science Council of Republic of China under Contract No. NSC 91-2215-E009-066.

### References

- [1] International Technology Roadmap for Semiconductors, Semiconductor Industry Association, Austin, Texas, 2001.

- [2] D.A. Chang, P. Lin, T.Y. Tseng, Effects of oxygen-argon mixing on the electrical and physical properties of ZrTiO<sub>4</sub> films sputtered on silicon at low temperature, J. Appl. Phys. 78 (1995) 7103–7108.

- [3] A. Chin, C.C. Liao, C.H. Lu, W.J. Chen, C. Tsai, Device and reliability of high-k Al<sub>2</sub>O<sub>3</sub> gate dielectric with good mobility and low D<sub>it</sub>, Symp. VLSI Tech. Dig. (1999) 135–136.

- [4] B.H. Lee, L. Kang, W.J. Qi, R. Nieh, Y. Jeon, K. Onishi, J.C. Lee, Ultrathin hafnium oxide with low leakage and excellent reliability for alternative gate dielectric application, Tech. Dig. Int. Electron Device Meeting (1999) 133–136.

- [5] J.C. Wang, S.H. Chiao, C.L. Lee, T.F. Lei, Y.M. Lin, M.F. Wang, S.C. Chen, C.Y. Lu, M.S. Liang, A physical model for hysteresis phenomenon of the ultrathin ZrO<sub>2</sub> film, J. Appl. Phys. 92 (2002) 3936–3940.

- [6] K. Eisenbeiser, J.M. Finder, Z. Yu, J. Ramdani, J.A. Curless, J.A. Hallmark, R. Droopad, W.J. Ooms, L. Salem, S. Bradshaw, C.D. Overgaard, Field effect transistors with SrTiO<sub>3</sub> gate dielectric on Si, Appl. Phys. Lett. 76 (2000) 1324–1326.

- [7] H.T. Lue, C.J. Wu, T.Y. Tseng, Device modeling of ferroelectric memory field-effect transistor for the application of ferroelectric random access memory, IEEE Trans. UFFC 50 (2003) 5–14.

- [8] G.D. Wilk, R.M. Wallace, J.M. Anthony, High-k gate dielectrics: current status and materials properties considerations, J. Appl. Phys. 89 (2001) 5243–5275.

- [9] C.Y. Liu, H.T. Lue, T.Y. Tseng, Effects of nitridation of silicon and repeated spike heating on the electrical properties of SrTiO<sub>3</sub> gate dielectrics, Appl. Phys. Lett. 81 (2002) 4416–4418.

- [10] C.C. Hong, W.J. Liao, J.G. Hwu, Thickness-dependent stress effect in p-type metal-oxide-semiconductor structure injection current, Appl. Phys. Lett. 82 (2003) 3916–3918.

- [11] S.M. Sze, Physics of Semiconductor Device, Wiley, New York, 1981.

- [12] E.H. Nicollian, J.R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology, Wiley, New York, 2003.

- [13] R.M. Patrikar, R. Lal, J. Vasi, High field characteristics of metaloxide-semiconductor capacitors with the silicon in inversion, J. Appl. Phys. 73 (1993) 3857–3859.