Journal of the European Ceramic Society 24 (2004) 1449-1453

www.elsevier.com/locate/jeurceramsoc

# Electrical properties of sputter deposited SrTiO<sub>3</sub> gate dielectrics

Chih-Yi Liu, Tseung-Yuen Tseng\*

Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30050, Taiwan, ROC

#### Abstract

We report the electrical properties of gate dielectric SrTiO<sub>3</sub> (STO) thin films on Si substrates grown by radio-frequency magnetron sputtering. The interfacial layer between STO and Si degrades the performance of the gate dielectric. We used SiON as a sacrificial layer for incorporating nitrogen into Si substrate surface, which can retard the formation of interfacial layer during the high temperature growth of STO gate dielectric. The polycrystalline STO film grown on nitrogen incorporated Si substrate exhibited lower leakage current due to better interfacial properties and higher dielectric constant. The repeated spike heating technique was also employed to deposit polycrystalline STO film for improving the thermal uniformity of the wafer, which leads to lower gate leakage current. The processing parameters including working pressure, oxygen mass ratio and plasma power also show obvious effect on the electrical properties of the films.

Keywords: Electrical properties; Films; Gate dielectric; SrTiO<sub>3</sub>

© 2003 Elsevier Ltd. All rights reserved.

## 1. Introduction

Following the device continuously scaling down, the conventional SiO<sub>2</sub> gate oxide thickness will be less than 2 nm in the near future. However, the use of ultrathin SiO<sub>2</sub> gate dielectric results in a number of issues, including high gate leakage current, reduced drive current, reliability degradation, boron penetration, and the necessity to grow ultra-thin and uniform SiO<sub>2</sub> layer. Any of these effects will fundamentally limit the usefulness of SiO<sub>2</sub> as a gate dielectric. According to the fundamental quantum mechanical law, the direct tunneling current increases exponentially with decreasing film thickness. The leakage current increases by one order of magnitude when each 0.2 nm thickness decreases. As the SiO<sub>2</sub> thickness scales below 2 nm, the gate leakage current will increase significantly due to direct tunneling. Many high-k materials have been investigated as potential replacements for SiO<sub>2</sub> to provide a physically thicker film for reducing leakage current and improving gate capacitance. The physical thickness of such high-k material can be much larger to reduce the tunneling

E-mail address: tseng@cc.nctu.edu.tw (T.-Yuen Tseng).

current, so alternative gate dielectrics with high dielectric constant are necessary. SrTiO<sub>3</sub> (STO) thin films have been proposed for applications in high charge storage capacity devices, such as DRAM capacitors, because of their high dielectric constant. Recently, STO thin films have been successfully epitaxially grown on Si by using molecular beam epitaxy at Motorola Labs<sup>2</sup> as a gate dielectric of MOSFETs. On the other hand, STO films with low equivalent oxide thickness (EOT) and low leakage current can also be a potential insulating layer as in metal/ferroelectric/insulator/semiconductor (MFIS) structure, which is a basic structure for ferroelectric gate non-volatile ferroelectric memory application.3 In general, interfacial layer will naturally form between high-k metal oxide materials and Si due to Si oxidation and inter-diffusion at high temperature. The resultant interfacial layer of low permittivity materials will limit the highest possible gate capacitance or the lowest achievable EOT. Several methods have been employed to reduce the interfacial reaction. Incorporating nitrogen in silicon substrate has been used to grow ultra thin oxide because nitrogen can suppress the growth of silicon oxide effectively.<sup>4</sup> A repeated-spikeheating technique has been proposed by Hong et al.<sup>5</sup> to grow ultrathin oxide. The radiation heat absorption in two different temperature regions on a wafer could be

<sup>\*</sup> Corresponding author. Tel.: +886-3-5712121; fax: +886-3-5724361.

compensated by repeated-spike-heating technique,<sup>6</sup> so such technique can improve the thermal uniformity to grow uniform SiO<sub>2</sub>. In the present study, we incorporated nitrogen into the silicon surface to alleviate the reaction of the silicon surface into SiO<sub>x</sub> thin interface layer during rf-sputtered deposition STO gate dielectric and to obtain better EOT value. The repeated-spike-heating technique was also employed to deposit STO films for improving the thermal uniformity of the wafer. Electrical characterizations of STO thin films were also performed. Besides the study of the interface improvement, the influence of the processing parameters including working pressure, oxygen mass ratio (OMR), and plasma power on electrical properties of STO thin films was also investigated.

## 2. Experimental

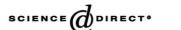

Boron doped p-type silicon (100) wafers with 1–10  $\Omega$ cm resistivity were used as the starting substrates. After standard RCA clean, a 8-nm SiON film was grown on silicon wafer at 950 °C in pure N<sub>2</sub>O gas as the sacrificial oxide. For comparison, 8-nm SiO<sub>2</sub> was thermally grown in pure O<sub>2</sub> ambient as the control sample. After SiON and SiO<sub>2</sub> films were removed by HF dip, the 20-nm STO thin films were deposited on the above pre-treated substrates by using rf magnetron sputtering at a substrate temperature of 500 °C at the same time. The fabrication flow chart is illustrated as Fig. 1(a). The repeated-spike-heating and typical profiles used for depositing STO films are shown in Fig. 1(b). The repeated-spike-heating method was set the temperature to ramp up and down between 450 and 550 °C, while the typical profile was held at a constant temperature of 500 °C. The rapid thermal annealing (RTA) was performed in  $N_2$  ambient to improve the quality of films. To investigate the effect of the processing parameters such as working pressure, OMR, and plasma power on the electrical properties of the films, the other

parameters were fixed while one was varied. For the electrical measurement, Al top electrode with an area of  $7.0\times10^{-4}~\rm cm^2$  was formed by thermal evaporation, followed by electrode patterning using a wet lithography process. Al was also used as backside electrode for obtaining ohmic contact. The capacitance-voltage (C-V) measurements were performed using a HP 4284A at 100 k to 1 M Hz. The current-voltage (I-V) measurements were recorded using a HP 4156A Semiconductor Parameter Analyzer.

#### 3. Results and discussion

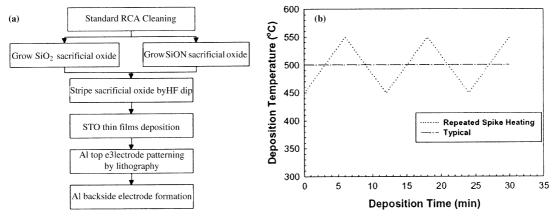

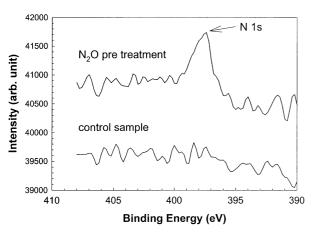

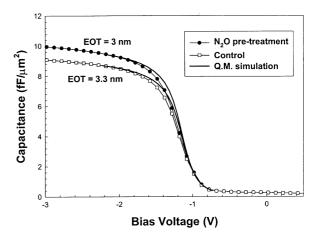

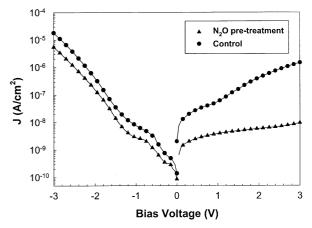

After the removal of SiON and SiO2 sacrificial oxide by dipping in HF, the X-ray photoelectron spectroscopy (XPS) profiles of the silicon substrates were recorded. The XPS profiles are illustrated in Fig. 2. It can be easily seen that nitrogen has been moderately incorporated onto the silicon substrate surface. The amount of nitrogen on the N<sub>2</sub>O pre-treatment wafer calculated from the XPS measurement data is 0.895% atomic ratio. While the STO dielectric capacitance was measured by HP4284A at 100 k to 1 M Hz, the C-V curves were found frequency dependence, as shown in Fig. 3. The phenomena are due to extrinsic parasitic inductance and resistance. After being calibrated by the two-frequency four-element model, illustrated in the insert of Fig. 3, the calibrated C-V curves of the N<sub>2</sub>O pre-treatment and control samples are shown in Fig. 4. We can observe that the EOT of N<sub>2</sub>O pre-treatment sample is smaller than that of the control sample. The quantum mechanical curve fitting<sup>8</sup> is also shown in Fig. 4, from which the EOT is extracted to be 3.0 and 3.3 nm for N<sub>2</sub>O pretreatment and control samples, respectively. The slight shift of the measured C-V curves in comparison with the theoretical curve is due to the interface trap density. Fig. 5 shows the leakage current densities of the N<sub>2</sub>O pre-treatment sample and the control sample. The N<sub>2</sub>O pre-treatment sample has leakage current density 2-3

Fig. 1. (a) Fabrication flow chart (b) Deposition temperatures for repeated-spike-heating and typical samples.

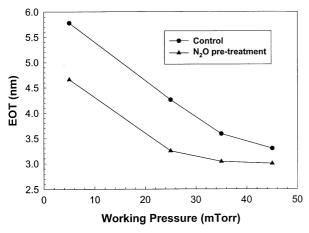

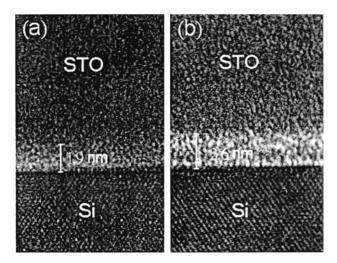

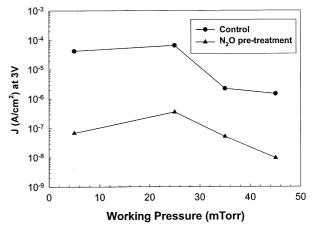

order-magnitude lower than the control sample at the positive bias, while the leakage current of the N<sub>2</sub>O pretreatment sample is little less than that of control sample at the negative bias. The EOT of 500 °C deposited 20 nm thick STO thin films on silicon substrates prepared with various working pressures, 5, 25, 35, and 45 mTorr, are shown in Fig. 6. As expected, the growth rate of the sputtered STO thin films decreases with increasing working pressure. Film thicknesses were fixed at 20 nm through controlling the deposition time in order to eliminate effect of thickness on dielectric properties. The composition of STO films is influenced by the working pressure and may affect the dielectric constant of the films accordingly. This may be the main reason for the EOT decreasing with the increase of working pressure for the samples indicated in Fig. 6. We can also observe that the N<sub>2</sub>O pre-treatment samples have lower EOT than the control samples. Fig. 7 shows the transmission electron microscopy (TEM) images of the N<sub>2</sub>O pre-treatment and the control samples with working

Fig. 2. XPS profiles of the silicon substrate surface after SiON and SiO<sub>2</sub> sacrificial oxides removed by HF dip.

Fig. 3. Measured capacitance of MOS capacitors with STO gate dielectric at three different frequencies. The inset is the equivalent circuit of the calibrated four-element model.

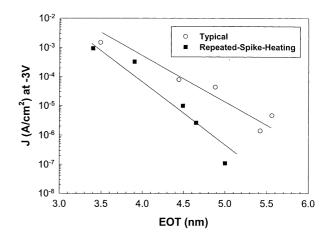

pressure of 45 mTorr, indicating that the interfacial layers of N2O pre-treatment sample and the control sample are 1.9 and 2.6 nm, respectively. Therefore, the N<sub>2</sub>O pre-treatment sample with lower EOT is attributed to its smaller thickness of interfacial layer between STO and Si. The variation of the leakage current density with working pressure for control and N<sub>2</sub>O pre-treatment samples is illustrated in Fig. 8. The N<sub>2</sub>O pre-treatment samples have leakage current densities 2-3 order-magnitude lower than control samples at 3 V. This difference may be due to the formation of the high band gap interfacial layer between STO and Si or the nitrogen can fill the dangling bonds at the interface leading to reduce the gate leakage current. The repeated spike heating technique was also employed to rf-sputtered STO film for improving the thermal uniformity of the wafer. After the STO thin films were deposited on Si substrate at 500 °C, RTA was performed in N2 ambient at the temperatures ranged from 650 to 800 °C to improve the quality of the films. With the same EOT, the repeated spike heating samples have leakage current densities 1–2 orders of magnitude lower than typical samples at -3V, as illustrated in Fig. 9. The reason for the reduction

Fig. 4. Calibrated C–V curves of control and N<sub>2</sub>O pre-treatment samples and their quantum mechanical (Q.M.) fitting.

Fig. 5. I–V curves of control and N<sub>2</sub>O pre-treatment samples.

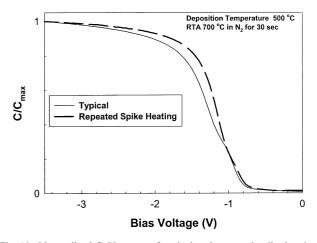

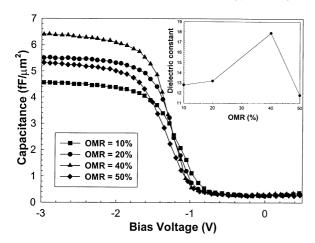

of leakage current in repeated spike heating samples might be due to the improvement of the thermal uniformity of the substrate. Such thermal uniformity may lead to the formation of uniform grain size films, which affects the properties of the STO films. Another possible reason may be due to the smaller interface state density. Fig. 10 indicates the normalized C-V curves of typical and repeated-spike-heating samples. We can observe that the repeated-spike-heating sample has smaller interface trap density than the typical sample. The wagging and stretching of Si-O bond are temperature dependent. Therefore, during the temperature ramping up and down in repeated-spike-heating recipe, it is possible that the residual oxygen in films has more chance to fill the silicon dangling bonds and thus, better interface has been formed. The C-V curves of 500 °C deposited STO thin films on silicon substrates with various  $O_2/(O_2 + Ar)$  (OMR) ratios, 10, 20, 40, and 50%, are shown in Fig. 11. The accumulation capacitance increases with increasing OMR up to 40%, and

Fig. 6. Variation of EOT with working pressure for control and  $N_2O$  pre-treatment samples.

Fig. 7. TEM micrographs of (a)  $N_2O$  pre-treatment STO thin film and (b) control sample.

then further increase of the OMR decreases the capacitance. In 10–40% OMR deposited films, the dielectric constant of STO films increases with the increasing OMR (insert of Fig. 11), which is due to the enhanced

Fig. 8. Gate leakage current density at 3 V of  $N_2O$  pre-treatment and control samples prepared at various working pressures.

Fig. 9. Variation of gate leakage current density with EOT for typical and repeated-spike- heating samples.

Fig. 10. Normalized C–V curves of typical and repeated-spike-heating samples.

Fig. 11. High frequency (100 kHz) C–V curves of MIS capacitors with various OMR STO films. The insert shows the dielectric constant of the films with various OMR.

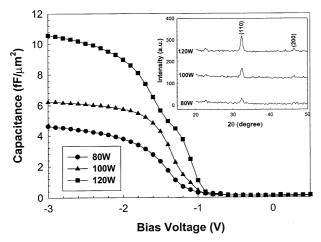

Fig. 12. High frequency (100 kHz) C–V curves of MIS capacitors with various plasma power STO films. The insert shows the XRD patterns of the films with various plasma power.

polarization after oxygen incorporation in the films. The decreased dielectric constant in 50% OMR deposited film may be attributed to thicker interfacial layer and smaller grain size of the films. Fig. 12 shows the high frequency C–V curves of MIS capacitors with various plasma powers deposited STO thin films. It is indicated that the accumulation capacitance increases with the increasing plasma power. Such higher capacitance is due to better crystallized films prepared at higher plasma power, which is confirmed by the XRD patterns as illustrated in the insert of Fig. 12. The kink observed in the C–V curve of 120 W STO film may be due to the trap resulting from the high plasma damage.

### 4. Conclusions

We have grown the SiON sacrificial oxide in pure  $N_2O$  ambient and then stripe it to incorporation nitro-

gen in the silicon surface. Nitrogen incorporation method was carried out to improve the C-V and I-V properties of the STO films. The EOT values of N2O pre-treatment samples are 10-24% lower than those of the control samples while their leakage current densities also have 2-3 order-magnitude lower than those of control samples at the positive bias. The difference may be attributed to the incorporation of certain amount of nitrogen onto the substrate surface during the N<sub>2</sub>O pretreatment to depress the formation of the interfacial layer and reduce the interface states during the high temperature growth of STO gate dielectrics. Besides, the repeated spike heating method was also studied to improve the film quality with the same EOT, this method can reduce the leakage current density 1-2 order-magnitude compared with normal samples, which may be due to resultant interface trap density reduction and uniform grain size. The processing parameters, such as working pressure, OMR, and plasma power have significant influence on the electrical properties of STO thin films.

## Acknowledgements

The authors acknowledge the financial support from the National Science Council of Republic of China under Contract No. NSC 90-2215-E009-100.

#### References

- 1. International Technology Roadmap for Semiconductors, 2001.

- Eisenbeiser, K., Finder, J. M., Yu, Z., Ramdani, J., Curless, J. A., Hallmark, J. A., Droopad, R., Ooms, W. J., Salem, L., Bradshaw, S. and Overgaard, C. D., Field effect transistors with SrTiO<sub>3</sub> gate dielectric on Si. *Appl. Phys. Lett.*, 2000, 76, 1324– 1326.

- Tseng, T. Y., 2001. Ferroelectric thin films for nonvolatile ferroelectric random access memory. In Extended Abstracts of the First International Meeting on Ferroelectric Random Access Memories. pp. 20–21.

- Nam, I. H., Sim, J. S., Hong, S. I., Park, B. K., Lee, J. D., Lee, S. W., Kang, M. S., Kim, Y. W., Suh, K. P. and Lee, W. S., Ultrathin gate oxide grown on nitrogen-implanted silicon for deep submicron CMOS transistors. *IEEE Trans. Electron Devices*, 2001, 48, 2310–2316.

- Hong, C. C., Chang, C. Y., Lee, C. Y. and Hwu, J. G., Reduction in leakage current of low-temperature thin-gate oxide by repeated spike oxidation technique. *IEEE Electron Device Lett.*, 2002, 23, 28–30.

- Hong, C. C., Lee, C. Y., Hsieh, Y. L., Liu, C. C., Fong, I. K. and Hwu, J. G., Improvement in oxide thickness uniformity by repeated spike oxidation (RSO). *IEEE Trans. Semiconduct. Manufact*, 2001, 14, 227–231.

- Lue, H. T., Liu, C. Y. and Tseng, T. Y., An improved twofrequency method of capacitance measurement for the high-k gate dielectrics. *IEEE Electron Device Lett.*, 2002, 23, 553–555.

- Berkeley Device Group [Online]. Available: www.device.eecs. berkeley.edu/qmcv/html.